# BeagleBoard System Reference Manual Rev D

Revision 1.00 October 15, 2012

#### THIS DOCUMENT

This work is licensed under the Creative Commons Attribution-Share Alike 3.0 Unported License. To view a copy of this license, visit <a href="http://creativecommons.org/licenses/by-sa/3.0/">http://creativecommons.org/licenses/by-sa/3.0/</a> or send a letter to Creative Commons, 171 Second Street, Suite 300, San Francisco, California, 94105, USA.

All derivative works are to be attributed to Gerald Coley of BeagleBoard.org.

For more information, see <a href="http://creativecommons.org/license/results-one?license">http://creativecommons.org/license/results-one?license</a> code=by-sa

For any questions, concerns, or issues submit them to gerald@BeagleBoard.org

#### BEAGLEBOARD DESIGN

These design materials referred to in this document are \*NOT SUPPORTED\* and DO NOT constitute a reference design. Only "community" support is allowed via resources at <a href="mailto:BeagleBoard.org/discuss.">BeagleBoard.org/discuss.</a>

THERE IS NO WARRANTY FOR THE DESIGN MATERIALS, TO THE EXTENT PERMITTED BY APPLICABLE LAW. EXCEPT WHEN OTHERWISE STATED IN WRITING THE COPYRIGHT HOLDERS AND/OR OTHER PARTIES PROVIDE THE DESIGN MATERIALS "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESSED OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE DESIGN MATERIALS IS WITH YOU. SHOULD THE DESIGN MATERIALS PROVE DEFECTIVE, YOU ASSUME THE COST OF ALL NECESSARY SERVICING, REPAIR OR CORRECTION.

We mean it; these design materials may be totally unsuitable for any purposes.

BeagleBoard.org provides the enclosed product(s) under the following conditions:

This evaluation board/kit is intended for use for **ENGINEERING DEVELOPMENT**, **DEMONSTRATION**, **OR EVALUATION PURPOSES ONLY** and is not considered by BeagleBoard.org to be a finished end-product fit for general consumer use. Persons handling the product(s) must have electronics training and observe good engineering practice standards. As such, the goods being provided are not intended to be complete in terms of required design-, marketing-, and/or manufacturing-related protective considerations, including product safety and environmental measures typically found in end products that incorporate such semiconductor components or circuit boards. This evaluation board/kit does not fall within the scope of the European Union directives regarding electromagnetic compatibility, restricted substances (RoHS), recycling (WEEE), FCC, CE or UL, and therefore may not meet the technical requirements of these directives or other related directives.

Should this evaluation board/kit not meet the specifications indicated in the User's Guide, the board/kit may be returned within 30 days from the date of delivery for a full refund. THE FOREGOING WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY SELLER TO BUYER AND IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED, IMPLIED, OR STATUTORY, INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE.

The user assumes all responsibility and liability for proper and safe handling of the goods. Further, the user indemnifies BeagleBoard.org from all claims arising from the handling or use of the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge.

EXCEPT TO THE EXTENT OF THE INDEMNITY SET FORTH ABOVE, NEITHER PARTY SHALL BE LIABLE TO THE OTHER FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES.

BeagleBoard.org currently deals with a variety of customers for products, and therefore our arrangement with the user is not exclusive. BeagleBoard.org assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein.

Please read the User's Guide and, specifically, the Warnings and Restrictions notice in the User's Guide prior to handling the product. This notice contains important safety information about temperatures and voltages. For additional information on BeagleBoard.org environmental and/or safety programs, please contact visit <a href="mailto:BeagleBoard.org">BeagleBoard.org</a>.

No license is granted under any patent right or other intellectual property right of BeagleBoard.org covering or relating to any machine, process, or combination in which such BeagleBoard.org products or services might be or are used.

Mailing Address:

BeagleBoard.org 675 North Glenville #195 Richardson, TX 75081

**WARRANTY:** The BeagleBoard is warranted against defects in materials and workmanship for a period of 90 days from purchase. This warranty does not cover any problems occurring as a result of improper use, modifications, exposure to water, excessive voltages, abuse, or accidents. All boards will be returned via standard mail if an issue is found. If no issue is found or express return is needed, the customer will pay all shipping costs.

# Before returning the board, please visit BeagleBoard.org/support

Please refer to sections 12 and 13 of this document for the board checkout procedures and troubleshooting guides.

To return a defective board, please request an RMA at <a href="http://beagleboard.org/support/rma">http://beagleboard.org/support/rma</a>.

# **Table of Contents**

| ES                            |            |

|-------------------------------|------------|

| ES                            | 11         |

| NTRODUCTION                   | 13         |

| HANGE HISTORY                 | 14         |

|                               |            |

|                               |            |

|                               |            |

|                               |            |

|                               |            |

|                               |            |

| DEFINITIONS                   | 15         |

| EAGLEBOARD OVERVIEW           | 15         |

| BEAGLEBOARD USAGE SCENARIOS   | 16         |

| EAGLEBOARD SPECIFICATION      | 17         |

| BEAGLEBOARD FEATURES          | 17         |

|                               |            |

|                               |            |

|                               |            |

|                               |            |

|                               |            |

| STEREO AUDIO OUTPUT CONNECTOR |            |

| STEREO AUDIO IN CONNECTOR     | 20         |

| S-VIDEO CONNECTOR             | 20         |

| DVI-D CONNECTOR               | 20         |

| LCD HEADER                    | 20         |

| SD/MMC 6 IN 1 CONNECTOR       | 21         |

| RESET BUTTON                  | 21         |

|                               |            |

| INDICATORS                    |            |

| POWER CONNECTOR               | 22         |

| JTAG CONNECTOR                |            |

| RS232 HEADER                  |            |

|                               |            |

|                               |            |

| ELECTRICAL SPECIFICATIONS     | 24         |

| RODUCT CONTENTS               | 26         |

| BEAGLEBOARD IN THE BOX REV C4 |            |

| SOFTWARE ON THE BEAGLEBOARD   |            |

| Repair                        | 27         |

| EAGLEBOARD HOOKUP             | 28         |

| CONNECTING USB OTG            |            |

| CONNECTING USB HOST           |            |

| CONNECTING OPTIONAL POWER     |            |

| CONNECTING JTAG               |            |

| CONNECTING SERIAL CABLE       | 32         |

|                               | TRODUCTION |

| 7.6 Con        | NNECTING S-VIDEO                        | 33 |

|----------------|-----------------------------------------|----|

| 7.7 Con        | NNECTING DVI-D CABLE                    | 34 |

|                | NNECTING STEREO OUT CABLE               |    |

|                | NNECTING STEREO IN CABLE                |    |

| 7.10 I         | INDICATOR LOCATIONS                     | 37 |

|                | BUTTON LOCATIONS                        |    |

|                | SD/MMC CONNECTION                       |    |

|                | LCD CONNECTION                          |    |

| 8.0 BEAG       | GLEBOARD SYSTEM ARCHITECTURE AND DESIGN | 41 |

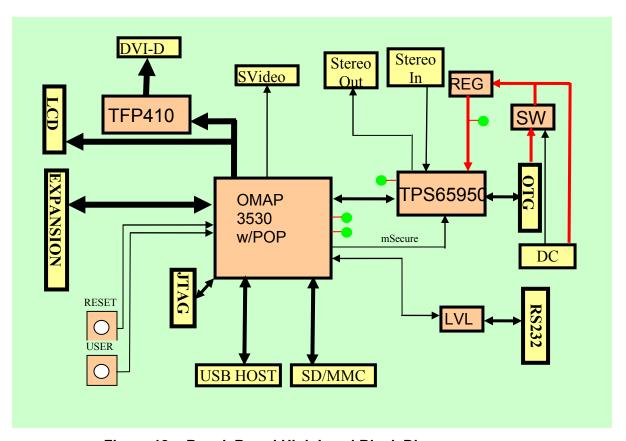

| 8.1 Sys        | STEM BLOCK DIAGRAM                      | 41 |

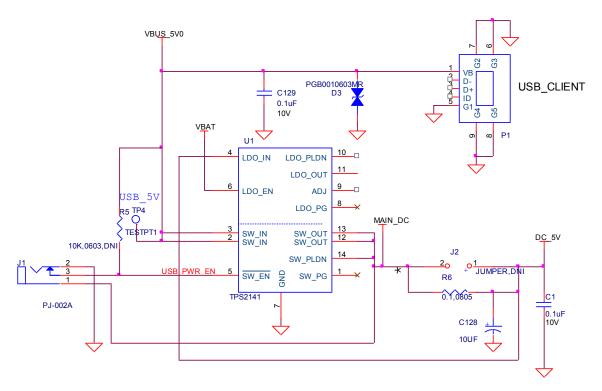

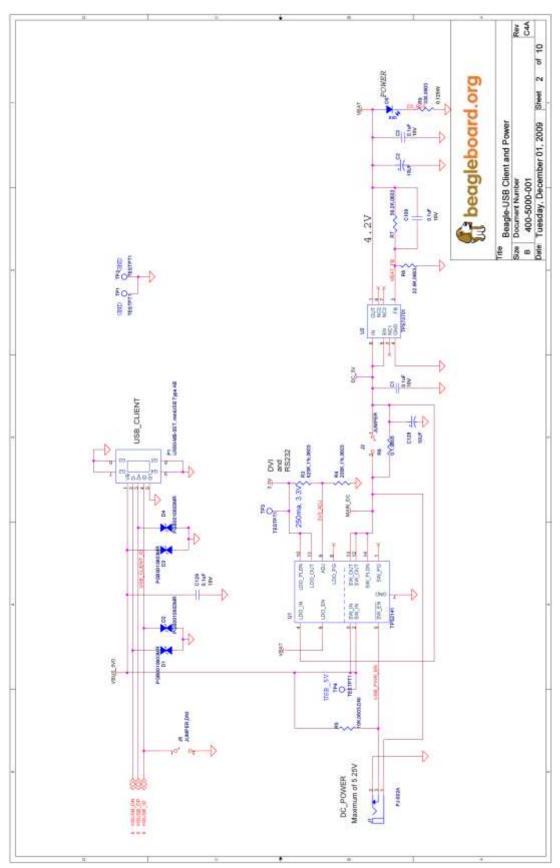

|                | UT POWER                                |    |

| 8.2.1          | USB DC Source                           |    |

| 8.2.2          | Wall Supply Source                      |    |

| 8.2.3          | DC Source Control                       |    |

| 8.2.4          | 3.3V Supply                             |    |

| 8.2.5          | Meter Current Measurement               | 46 |

| 8.2.6          | Processor Current Measurement           | 46 |

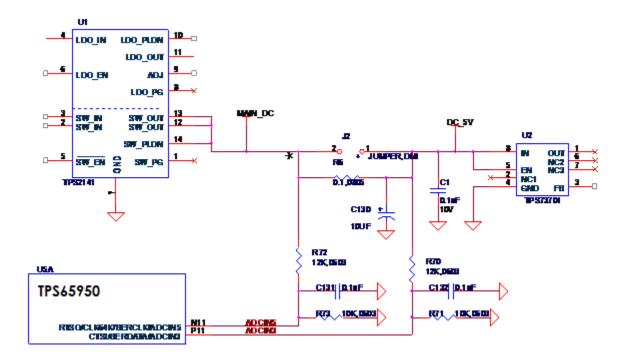

| 8.3 Pov        | WER CONDITIONING                        | 47 |

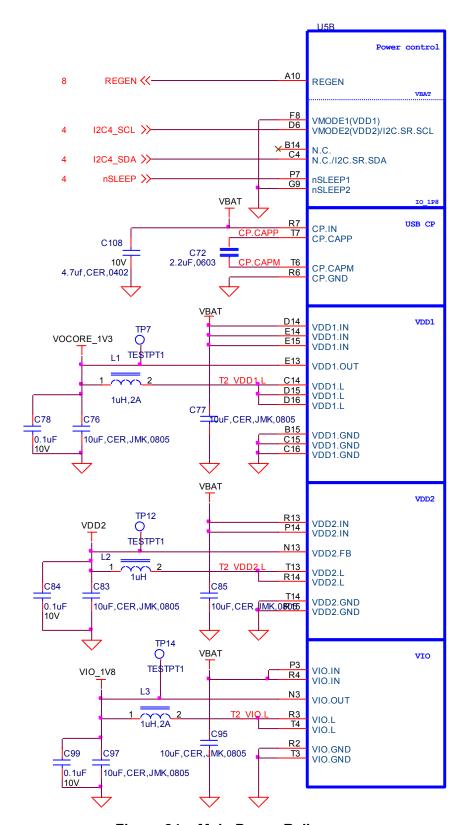

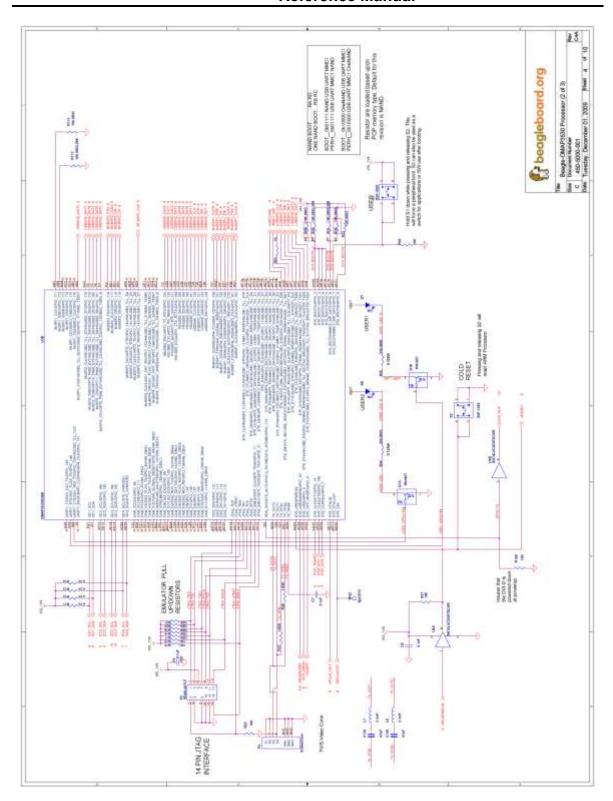

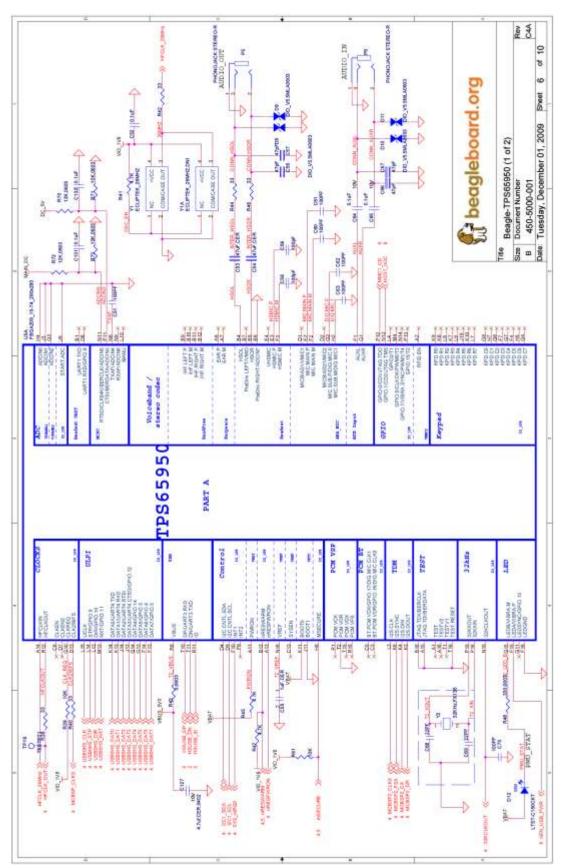

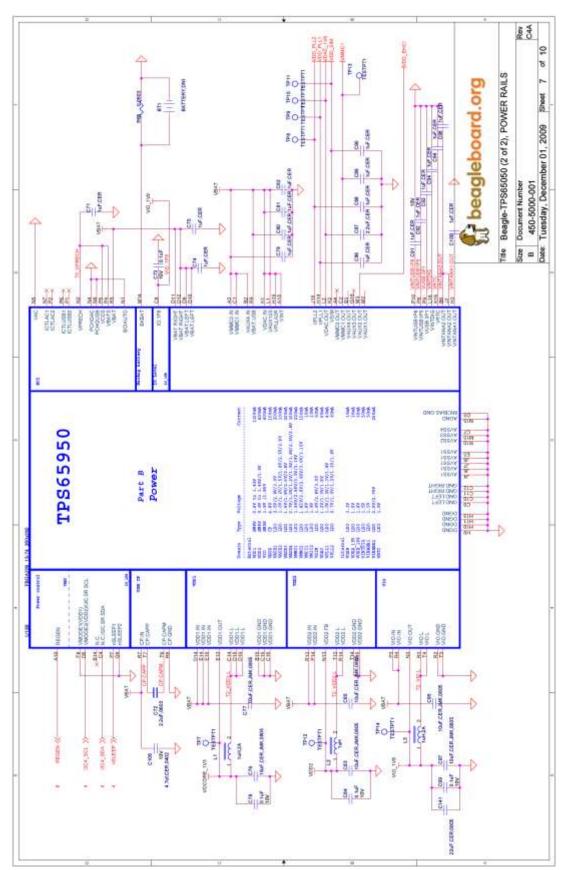

| 8.4 TPS        | S65950 RESET AND POWER MANAGEMENT       | 48 |

| 8.4.1          | Main Core Voltages                      | 49 |

| 8.4.2          | Main DC Input                           | 49 |

| 8.4.3          | OMAP3530 I2C Control                    |    |

| 8.4.4          | VIO 1V8                                 | 49 |

| 8.4.5          | Main Core Voltages Smart Reflex         |    |

| 8.4.6          | VOCORE 1V3                              | 51 |

| 8.4.7          | VDD2                                    | 51 |

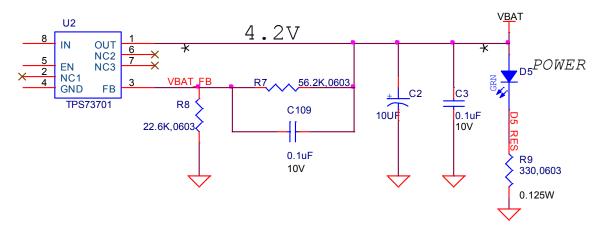

| 8.5 PER        | RIPHERAL VOLTAGES                       | 52 |

| 8.5.1          | VDD_PLL2                                |    |

| 8.5.2          | VDD_PLL1                                |    |

| 8.5.3          | VDAC_1V8                                |    |

| 8.5.4          | VDD_SIM                                 |    |

| 8.5.5          | VMMC1                                   |    |

| 8.5.6          | VAUX2                                   |    |

| 8.5.7          | Boot Configuration                      |    |

| 8.5.8          | RTC Backup Battery                      |    |

| 8.5.9          | Power Sequencing                        |    |

| 8.5.10         |                                         |    |

| 8.5.11         | 0                                       |    |

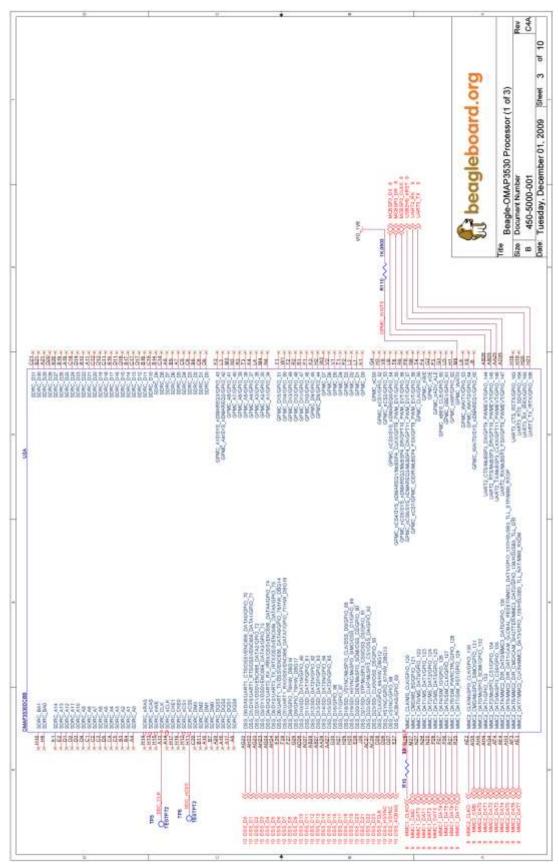

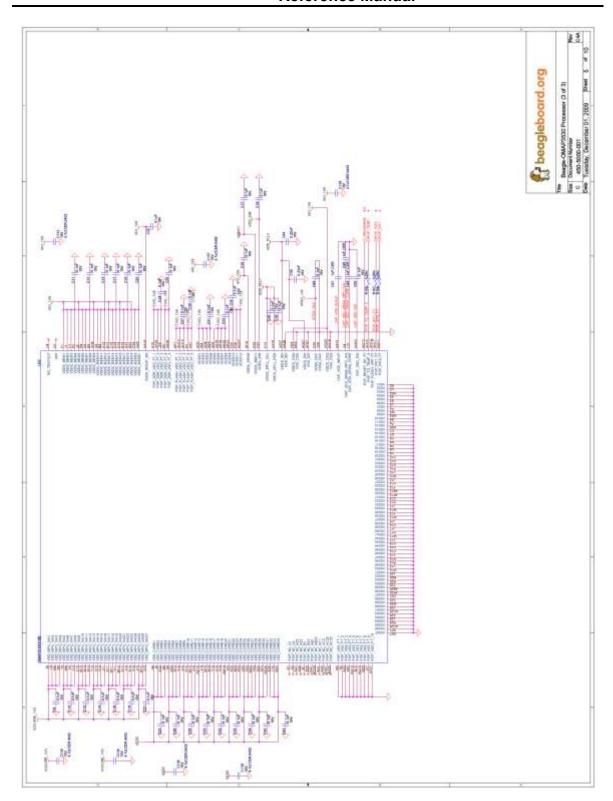

|                | IAP3530 Processor                       |    |

| 8.6.1          | Overview                                |    |

| 8.6.2          | SDRAM Bus                               |    |

| 8.6.3          | GPMC Bus                                |    |

| 8.6.4          | DSS Bus                                 |    |

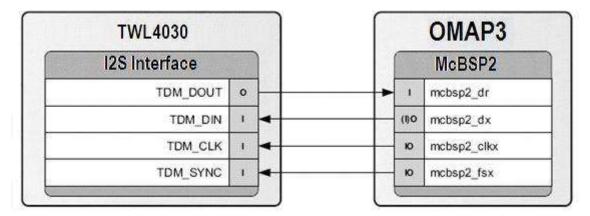

| 8.6.5          | McBSP2                                  |    |

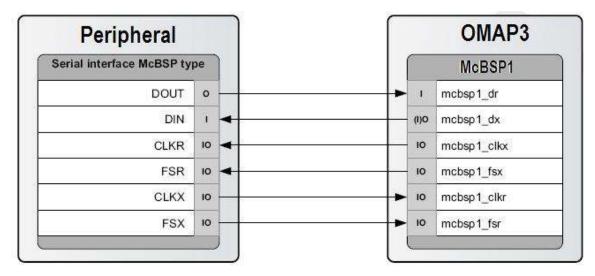

| 8.6.6          | McBSP1                                  |    |

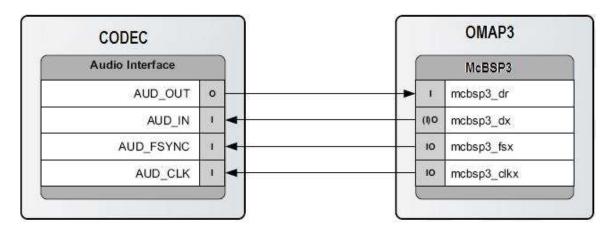

| 8.6.7          | McBSP3                                  |    |

| 8.6.8          | Pin Muxing                              |    |

| 8.6.9          | GPIO Mapping                            |    |

| 8.6.10         | 1 11 0                                  |    |

|                | P MEMORY DEVICE                         |    |

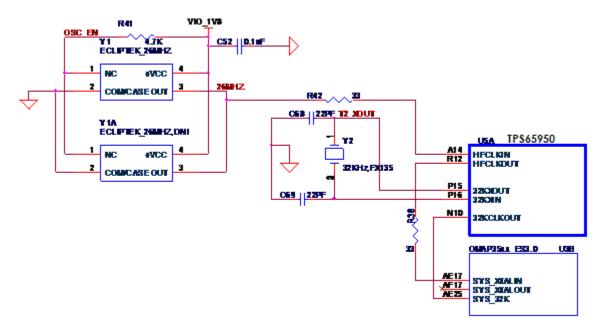

|                | STEM CLOCKS                             |    |

| 8.8.1<br>8.8.2 | 32KHz Clock                             |    |

|                | 26MHz Clock                             |    |

| 0.0.3          | WUDDI CLIXX                             |    |

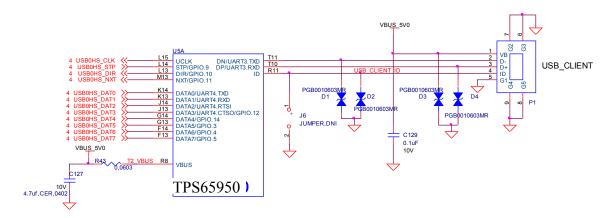

| 8.9 USB  | OTG PORT                   |     |

|----------|----------------------------|-----|

| 8.9.1    | USB OTG Overview           | 67  |

| 8.9.2    | USB OTG Design             | 68  |

| 8.9.3    | OTG ULPI Interface         | 68  |

| 8.9.4    | OTG Charge Pump            | 69  |

| 8.9.5    | OTG USB Connector          | 70  |

| 8.9.6    | OTG USB Protection         | 70  |

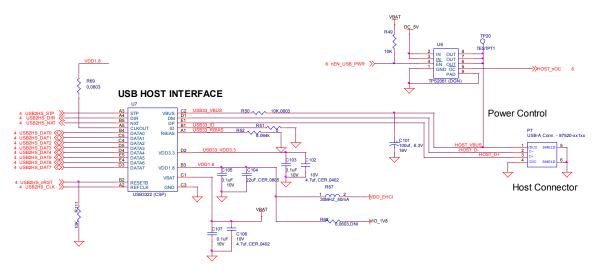

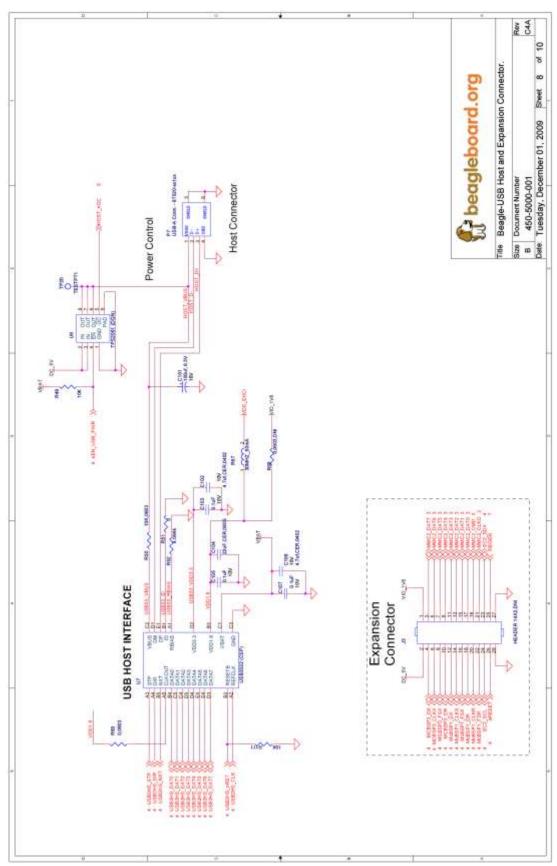

| 8.10 US  | SB Host Port               | 70  |

| 8.10.1   | Host USB OMAP3 Interface   | 71  |

| 8.10.2   | Host USB PHY               | 71  |

| 8.10.3   | Host USB Connector         | 72  |

| 8.10.4   | Host USB Power Control     |     |

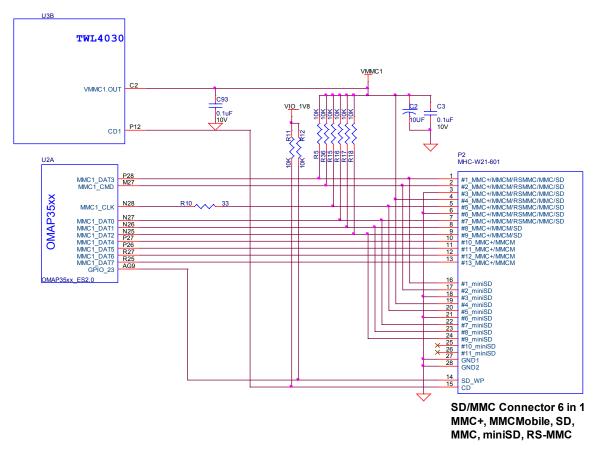

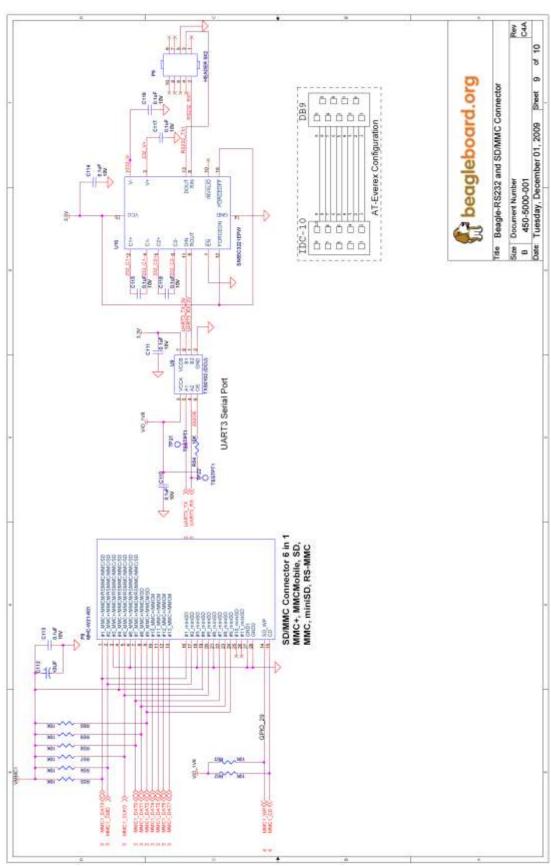

| 8.11 SE  | D/MMC                      | 73  |

| 8.11.1   | <i>MMC Power</i>           |     |

| 8.11.2   | OMAP3530 Interface         | 76  |

| 8.11.3   | Card Detect                |     |

| 8.11.4   | Write Protect              |     |

| 8.11.5   | 8 Bit Mode                 |     |

| 8.11.6   | Booting From SD/MMC Cards  |     |

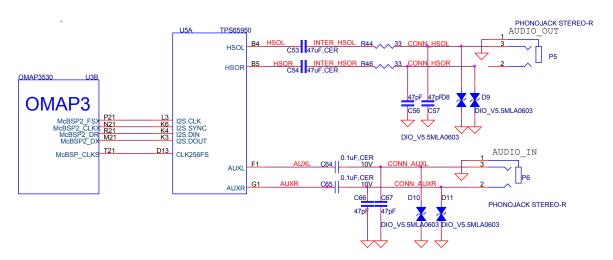

| 8.12 Au  | JDIO INTERFACE             |     |

| 8.12.1   | OMAP3530 Audio Interface   |     |

| 8.12.2   | TPS65950 Audio Interface   |     |

| 8.12.3   | Audio Output Jack          |     |

| 8.12.4   | Audio Input Jack           |     |

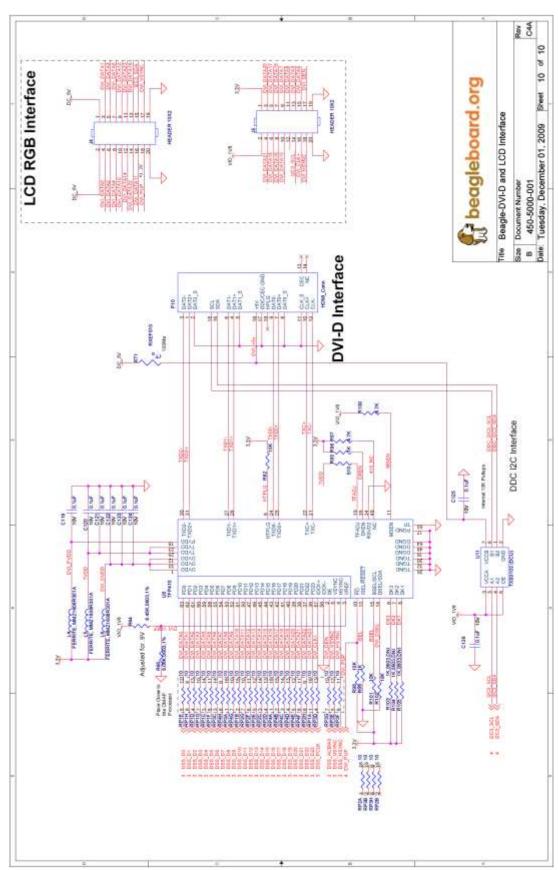

|          | VI-D Interface             |     |

| 8.13.1   | OMAP3530 LCD Interface     |     |

| 8.13.2   | OMAP3530 LCD Power         |     |

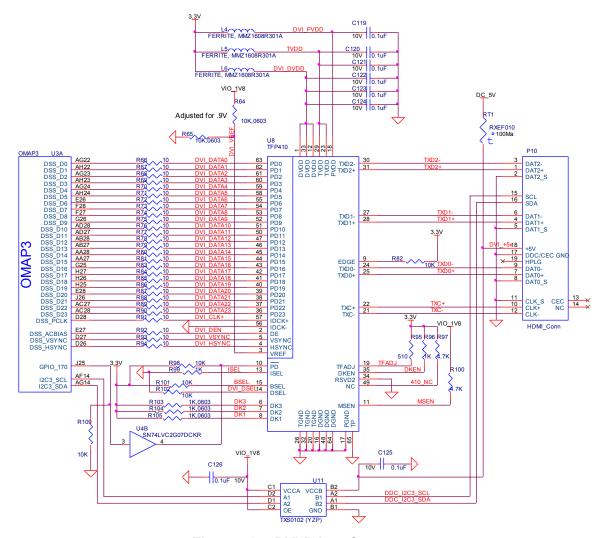

| 8.13.3   | TFP410 Framer              |     |

| 8.13.4   | TFP410 Power               |     |

| 8.13.5   | TFP410 Control Pins        |     |

| 8.13.6   | DVI-D Connector            |     |

|          | CD Expansion Headers       |     |

|          | VIDEO                      |     |

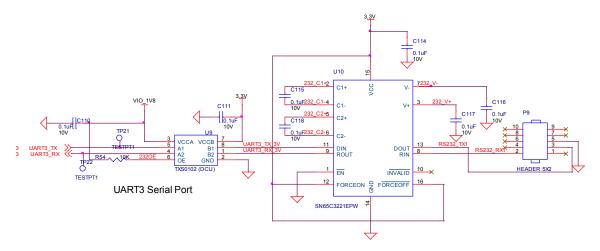

|          | S232 Port.                 |     |

| 8.16.1   |                            |     |

| 8.16.2   | OMAP3530 Level Translator  |     |

| 8.16.3   | RS232 Transceiver          |     |

| 8.16.4   | Connector                  |     |

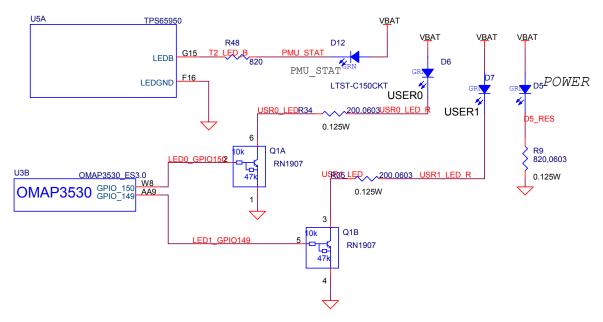

|          | DICATORS                   |     |

| 8.17.1   | Power Indicator            |     |

| 8.17.2   | PMU Status Indicator       |     |

| 8.17.3   | User Indicators            |     |

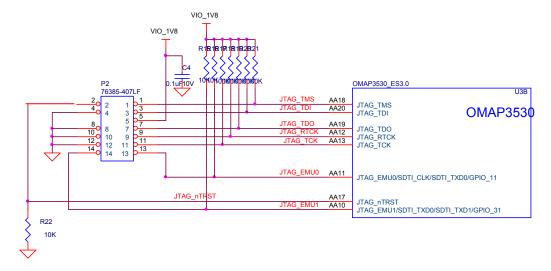

|          | AG                         |     |

| 8.18.1   | OMAP3530 Interface         |     |

| 8.18.2   | Connector                  |     |

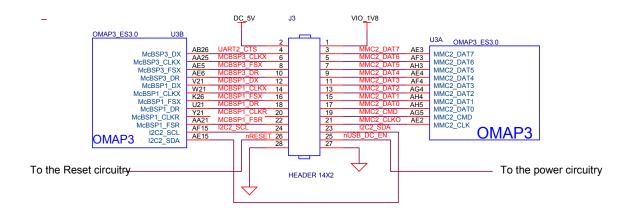

|          | XPANSION HEADER            |     |

| 8.19.1   | OMAP3530 Interface         |     |

| 8.19.2   | Expansion Signals          |     |

| 8.19.3   | Power                      |     |

| 8.19.4   | Reset                      |     |

| 8.19.5   | Power Control              |     |

|          | DDITIONAL EXPANSION HEADER |     |

|          |                            |     |

|          | ECTOR PINOUTS AND CABLES   |     |

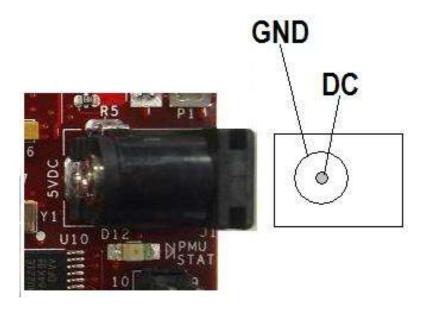

| 9.1 Powe | ER CONNECTOR               | 100 |

| 9.2                                                                                                                       | USB OTG                                                                                                                                                                                                                                                                                                                                                                                                                          | 101               |

|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 9.3                                                                                                                       | S-VIDEO                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |

| 9.4                                                                                                                       | DVI-D                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |

| 9.5                                                                                                                       | LCD                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

| 9.                                                                                                                        | 5.1 Connector Pinout                                                                                                                                                                                                                                                                                                                                                                                                             |                   |

| 9.                                                                                                                        | 5.2 Connector Suppliers                                                                                                                                                                                                                                                                                                                                                                                                          | 106               |

| 9.                                                                                                                        | 5.3 Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                   | 107               |

| 9.                                                                                                                        | 5.4 Mounting Scenarios                                                                                                                                                                                                                                                                                                                                                                                                           | 108               |

| 9.6                                                                                                                       | AUDIO CONNECTIONS                                                                                                                                                                                                                                                                                                                                                                                                                | 110               |

| 9.7                                                                                                                       | Audio Out                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |

| 9.8                                                                                                                       | JTAG                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |

| 9.9                                                                                                                       | RS232                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |

| 9.10                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |

| 9.11                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |

|                                                                                                                           | 11.1 Battery                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

| 9.                                                                                                                        | 11.2 Battery Installation                                                                                                                                                                                                                                                                                                                                                                                                        | 116               |

| 10.0                                                                                                                      | BEAGLEBOARD ACCESSORIES                                                                                                                                                                                                                                                                                                                                                                                                          | 118               |

| 10.1                                                                                                                      | DC Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                  | 110               |

| 10.1                                                                                                                      | SERIAL RIBBON CABLE                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

| 10.2                                                                                                                      | USB HUBS                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| 10.3                                                                                                                      | DVI CABLES                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |

| 10.4                                                                                                                      | DVI-D MONITORS                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |

| 10.5                                                                                                                      | SD/MMC CARDS                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

| 10.7                                                                                                                      | USB to Ethernet                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |

| 10.8                                                                                                                      | USB to WiFi                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |

| 10.9                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |

|                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |

|                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                  | 126               |

| 11.0                                                                                                                      | MECHANICAL INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                           |                   |

| 11.1                                                                                                                      | BEAGLEBOARD DIMENSIONS                                                                                                                                                                                                                                                                                                                                                                                                           | 126               |

| 11.1<br>11.2                                                                                                              | BEAGLEBOARD DIMENSIONSBEAGLEBOARD EXPANSION CARD DESIGN INFORMATION                                                                                                                                                                                                                                                                                                                                                              | 126               |

| 11.1<br>11.2                                                                                                              | BEAGLEBOARD DIMENSIONS                                                                                                                                                                                                                                                                                                                                                                                                           | 126<br>127<br>127 |

| 11.1<br>11.2                                                                                                              | BEAGLEBOARD DIMENSIONS BEAGLEBOARD EXPANSION CARD DESIGN INFORMATION                                                                                                                                                                                                                                                                                                                                                             |                   |

| 11.1<br>11.2                                                                                                              | BEAGLEBOARD DIMENSIONS                                                                                                                                                                                                                                                                                                                                                                                                           |                   |

| 11.1<br>11.2<br>1.1<br>12.0                                                                                               | BEAGLEBOARD DIMENSIONS                                                                                                                                                                                                                                                                                                                                                                                                           |                   |

| 11.1<br>11.2<br>1.                                                                                                        | BEAGLEBOARD DIMENSIONS                                                                                                                                                                                                                                                                                                                                                                                                           |                   |

| 11.1<br>11.2<br>1.1<br>12.0<br>12.1                                                                                       | BEAGLEBOARD DIMENSIONS                                                                                                                                                                                                                                                                                                                                                                                                           |                   |

| 11.1<br>11.2<br>1.<br>12.0<br>12.1<br>12.2                                                                                | BEAGLEBOARD DIMENSIONS                                                                                                                                                                                                                                                                                                                                                                                                           |                   |

| 11.1<br>11.2<br>1.1<br>12.0<br>12.1<br>12.2<br>12.3                                                                       | BEAGLEBOARD DIMENSIONS BEAGLEBOARD EXPANSION CARD DESIGN INFORMATION  1.2.1 Mounting Method 1.2.2 Expansion EEPROM  BOARD VERIFICATION  EQUIPMENT OUT OF THE BOX SD CARD CONFIGURATION FACTORY BOOT VERIFICATION                                                                                                                                                                                                                 |                   |

| 11.1<br>11.2<br>1.<br>12.0<br>12.1<br>12.2<br>12.3<br>12.4                                                                | BEAGLEBOARD DIMENSIONS BEAGLEBOARD EXPANSION CARD DESIGN INFORMATION  1.2.1 Mounting Method 1.2.2 Expansion EEPROM  BOARD VERIFICATION  EQUIPMENT OUT OF THE BOX SD CARD CONFIGURATION FACTORY BOOT VERIFICATION BOARD SD BOOT                                                                                                                                                                                                   |                   |

| 11.1<br>11.2<br>1.<br>12.0<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5                                                        | BEAGLEBOARD DIMENSIONS BEAGLEBOARD EXPANSION CARD DESIGN INFORMATION  1.2.1 Mounting Method 1.2.2 Expansion EEPROM  BOARD VERIFICATION  EQUIPMENT OUT OF THE BOX SD CARD CONFIGURATION FACTORY BOOT VERIFICATION BOARD SD BOOT FACTORY BOOT REINSTALL                                                                                                                                                                            |                   |

| 11.1<br>11.2<br>12.0<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6                                                      | BEAGLEBOARD DIMENSIONS BEAGLEBOARD EXPANSION CARD DESIGN INFORMATION  1.2.1 Mounting Method 1.2.2 Expansion EEPROM  BOARD VERIFICATION  EQUIPMENT OUT OF THE BOX SD CARD CONFIGURATION FACTORY BOOT VERIFICATION BOARD SD BOOT FACTORY BOOT REINSTALL BOOTING THE KERNEL                                                                                                                                                         |                   |

| 11.1<br>11.2<br>1.1<br>12.0<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7<br>12.8                               | BEAGLEBOARD DIMENSIONS BEAGLEBOARD EXPANSION CARD DESIGN INFORMATION  1.2.1 Mounting Method 1.2.2 Expansion EEPROM  BOARD VERIFICATION  EQUIPMENT OUT OF THE BOX SD CARD CONFIGURATION FACTORY BOOT VERIFICATION BOARD SD BOOT FACTORY BOOT REINSTALL BOOTING THE KERNEL                                                                                                                                                         |                   |

| 11.1<br>11.2<br>1.1<br>12.0<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7<br>12.8                               | BEAGLEBOARD DIMENSIONS BEAGLEBOARD EXPANSION CARD DESIGN INFORMATION  1.2.1 Mounting Method 1.2.2 Expansion EEPROM.  BOARD VERIFICATION  EQUIPMENT OUT OF THE BOX SD CARD CONFIGURATION FACTORY BOOT VERIFICATION BOARD SD BOOT FACTORY BOOT REINSTALL BOOTING THE KERNEL UBOOT TESTS                                                                                                                                            |                   |

| 11.1<br>11.2<br>1.1<br>12.0<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7<br>12.8                               | BEAGLEBOARD DIMENSIONS BEAGLEBOARD EXPANSION CARD DESIGN INFORMATION  1.2.1 Mounting Method 1.2.2 Expansion EEPROM.  BOARD VERIFICATION  EQUIPMENT OUT OF THE BOX SD CARD CONFIGURATION FACTORY BOOT VERIFICATION BOARD SD BOOT FACTORY BOOT REINSTALL BOOTING THE KERNEL UBOOT TESTS                                                                                                                                            |                   |

| 11.1<br>11.2<br>1.1<br>12.0<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7<br>12.8<br>1.1<br>12.9                | BEAGLEBOARD DIMENSIONS BEAGLEBOARD EXPANSION CARD DESIGN INFORMATION  1.2.1 Mounting Method 1.2.2 Expansion EEPROM.  BOARD VERIFICATION  EQUIPMENT OUT OF THE BOX SD CARD CONFIGURATION FACTORY BOOT VERIFICATION BOARD SD BOOT FACTORY BOOT REINSTALL BOOTING THE KERNEL UBOOT TESTS 2.8.1 EDID Test 2.8.2 LED Test 2.8.3 DVI-D Test KERNEL BASED TESTS                                                                         |                   |

| 11.1<br>11.2<br>1.1<br>12.0<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7<br>12.8<br>1.1<br>12.9                | BEAGLEBOARD DIMENSIONS BEAGLEBOARD EXPANSION CARD DESIGN INFORMATION  1.2.1 Mounting Method 1.2.2 Expansion EEPROM  BOARD VERIFICATION  EQUIPMENT OUT OF THE BOX SD CARD CONFIGURATION FACTORY BOOT VERIFICATION BOARD SD BOOT FACTORY BOOT REINSTALL BOOTING THE KERNEL UBOOT TESTS 2.8.1 EDID Test 2.8.2 LED Test KERNEL BASED TESTS                                                                                           |                   |

| 11.1<br>11.2<br>1.1<br>12.0<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7<br>12.8<br>1.1                        | BEAGLEBOARD DIMENSIONS BEAGLEBOARD EXPANSION CARD DESIGN INFORMATION  1.2.1 Mounting Method 1.2.2 Expansion EEPROM.  BOARD VERIFICATION  EQUIPMENT OUT OF THE BOX SD CARD CONFIGURATION FACTORY BOOT VERIFICATION BOARD SD BOOT FACTORY BOOT REINSTALL BOOTING THE KERNEL UBOOT TESTS 2.8.1 EDID Test 2.8.2 LED Test KERNEL BASED TESTS 2.9.1 DVI-D Test 2.9.2 S-Video Test                                                      |                   |

| 11.1<br>11.2<br>1.1<br>12.0<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7<br>12.8<br>1.1                        | BEAGLEBOARD DIMENSIONS BEAGLEBOARD EXPANSION CARD DESIGN INFORMATION  1.2.1 Mounting Method 1.2.2 Expansion EEPROM  BOARD VERIFICATION  EQUIPMENT OUT OF THE BOX SD CARD CONFIGURATION FACTORY BOOT VERIFICATION BOARD SD BOOT FACTORY BOOT REINSTALL BOOTING THE KERNEL UBOOT TESTS 2.8.1 EDID Test 2.8.2 LED Test KERNEL BASED TESTS                                                                                           |                   |

| 11.1<br>11.2<br>1.1<br>12.0<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7<br>12.8<br>1.1                        | BEAGLEBOARD DIMENSIONS BEAGLEBOARD EXPANSION CARD DESIGN INFORMATION  1.2.1 Mounting Method 1.2.2 Expansion EEPROM.  BOARD VERIFICATION  EQUIPMENT OUT OF THE BOX SD CARD CONFIGURATION FACTORY BOOT VERIFICATION BOARD SD BOOT FACTORY BOOT REINSTALL BOOTING THE KERNEL UBOOT TESTS 2.8.1 EDID Test 2.8.2 LED Test KERNEL BASED TESTS 2.9.1 DVI-D Test 2.9.2 S-Video Test                                                      |                   |

| 11.1<br>11.2<br>1.1<br>12.0<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7<br>12.8<br>1.1<br>12.9                | BEAGLEBOARD DIMENSIONS BEAGLEBOARD EXPANSION CARD DESIGN INFORMATION  1.2.1 Mounting Method  1.2.2 Expansion EEPROM  BOARD VERIFICATION  EQUIPMENT  OUT OF THE BOX SD CARD CONFIGURATION FACTORY BOOT VERIFICATION BOARD SD BOOT FACTORY BOOT REINSTALL BOOTING THE KERNEL UBOOT TESTS  2.8.1 EDID Test 2.8.2 LED Test 2.8.3 DVI-D Test KERNEL BASED TESTS 2.9.1 DVI-D Test 2.9.2 S-Video Test 2.9.3 Audio Test  TROUBLESHOOTING |                   |

| 11.1<br>11.2<br>1.1<br>12.0<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7<br>12.8<br>1.1<br>12.9<br>1.1<br>13.0 | BEAGLEBOARD DIMENSIONS BEAGLEBOARD EXPANSION CARD DESIGN INFORMATION  1.2.1 Mounting Method 1.2.2 Expansion EEPROM.  BOARD VERIFICATION  EQUIPMENT OUT OF THE BOX SD CARD CONFIGURATION FACTORY BOOT VERIFICATION BOARD SD BOOT FACTORY BOOT REINSTALL BOOTING THE KERNEL UBOOT TESTS 2.8.1 EDID Test 2.8.2 LED Test 2.8.3 DVI-D Test KERNEL BASED TESTS 2.9.1 DVI-D Test 2.9.2 S-Video Test 2.9.3 Audio Test  TROUBLESHOOTING.  |                   |

| 13.2   |                | ROUBLESHOOTING GUIDE                   |     |

|--------|----------------|----------------------------------------|-----|

| 13.3   |                | ERIAL PORT ISSUES                      |     |

| _      | 3.3.1          | First Step                             |     |

|        | 3.3.2<br>3.3.3 | Second StepThird Step                  |     |

|        | 3.3.4          | Fourth Step                            |     |

| 14.0   | KNO            | OWN ISSUES                             | 156 |

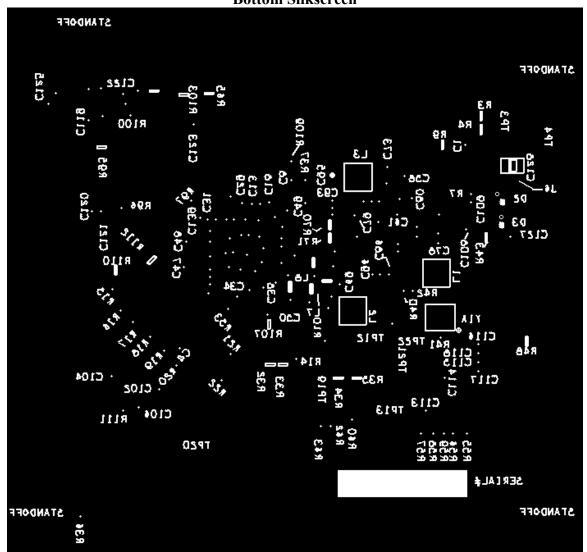

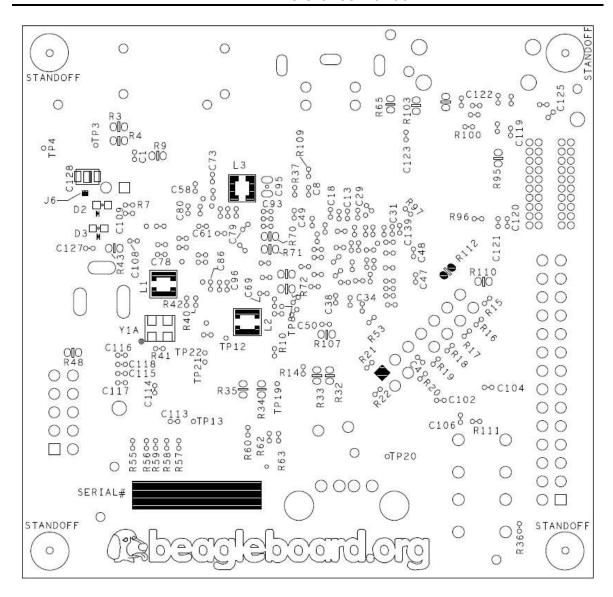

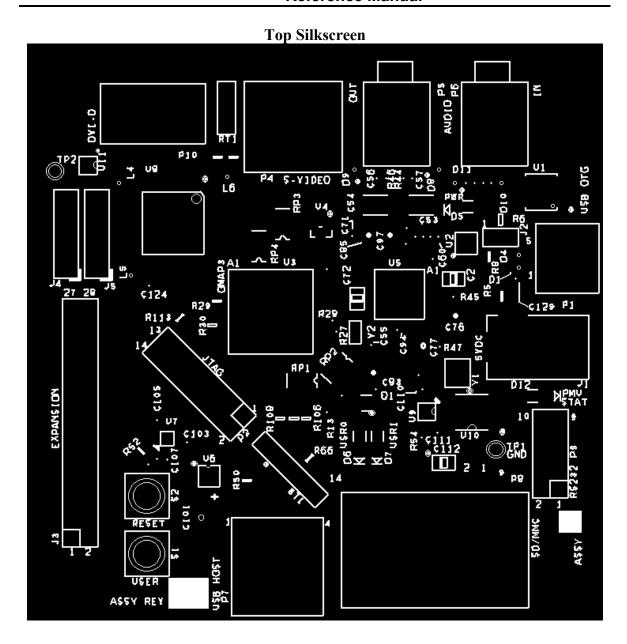

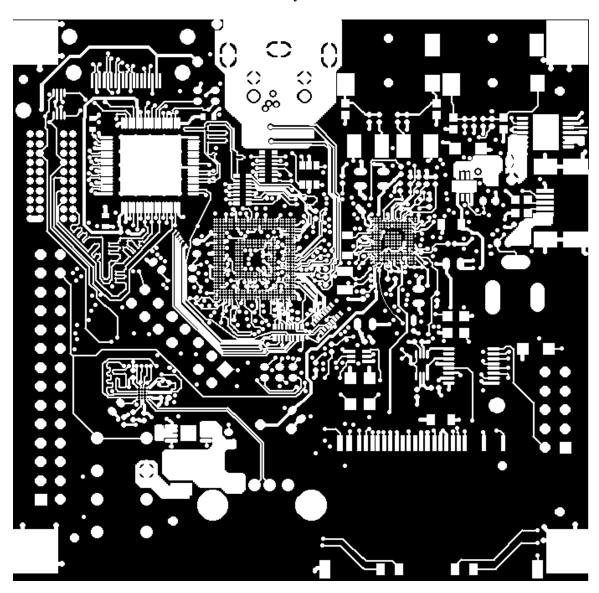

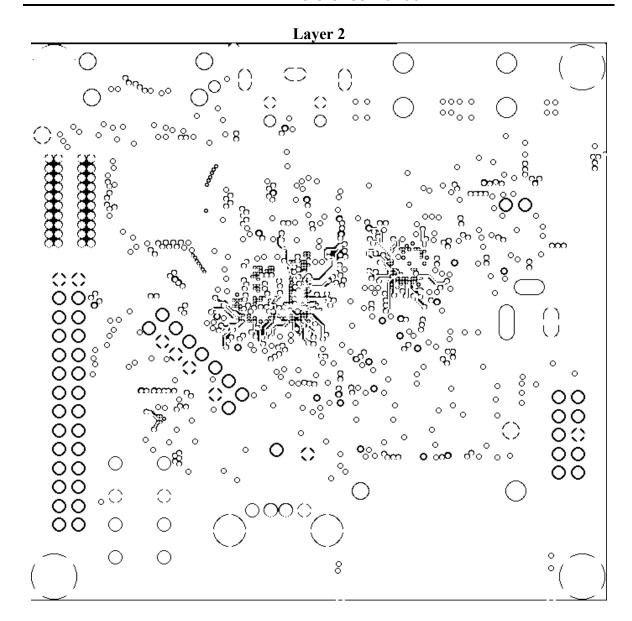

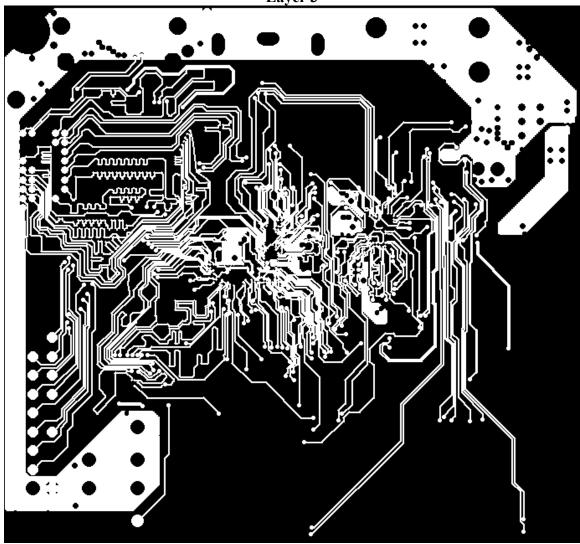

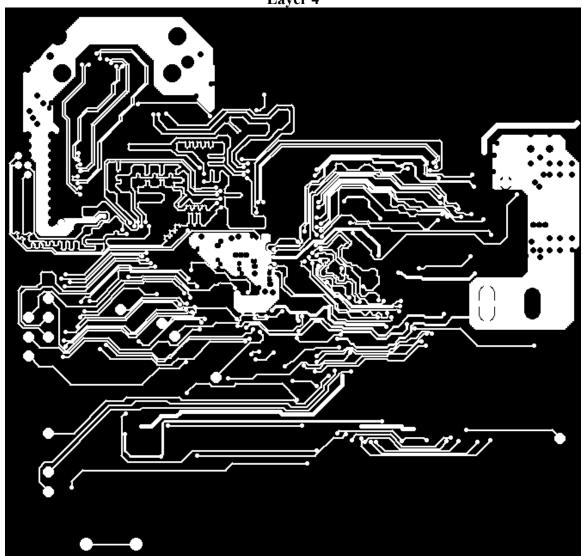

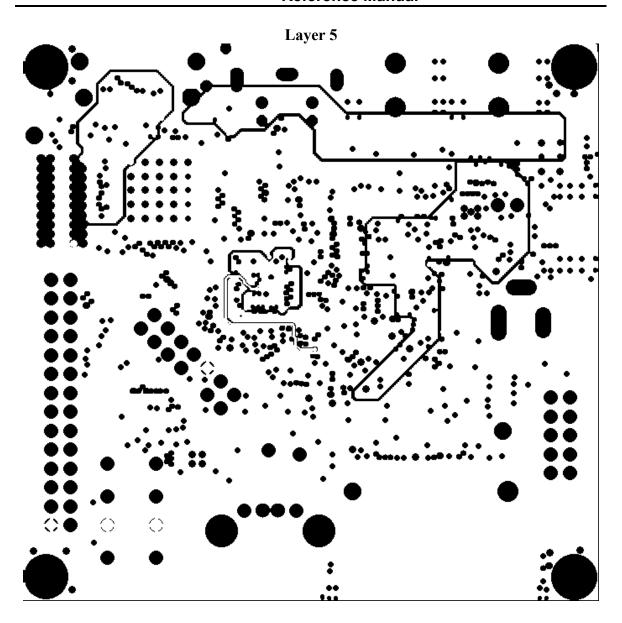

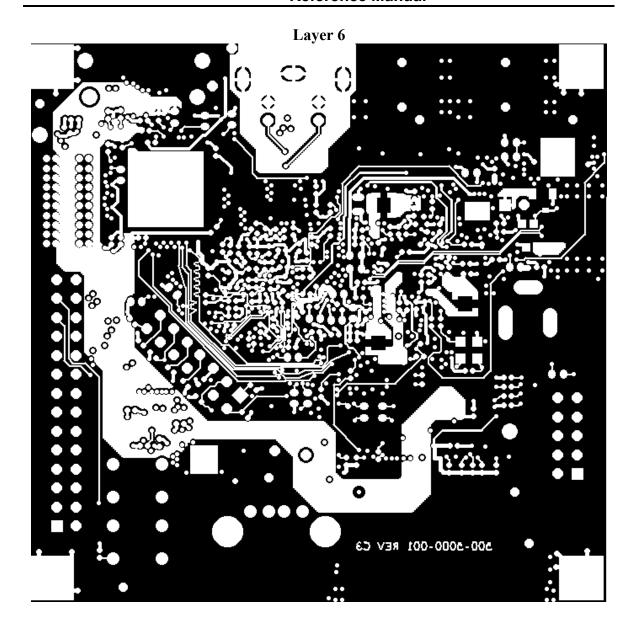

| 15.0   | PCB            | COMPONENT LOCATIONS                    | 157 |

| 16.0   | SCH            | IEMATICS                               | 159 |

| 17.0   | BIL            | LS OF MATERIAL                         | 170 |

| 18.0   | PCB            | INFORMATION                            | 171 |

|        |                |                                        |     |

|        |                |                                        |     |

|        |                | Figures                                |     |

| Figure | 1 <b>د</b>     | BeagleBoard Usage Scenarios            | 16  |

| Figure |                | USB Y-Cable                            |     |

| Figure |                | The Rev C4 Box.                        |     |

| Figure |                | Rev C4 Box Contents                    |     |

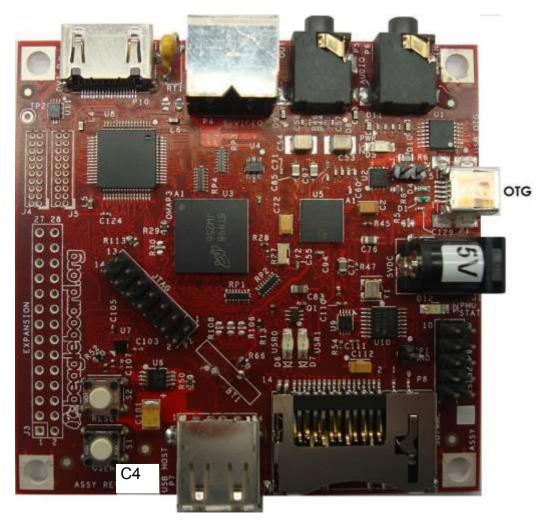

| Figure |                | USB OTG Connection                     |     |

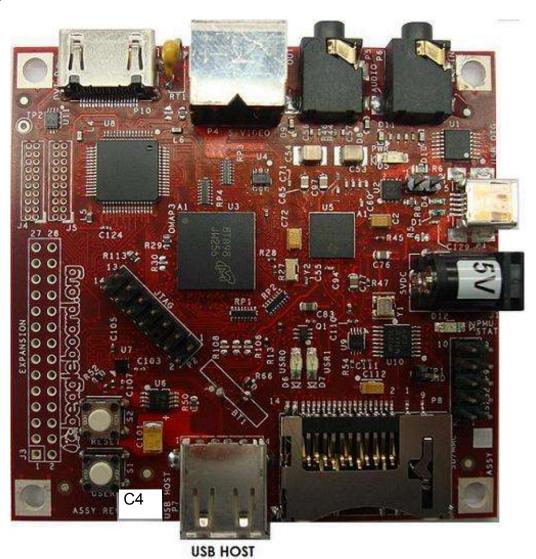

| Figure |                | USB Host Connection                    |     |

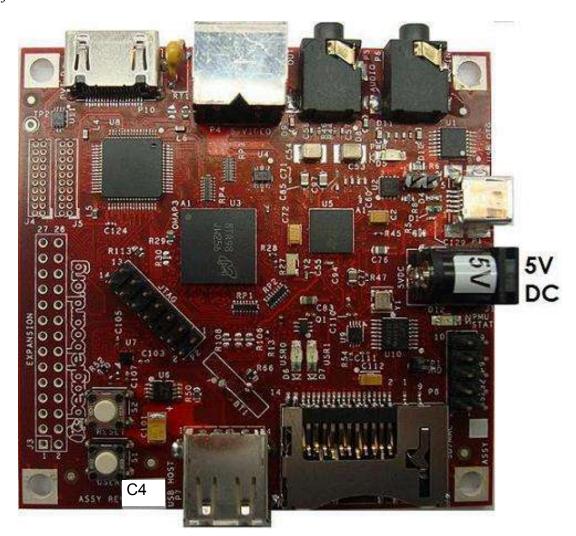

| Figure |                | DC Power Connection                    |     |

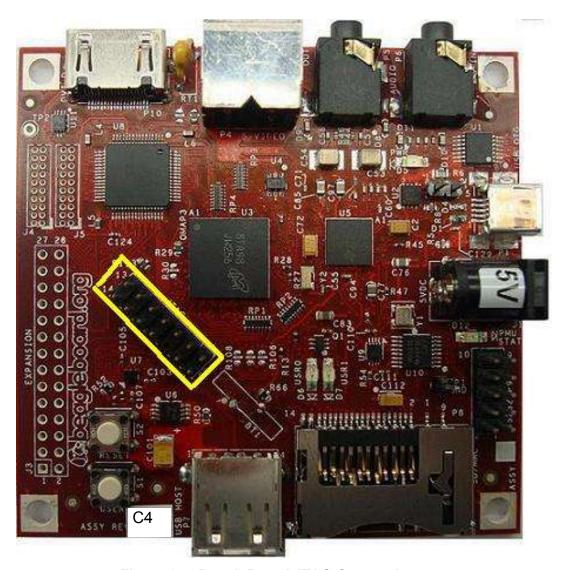

| Figure |                | BeagleBoard JTAG Connection            |     |

| Figure |                | BeagleBoard Serial Cable Connection    |     |

| Figure |                | BeagleBoard S-Video Connection         |     |

| Figure |                | BeagleBoard DVI-D Connection           |     |

| Figure |                | BeagleBoard Audio Out Cable Connection |     |

| Figure |                | BeagleBoard Audio In Cable Connection  |     |

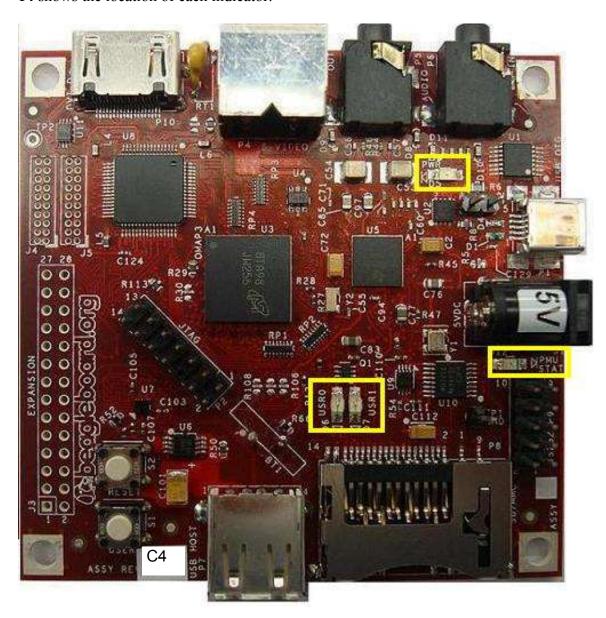

| Figure |                | BeagleBoard Indicator Locations        |     |

| Figure |                | BeagleBoard Button Location.           |     |

| Figure |                | BeagleBoard SD/MMC Location            |     |

| Figure |                | BeagleBoard LCD Header Location        |     |

| Figure |                | BeagleBoard High Level Block Diagram   |     |

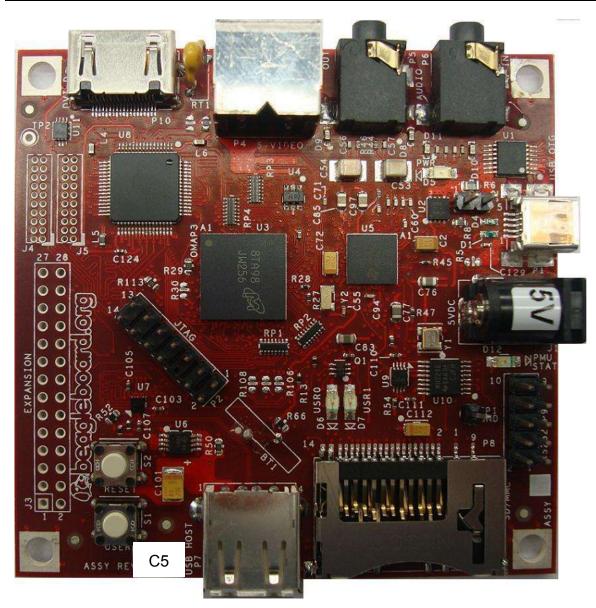

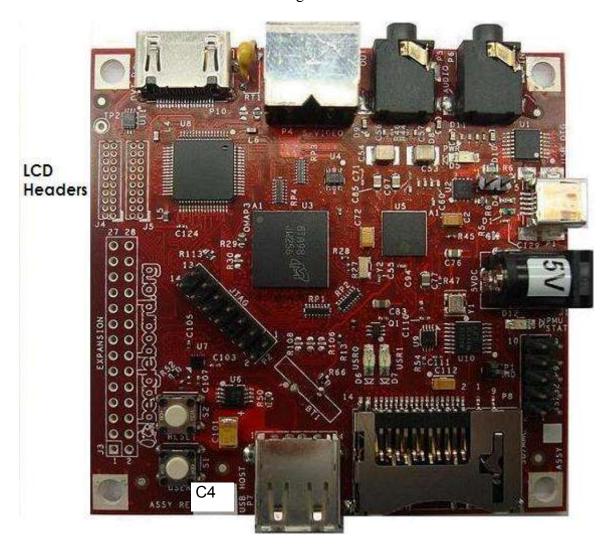

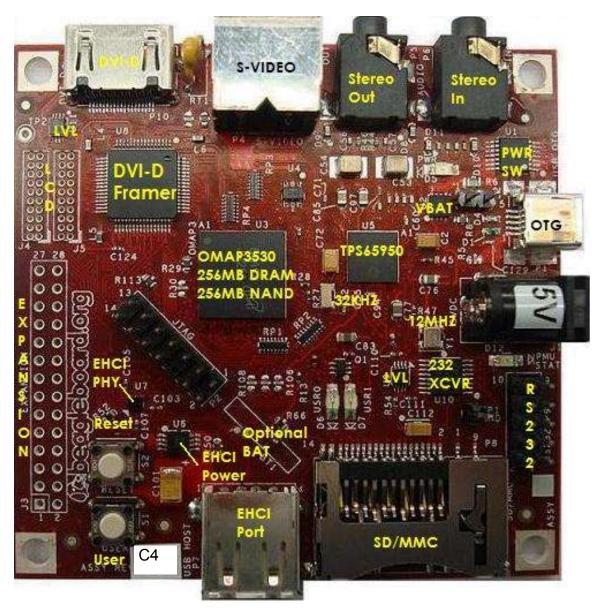

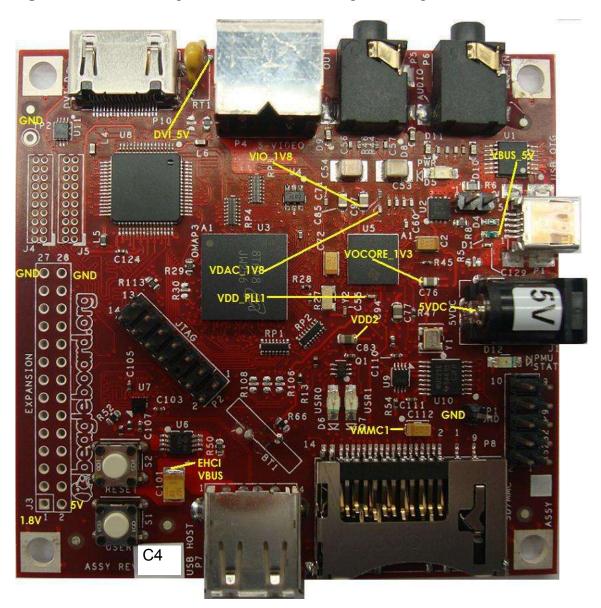

| Figure |                | BeagleBoard Top Side Components        |     |

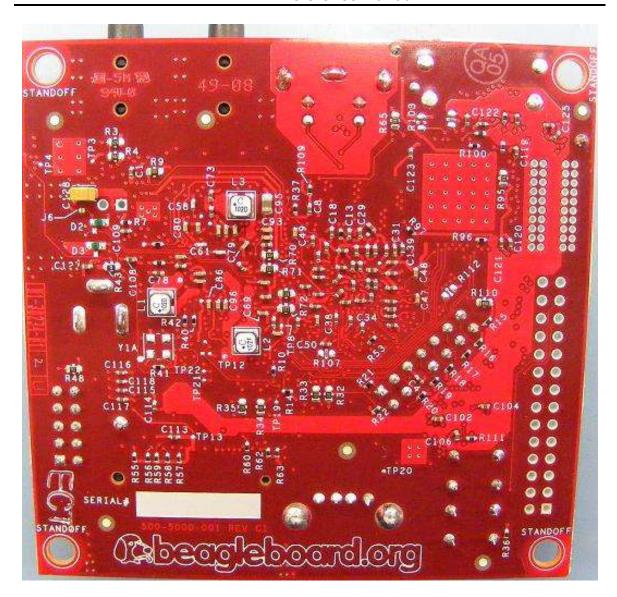

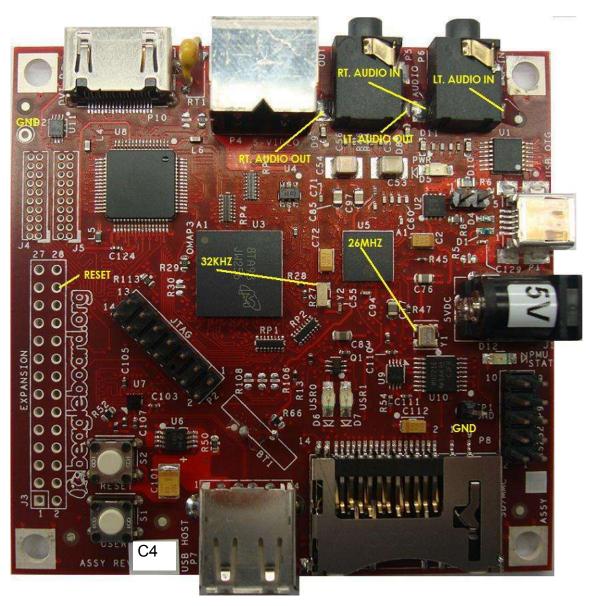

| Figure |                | BeagleBoard Backside Components        |     |

| Figure | e 21.          | Input Power Section                    |     |

| Figure | e 22.          | Processor Current Measurement          |     |

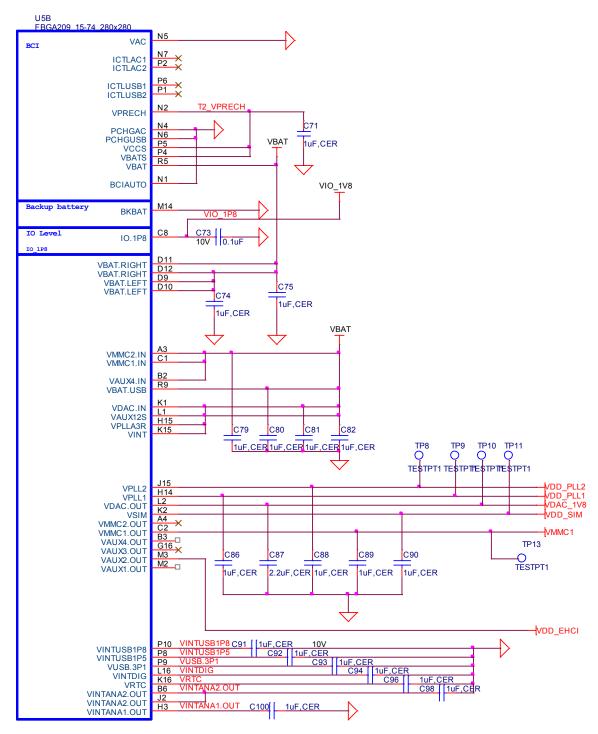

| Figure | e 23.          | Power Conditioning                     | 48  |

| Figure |                | Main Power Rails                       |     |

| Figure |                | Peripheral Voltages                    | 53  |

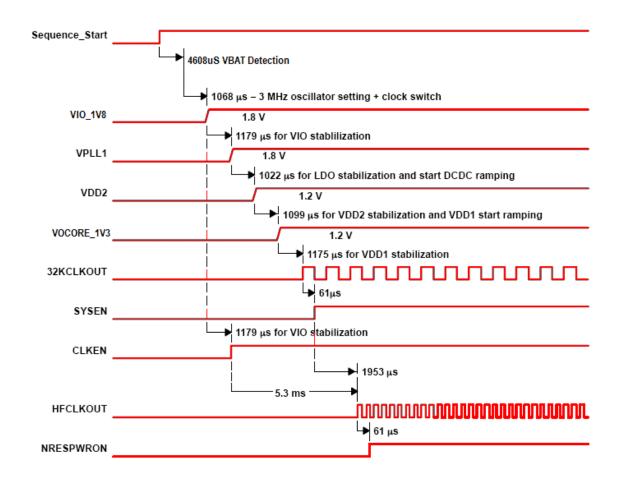

| Figure | e 26.          | Power Sequencing                       | 56  |

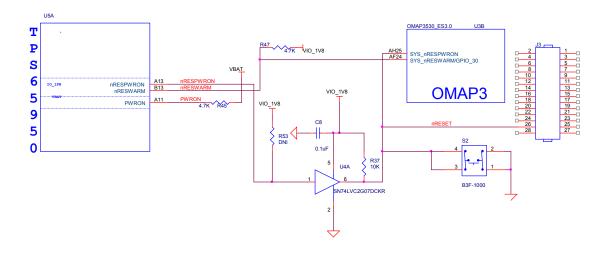

| Figure |                | Reset Circuitry                        | 57  |

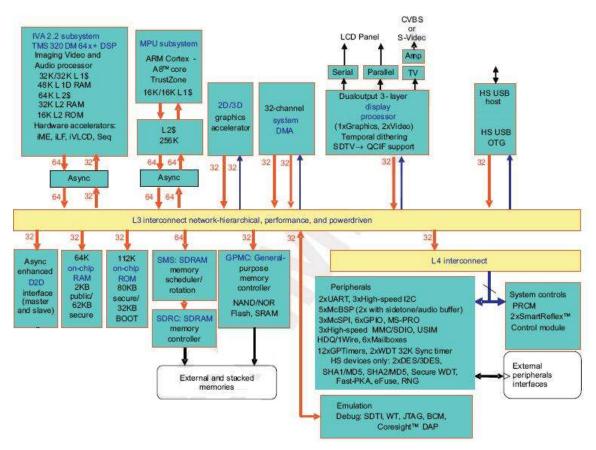

| Figure | e 28.          | OMAP3530 Block Diagram                 | 59  |

| Figure | e 29.          | McBSP2 Interface                       | 61  |

| Figure | 30             | McRSP1 Interface                       | 62  |

# BeagleBoard System Reference Manual

| Figure 31.            | McBSP3 Interface                         | 62 |

|-----------------------|------------------------------------------|----|

| Figure 32.            | POP Memory                               |    |

| Figure 33.            | System Clocks                            |    |

| Figure 34.            | USB OTG Design                           |    |

| Figure 35.            | USB Host Design                          |    |

| Figure 36.            | Example of an SDIO Card                  |    |

| Figure 37.            | RS-MMC and Card                          |    |

| Figure 38.            | SD/MMC Interface                         |    |

| Figure 39.            | Audio Circuitry                          |    |

| Figure 40.            | DVI-D Interface                          |    |

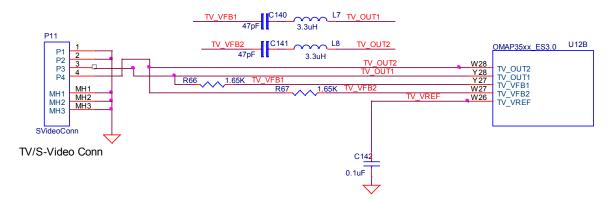

| Figure 41.            | S-Video Interface                        |    |

| Figure 42.            | RS232 Interface Design                   |    |

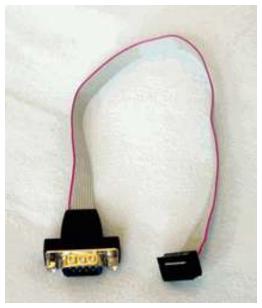

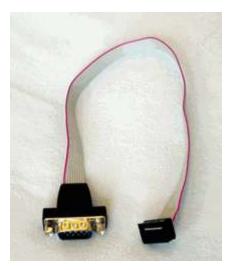

| Figure 43.            | RS232 Cable                              |    |

| Figure 44.            | Indicator Design                         |    |

| Figure 45.            | JTAG Interface                           |    |

| Figure 46.            | Expansion Header                         |    |

| Figure 47.            | Power Connector                          |    |

| Figure 48.            | USB OTG Connector                        |    |

| Figure 49.            | OTG Host Shorting Pads                   |    |

| Figure 50.            | S-Video Connector                        |    |

| Figure 51.            | DVI-D Connector                          |    |

| Figure 51.            | DVI-D Cable                              |    |

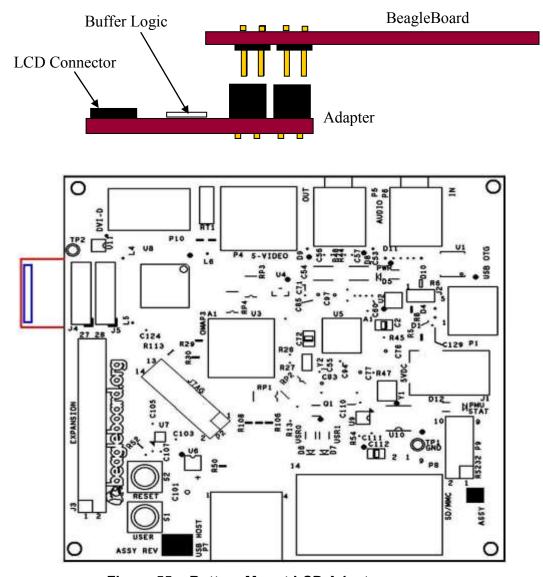

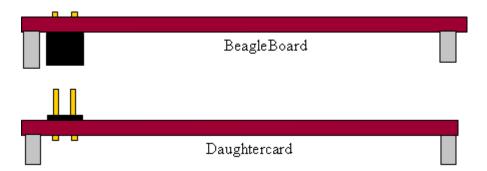

| Figure 52. Figure 53. | Top Mount LCD Adapter                    |    |

| Figure 54.            | Top Mount LCD Adapter                    |    |

| Figure 55.            | Bottom Mount LCD Adapter                 |    |

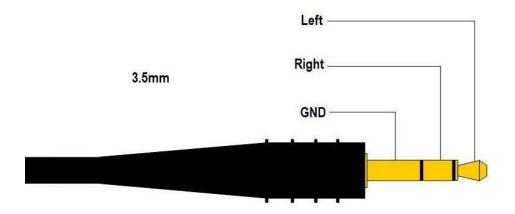

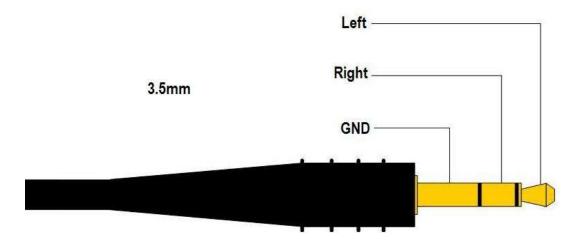

| Figure 56.            | Audio In Plug                            |    |

| Figure 57.            | Audio In Plug                            |    |

| Figure 58.            | Audio Out Plug                           |    |

| Figure 59.            | Audio In Plug                            |    |

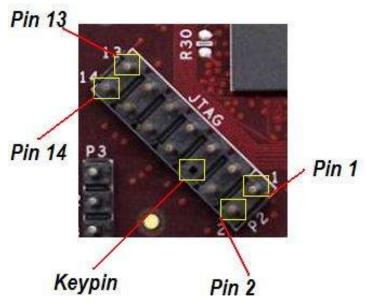

| Figure 60.            | JTAG Connector Pinout                    |    |

| Figure 61.            | JTAG 14 to 20 Pin Adapter                |    |

| Figure 62.            | JTAG Connector Pinout                    |    |

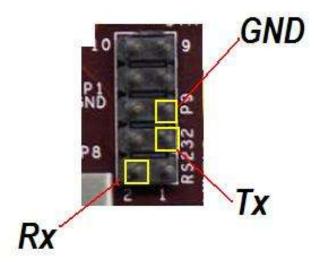

| Figure 63.            | RS232 Header                             |    |

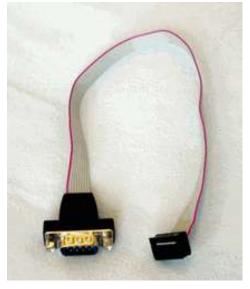

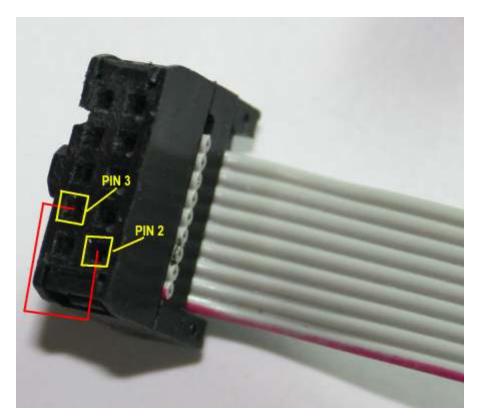

| Figure 64.            | RS232 Flat Cable                         |    |

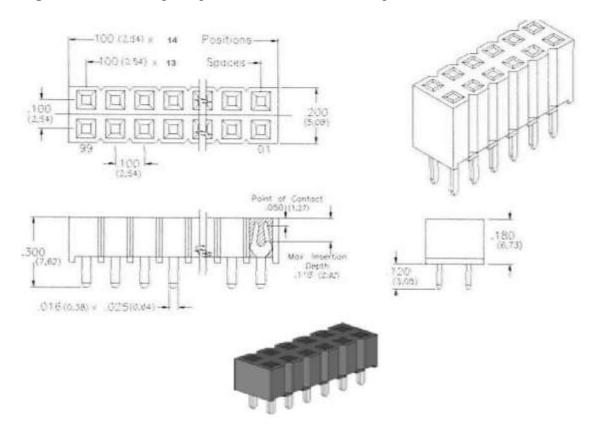

| Figure 65.            | Expansion Sockets                        |    |

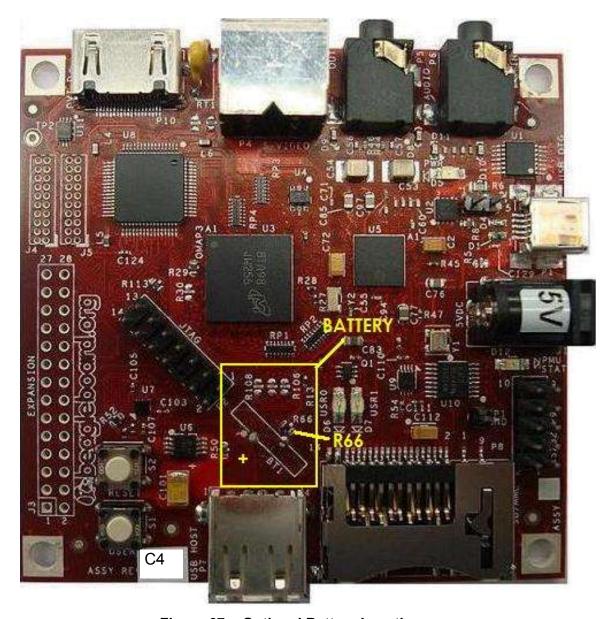

| Figure 66.            | Optional Battery                         |    |

| Figure 67.            | Optional Battery Location.               |    |

| Figure 68.            | DC Power Supply                          |    |

| Figure 69.            | RS232 Cable                              |    |

| Figure 70.            | RS232 Cable Wiring                       |    |

| Figure 71.            | HDMI to DVI-D Cable                      |    |

| Figure 72.            | USB to Ethernet Adapters                 |    |

| Figure 73.            | USB to WiFi                              |    |

| Figure 74.            | USB to Bluetooth                         |    |

| Figure 75.            | BeagleBoard Dimension Drawing            |    |

| Figure 76             | BeagleBoard Bottom Stacked Daughter Card |    |

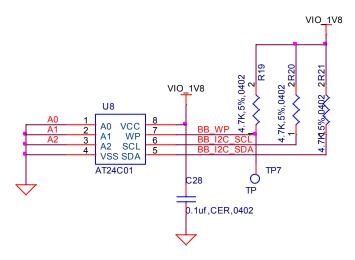

| Figure 77. | BeagleBoard Expansion Board EEPROM Schematic | 128 |

|------------|----------------------------------------------|-----|

| Figure 78. | BeagleBoard Voltage Access Points            |     |

| Figure 79. | BeagleBoard Signal Access Points             |     |

| Figure 80. | BeagleBoard Serial Cable Orientation         |     |

| Figure 81. | DB9 Male Connector                           |     |

| Figure 82. | DB9 Null Modem Cable                         | 153 |

| Figure 83. | Serial Cable Loopback                        |     |

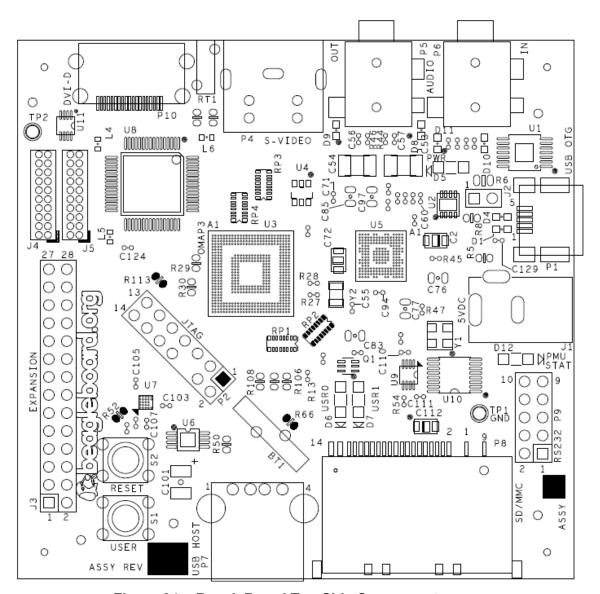

| Figure 84. | BeagleBoard Top Side Components              |     |

| Figure 85. | BeagleBoard Bottom Side Components           |     |

| _          |                                              |     |

|            | Tables                                       |     |

| Table 1.   | Change History                               | 14  |

| Table 2.   | BeagleBoard Features                         | 17  |

| Table 3.   | BeagleBoard Electrical Specification Rev C4  | 24  |

| Table 4.   | OMAP3530 Pin Muxing Settings                 | 63  |

| Table 5.   | OMAP3530 GPIO Pins                           | 64  |

| Table 6.   | OMAP3530 Interrupt Pins                      | 64  |

| Table 7.   | OMAP3530 ULPI Interface                      | 69  |

| Table 8.   | OMAP3530 ULPI Interface                      | 69  |

| Table 9.   | USB OTG Charge Pump Pins                     | 70  |

| Table 10.  | USB Host Port OMAP Signals                   |     |

| Table 11.  | SD/MMC OMAP Signals                          | 78  |

| Table 12.  | OMAP3530 Audio Signals                       |     |

| Table 13.  | OMAP3530 Audio Signals                       |     |

| Table 14.  | OMAP3530 LCD Signals                         | 82  |

| Table 15.  | TFP410 Interface Signals                     | 83  |

| Table 16.  | J4 LCD Signals                               |     |

| Table 17.  | J5 LCD Signals                               |     |

| Table 18.  | S-Video Interface Signals                    |     |

| Table 19.  | JTAG Signals                                 |     |

| Table 20.  | Expansion Connector Signals                  |     |

| Table 21.  | Expansion Connector Signal Groups            |     |

| Table 22.  | J4 GPIO Signals                              |     |

| Table 23.  | J5 GPIO Signals                              |     |

| Table 24.  | DVI-D to HDMI Cable                          |     |

| Table 25.  | J4 LCD Signals                               |     |

| Table 26.  | J5 LCD Signals                               |     |

| Table 27.  | J4 and J5 Connector Sources                  |     |

| Table 28.  | Connector Dimensions                         |     |

| Table 29.  | JTAG Signals                                 |     |

| Table 30.  | DC Power Supply Specifications               |     |

| Table 31.  | DC Power Supplies                            |     |

| Table 32.  | Cable Pinout                                 |     |

| Table 33.  | USB Hubs Tested                              |     |

| Table 34.  | DVI-D Monitors Tested                        | 122 |

# REF: BB\_SRM BeagleBoard System Reference Manual

# **Revision D**

| Table 35. | SD/MMC Cards Tested       | 122 |

|-----------|---------------------------|-----|

| Table 36. | USB to Ethernet Adapters  | 123 |

|           | USB to WiFi Adapters      |     |

|           | USB to Bluetooth Adapters |     |

| Table 39. | Voltages                  | 149 |

| Table 40. | Troubleshooting           | 151 |

| Table 41  | Known Issues              | 156 |

#### 1.0 Introduction

This document is the System Reference Manual for the BeagleBoard, a low cost OMAP3530 based board supported through <u>BeagleBoard.org</u>. This document provides detailed information on the overall design and usage of the BeagleBoard from the system level perspective. It is not intended to provide detailed documentation of the OMAP3530 processor or any other component used on the board. It is expected that the user will refer to the appropriate documents for these devices to access detailed information.

The key sections in this document are:

#### **Section 2.0– Change History**

Provides tracking for the changes made to the System Reference Manual.

#### **Section 3.0– Definitions and References**

This section provides definitions for commonly used terms and acronyms.

#### **Section 4.0– Overview**

This is a high level overview of the BeagleBoard.

#### **Section 5.0– Specification**

Provided here are the features and electrical specifications of the BeagleBoard.

#### **Section 6.0-Product Contents**

Describes what the BeagleBoard package looks like and what is included in the box.

#### **Section 7.0– Hookup**

Covered here is how to connect the various cables to the BeagleBoard.

#### **Section 8.0– System Architecture and Design**

This section provides information on the overall architecture and design of the BeagleBoard. This is a very detailed section that goes into the design of each circuit on the board.

#### **Section 9.0– Connector Pinouts and Cables**

The section describes each connector and cable used in the system. This will allow the user to create cables, purchase cables, or to perform debugging as needed.

#### Section 10.0- BeagleBoard Accessories

Covered in this section are a few of the accessories that may be used with BeagleBoard. This is not an exhaustive list, but does provide an idea of the types of cables and accessories that can be supported and how to find them. It also provides a definition of what they need to be. It does not guarantee that these devices will work on all OS implementations.

#### Section 11.0 - Mechanical

Information is provided here on the dimensions of the BeagleBoard.

#### **Section 12.0 – Board Verification**

A description is provided on how to setup the board and using the verification process and SW to verify that the board is functional.

#### **Section 13.0 – Troubleshooting**

Here is where you can find tips on troubleshooting the setup of the BeagleBoard.

#### **Section 14.0- Known Issues**

This section describes the known issues with the current revision of the BeagleBoard and any workarounds that may be possible.

#### **Section 15.0- BeagleBoard Components**

This section provides information on the top and bottom side silkscreen of the BeagleBoard showing the location of the components.

#### Section 16.0- BeagleBoard Schematics

These are the schematics for the BeagleBoard and information on where to get the PDF and OrCAD files..

#### Section 17.0- Bill Of Material

This section describes where to get the latest Bill of Material for the BeagleBoard.

#### Section 18.0- BeagleBoard PCB Information

This section describes where to get the PCB file information for the BeagleBoard.

### 2.0 Change History

#### 2.1 Change History

**Table 1** tracks the changes made for each revision of this document.

Rev By Changes Date C4 Initial release. 12/15/2009 GC GC C4.1 Typos and miscellaneous corrections. 7/29/2010 Updated resistor values in section 8.2.6 to reflect schematic and BOM values. GC C4.2 11/25/2010 1. Updated Tables 20 and 21 GC C5 2. Updated to rev C5 to cover new Memory device used due to 7/15/2011 obsolescence of previous version. D Updated processor to a new revision. No expected impact on operation. 10/11/2012

Table 1. Change History

#### 2.2 Revision C3 vs. C4

There are three key changes on the Rev C4 board versus the Rev C3 version.

- Use of the OMAP3530DCBB72 device which is the 720MHZ version of the OMAP3530.

- An updated version of the UBoot software. The following changes will affect the user experience:

- o The Beagle splash screen has been replaced with an orange only screen at boot up.

- o Turning on VAUX2 for the EHCI fix

- A more advanced fix for the EHCI noise issue on Rev C3 board. This involves a change in the power circuitry for the 1.8V rail supplied to the EHCI PHY interface. The power is now derived from the VAUX2 on the TPS65950 through a filter circuit.

#### 2.3 Revision C4 vs. C5

- The memory device is no longer offered by Micron. This required a move to upgrade to the replacement part. This resulted in a doubling of the NAND flash memory from 2Gb (256MB) to 4Gb (512MB). The LPDDR memory size remains the same.

- o In order to support the new NAND size, a newer image is loaded onto the flash on the C5 version.

#### 2.4 Revision C5 vs. D

Processor revision was changed from OMAP3530DCBB72 which has been obsoleted to OMAP3530ECBB72. There is no expected impact on operation of the board. Refer to <a href="http://www.ti.com/product/omap3530">http://www.ti.com/product/omap3530</a> for more information.

#### 3.0 Definitions and References

#### 3.1 Definitions

**SD-** Secure Digital

**SDIO-** Secure Digital Input Output

MMC- Multimedia Card

MDDR- Mobile Dual Data Rate

**SDRAM-** Synchronous Dual Access Memory

**OMAP3530**- The CortexA8 based System on a Chip from Texas Instruments.

# 4.0 BeagleBoard Overview

The BeagleBoard is an OMAP3530 platform designed specifically to address the Open Source Community. It has been equipped with a minimum set of features to allow the user to experience the power of the OMAP3530 and is not intended as a full development platform as many of the features and interfaces supplied by the OMAP3530 are not accessible from the BeagleBoard. By utilizing standard interfaces, the BeagleBoard is highly extensible to add many features and interfaces. It is not intended for use in end products. All of the design information is freely available and can be used as the basis for a product. BeagleBoards will not be sold for use in any product as this hampers the

ability to get the boards to as many community members as possible and to grow the community.

# 4.1 BeagleBoard Usage Scenarios

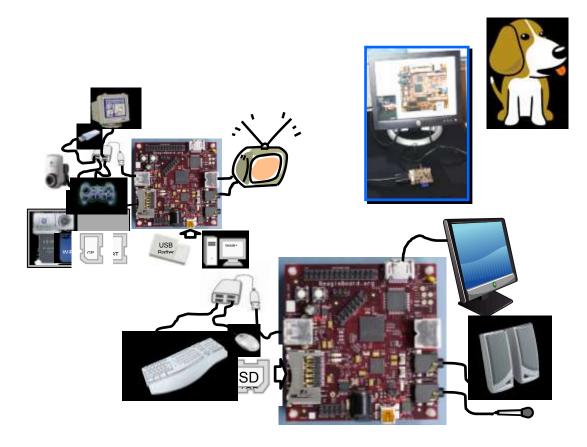

The **Figure 1** provides an example of a few of the various usage scenarios for the BeagleBoard.

Figure 1. BeagleBoard Usage Scenarios

# 5.0 BeagleBoard Specification

This section covers the specifications of the BeagleBoard and provides a high level description of the major components and interfaces that make up the BeagleBoard.

#### 5.1 BeagleBoard Features

Table 2 provides a list of the BeagleBoard's features.

Table 2. BeagleBoard Features

|                         | Feature                                 |                               |  |  |  |

|-------------------------|-----------------------------------------|-------------------------------|--|--|--|

| Processor               | OMAP3530DCBB72 720MHz                   |                               |  |  |  |

|                         | Micron                                  |                               |  |  |  |

| POP Memory              | 2Gb NAND (256MB)                        | 2Gb MDDR SDRAM (256MB)        |  |  |  |

|                         | 4Gb C5                                  |                               |  |  |  |

|                         |                                         | Regulators                    |  |  |  |

| PMIC TPS65950           | Audio                                   | CODEC                         |  |  |  |

| 1 MIC 11 503/30         |                                         | eset                          |  |  |  |

|                         | USB C                                   | OTG PHY                       |  |  |  |

| Debug Support           | 14-pin JTAG                             | GPIO Pins                     |  |  |  |

| Denug Support           | UART                                    | LEDs                          |  |  |  |

| PCB                     | 3.1" x 3.0" (78.74 x 76.2mm)            | 6 layers                      |  |  |  |

| Indicators              | Power                                   | 2-User Controllable           |  |  |  |

| indicators              | PMU                                     |                               |  |  |  |

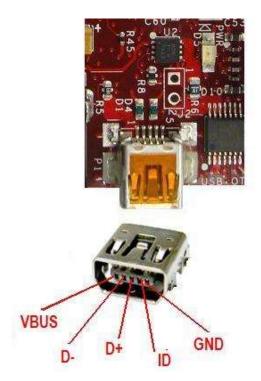

| HS USB 2.0 OTG          | Mini AB USB connector                   |                               |  |  |  |

| Port                    | TPS65950 I/F                            |                               |  |  |  |

| 1011                    | MiniAB                                  |                               |  |  |  |

| <b>HS USB Host Port</b> | Single USB HS Port                      | Up to 500ma Power             |  |  |  |

| Audio Connectors        | 3.5mm                                   | 3.5mm                         |  |  |  |

| Audio Connectors        | L+R out                                 | L+R Stereo In                 |  |  |  |

| <b>SD/MMC Connector</b> | 6 in 1 SD/MMC/SDIO                      | 4/8 bit support, Dual voltage |  |  |  |

| <b>User Interface</b>   | 1-User defined button                   | Reset Button                  |  |  |  |

| Video                   | DVI-D                                   | S-Video                       |  |  |  |

| Power Connector         | USB Power                               | DC Power                      |  |  |  |

| E                       | Power (5V & 1.8V)                       | UART                          |  |  |  |

| Expansion<br>Connector  | McBSP                                   | McSPI                         |  |  |  |

|                         | I2C                                     | GPIO                          |  |  |  |

| (Not Populated)         | MMC                                     | PWM                           |  |  |  |

| 2 LCD Connectors        | Access to all of the LCD                | 2 2 7 5 7 1 0 7               |  |  |  |

|                         | control signals plus I2C 3.3V, 5V, 1.8V |                               |  |  |  |

The following sections provide more detail on each feature and sections of the BeagleBoard.

#### 5.2 OMAP Processor

The BeagleBoard uses the OMAP3530DCBB72 720MHZ version and comes in a .4mm pitch POP package. POP (Package on Package) is a technique where the memory, NAND and SDRAM, are mounted on top of the OMAP3530. For this reason, when looking at the BeagleBoard, you will not find an actual part labeled OMAP3530.

#### 5.3 Memory

The Micron POP memory is used on the Rev C4 BeagleBoard and is mounted on top of the processor as mentioned. The key function of the POP memory is to provide:

- o 2Gb NAND x 16 (256MB)

- o 2Gb MDDR SDRAM x32 (256MB @ 166MHz)

No other memory devices are on the BeagleBoard. It is possible however, that additional memory can be added to BeagleBoard by:

- o Installing a SD or MMC in the SD/MMC slot

- Use the USB OTG port and a powered USB hub to drive a USB Thumb drive or hard drive.

- o Install a thumbdrive into the EHCI USB port

Support for this is dependent upon driver support in the OS.

#### 5.4 Power Management

The TPS65950 is used on the Rev C4 to provide power to the BeagleBoard with the exception of the 3.3V regulator which is used to provide power to the DVI-D encoder and RS232 driver. In addition to the power the TPS65950 also provides:

- Stereo Audio Out

- Stereo Audio in

- o Power on reset

- o USB OTG PHY

- Status LED

#### 5.5 HS USB 2.0 OTG Port

The USB OTG port can be used as the primary power source and communication link for the BeagleBoard and derives power from the PC over the USB cable. The client port is limited in most cases to 500mA by the PC. A single PC USB port is sufficient to power the BeagleBoard. If additional devices are connected to the expansion bus and the 5V rail is used to power them or if a high powered USB device is connected to the EHCI port, then the power required could exceed that supplied by a USB port or Hub.

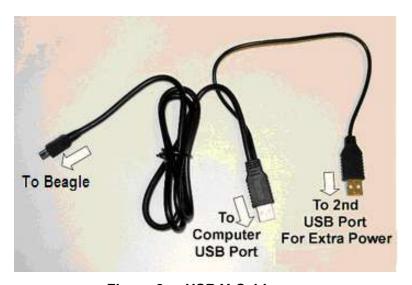

It is possible to take this to 1A by using a Y cable if additional power is needed for either the USB host port or an expansion card. **Figure 2** shows and example of the Y-Cable for the USB.

Figure 2. USB Y-Cable

The BeagleBoard requires a single minAB to USB A cable or as mentioned a Y-Cable can be used if needed.

There is an option to provide external power to the BeagleBoard using a 5V DC supply and is discussed later in this section.

#### 5.6 HS USB 2.0 Host Port

On the Rev C4 board a single USB HS only Host port is provided via a USB Type A connector. It provides power on/off control and up to 500mA of current at 5V.

The HS USB Port is HS only. In order to support a FS/LS device, a HUB must be used.

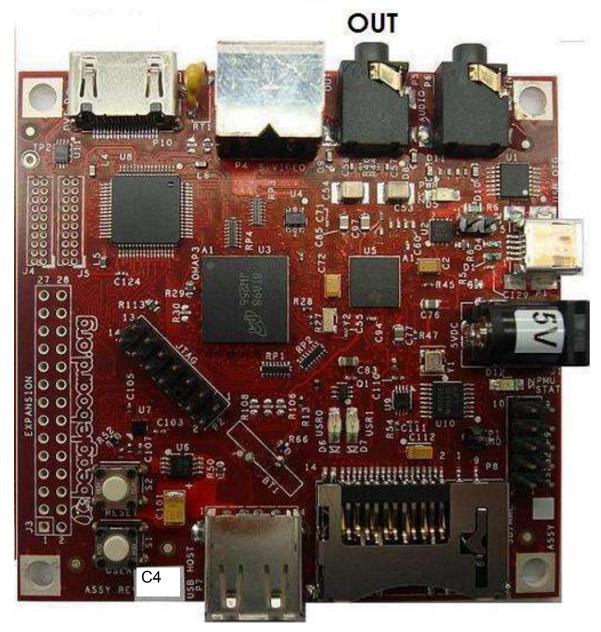

#### 5.7 Stereo Audio Output Connector

A 3.5mm standard stereo output audio jack is provided to access the stereo output of the onboard audio CODEC. The Audio CODEC is provided by the TPS65950.

#### 5.8 Stereo Audio In Connector

A 3.5mm standard stereo audio input jack is provided to access the stereo output of the onboard audio CODEC.

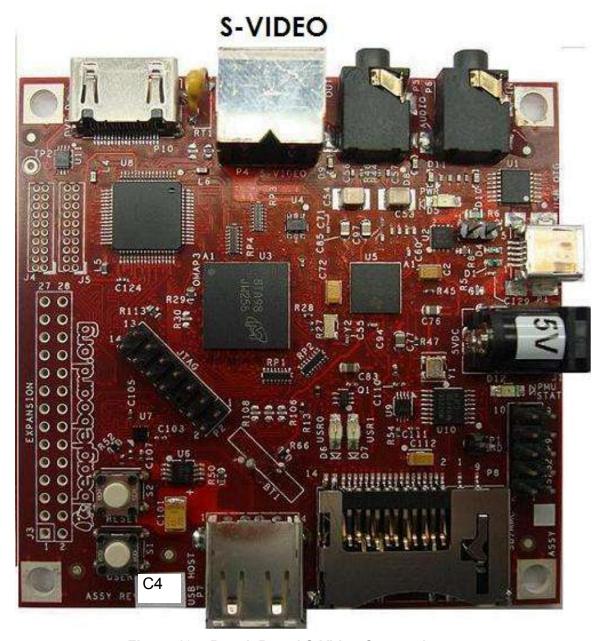

#### 5.9 S-Video Connector

A 4 pin DIN connector is provided to access the S-Video output of the BeagleBoard. This is a separate output from the OMAP processor and can contain different video output data from what is found on the DVI-D output if the software is configured to do it.

It will support NTSC or PAL format output to a standard TV. The default is NTSC, but can be changed via the Software.

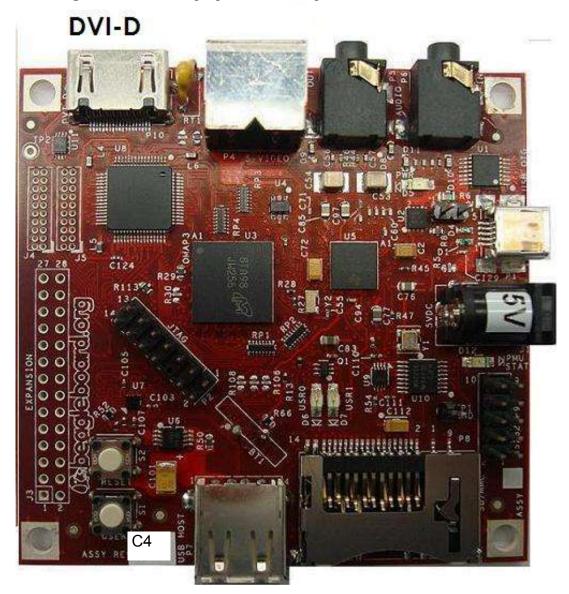

#### 5.10 DVI-D Connector

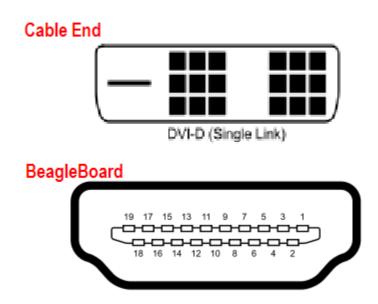

The BeagleBoard can drive a LCD panel equipped with a DVI-D digital input. This is the standard LCD panel interface of the OMAP3530 and will support 24b color output. DDC2B (Display Data Channel) or EDID (Enhanced Display ID) support over I2C is provided in order to allow for the identification of the LCD monitor type and the required settings.

The BeagleBoard is equipped with a DVI-D interface that uses an HDMI connector that was selected for its small size. It does not support the full HDMI interface and is used to provide the DVI-D interface portion only. The user must use a HDMI to DVI-D cable or adapter to connect to a LCD monitor. This cable or adapter is not provided with the BeagleBoard. A standard HDMI cable can be used when connecting to a monitor with an HDMI connector.

DO NOT PLUG IN THE DVI-D CONNECTOR TO A DISPLAY WITH THE BEAGLEBAORD POWERED ON. PLUG IN THE CABLE TO THE DISPLAY AND THEN POWER ON THE BEAGLEBOARD.

#### 5.11 LCD Header

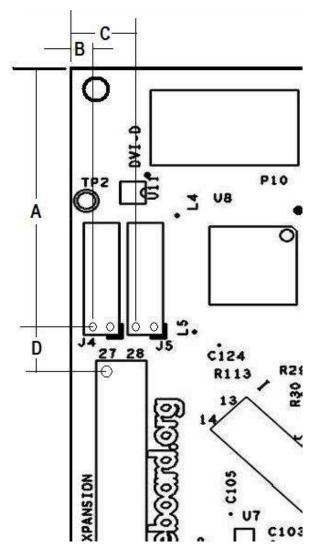

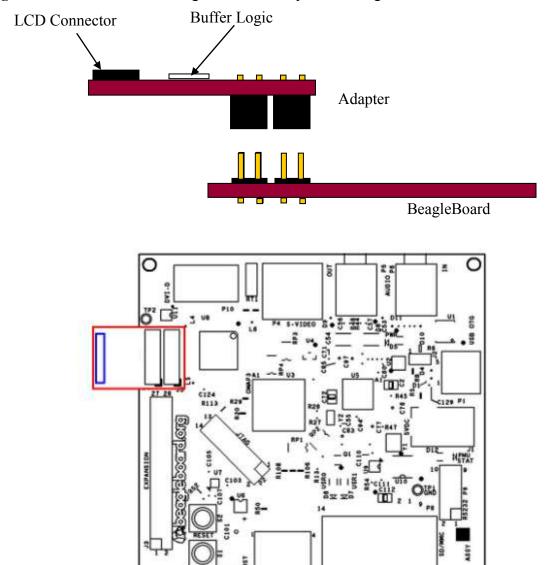

A pair of 1.27mm pitch 2x10 headers are provided to gain access to the LCD signals. This allows for the creation of LCD boards that will allow adapters to be made to provide the level translation to support different LCD panels.

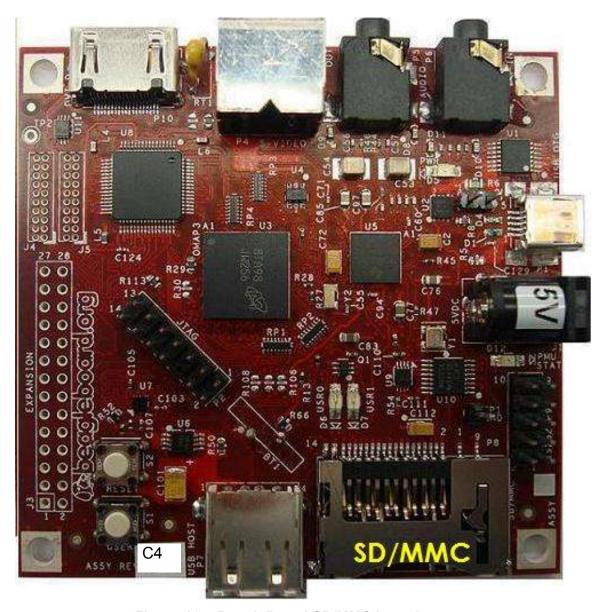

#### 5.12 SD/MMC 6 in 1 Connector

A 6 in 1 SD/MMC connector is provided as a means for expansion and can support such devices as:

- WiFi Cards

- o Camera

- o Bluetooth Cards

- o GPS Modules

- o SD Memory Cards

- o MMC Memory Cards

- o SDIO Cards

- MMCMobile cards

- o RS-MMC Cards

- o miniSD Cards

It supports the MMC4.0 (MMC+) standard and can boot from MMC or SD cards. It will support both 4 and 8 bit cards. It will also support most SDHC cards as well.

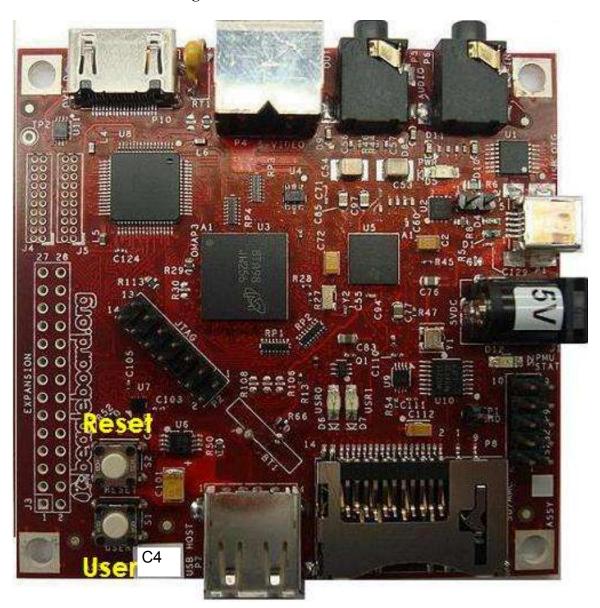

#### 5.13 Reset Button

When pressed and released, causes a power on reset of the BeagleBoard.

#### 5.14 User/Boot Button

A button is provided on the BeagleBoard to provide two functions:

- Force a change in the boot sequence of the OMAP3530.

- Used as an application button that can be used by SW as needed.

When used in conjunction with the RESET button, it will force a change to the order in which boot sources are checked as viable boot sources.

If the button is pressed while the RESET button is released, the sequence becomes:

- o USB

- o UART

- o MMC1

- o NAND

Even though the NAND may have a program in it, if a card is placed in the MMC slot, it will try to boot from it first. If it is not there, it will boot from NAND.

There is also the option to have a serial download application that will program the NAND if connected to the serial or USB ports. In this scenario the internal ROM will

stop on either the serial or USB port and start the download process from there. It does require an application to be run on the host PC in order to perform this function.

If the user button is not pressed at reset, the sequence in which the internal ROM looks for viable boot sources is as follows:

- o NAND

- o USB

- o UART3

- o MMC1

In this case, NAND overrides every option and will always boot from NAND if there is data in the NAND. If the NAND is empty, then the other sources are available to be used based on the boot order.

To force a boot from the SD/MMC card, the reset button must be pushed and the reset button pushed and reelased.

#### 5.15 Indicators

There are three green LEDs on the BeagleBoard that can be controlled by the user.

- o One on the TPS65950 that is programmed via the I2C interface

- o Two on the OMAP3530 Processor controlled via GPIO pins

There is a fourth LED on the BeagleBoard that provides an indication that power is supplied to the board and is not controlled via software.

#### 5.16 Power Connector

Power will be supplied via the USB OTG connector and if a need arises for additional power, such as when a board is added to the expansion connectors, a larger wall supply 5V can be plugged into the optional power jack. When the wall supply is plugged in, it will remove the power path from the USB connector and will be the power source for the whole board. The power supply is not provided with the BeagleBoard.

When using the USB OTG port in the host mode, the DC supply must be connected as the USB port will be used to provide limited power to the hub at a maximum of 100mA, so a hub must be powered. The 100mA is not impacted by having a higher amperage supply plugged into the DC power jack. The 100mA is a function of the OTG port itself.

WARNING: DO NOT PLUG IN ANYTHING BUT 5V TO THE DC CONNECTOR OR THE BOARD WILL BE DAMAGED!

Make sure the DC supply is regulated and a clean supply.

#### 5.17 JTAG Connector

A 14 pin JTAG header is provided on the BeagleBoard to facilitate the SW development and debugging of the board by using various JTAG emulators. The interface is at 1.8V on all signals. Only 1.8V Levels are supported. **DO NOT expose the JTAG header to 3.3V.**

#### **5.18** RS232 Header

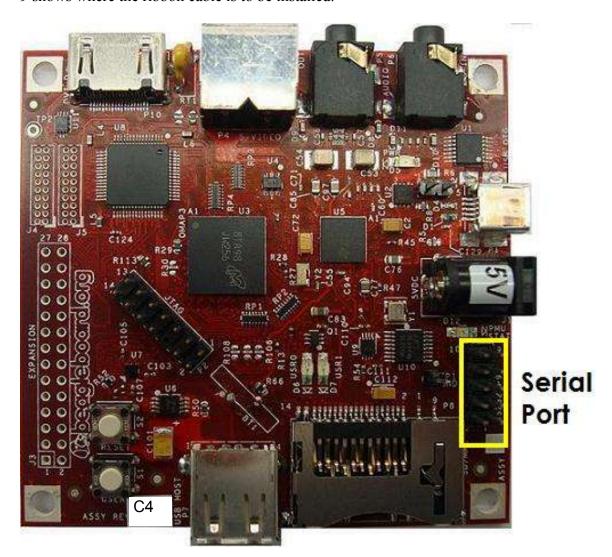

Support for RS232 via UART3 is provided by a 10 pin header on the BeagleBoard for access to an onboard RS232 transceiver. It does require an IDC to DB9 flat cable, which is not provided, to access the serial port.

#### 5.19 Expansion Header

An option for a single 28 pin header is provided on the board to allow for the connection of various expansion cards that could be developed by the users or other sources. Due to multiplexing, different signals can be provided on each pin. This header is not populated on the BeagleBoard so that based on the usage scenario it can be populated as needed.

#### 5.20 BeagleBoard Mechanical Specifications

Size: 3.0" x 3.1"

Max height: TBM

Layers: 6

PCB thickness: .062"

RoHS Compliant: Yes

Weight: TBW

# **5.21** Electrical Specifications

**Table 3** is the electrical specification of the external interfaces to the Rev C4 BeagleBoard.

Table 3. BeagleBoard Electrical Specification Rev C4

| Specification                                                  | Min  | Тур    | Max   | Unit   |  |  |

|----------------------------------------------------------------|------|--------|-------|--------|--|--|

| Power                                                          |      |        |       |        |  |  |

| Input Voltage USB 5 5.2 V                                      |      |        |       |        |  |  |

| Current USB                                                    |      | 350    |       | mA     |  |  |

| Input Voltage DC                                               | 4.8  | 5      | 5.2   | V      |  |  |

| Current DC                                                     |      | 350    |       | mA     |  |  |

| Expansion Voltage (5V)                                         | 4.8  | 5      | 5.2   | V      |  |  |

| Current (Depends on source current available)                  |      | 1      |       | A      |  |  |

| Expansion Voltage (1.8V)                                       | 1.75 | 1.8    | 1.85  | V      |  |  |

| Current                                                        |      |        | 30    | mA     |  |  |

| USB Host (Same as the DC supplied by the power plug or USB 5V) | 4.8  | 5      | 5.2   | V      |  |  |

| Current (Depends on what the DC source can supply over         |      | Varies |       |        |  |  |

| what the board requires)                                       |      |        |       |        |  |  |

| USB OTG                                                        |      |        |       |        |  |  |

| High Speed Mode                                                |      |        | 480   | Mb/S   |  |  |

| Full Speed Mode                                                |      |        | 12.5  | Mb/S   |  |  |

| Low Speed Mode                                                 |      |        | 1.5   | Mb/S   |  |  |

| USB Host                                                       |      |        |       |        |  |  |

| High Speed Mode                                                |      |        | 480   | Mb/S   |  |  |

| RS232                                                          |      |        |       |        |  |  |

| Transmit                                                       |      |        |       |        |  |  |

| High Level Output Voltage                                      |      | 5      | 5.4   | V      |  |  |

| Low Level output voltage                                       |      | -5     | -5.5  | V      |  |  |

| Output impedance                                               |      | +/-35  | +/-60 | mA     |  |  |

| Maximum data rate                                              | 250  |        |       | Kbit/S |  |  |

| Receive                                                        |      |        |       |        |  |  |