# **KS10 FPGA Processor Manual**

Revision 47

Copyright 2012-2021 Rob Doyle

All rights reserved.

doyle (at) cox (dot) net

#### **Table of Contents**

| 1        | Introduction                                                 |    |

|----------|--------------------------------------------------------------|----|

| 1.1      | The DEC KS10                                                 |    |

| 1.2      | The KS10 FPGA                                                |    |

| 2        | The KS10 FPGA Architecture                                   |    |

| 2.1      | The KS10 FPGA Design Hierarchy                               |    |

| 2.2      | The KS10 FPGA Design Description                             | 17 |

| 2.2.1    | KS10 Bus Arbiter (ARB)                                       | 17 |

| 2.2.2    | KS10 Console Interface (CSL)                                 |    |

| 2.2.3    | KS10 Central Processing Unit (CPU)                           | 17 |

| 2.2.3.1  | KS10 CPU Interval Timer (TIMER)                              |    |

| 2.2.3.2  | KS10 CPU Virtual Memory Address (VMA)                        | 20 |

| 2.2.3.3  | KS10 CPU Priority Interrupt Controller (PI)                  |    |

| 2.2.3.4  | KS10 CPU DBM Mux (DBM)                                       |    |

| 2.2.3.5  | KS10 CPU Backplane Interface (BUS)                           |    |

| 2.2.3.6  | KS10 CPU Arithmetic Processor Flags (APR)                    |    |

| 2.2.3.7  | KS10 CPU Arithmetic Logic Unit (ALU)                         |    |

| 2.2.3.8  | KS10 CPU Microsequencer (USEQ)                               |    |

| 2.2.3.9  | KS10 CPU DBUS                                                |    |

| 2.2.3.10 | KS10 CPU Instruction Register (IR)                           |    |

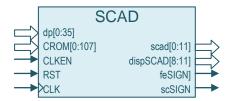

| 2.2.3.11 | KS10 CPU Step Count Adder (SCAD)                             | 33 |

| 2.2.3.11 | KS10 CPU RAMFILE                                             |    |

| 2.2.3.12 | KS10 CPU Pager (PAGER)                                       |    |

| 2.2.3.14 | KS10 CPU Page Fault Dispatch (PF_DISP)                       |    |

| 2.2.3.15 | KS10 CPU Next Instruction Dispatch (NI_DISP)                 |    |

| 2.2.3.16 | KS10 CPU Previous Context (PXCT)                             |    |

| 2.2.4    | KS10 GF0 Frevious Context (FXC1)KS10 Memory Controller (MEM) |    |

| 2.2.5    | KS10 IO Bus Adapter (UBA)                                    |    |

| 3        | KS10 FPGA Backplane                                          |    |

| 3.1      | KS10 FPGA Address Bus                                        |    |

| 3.2      | KS10 FPGA Bus Cycles                                         |    |

| 3.2.1    | •                                                            |    |

| 3.2.1    | KS10 FPGA Interrupt Sequence                                 |    |

| -        | APR / Timer Interrupt                                        |    |

| 3.2.3    | KS10 FPGA External Interrupt                                 |    |

| 4        | Console Processor                                            |    |

| 4.1      | Booting the KS10 FPGA                                        |    |

| 4.2      | KS10 FPGA Console Commands                                   |    |

| 5        | KS10 FPGA Console Interface                                  |    |

| 5.1      | KS10 FPGA Console Interface Registers                        |    |

| 5.1.1    | Console Microcontroller Interface                            |    |

| 5.1.2    | Console Interface Bus Design                                 |    |

| 5.1.3    | Console Interface Register Memory Map                        |    |

| 5.1.4    | Console Control/Status Register                              |    |

| 5.1.5    | Console Data Register                                        |    |

| 5.1.6    | Console Address Register                                     |    |

| 5.1.7    | Console Instruction Register                                 | 66 |

| 5.1.8    | DZ11 Console Control Register (DZCCR)                        | 67 |

| 5.1.9    | LP20 Console Control Register (LPCCR)                        |    |

| 5.1.10   | DUP11 Console Control Register (DPCCR)                       |    |

| 5.1.11   | RPXX Console Control Register (RPCCR)                        | 71 |

| 5.1.12   | RH11 Debug Register                                    | 72  |

|----------|--------------------------------------------------------|-----|

| 5.1.13   | Debug Interface                                        |     |

| 5.1.13.1 | Debug Control/Status Register (DCSR)                   | 73  |

| 5.1.13.2 | Debug Breakpoint Address Register (DBAR)               | 77  |

| 5.1.13.3 | Debug Breakpoint Mask Register (DBMR)                  | 78  |

| 5.1.13.4 | Debug Instruction Trace Register (DITR)                | 79  |

| 5.1.13.5 | Debug Program Counter and Instruction Register (DPCIR) | 80  |

| 5.1.14   | Firmware Version Register                              | 80  |

| 5.2      | Controlling the KS10                                   |     |

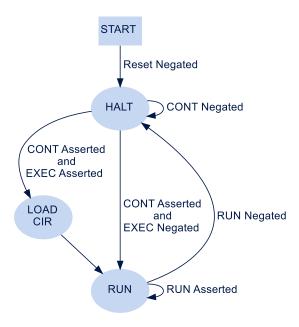

| 5.2.1    | The RUN bit                                            | 82  |

| 5.2.2    | The CONT bit                                           | 83  |

| 5.2.3    | The EXEC bit                                           | 83  |

| 5.3      | Console Interface Protocol                             | 83  |

| 5.4      | The Communications Area                                |     |

| 5.4.1    | Halt Switch                                            | 85  |

| 5.4.2    | Keep Alive                                             |     |

| 5.4.3    | Console TTY (CTY) Protocol                             |     |

| 5.4.3.1  | Console TTY (CTY) Input Protocol                       |     |

| 5.4.3.2  | Console TTY (CTY) Output Protocol                      |     |

| 5.4.4    | KLINIK Protocol                                        |     |

| 5.4.4.1  | KLINIK Input Protocol                                  |     |

| 5.4.4.2  | KLINIK Output Protocol                                 |     |

| 5.4.5    | Boot RH11 Address                                      | 89  |

| 5.4.6    | Boot Unit Number                                       |     |

| 5.4.7    | Boot Magtape Parameters                                | 90  |

| 6        | KS10 Memory Controller                                 | 92  |

| 6.1      | Memory Status Registers                                | 92  |

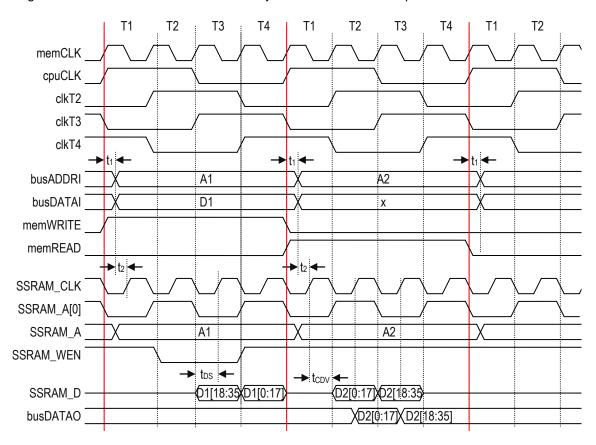

| 6.2      | SSRAM Memory Interface                                 | 93  |

| 6.2.1    | 18-bit SSRAM Memory Interface                          | 93  |

| 6.2.1.1  | 18-bit SSRAM Burst Read Cycle                          | 94  |

| 6.2.1.2  | 18-bit SSRAM Burst Write Cycle                         | 95  |

| 6.2.2    | 36-bit SSRAM Memory Interface                          | 95  |

| 7        | KS10 IO Bus (Unibus) Bridge                            | 99  |

| 7.1      | IO Bus Bridge Registers                                | 99  |

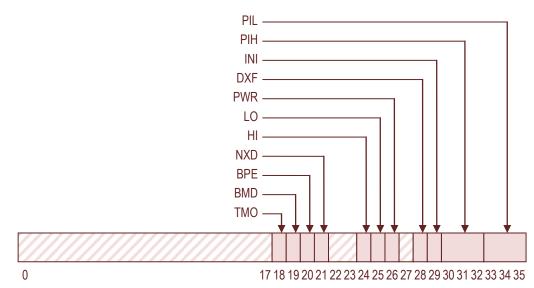

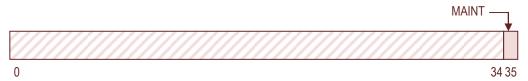

| 7.1.1    | IO Bus Bridge Control Status Register (UBACSR)         | 99  |

| 7.1.2    | IO Bus Bridge Maintenance Register                     |     |

| 7.2      | IO Bus Bridge Paging                                   | 102 |

| 7.2.1    | IO Bus Bridge Paging Memory                            | 102 |

| 7.2.2    | IO Bus Page Translation                                | 103 |

| 7.3      | IO Bus Bridge Address Mapping                          | 104 |

| 8        | DUP11 Synchronous Communications Adapter               | 106 |

| 8.1      | Synchronous Serial Protocols                           | 106 |

| 8.1.1    | DDCMP/BISYNC Mode                                      | 106 |

| 8.1.2    | SDLC/ADCCP Mode                                        | 107 |

| 8.1.3    | SDLC Receiver Synchronization                          | 107 |

| 8.2      | DUP11 Registers                                        | 107 |

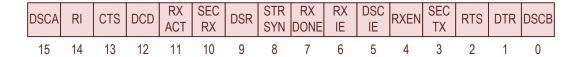

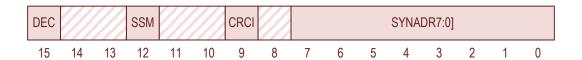

| 8.2.1    | DUP11 Receiver Control/Status Register (RXCSR)         | 107 |

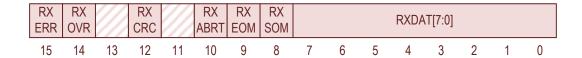

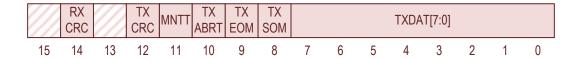

| 8.2.2    | DUP11 Received Data Buffer (RXDBUF)                    | 112 |

| 8.2.3    | DUP11 Parameter Control/Status Register (PARCSR)       | 116 |

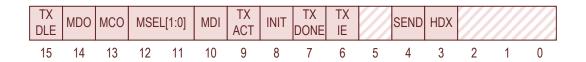

| 8.2.4    | DUP11 Transmitter Control/Status Register (TXCSR)      | 118 |

|          |                                                        |     |

| 8.2.5    | DUP11 Transmitter Data Buffer (TXDBUF)      | 123 |

|----------|---------------------------------------------|-----|

| 8.3      | DUP11 Interrupts                            | 126 |

| 8.3.1    | Transmitter Interrupt                       | 126 |

| 8.3.2    | Receiver Interrupt                          |     |

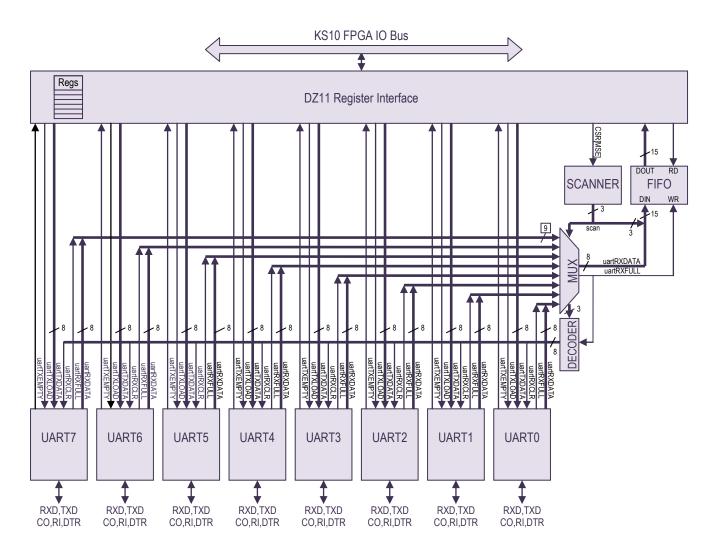

| 9        | DZ11 Asynchronous Multiplexer               | 127 |

| 9.1      | DZ11 Registers                              | 128 |

| 9.1.1    | DZ11 Control and Status Register (CSR)      | 128 |

| 9.1.2    | DZ11 Receiver Buffer Register (RBUF)        | 131 |

| 9.1.3    | DZ11 Line Parameter Register (LPR)          | 132 |

| 9.1.4    | DZ11 Transmit Control Register (TCR)        | 134 |

| 9.1.5    | DZ11 Modem Status Register (MSR)            | 134 |

| 9.1.6    | DZ11 Transmit Data Register (TDR)           | 135 |

| 9.2      | DZ11 Interrupts                             |     |

| 9.2.1    | DZ11 Transmitter Interrupt                  | 135 |

| 9.2.2    | DZ11 Receiver Interupt                      | 136 |

| 9.3      | Hardware Description                        | 136 |

| 9.3.1    | The Transmitter Scanner                     | 136 |

| 9.3.2    | The Baud Rate Generator                     |     |

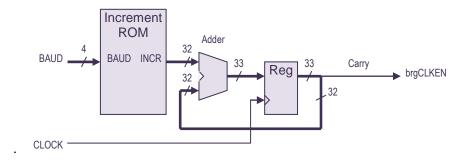

| 9.3.2.1  | The Fractional-N Divider                    | 136 |

| 10       | KMC11 Co-Processor                          |     |

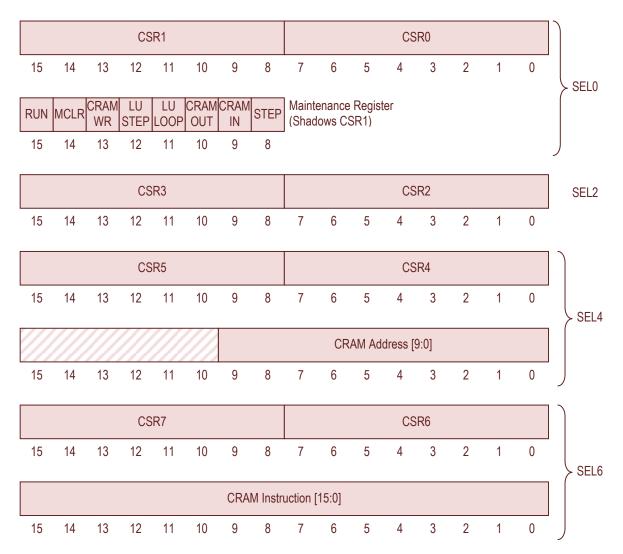

| 10.1     | KMC11 Registers                             |     |

| 10.1.1   | KMC11 Control and Status Registers (CSRs)   |     |

| 10.1.2   | KMC11 Maintenance Register                  |     |

| 10.1.3   | KMC11 Maintenance Address Register          |     |

| 10.1.4   | KMC11 Maintenance Instruction Register      |     |

| 10.2     | KMC11 Microprocessor Registers              |     |

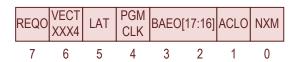

| 10.2.1   | KMC11 MISC Register (MISC)                  |     |

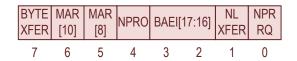

| 10.2.2   | KMC11 NPR Control Register (NPRC)           |     |

| 11       | RH11 Massbus Disk Controller                |     |

| 11.1     | Definitions                                 |     |

| 11.1.1   | Disk Clear Operations                       |     |

| 11.1.1.1 | IO Bridge Clear                             |     |

| 11.1.1.2 | Controller Clear                            |     |

| 11.1.1.3 | Drive Clear                                 |     |

| 11.1.1.4 | Error Clear                                 |     |

| 11.2     | RH11 Registers                              |     |

| 11.2.1   | RH11 Control and Status #1 (RHCS1) Register |     |

| 11.2.2   | RH11 Word Count (RHWC) Register             |     |

| 11.2.3   | RH11 Bus Address (RHBA) Register            |     |

| 11.2.4   | RH11 Control and Status #2 (RHCS2) Register |     |

| 11.2.5   | RH11 Data Buffer (RHDB) Register            |     |

| 11.3     | RH11 Interrupts                             |     |

| 12       | RP06/07 Disk Simulator                      |     |

| 12.1     | RPXX Registers                              |     |

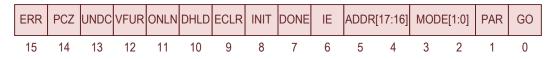

| 12.1.1   | RP Control and Status #1 (RPCS1) Register   |     |

| 12.1.2   | RP Disk Address (RPDA) Register             |     |

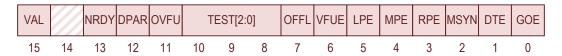

| 12.1.3   | RP Drive Status (RPDS) Register             |     |

| 12.1.4   | RP Error #1 (RPER1) Register                |     |

| 12.1.5   | RP Attention Summary (RPAS) Register        |     |

| 12.1.6   | RP Look Ahead (RPLA) Register               |     |

| 12.1.7   | RP Maintenance (RPMR) Register              | 169 |

| 12.1.8   | RP Drive Type (RPDT) Register                     | 172 |

|----------|---------------------------------------------------|-----|

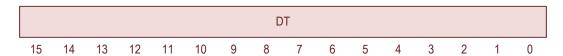

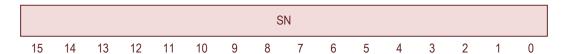

| 12.1.9   | RP Serial Number (RPSN) Register                  |     |

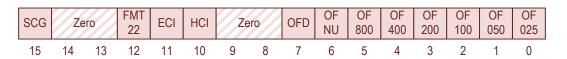

| 12.1.10  | RP Offset (RPOF) Register                         | 173 |

| 12.1.11  | RP Desired Cylinder (RPDC) Register               |     |

| 12.1.12  | RP Current Cylinder (RPCC) Register               |     |

| 12.1.13  | RP Error Status #2 (RPER2) Register               |     |

| 12.1.14  | RP Error Status #3 (RPER3) Register               |     |

| 12.1.15  | RP Error Position (RPEC1) Register                |     |

| 12.1.16  | RP Error Pattern (RPEC2) Register                 |     |

| 12.2     | RMXX Registers                                    |     |

| 12.2.1   | RM Control and Status #1 (RMCS1) Register         |     |

| 12.2.2   | RM Disk Address (RMDA) Register                   |     |

| 12.2.3   | RM Drive Status (RMDS) Register                   |     |

| 12.2.4   | RM Error #1 (RMER1) Register                      |     |

| 12.2.5   | RM Attention Summary (RMAS) Register              |     |

| 12.2.6   | RM Look Ahead (RMLA) Register                     |     |

| 12.2.7   | RM Maintenance Register #1 (RMMR1) Register       |     |

| 12.2.8   | RM Drive Type (RMDT) Register                     |     |

| 12.2.9   | RM Serial Number (RMSN) Register                  |     |

| 12.2.10  | RM Offset (RMOF) Register                         |     |

| 12.2.11  | RM Desired Cylinder (RMDC) Register               |     |

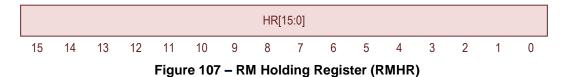

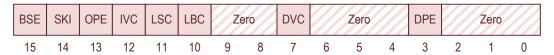

| 12.2.12  | RM Holding Register (RMHR) Register               |     |

| 12.2.13  | RM Maintenance Register #2 (RMMR2) Register       |     |

| 12.2.14  | RM Error Register #2 (RMER2) Register             |     |

| 12.2.15  | RM Error Position (RMEC1) Register                |     |

| 12.2.16  | RM Error Pattern (RMEC2) Register                 |     |

| 12.3     | Disk Functions                                    |     |

| 12.3.1   | Seek Function                                     |     |

| 12.3.2   | Search Function                                   |     |

| 12.3.3   | Offset Command and Return to Centerline Functions |     |

| 12.3.4   | Recalibrate Function                              |     |

| 12.3.5   | Unload Function                                   |     |

| 12.3.6   | Pack Acknowledge Function                         |     |

| 12.3.7   | Read-in Preset Function                           |     |

| 12.3.8   | Release Function                                  |     |

| 12.3.9   | Data Transfer Functions                           |     |

| 12.3.9.1 | Read header plus data                             |     |

| 12.3.9.2 | Read data                                         |     |

| 12.3.9.3 | Write header plus data                            |     |

| 12.3.9.4 | Write header                                      |     |

| 12.3.9.5 | Write check header plus data                      |     |

| 12.3.9.6 | Write check data                                  |     |

| 12.4     | Disk Completion Monitor                           |     |

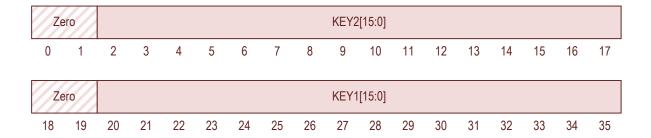

| 12.5     | Secure Digital (SD) Disk Controller               |     |

| 12.6     | Secure Digital (SD) Capability Issues             |     |

| 12.6.1   | SIMH Cylinder/Head/Sector (CHS) Disk Addressing   |     |

| 12.6.2   | Cylinder/Head/Sector (CHS) Disk Address Increment |     |

| 12.6.3   | SIMH "Sector" Size                                |     |

| 12.6.4   | Disk Drive Parameters                             |     |

| 12.6.5   | RPxx/RMxx Disk Addressing                         |     |

| 12.6.6   | SD Disk Organization                              |     |

|          | ::ga:::                                           |     |

| 13       | LP20 Printer Controller                                           | 200 |

|----------|-------------------------------------------------------------------|-----|

| 13.1     | LP20 Registers                                                    | 200 |

| 13.1.1   | Control/Status A Register (CSRA)                                  | 200 |

| 13.1.2   | Control/Status B Register (CSRB)                                  | 206 |

| 13.1.3   | Bus Address Register (BAR)                                        | 211 |

| 13.1.4   | Byte Count Register (BCTR)                                        | 212 |

| 13.1.5   | Page Count Register (PCTR)                                        |     |

| 13.1.6   | RAM Data Register (RAMD)                                          |     |

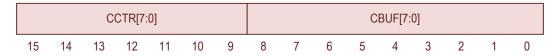

| 13.1.7   | Column Counter Register (CCTR) / Character Buffer Register (CBUF) |     |

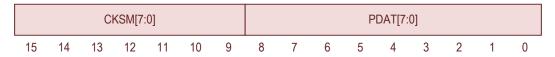

| 13.1.8   | Checksum Register (CKSM) / Printer Data Register (PDAT)           |     |

| 13.2     | LP20 Interrupts                                                   |     |

| 13.3     | LP20 Modes                                                        |     |

| 13.3.1   | Print Mode                                                        |     |

| 13.3.2   | Test Mode                                                         |     |

| 13.3.2.1 | Normal Test Mode                                                  |     |

| 13.3.2.2 | Demand Timeout Test Mode                                          |     |

| 13.3.2.3 | SSYN Timeout Test Mode                                            |     |

| 13.3.2.4 | RAM Parity Test Mode                                              |     |

| 13.3.2.5 | Memory Parity Test Mode                                           |     |

| 13.3.2.6 | Line Printer Parity Test Mode                                     |     |

| 13.3.2.7 | Page Counter Test Mode                                            |     |

| 13.3.3   | Load DAVFU Mode                                                   |     |

| 13.3.4   | Load RAM Mode                                                     |     |

| 14       | LP26 Line Printer                                                 |     |

| 14.1     | Vertical Format Units                                             |     |

| 14.1.1   | Tape Controlled Vertical Format Unit (TCVFU)                      |     |

| 14.1.2   | Direct Access Vertical Format Unit (DAVFU)                        |     |

| 14.1.2.1 | DAVFU Loading                                                     |     |

| 14.1.2.2 | DAVFU Use                                                         |     |

| 14.1.2.3 | Error Conditions                                                  |     |

| 15       | Executive Mode and IO Instructions                                |     |

| 15.1     | Executive Mode Instructions                                       |     |

| 15.1.1   | Arithmetic Processor Interface (APR) Instructions                 |     |

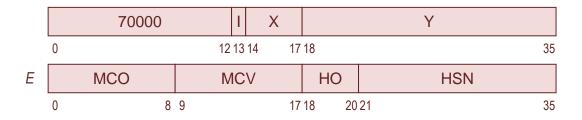

| 15.1.1.1 | APR Identification (APRID/BLKI APR)                               |     |

| 15.1.1.2 | Write APR (WRAPR/CONO APR)                                        |     |

| 15.1.1.3 | Read APR (RDAPR/CONI APR) conditions                              |     |

| 15.1.2   | Priority Interrupt Controller (PI) Instructions                   |     |

| 15.1.2.1 | Write Priority Interrupt (WRPI/CONO PI)                           |     |

| 15.1.2.2 | Read Priority Interrupt (RDPI/CONI PI)                            |     |

| 15.1.3   | User Base Register (UBR) Instructions                             |     |

| 15.1.3.1 | Write to the User Base Register (WRUBR/DATO PAG)                  |     |

| 15.1.3.2 | Read User Base Register (RDUBR/DATI PAG)                          |     |

| 15.1.4   | Clear Page Table Entry (CLRPT/BLKO PAG)                           |     |

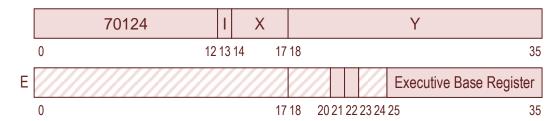

| 15.1.5   | Executive Base Register (EBR) Instructions                        |     |

| 15.1.5.1 | Write to the Executive Base Register (WREBR/CONO PAG)             |     |

| 15.1.5.2 | Read the Executive Base Register (RDEBR/CONI PAG)                 |     |

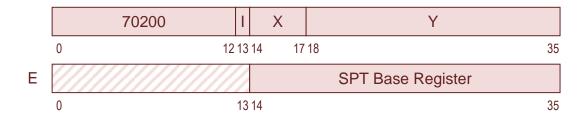

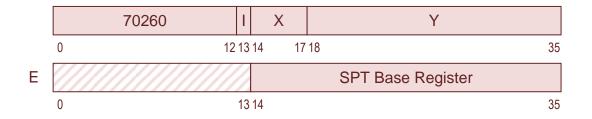

| 15.1.6   | Shared Pointer Table (SPT) Base Address Register                  |     |

| 15.1.6.1 | Read Shared Pointer Table Base Address Register (RDSPB)           |     |

| 15.1.6.2 | Write Shared Pointer Table Base Address Register (WRSPB)          |     |

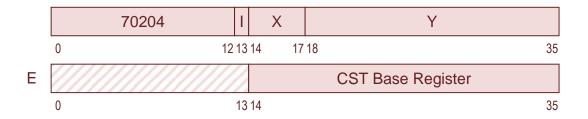

| 15.1.7   | Core Status Table (CST) Instructions                              |     |

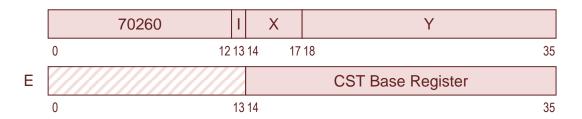

| 15.1.7.1 | Read Core Status Table Base Register (RDCSB)                      |     |

|          |                                                                   | 207 |

| 15.1.7.2  | Write Core Status Table Base Register (WRCSB)        | 234 |

|-----------|------------------------------------------------------|-----|

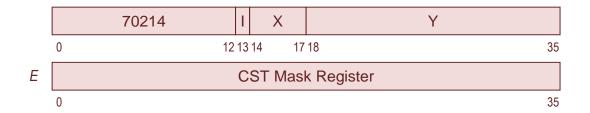

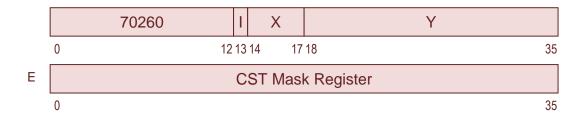

| 15.1.7.3  | Read Core Status Table Mask Register (RDCSTM)        |     |

| 15.1.7.4  | Write Core Status Table Mask Register (WRCSTM)       | 235 |

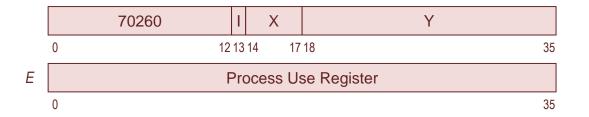

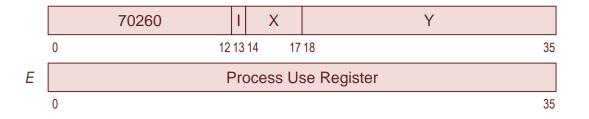

| 15.1.7.5  | Read Core Status Table Process Use Register (RDPUR)  | 235 |

| 15.1.7.6  | Write Core Status Table Process Use Register (WRPUR) | 235 |

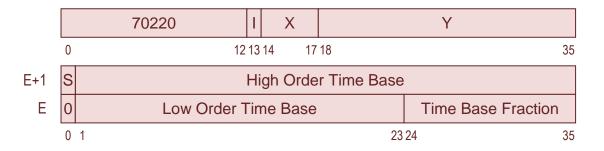

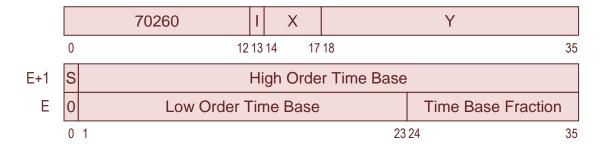

| 15.1.8    | Timebase Instructions                                | 235 |

| 15.1.8.1  | RDTIM – Read Timebase                                | 236 |

| 15.1.8.2  | WRTIM - Write Timebase                               | 236 |

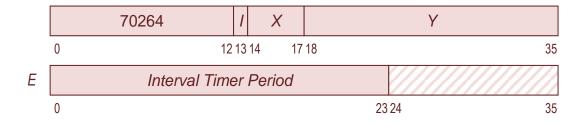

| 15.1.9    | Interval Timer Instructions                          | 237 |

| 15.1.9.1  | RDINT – Read Interval Timer                          |     |

| 15.1.9.2  | WRINT - Write Interval Timer                         | 237 |

| 15.1.10   | Halt Status Block Address Instructions               | 237 |

| 15.1.10.1 | RDHSB - Read Halt Status Block Address               | 238 |

| 15.1.10.2 | WRHSB - Write Halt Status Block Address              | 238 |

| 16        | Diagnostics                                          |     |

| 17        | Building the KS10 FPGA System                        | 241 |

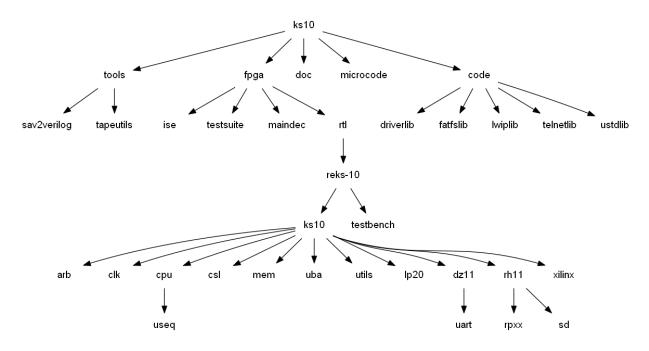

| 17.1      | Tools                                                | 241 |

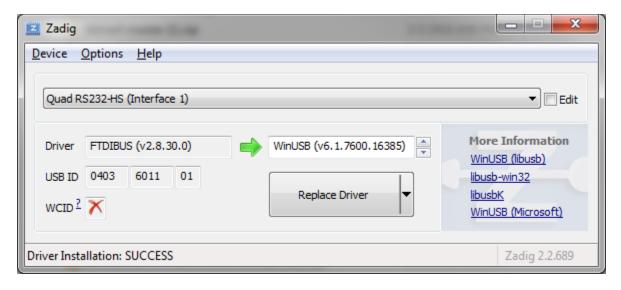

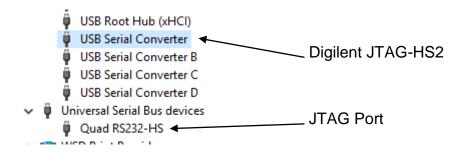

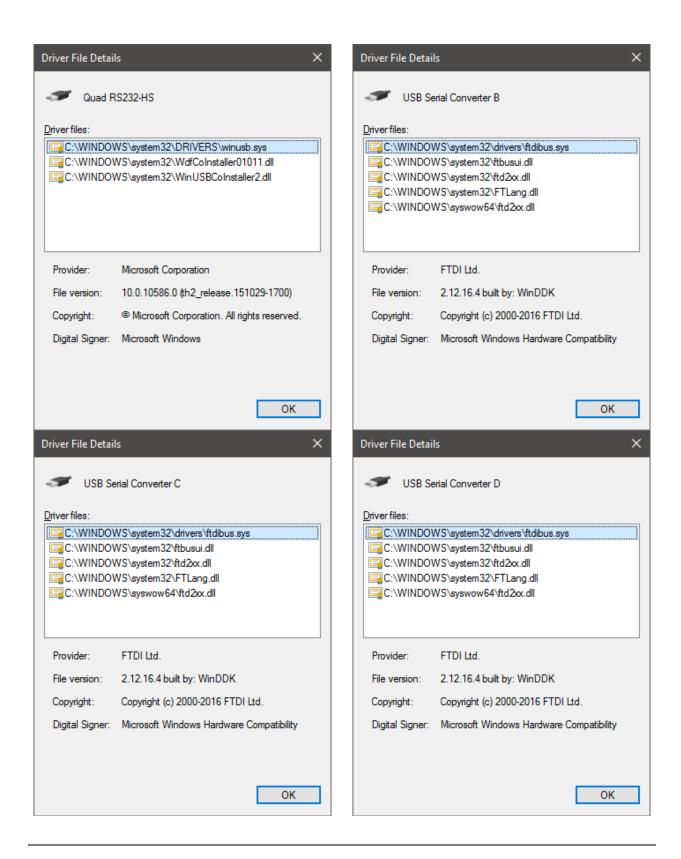

| 17.1.1    | FTDI USB drivers                                     | 241 |

| 17.1.1.1  | FTDI Hardware                                        | 242 |

| 17.1.2    | FPGA Tools                                           |     |

| 17.1.2.1  | Xilinx ISE Webpack Version 14.7                      | 242 |

| 17.1.2.2  | Icarus Verilog                                       |     |

| 17.1.2.3  | FPGA JTAG Programming Cable                          | 242 |

| 17.1.2.4  | Xilinx Chipscope (optional)                          | 243 |

| 17.1.3    | Software Tools                                       | 243 |

| 17.1.3.1  | GCC tool suite ARM processors                        |     |

| 17.1.3.2  | GDB Debugger for ARM processors                      |     |

| 17.1.3.3  | OpenOCD On-Chip Debugger                             | 244 |

| 17.1.3.4  | Eclipse Integrated Development Environment           | 244 |

# **List of Figures**

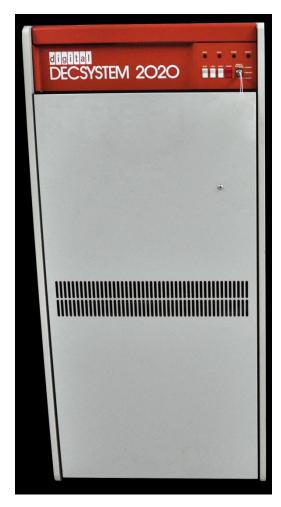

| Figure 1 – DEC KS10                                                           | 16 |

|-------------------------------------------------------------------------------|----|

| Figure 2 – DEC KS10 with Covers Removed                                       | 16 |

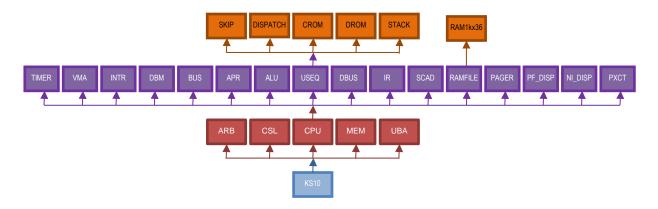

| Figure 3 – KS10 FPGA Design Hierarchy                                         |    |

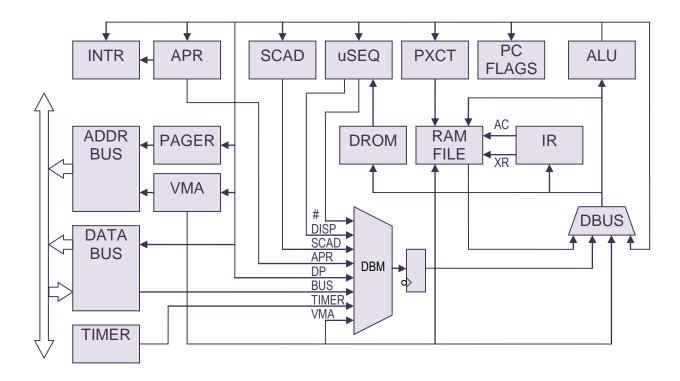

| Figure 4 – KS10 FPGA CPU Block Diagram                                        |    |

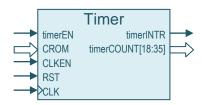

| Figure 5 – Timer Interface Diagram                                            |    |

| Figure 6 – Interval Timer Register                                            | 19 |

| Figure 7 – Timer Block Diagram                                                |    |

| Figure 8 – Priority Interrupt Register Format                                 |    |

| Figure 9 – Priority Interrupt Block Diagram                                   |    |

| Figure 10 – DBM Block Diagram                                                 |    |

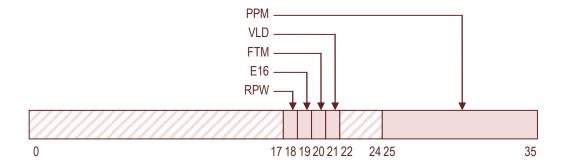

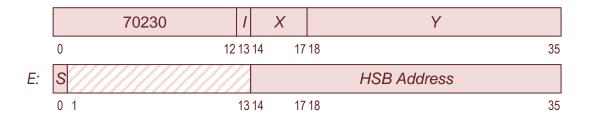

| Figure 11 – Extended Address                                                  |    |

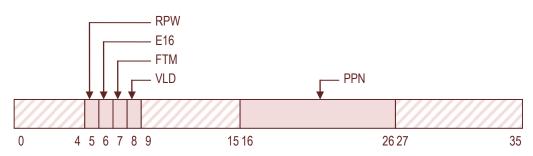

| Figure 12 - Physical Address                                                  |    |

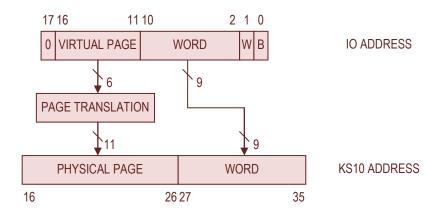

| Figure 13 - Paged Address                                                     |    |

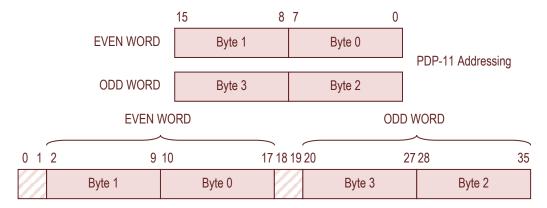

| Figure 14 - WRU Address                                                       |    |

| Figure 15 - Bus Interface                                                     |    |

| Figure 16 – APR Interface Diagram                                             |    |

| Figure 17 – ALU Interface Diagram                                             |    |

| Figure 18 – DEC KS10 ALU Implementation                                       |    |

| Figure 19 – KS10 FPGA ALU Implementation                                      |    |

| Figure 20 – Microsequencer Interface                                          |    |

| Figure 21 – Microsequencer Block Diagram                                      |    |

| Figure 22 – Dispatch Interface Diagram                                        |    |

| Figure 23 – Skip Interface Diagram                                            |    |

| Figure 24 – Stack Interface Diagram                                           |    |

| Figure 25 – Stack Block Diagram                                               |    |

| Figure 26 – DBUS Interface Diagram                                            |    |

| Figure 27 – DBUS Block Diagram                                                |    |

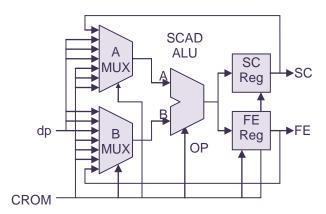

| Figure 28 – SCAD Interface Diagram                                            | 34 |

| Figure 29 – SCAD Block Diagram                                                |    |

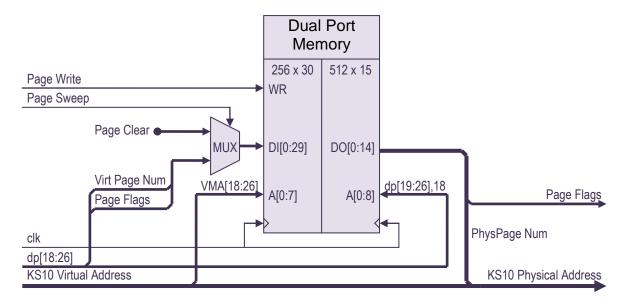

| Figure 30 – Pager Address Translation                                         | 36 |

| Figure 31 – Pager Block Diagram                                               | 37 |

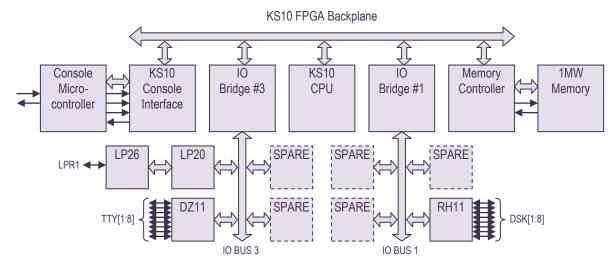

| Figure 32 – KS10 FPGA Bus Architecture                                        | 39 |

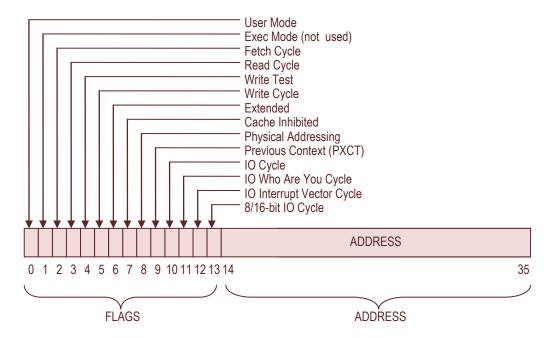

| Figure 33 – KS10 FPGA Address Bus Illustration                                |    |

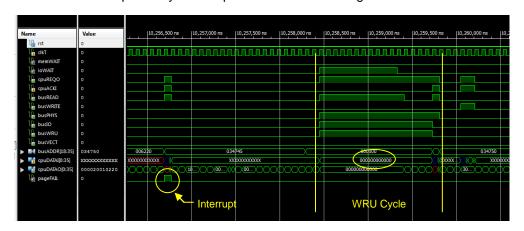

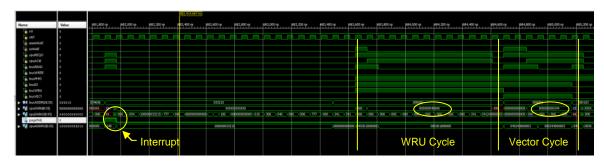

| Figure 34 – APR Interrupt Bus Cycle                                           | 46 |

| Figure 35 – External Interrupt Bus Cycle                                      | 47 |

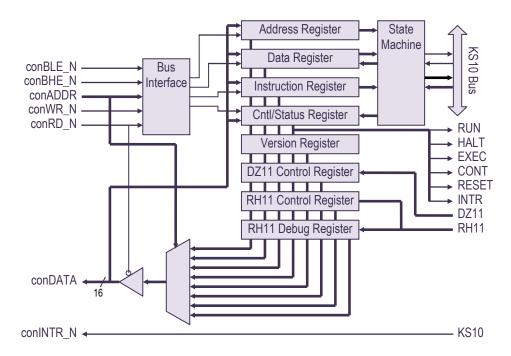

| Figure 36 – KS10 Console Interface Block Diagram                              | 56 |

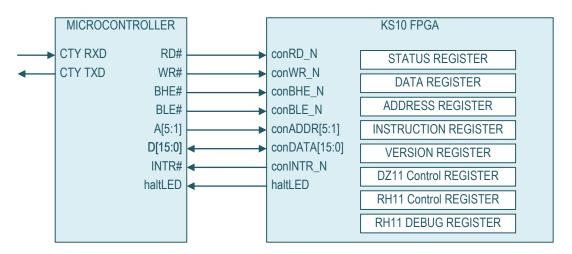

| Figure 37 – Console Microcontroller and KS10 FPGA Interface                   | 57 |

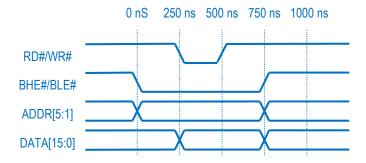

| Figure 38 - Console Microcontroller Interface Read/Write Cycle Timing Diagram | 58 |

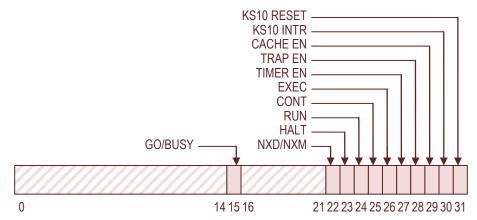

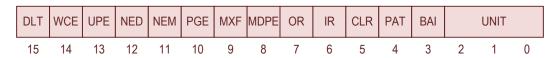

| Figure 39 – Console Control/Status Register                                   |    |

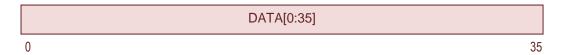

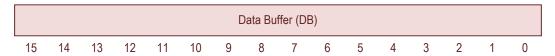

| Figure 40 – Console Data Register                                             | 66 |

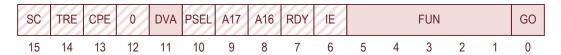

| Figure 41 – Console Address Register                                          | 66 |

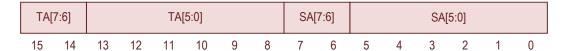

| Figure 42 – Console Instruction Register                                      |    |

| Figure 43 – DZ11 Console Control Register (DZCCR)                             |    |

| Figure 44 – LP20 - Console Control Register (LPCCR)                           |    |

| Figure 45 – DUP11 Console Control Register (DPCCR)                            |    |

| Figure 46 – RPXX Console Control Register (RPCCR)                             |    |

| Figure 47 – RH11 Debug Register                                               | 72 |

| Figure 48 – Debug Control/Status Register (DCSR)                              |    |

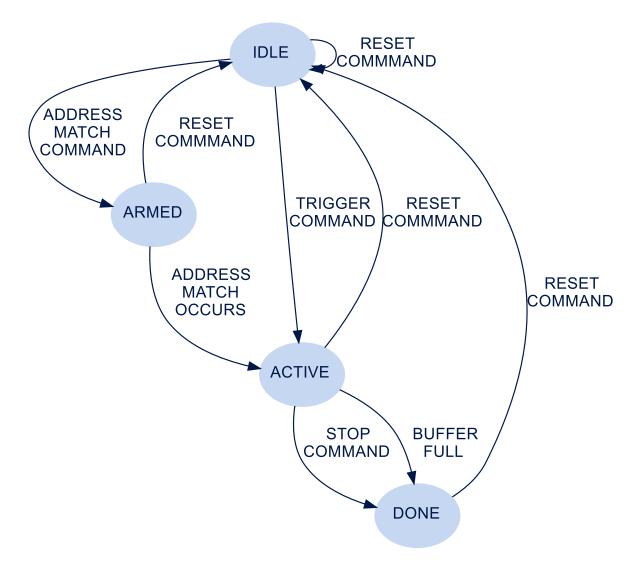

| Figure 49 - Instruction Trace State Diagram                                   |    |

| Figure 50 – Debug Breakpoint Address Register (DBAR)              | 77    |

|-------------------------------------------------------------------|-------|

| Figure 51 – Breakpoint Mask Register (DBMR)                       |       |

| Figure 52 – Debug Instruction Trace Register                      |       |

| Figure 53 – Firmware Version Register                             |       |

| Figure 54 – KS10 Control State Diagram                            |       |

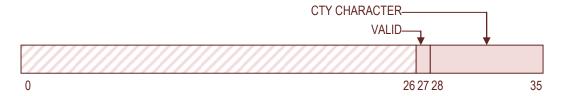

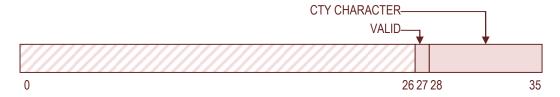

| Figure 55 – KS10 CTY Input Word (KS10 Memory Address 000032)      |       |

| Figure 56 - KS10 CTY Output Word (KS10 Memory Address 000033)     | 87    |

| Figure 57 – Memory Status Register (Read)                         |       |

| Figure 58 – Memory Status Register (Write)                        |       |

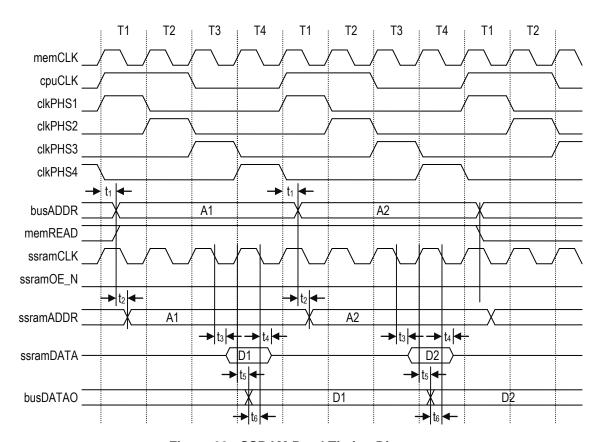

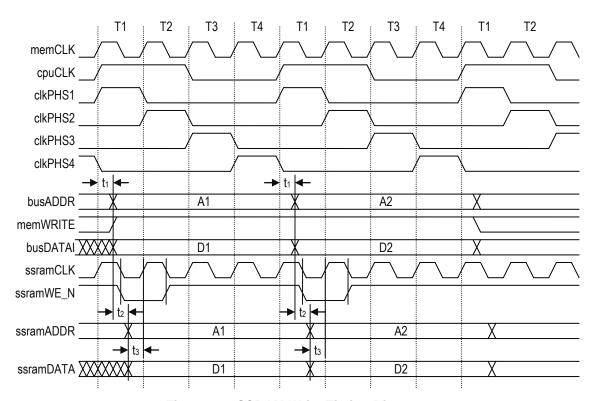

| Figure 59 – 18-bit SSRAM Burst Bus Cycles                         |       |

| Figure 60 - SSRAM Read Timing Diagram                             |       |

| Figure 61 - SSRAM Write Timing Diagram                            |       |

| Figure 62 – IO Bridge Control Status Register (UBACSR)            | .100  |

| Figure 63 – IO Bridge Maintenance Register (UBAMR)                |       |

| Figure 64 – IO Bridge Paging RAM Write                            |       |

| Figure 65 – IO Bridge Paging RAM Read                             |       |

| Figure 66 – IO Bus Page Translation                               |       |

| Figure 67 – IO Bus Byte and Word Translation                      |       |

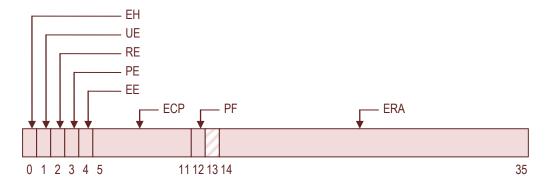

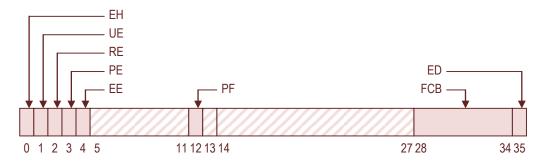

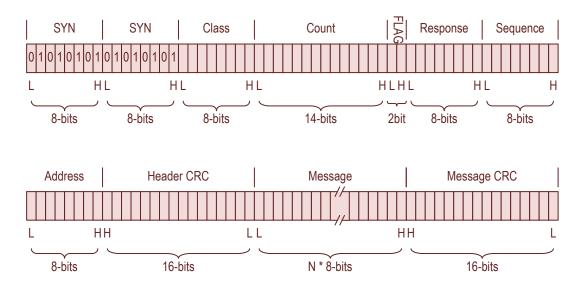

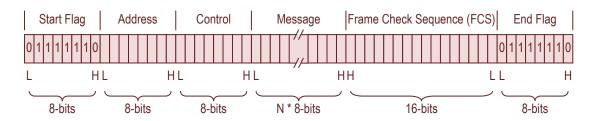

| Figure 68 – DDCMP Message Format                                  |       |

| Figure 69 – SDLC Message Format                                   |       |

| Figure 70 – DUP11 Receiver Control and Status Register (RXCSR)    | 108   |

| Figure 71 – DUP11 Receiver Data Buffer (RXDBUF)                   |       |

| Figure 72 – DUP11 Parameter Control and Status Register (PARCSR)  |       |

| Figure 73 – DUP11 Transmitter Control and Status Register (TXCSR) |       |

| Figure 74 – DUP11 Transmitter Data Buffer (TXDBUF)                |       |

| Figure 75 – DZ11 Block Diagram                                    |       |

| Figure 76 – DZ11 Control and Status Register (CSR)                |       |

| Figure 77 – DZ11 Receiver Buffer Register (RBUF)                  |       |

| Figure 78 – DZ11 Line Parameter Register (LPR)                    |       |

| Figure 79 – DZ11 Transmit Control Register TCR)                   | . 134 |

| Figure 80 – Fractional-N Divider Block Diagram                    | . 136 |

| Figure 81 – KMC11 Control and Status Registers                    | . 139 |

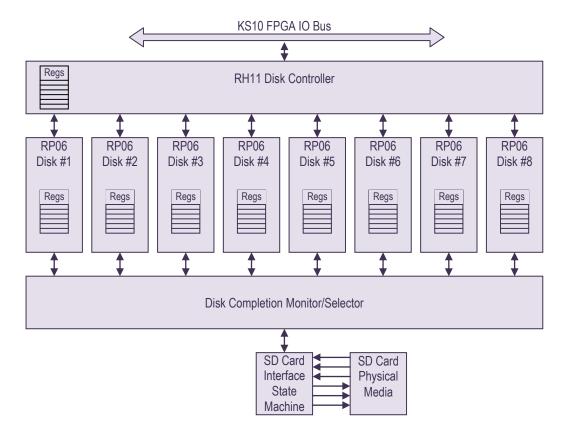

| Figure 82 – KS10 FPGA Disk Subsystem Architecture                 |       |

| Figure 83 – RH11 Control and Status Register #1 (RHCS1)           |       |

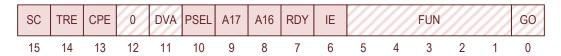

| Figure 84 – RH11 Word Count Register (RHWC)                       |       |

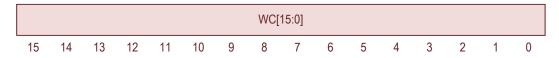

| Figure 85 – RH11 Bus Address Register (RPBA)                      |       |

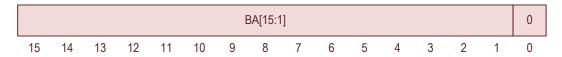

| Figure 86 – RH11 Control and Status Register #2 (RHCS2)           |       |

| Figure 87 – RH11 Data Buffer Register (RPDB)                      |       |

| Figure 88 – RP Control and Status Register #1 (RPCS1)             |       |

| Figure 89 – RP Disk Address Register (RPDA)                       |       |

| Figure 90 – RP Drive Status Register (RPDS)                       |       |

| Figure 91 – RP Error Register #1 (RPER1)                          |       |

| Figure 92 – RP Attention Summary Register (RPAS)                  |       |

| Figure 93 – RP Look Ahead Register (RPLA)                         |       |

| Figure 94 – RP Maintenance Register (RPMR)                        |       |

| Figure 95 – RP Drive Type Register (RPDT)                         |       |

| Figure 96 – RP Serial Number Register (RPSN)                      |       |

| Figure 97 – RP Offset Register (RPOF)                             |       |

| Figure 98 – RP Desired Cylinder Register (RPDC)                   | .175  |

| Figure 99 – RP Current Cylinder Register (RPCC)                   |       |

| Figure 100 – RP Error Status #2 (RPER2)                           |       |

|                                                                   |       |

| Figure 101 – RP Error Status #3 (RPER3)                                        |       |

|--------------------------------------------------------------------------------|-------|

| Figure 102 – RP Error Position Register (RPEC1)                                | . 180 |

| Figure 103 – RP Error Pattern Register (RPEC2)                                 | . 180 |

| Figure 104 – RM Look Ahead Register (RMLA)                                     |       |

| Figure 105 – RM Maintenance Register #1 (RMMR) (READ)                          |       |

| Figure 106 – RM Maintenance Register #1 (RMMR) (WRITE)                         | . 183 |

| Figure 107 – RM Holding Register (RMHR)                                        | . 185 |

| Figure 108 – RM Maintenance Register #2 (RMMR2)                                |       |

| Figure 109 – RM Error Register #2 (RMER2)                                      |       |

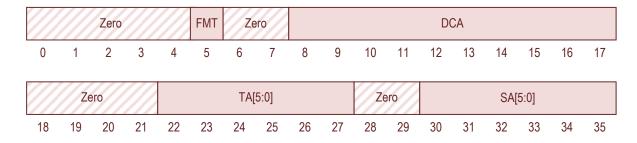

| Figure 110 – Sector Header Word #1                                             |       |

| Figure 111 – Sector Header Word #2                                             |       |

| Figure 112 – Sector Increment Algorithm                                        | . 195 |

| Figure 113 – SIMH/PDP10 Disk Image Hex Dump                                    |       |

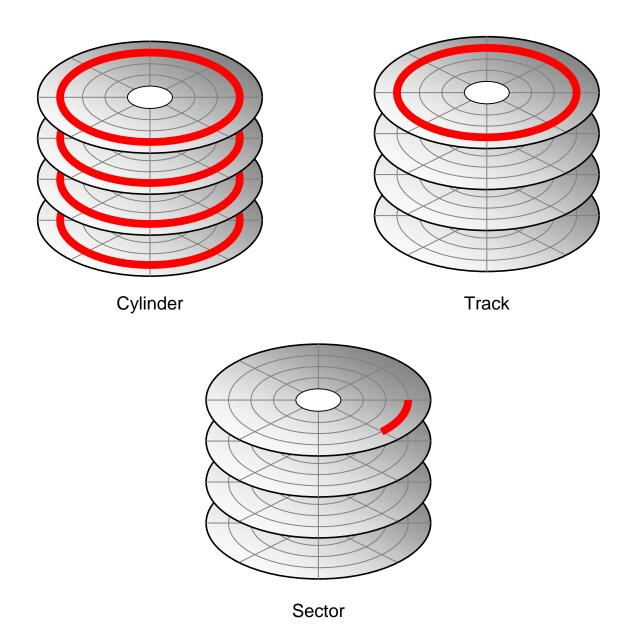

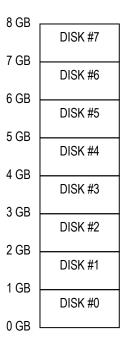

| Figure 114 – Disk Cylinder, Track, and Sector                                  |       |

| Figure 115 – SD Card Storage Allocation                                        | . 199 |

| Figure 116 – Control/Status A Register (CSRA)                                  |       |

| Figure 117 – Control/Status B Register (CSRB)                                  |       |

| Figure 118 – Bus Address Register (BAR)                                        |       |

| Figure 119 – Byte Count Register (BCTR)                                        |       |

| Figure 120 – Page Count Register (PCTR)                                        |       |

| Figure 121 – RAM Data Register (RAMD)                                          |       |

| Figure 122 - Column Counter Register (CCTR) / Character Buffer Register (CBUF) |       |

| Figure 123 – Printer Data Register (PDAT) / Checksum Register (CKSM)           |       |

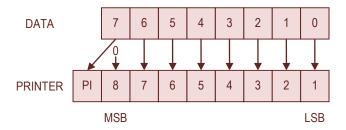

| Figure 124 – Printer Data Munging                                              |       |

| Figure 125 – APRID (BLKI APR) Instruction                                      |       |

| Figure 126 – WRAPR (CONO APR) Instruction                                      |       |

| Figure 127 – RDAPR (CONLAPR) Instruction                                       |       |

| Figure 128 – WRPI (CONO PI) Instruction                                        |       |

| Figure 129 – RDPI (CONI PI) Instruction                                        |       |

| Figure 130 – WRUBR (DATO PAG) Instruction                                      |       |

| Figure 131 – RDUBR (DATI PAG) Instruction                                      |       |

| Figure 132 – CLRPT (BLKO PAG) Instruction                                      |       |

| Figure 133 – WREBR (CONO PAG) Instruction                                      |       |

| Figure 134 – RDEBR (CONI PAG) Instruction                                      |       |

| Figure 135 – RDSPB Instruction                                                 |       |

| Figure 136 – WRSPB Instruction                                                 |       |

| Figure 137 – RDCSB Instruction                                                 |       |

| Figure 138 – WRCSB Instruction                                                 |       |

| Figure 139 – RDCSTM Instruction                                                |       |

| Figure 140 – WRCSTM Instruction                                                |       |

| Figure 141 – RDPUR Instruction                                                 |       |

| Figure 142 – WRPUR Instruction                                                 |       |

| Figure 143 – RDTIM Instruction                                                 |       |

| Figure 144 – WRTIM Instruction                                                 |       |

| Figure 145 – RDINT Instruction                                                 |       |

| Figure 146 – WRINT Instruction                                                 |       |

| Figure 147 – RDHSB Instruction                                                 |       |

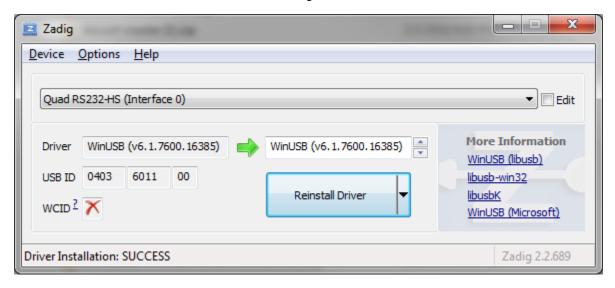

| Figure 148 – WRHSB Instruction                                                 |       |

| Figure 149 – Directory Structure                                               | . 241 |

Page 11 22 June 2021

#### **List of Tables**

| Table 1 – APR Flags                                                                                |        |

|----------------------------------------------------------------------------------------------------|--------|

| Table 2 – KS10 Microcode Variations                                                                |        |

| Table 3 – RAMFILE Addressing                                                                       | 34     |

| Table 4 – "Page Fail" Dispatches                                                                   |        |

| Table 5 – Bus Arbiter Operations                                                                   |        |

| Table 6 – Address Flag Definitions                                                                 | 40     |

| Table 7 – KS10 Bus Cycles                                                                          |        |

| Table 8 – KS10 Console Command Summary                                                             |        |

| Table 9 – Console Interface Register Memory Map                                                    |        |

| Table 10 – Console Control/Status Register Definitions                                             |        |

| Table 11 – DZ11 Console Control Register (DZCCR) Definition                                        |        |

| Table 12 – LP20 Console Control Register (LPCCR) Definition                                        |        |

| Table 13 – DUP11 Console Control Register (DPCCR) Definition                                       |        |

| Table 14 – RPXX Console Control Register (RPCCR) Definition                                        |        |

| Table 15 – RH11 Debug Register Definitions                                                         | 73     |

| Table 16 – Debug Control/Status Register (DCSR) Definitions                                        |        |

| Table 17 – Debug Breakpoint Address Register (DBAR) Definitions                                    |        |

| Table 18 – Debug Breakpoint Mask Register Definitions (DBMR)                                       |        |

| Table 19 – Debug Instruction Trace Register Definitions                                            |        |

| Table 20 – Console Firmware Version Register Definitions                                           |        |

| Table 21 – Control Operation from Halt State                                                       |        |

| Table 22 – KS10/Console Communications Area                                                        |        |

| Table 23 – KS10 Halt Switch Word (KS10 Memory Address 000030)                                      |        |

| Table 24 – 8080 Status Word (KS10 Memory Address 000031)                                           |        |

| Table 25 – KS10 CTY Input Word (KS10 Memory Address 000032)                                        |        |

| Table 26 – KS10 CTY Output Word (KS10 Memory Address 000032)                                       |        |

| Table 27 – KS10 KLINIK Input Word (KS10 Memory Address 000034)                                     |        |

| Table 28 – KS10 KLINIK Output Word (KS10 Memory Address 000035)                                    |        |

| Table 29 – KS10 RH11 Address Word (KS10 Memory Address 000036)                                     |        |

| Table 30 – KS10 Boot Unit Number Word (KS10 Memory Address 000037                                  | ′)90   |

| Table 31 – KS10 Boot Magtape Parameter Word (KS10 Memory Address                                   |        |

| Table 32 – Memory Status Register Definitions                                                      |        |

| Table 33 - SSRAM Read Timing Parameters                                                            |        |

| Table 34 – SSRAM Write Timing Parameters                                                           |        |

| Table 35 – IO Bridge Control Status Register (UBACSR) Definitions                                  |        |

| Table 36 – IO Bridge Maintenance Register (UBAMR) Definitions                                      |        |

| Table 37 – IO Bridge Paging RAM Definitions                                                        |        |

| Table 38 – UBA Address Translation                                                                 |        |

| Table 39 – DUP11 Configuration                                                                     |        |

| Table 40 – DUP11 Register Summary                                                                  |        |

| Table 41 – DUP11 RX Control/Status Register (RXCSR) – IO Address 76                                |        |

| Table 42 – DUP11 RX Data Buffer Register (RXDBUF) – IO Address 7603                                |        |

| Table 43 – DUP11 Param Control/Status Register (PARCSR) - IO Addres                                |        |

| Table 44 – DUP11 TX Control/Status Register (TXCSR) - IO Address 760                               | 304119 |

| Table 45 – DUP11 TX Data Buffer (TXDBUF) - IO Address 760306                                       | 124    |

| Table 46 – DZ11 ConfigurationTable 47 – DZ11 Control and Status Register (CSR) – IO Address 760010 |        |

| Table 47 – DZ11 Control and Status Register (CSR) – IO Address 760010                              | )129   |

| Table 48 – DZ11 Receiver Buffer Register (RBUF) – IO Address 760012.                               |        |

| Table 49 - DZ11 Line Parameter Register (LPR) - IO Address 760012                                  | 132    |

| Table 50 – DZ11 Transmit Control Register (TCR) – IO Address 760014        |     |

|----------------------------------------------------------------------------|-----|

| Table 51 – DZ11 Modem Status Register (TDR) – IO Address 760016            | 135 |

| Table 52 – DZ11 Transmit Data Register (TDR) – IO Address 760016           | 135 |

| Table 53 – KMC11 Configuration                                             |     |

| Table 54 – RH11 Configuration                                              | 147 |

| Table 55 – RH11 Controller Register Summary                                | 149 |

| Table 56 – RH11 Control and Status Register #1 (RHCS1) – IO Address 776700 | 150 |

| Table 57 – RH11 Word Count Register (RHWC) – IO Address 776702             |     |

| Table 58 – RH11 Bus Address Register (RHBA) – IO Address 776704            | 152 |

| Table 59 – RH11 Control and Status Register #2 (RHCS2) – IO Address 776710 |     |

| Table 60 – RH11 Data Buffer Register (RHDB) – IO Address 776722            |     |

| Table 61 – RPxx Device Registers                                           | 156 |

| Table 62 – Massbus Register Address Cross Reference                        |     |

| Table 63 – RP Control and Status Register #1 (RPCS1) – IO Address 776700   | 158 |

| Table 64 – RP Disk Address Register (RPDA) – IO Address 776706             |     |

| Table 65 – RP Drive Status Register (RPDS) – IO Address 776712             |     |

| Table 66 – RP Error Register #1 (RPER1) – IO Address 776714                | 164 |

| Table 67 – RP Attention Summary (RPAS) – IO Address 776716                 | 167 |

| Table 68 – RP Look Ahead (RPLA) – IO Address 776720                        |     |

| Table 69 – RP Maintenance Register (RPMR) – IO Address 776724              | 169 |

| Table 70 – RP Drive Type Register (RPDT) – IO Address 776726               | 172 |

| Table 71 – RP Serial Number Register (RPSN) – IO Address 776730            | 173 |

| Table 72 – RP Offset Register (RPOF) – IO Address 776732                   | 174 |

| Table 73 – RP Desired Cylinder (RPDC) – IO Address 776734                  | 175 |

| Table 74 – RP Current Cylinder Register (RPCC) – IO Address 776736         |     |

| Table 75 – RP Error Status Register #2 (RPER2) – IO Address 776740         | 176 |

| Table 76 – RP Error Status Register #1 (RPER3) – IO Address 776742         | 179 |

| Table 77 – RP Error Position Register (RPEC1) – IO Address 776744          |     |

| Table 78 – RP Error Pattern Register (RPEC2) – IO Address 776746           | 180 |

| Table 79 - RM Look Ahead (RMLA) - IO Address 776720                        | 181 |

| Table 80 – RM Maintenance Register (RMMR1) – IO Address 776724 (READ)      | 182 |

| Table 81 - RM Maintenance Register (RMMR1) - IO Address 776724 (WRITE)     | 183 |

| Table 82 – RH Holding Register (RMHR) – IO Address 776736                  | 186 |

| Table 83 – RM Maintenance Register #2 (RMMR2) – IO Address 776740          | 186 |

| Table 84 – RM Error Register #2 (RMER2) – IO Address 776742                | 187 |

| Table 85 - RP06 Seek Timing Simulation                                     | 189 |

| Table 86 – Disk Parameters                                                 | 196 |

| Table 87 - LP20 Register Summary                                           | 200 |

| Table 88 – Control/Status A Register (CSRA) – IO Address 775400            | 201 |

| Table 89 – Control/Status B Register (CSRB) – IO Address 775402            | 207 |

| Table 90 – Bus Address Register (BAR) – IO Address 775404                  |     |

| Table 91 – Byte Count Register (BCTR) – IO Address 775406                  |     |

| Table 92 – Page Count Register (PCTR) – IO Address 775410                  |     |

| Table 93 – RAM Data Register (RAMD) – IO Address 775412                    |     |

| Table 94 – CCTR and CBUF Register                                          |     |

| Table 95 – PDAT and CKSM Registers                                         | 215 |

| Table 96 – Channel Commands                                                |     |

| Table 97 – Slew Commands                                                   |     |

| Table 98 – APRID (BLKI APR) Bit Definitions                                |     |

| Table 99 – WRAPR (CONO APR) Bit Definitions                                |     |

| Table 100 – RDAPR (CONI APR) Bit Definitions                               |     |

|                                                                            |     |

Page 13 22 June 2021

| Table 101 – WRPI (CONO PI) Bit Definitions   | 226 |

|----------------------------------------------|-----|

| Table 102 – RDPI (CONI PI) Bit Definitions   |     |

| Table 103 – WRUBR (DATO PAG) Bit Definitions |     |

| Table 104 – RDUBR (DATI PAG) Bit Definitions |     |

| Table 105 – WREBR (CONO PAG) Bit Definitions |     |

| Table 106 – RDEBR (CONI PAG) Bit Definitions | 232 |

| Table 107 – Diagnostic Status                | 239 |

| Table 108 – SMMON Command Summary            | 245 |

Page 14 22 June 2021

#### 1 Introduction

The Digital Equipment Corporation (DEC) KS10 was a low cost implementation of the popular PDP-10 mainframe computer.

-The goal of this project is to re-implement the KS10 using modern components and technology. This project will retain microcode compatibility with the DEC KS10 - this will increase the chances that this design will behave *exactly* like the DEC KS10 implementation.

The KS10 system, including the Central Processing Unit (CPU), Memory Controller, DZ11 Terminal Multiplexer, RH11 Massbuss Disk Controller, and Console Interface will be implemented in a single Field Programmable Gate Array (FPGA) instead using of boards of discrete logic.

The peripherals will be significantly different: modern peripherals like solid state Secure Digital High-Capacity (SDHC) disk drives will replace rotating magnetic media disk drives and 9-track magtape drives; Universal Serial Bus (USB) and Ethernet interfaces will be provided in addition to standard RS-232 devices.

This document is a compilation of many other documents. It is an attempt to gather all of the relevant information that is required to design this product into one place.

#### 1.1 The DEC KS10

The DEC KS10 was implemented in 1978 using AMD am29xx TTL bit-slice device and 74LSxx SSI and MSI devices. The DEC KS10 had a 6.66 MHz clock cycle.

The DEC KS10 consisted of the following circuit boards:

- 4 board CPU set

- Console based on Intel 8080 microprocessor

- Memory Controller

- 8 Memory boards(64K x 36 with ECC)

- 2 Unibus Adapters

- Unibus-based Disk IO (RH11)

- Unibus-based TTY IO (DZ11)

- Power Supply

The CPU, Console, Memory Controller, and Unibus Adapters boards are all interconnected by the KS10 backplane bus.

#### 1.2 The KS10 FPGA

This document describes an implementation of the DEC KS10 system using modern FPGA technology. The bulk of the logic is contained in a single FPGA. This FPGA requires support from a Console Processor and a memory device. For now, this FPGA implementation assumes a Console Processor with an 8-bit multiplexed address and data bus and it assumes a 36-bit wide Synchronous SRAM memory device. It is expected that this assumption will be revisited as the FPGA design evolves and matures.

The KS10 FPGA currently has a 20.0 MHz clock cycle.

Page 15 22 June 2021

Figure 1 – DEC KS10 (photos from LCM)

Figure 2 – DEC KS10 with Covers Removed (photos from RCIM)

Page 16 22 June 2021

#### 2 The KS10 FPGA Architecture

The following sections describe the KS10 FPGA architecture.

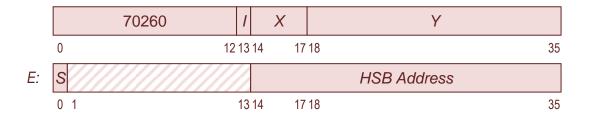

#### 2.1 The KS10 FPGA Design Hierarchy

The KS10 FPGA design hierarchy is illustrated below in Figure 3. The design hierarchy is only loosely based on the actual KS10 implementation. It is intended to describe the relationships between the Verilog modules.

Figure 3 - KS10 FPGA Design Hierarchy

#### 2.2 The KS10 FPGA Design Description

This section does not attempt to describe the operation of the DEC KS10. There are really excellent manuals that cover that sufficiently.

Instead, this section attempts to provide a brief description of the block and to document some of the design changes that were required to convert the original KS10 design into a design that could be implemented in the FPGA.

## 2.2.1 KS10 Bus Arbiter (ARB)

TBD.

### 2.2.2 KS10 Console Interface (CSL)

TBD.

### 2.2.3 KS10 Central Processing Unit (CPU)

The KS10 FPGA is organized a little differently that the DEC KS10. In many cases, the DEC KS10 was organized in a manner to minimize interconnections between circuit boards and to fill boards with circuitry.

The KS10 FPGA has neither of these constraints and attempts to organize logic based on function only.

Page 17 22 June 2021

Figure 4 - KS10 FPGA CPU Block Diagram

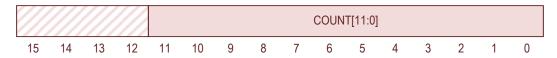

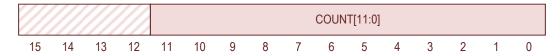

# 2.2.3.1KS10 CPU Interval Timer (TIMER)

The PDP-10 Interval Timer is used by the Monitor to measure run elapsed time, run times, and time-of-day. The timer provides two basic units of time: a 10 microsecond clock where greater precision is required, and a 1 millisecond clock for normal operation.

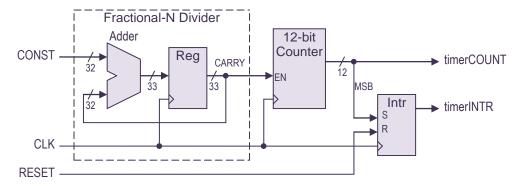

A block diagram of the TIMER module is illustrated below in Figure 5.

Figure 5 - Timer Interface Diagram

The KS10 implements this function by providing a 12-bit timer that is clocked at 4.1 MHz. The RDTIME instruction microcode reads the timer register contents and divides the result by 41 to support the 10 microsecond timing. The 4.1 MHz clock is divided by 4096 in the 12-bit timer which overflows every 0.999024 milliseconds. This timer overflow generates a Timer Interrupt to the CPU. You might note that the timer interrupt actually occurs 0.1 percent fast. This timing error is fixed by the microcode so that the time-of-date service is correct.

Page 18 22 June 2021

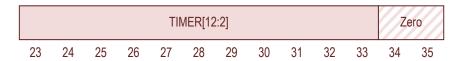

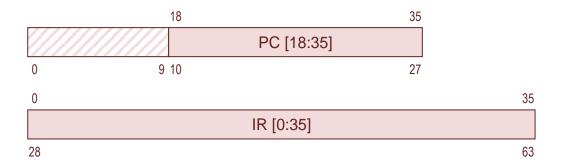

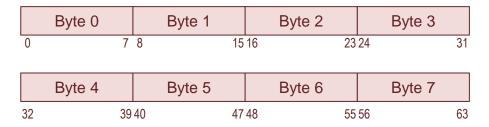

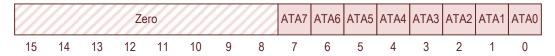

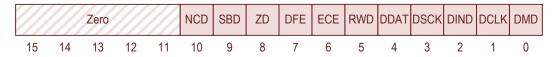

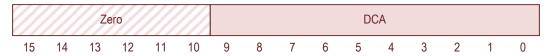

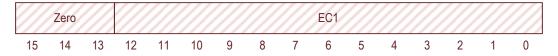

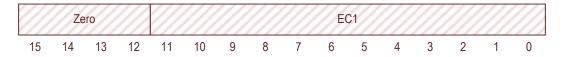

The Interval Timer Register is multiplexed into the CPU via the DBM Multiplexer. In the KS10 implementation (like the KS10), the Interval Timer Register input to the bottom half of the DBM is actually 18-bits wide: there are six bits of padding which are always zero, ten bits of timer, and the two timer LSBs which are always read as zero. This is illustrated below.

Figure 6 - Interval Timer Register

The microcode seems to read all 18-bits that are presented to the DBM and does not perform any masking. Whenever the Interval Timer Register is read, its two least significant bits are ignored so the register's contents approximately represent a count in microseconds. The upper 6 bits are just unused and unnecessary.

The time base value is a 71-bit value that is stored in the RAMFILE. The 12 LSBs of the time base corresponds to the Interval Timer Register. The Write Time Base instruction (WRTIM) can initialize the time base as a number of milliseconds but cannot alter the Interval Timer contents - the 12 LSBs are ignored.

The KS10 FPGA actually does not contain a 4.1 MHz clock source like the DEC KS10. The KS10 FPGA generates the 4.1 MHz clock enable signal using a 32-bit Fractional-N divider operating at 50 MHz. The Fractional-N divider uses an accumulator instead of a divider to create the output signal - the accumulator maintains the fractional time when the count overflows. The accumulator keeps the average output frequency correct although the output will jitter by 20 nanoseconds as the output is still synchronous to the input clock. The 32-bit accumulator was chosen so that the frequency error caused by the Fractional-N Divider implementation is less than the frequency error of the oscillator device. Gates are cheap.

As stated above, a Timer Interrupt is generated when the Interval Timer overflows which is approximately every millisecond. Once asserted, the Timer Interrupt is cleared by a microcode instruction.

A block diagram of the TIMER module is illustrated below.

Figure 7 - Timer Block Diagram

Page 19 22 June 2021

### 2.2.3.2KS10 CPU Virtual Memory Address (VMA)

TBD.

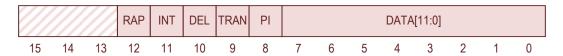

### 2.2.3.3KS10 CPU Priority Interrupt Controller (PI)

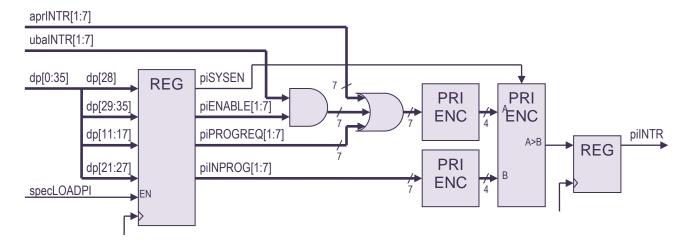

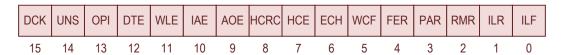

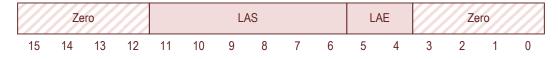

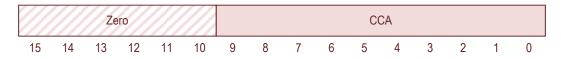

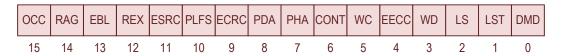

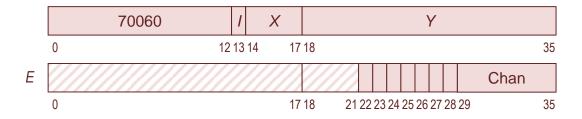

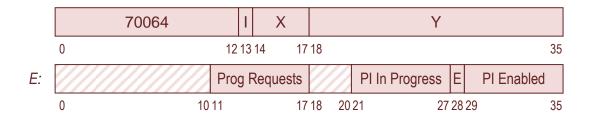

The KS10 Priority Interrupt Controller is responsible for controlling the KS10 CPU's response to interrupt requests. The Priority Interrupt Controller maintains a notion of the Current Interrupt Priority, whether an individual interrupt is enabled and whether the Priority Interrupt Controller is enabled.

When an interrupt input is asserted, the interrupt controller determines if the new interrupt is of a higher priority than the current interrupt state. If it is, and interrupt request to the KS10 CPU is made.

The KS10 supports three interrupt sources which are enumerated below:

- 1. Arithmetic Processor (APR) Interrupts

- 2. IO Bus (UBA) Interrupts

- 3. Software Interrupts (Program Requests).

Each of the interrupt sources can provide 7 interrupt requests. Tb he highest interrupt request priority is interrupt 1; the lowest interrupt request priority is interrupt 7.

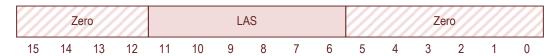

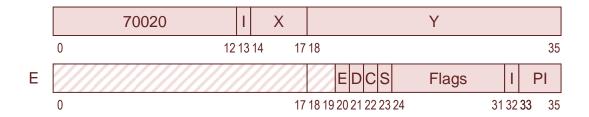

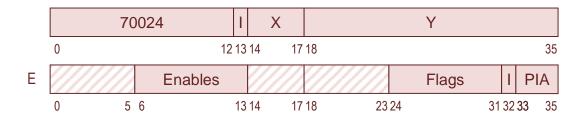

The Priority Interrupt Register state is stored inside the ALU Register 14 (octal). When the "specLOADPI" microcode instruction is executed, the Priority Interrupt Register state is loaded from the ALU into the Priority Interrupt hardware via the DP bus.

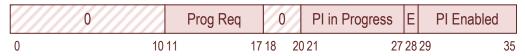

The format of the Priority Interrupt Register is closely resembles the operand of the Executive Mode RDPI instruction.

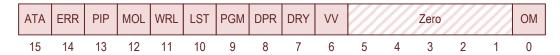

Figure 8 - Priority Interrupt Register Format

Page 20 22 June 2021

Figure 9 - Priority Interrupt Block Diagram

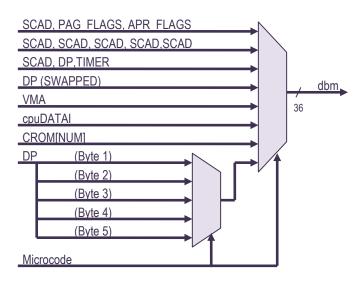

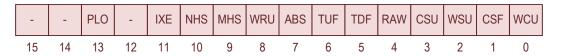

#### 2.2.3.4KS10 CPU DBM Mux (DBM)

The DBM Mux is used to access the SCAD, Timer, VMA Register, Bus Interface, and the Number field of the microcode. It can perform left-half/right-half bus swap and it is also used to do hardware byte selection when the byte is exactly 7 bits.

The DBM Mux is controlled by the microcode DBM Select (DBM\_SEL) field, the byte select mux is controlled by the microcode SPECIAL (DBM\_SPEC) field.

Figure 10 - DBM Block Diagram

Page 21 22 June 2021

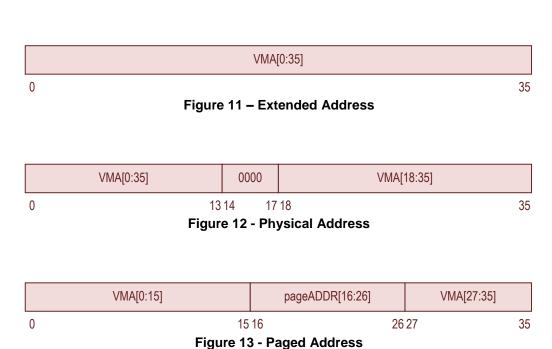

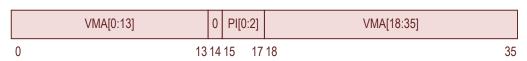

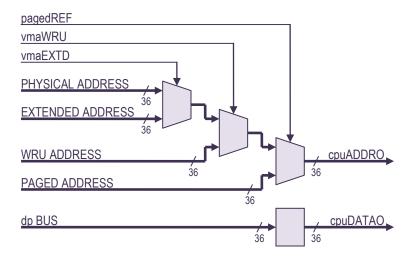

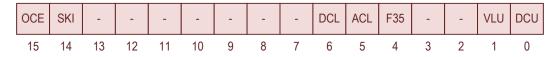

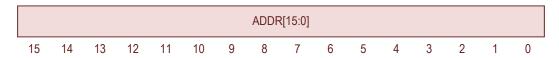

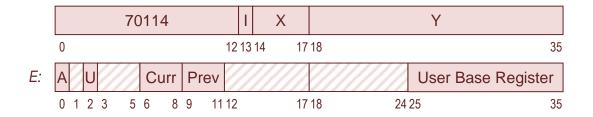

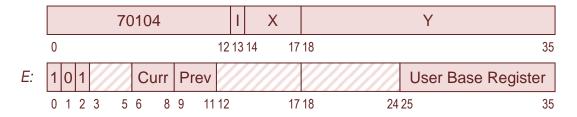

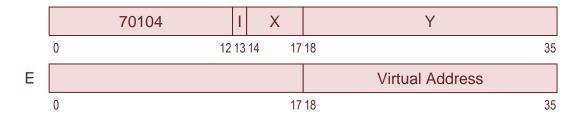

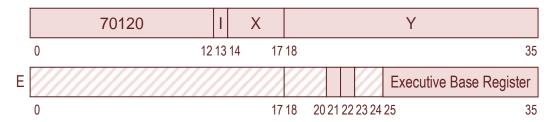

### 2.2.3.5KS10 CPU Backplane Interface (BUS)

The CPU Backplane Interface is the interface between the CPU and the backplane peripherals.

The major function of the backplane is to determine the KS10 addressing mode. The KS10 understands four addressing modes. Namely:

- 1. Extended Address This is a full 20-bit address.

- 2. Physical Address This is a 18-bit address.

- 3. Paged Address This is a 20-bit virtual address.

- 4. WRU Address A "Who Are You (WRU)" cycle is part of the interrupt acknowledge bus cycle. It addresses whatever device is asserting the highest priority interrupt request.

Figure 14 - WRU Address

The Bus Address Multiplexer is simply a 36-bit wide 4-input multiplexer as illustrated below.

Page 22 22 June 2021

Figure 15 - Bus Interface

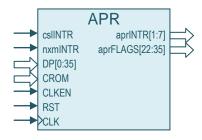

#### 2.2.3.6KS10 CPU Arithmetic Processor Flags (APR)

The APR block manages the arithmetic processor flags. A block diagram of the APR module is illustrated below in Figure 16.

Figure 16 - APR Interface Diagram

The KS10 FPGA APR circuitry is implemented fairly closely to the DEC KS10 implementation.

The Executive Instructions that Control the APR are described in Section 15.1.1.

The aprINTR[1:7] outputs are routed to the Priority Interrupt (PI) block inputs.

The APR register bits are defined below in Table 1.

Page 23 22 June 2021

| Table 1 – APR Flags |                                                                                                                                                                                                                                     |  |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit(s)              | Description                                                                                                                                                                                                                         |  |  |

| 22                  | Trap enable status. This bit is asserted when traps are enabled.                                                                                                                                                                    |  |  |

| 23                  | Page enable. This bit is asserted when paging enabled.                                                                                                                                                                              |  |  |

| 24                  | APR flag 24.  This flag had no function on the KS10 but can be used as a software interrupt.  This flag can be set or cleared by the microcode.                                                                                     |  |  |

| 25                  | Interrupt to KS10 console.  This bit is asserted when the KS10 wants to interrupt the console microcontroller.  This flag can be set or cleared by the microcode.                                                                   |  |  |

| 26                  | Power fail interrupt.  The power fail detection is not implemented so this flag is never set automatically.  This flag can be set or cleared by the microcode.                                                                      |  |  |

| 27                  | NXM interrupt.  This flag is asserted automatically when non-existent memory is accessed.  This flag can be set or cleared by the microcode.                                                                                        |  |  |

| 28                  | Uncorrectable memory error.  Uncorrectable memory error (ECC) detection is not implemented so this flag is never set automatically.  This flag can be set or cleared by the microcode.                                              |  |  |

| 29                  | Correctable memory error Correctable memory error (ECC) detection is not implemented so this flag is never set automatically. This flag can be set or cleared by the microcode                                                      |  |  |

| 30                  | Interval timer interrupt The Interval Timer is implemented in microcode so this bit is so this bit is not set automatically. The microcode asserts this bit every 1.0 millisecond. This flag can be set or cleared by the microcode |  |  |

| 31                  | Interrupt from KS10 console  The Console Interrupt is implemented in microcode so this bit is not set automatically.  This flag can be set or cleared by the microcode                                                              |  |  |

Page 24 22 June 2021

| Table 1 – APR Flags |                   |  |  |

|---------------------|-------------------|--|--|

| Bit(s)              | Description       |  |  |

| 32                  | Interrupt request |  |  |

| 33                  | Always set to 1   |  |  |

| 34                  | Always set to 1   |  |  |

| 35                  | Always set to 1   |  |  |

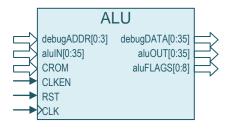

#### 2.2.3.7KS10 CPU Arithmetic Logic Unit (ALU)

A block diagram of the ALU is illustrated below in Figure 17.

Figure 17 - ALU Interface Diagram

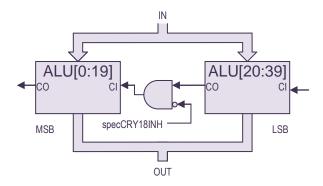

The DEC KS10 ALU implementation uses ten cascaded AM2901 4-bit processor slices. Some quick study showed that this did not work well with an FPGA implementation. Most FPGAs have optimized (very fast) carry logic that is provided to support counters and adders. This carry logic is much faster than the AM2902 parallel carry devices that supported the AM2901 slices in the KS10.

It turns out that the Verilog (and VHDL) synthesis tools could not infer that there was a single 40-bit carry chain from the Register Transfer Logic (RTL) description of the ten cascaded 4-bit slices. The resulting ALU was very slow.

One of the architectural features of the PDP10 ALU is the requirement to operate as a single 36-bit ALU or to operate as two independent 18-bit ALUs with no carry between the lower 18-bits and upper 18-bits. The DEC KS10 inserts an "AND Gate" in the middle of the carry string to implement this feature. This is illustrated below in Figure 18.

Page 25 22 June 2021

Figure 18 - DEC KS10 ALU Implementation

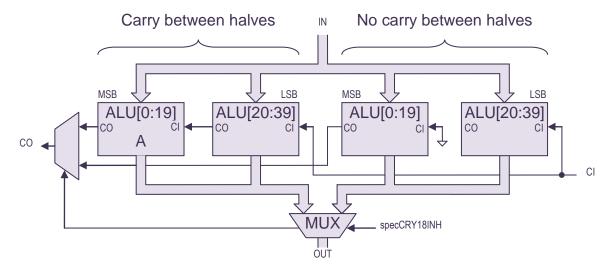

In the FPGA implementation, maintaining the integrity of the carry chain is very important to the speed of the ALU.

To that end, the KS10 FPGA ALU is implemented both ways: as a single 40-bit wide ALU and as two independent 20-bit ALUs. Gates are cheap. The two different types of operations occur in parallel and are selected at the module output. This is illustrated below in Figure 19.

Figure 19 - KS10 FPGA ALU Implementation

Both of these ALU operations occur in parallel. Instead of the microcode enabling the carry between the two halves of the ALU, the microcode selects between the 40-bit ALU with the carry between the two halves and the 40-bit ALU with no carry between the two halves. This is illustrated in Figure 18 above.

This saves 'cutting' the 40-bit ALU carry chain in the middle and maintains the ALU speed.

This design change actually makes the description of the KS10 FPGA much simpler than the alternative. The operation of the 40-bit Q-shifter and the 40-bit F-shifter is much more visible than in the original DEC KS10 design.

So why is the ALU 40-bits wide instead of 36-bits?

Page 26 22 June 2021

Notice that the ALU is sign extended by two bits on the left, and zero padded by two bits on the right.

The ALU is implemented with 4-bit wide slices. This implementation gives the hardware access to the CRY2 (Carry 2) signal which is available at the interface between the first and second ALU chip. If this was implemented as a 36-bit wide ALU, this signal would be buried inside the am2901 chip and not accessible. There may be other signals also.

#### 2.2.3.8KS10 CPU Microsequencer (USEQ)

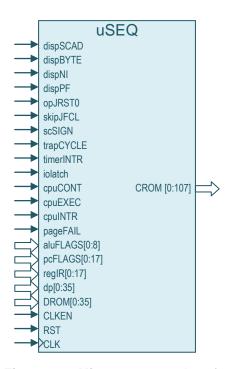

The microsequencer is a device that sequences through the microcode. The microsequencer has various inputs that control the execution sequence but the only output from the microsequencer block is the Control ROM which provides the KS10 microcode. This microcode is used to control the various blocks of the KS10 hardware.

The interfaces to the microsequencer are captured below in Figure 20.

Figure 20 - Microsequencer Interface

The DEC KS10 CPU was implemented using 2048 words of 108-bit wide <a href="https://horizontal.microcode">horizontal microcode</a> (as opposed to <a href="https://www.vertical.microcode">words</a>). The microarchitecture supports 12-bit addressing of microcode (4096 words) but the DEC KS10 only implemented 2048 words microcode. The KS10 FPGA implements all 4096 words of microcode.

The microcode begins execution at address 0000. The microsequencer continuously re-executes instruction at address 0000 while the RESET signal is asserted and will only execute the next instruction after the RESET signal has been negated. This design assumes that the RESET negation is synchronized to the clock and that the RESET signal is asserted for a few clock cycles minimum to ensure that the instruction at address 0000 has been executed at least once.

Page 27 22 June 2021

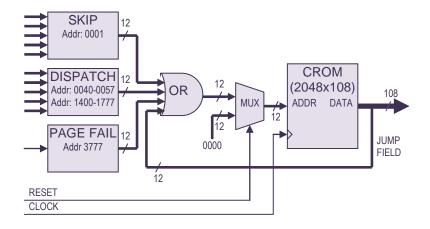

The Page Fail hardware is hard coded to vector to the Page Fail handler address. The Page Fail vector hardware is a bunch of "OR Gates" which just assert all of the microcode ROM address bits - therefore the Page Fail handler is located at 3777 (octal) for the DEC KS10 and 7777 (octal) for the KS10 FPGA. In general, the hardware addressing (Reset, Page Fail, Skip, and Dispatch) must match the addresses in the microcode. Therefore the hardware cannot be modified without appropriate changes to the microcode.

The addressing the microsequencer is very minimalistic. Whereas a modern implementation might use a multiplexer to control the addressing, the KS10 uses simple "OR" gates. Therefore the SKIP, DISPATCH, and PAGE FAIL logic can only modify the addressing by setting bits – never clearing address bits.

On a normal microcode instruction, the SKIP, DISPATCH, and PAGE FAIL addresses are zero. The Control ROM supplies the next address from the microcode "Jump" field.

When a SKIP is to be performed (a primitive conditional branch-like instruction), the SKIP entity conditionally supplies an address of 0000 or 0001. This conditionally sets the LSB of the address. Of course the microcode must be designed such that the two destination addresses are appropriate.

The DISPATCH is similar to a SKIP except that an N-way branch can be executed. Again, the microcode must be designed such that all of the possible destination addresses are correct. The microcode uses a 512-way branch to quickly decode instruction opcodes, and additional N-way branches to quickly decode addressing modes. The opcode dispatch address is provided by the Dispatch ROM (DROM) – which is not part of the microsequencer illustrated below.

The PAGE FAIL always vectors the microcode to address 7777.

Figure 21 – Microsequencer Block Diagram

### 2.2.3.8.1 KS10 CPU Microsequencer Control ROM (CROM)

The Control ROM contains the executable microcode of the microsequencer.

This module of the KS10 FPGA microsequencer is implemented significantly different than the DEC KS10 circuit but performs exactly the same function.

Page 28 22 June 2021

The DEC KS10 implementation has several implementation issues which must be addressed in an FPGA design. These are:

- 1. The microcode is stored in a RAM which must be loaded by the console processor at power-up. This is complicated and unnecessary. The FPGA can provide ROM for this function.

- 2. The Control RAM is asynchronous. The FPGA provides synchronous memory.

In the KS10 FPGA, the Control RAM is replaced by a synchronous ROM which is not writeable. This simplifies the boot procedure. The Control RAM microcode is post-processed to remove unused fields and rearrange the bits (I assume to optimize the hardware design). For example, the microcode listing defines a 108-bit wide microcode word whereas the hardware is only 96-bits wide. In the KS10 FPGA, the post-processing step has been elided as it is unnecessary. The Verilog synthesis tool is smart enough to identify and remove unused (or constant) data fields in the ROM. Also, the post-processing also adds parity which is not really necessary for the FPGA.

The DEC KS10 microsequencer had a 12-bit address which could have supported 4096 words of microcode; however, only half of the memory was actually implemented in the production hardware. Unfortunately the microcode grew to be larger 2048 words. Therefore DEC shipped three version of the microcode – each matching a specific application. The various types of microcode are detailed below in Table 2.

Fortunately all three versions of microcode were derived from a single codebase using conditional compiles to remove microcode as required.

It was desirable for the KS10 FPGA to have the microcode in ROM. The additional microcode memory allowed the KS10 FPGA to support a functional superset of all of the DEC microcode.

Implementing the new version of microcode only required some minor modifications to the conditional compiles and some new build command files. A small design change was required to move the PAGE-FAIL entry point from 3777 (octal) to 7777 (octal).

When a page failure occurs, the PAGE-FAIL address is generated in the hardware by setting all of the microcode address bits to one (using 12 OR gates). Because the MSB of the address was unused and the microcode was limited to 2048 words, this created a PAGE-FAIL entry point of 3777 (octal) in the microcode. Once the full microcode memory was implemented, the correct entry point of 7777 (octal) was exposed to the microcode.

| Table 2 – KS10 Microcode Variations |                                                                                                              |  |  |  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|

| FILENAME                            | Description                                                                                                  |  |  |  |

| KS10.MCR                            | Diagnostic microcode. Includes TOPS10 paging and TOPS20 paging but does not include the UBABLT instructions. |  |  |  |

| T10KI.MCR                           | TOPS10 microcode. Includes TOPS10 paging and UBABLT instructions but does not include TOPS20 paging.         |  |  |  |

| T10KL.MCR                           | TOPS20 microcode. Includes TOPS20 paging and UBABLT instructions but does not include TOPS10 paging.         |  |  |  |

| CRAM4K.MCR                          | *NEW* Unified microcode. Includes TOPS10 paging, TOPS20 paging, and UBABLT instructions.                     |  |  |  |

Page 29 22 June 2021

The Control ROM contents are extracted from the microcode listing file by an AWK script.

#### 2.2.3.8.2 KS10 CPU Microsequencer Dispatch ROM (DROM)

The Dispatch ROM maps the instruction (from the Instruction Register) to the address of microcode in the Control ROM that decodes and executes that instruction.

The DEC KS10 implementation of the Dispatch ROM is problematic for an FPGA implementation because the DROM in the KS10 is asynchronous and FPGA memories are synchronous.

Fortunately the DROM is addressed by the Instruction Register (IR) which *is* loaded synchronously. Therefore we can absorb a copy of the OPCODE portion of IR directly into Dispatch ROM addressing.

Simply put: when we load the IR, we also simultaneously and synchronously lookup the contents of the Dispatch ROM.

The Dispatch ROM is a 512 x 36 bit synchronous ROM.

As with the DEC KS10 Control ROM, the DEC KS10 Dispatch ROM contents is post-processed to remove unused fields and rearrange the bits. In the KS10 FPGA implementation, the Dispatch ROM contents match the format of the microcode listing and the post-processing step is elided. Again, the Verilog compiler is smart enough to remove unused microcode fields from the ROM

The Dispatch ROM contents are extracted from the microcode listing file by a simple AWK script.

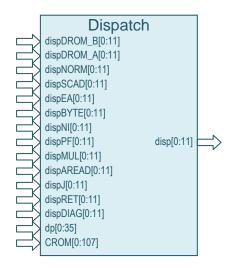

#### 2.2.3.8.3 KS10 CPU Microsequencer Dispatch Logic (DISPATCH)

As stated above, the dispatch logic allows the microcode to perform an N-way branch based on a set of inputs.

The dispatch block is a large multiplexer that is controlled by the microcode that provides a 12-bit dispatch address output.

The multiplexer is broken into two halves: the upper 8-bits are controlled independently from the lower 4-bits. This segregation into halves provides many 16-way dispatches and a few larger (up to 512-way) dispatches.

The instruction opcode decode dispatch is a 512-way dispatch where the address is supplied by the dispatch ROM.

The KS10 FPGA dispatch block replicates the DEC KS10 dispatch logic with one minor exception. The DEC KS10 dispatch logic was fairly convoluted (and very difficult to understand) in order to minimize logic and limit the size of the dispatch ROM.

For example, the instruction opcode decode dispatch is constrained to be in the address range between o1400 and o1700 in the microcode. Therefore in the DEC KS10 design during the opcode decode dispatch, the logic was hardwired to generate addresses in this address range. In the KS10 FPGA, the entire dispatch address is stored in the dispatch ROM. The logic synthesis tool is 'smart enough' to determine that the data contents of those ROM bits is constant for all addresses, remove the data from the ROM, and replace the ROM contents with hardwired logic just like the DEC KS10 – except that the design intent is much more evident in the FPGA version.

Changes to the dispatch logic would require changes to the microcode.

Page 30 22 June 2021

Figure 22 - Dispatch Interface Diagram

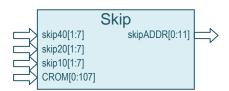

#### 2.2.3.8.4 KS10 CPU Microsequencer Skip Logic (SKIP)

The skip logic provides a means for the microcode to perform a conditional jump operation based on a Boolean value.

Figure 23 - Skip Interface Diagram

The skipADDR output is always either 0000 (octal) for "no skip" condition or 0001 (octal) for a "skip" condition.

Skips always occur from even addresses to odd addresses because the SKIP block can only OR the address. It is not a multiplex operation.

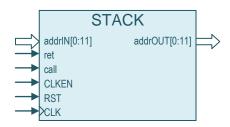

### 2.2.3.8.5 KS10 CPU Microsequencer Call/Return Stack (STACK)

This stack provides a mechanism for the microcode to 'call' and 'return' from microcode functions. The microsequencer stack is implemented quite a bit differently than the KS10 simply because the FPGA provides Dual Port RAMs.

The addrOUT 'read' port of the Dual Port RAM provides the return address. This port always points to the top-of-stack and can always be read independently.

The addrIN 'write' port of the Dual Port RAM is used to store the next 'call' address. This port always points to the address past the top-of-stack and can always be written independently.

An interface diagram of the STACK module is illustrated below in Figure 24 while a block diagram is illustrated below in Figure 25.

Page 31 22 June 2021

Figure 24 - Stack Interface Diagram

Figure 25 - Stack Block Diagram

When the 'call' input to the block is asserted, the 'call' address is stored, the stack pointer is incremented and the return address automatically becomes available at the new top-of-stack.

When the 'ret' (return) input to the block is asserted, the stack pointer is decremented. The return address is always available at the addrOUT[0:11] port.

This implementation saves all the KS10 logic to dynamically change RAM address depending if a 'call' or 'return' instruction is being processed. It also allows the stack to always update in a single clock cycle.

The 'call' and 'return' operation of the microcode is quite a bit different than modern computers. The microsequencer stores the address of the 'call' instruction on the stack. The 'return' instruction must include a dispatch offset to the address in order to return to an instruction after the 'call' instruction.

When a Page Fail exception occurs, the microcode vectors to the 'Page Fail' handler. When the Page Fail handler code has completed execution, the microsequencer returns to the microcode instruction (the read or write operation that caused the Page Fail exception) and re-executes that instruction.

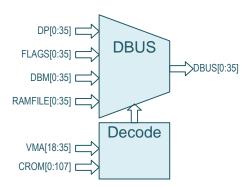

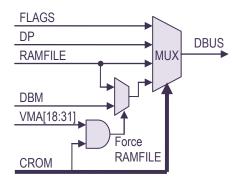

#### 2.2.3.9KS10 CPU DBUS

The DBUS module is essentially a 36-bit wide 4-to-1 multiplexer. The DBUS multiplexer selects between the FLAGS, the ALU Output (DP), the DBM Multiplexer, and the RAMFILE. On a read operation, the DBUS Multiplexer also selects between the RAMFILE (where the ACs are stored) if an AC is being read and memory if an AC is not being read.

Page 32 22 June 2021

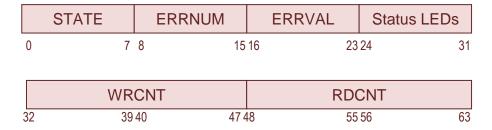

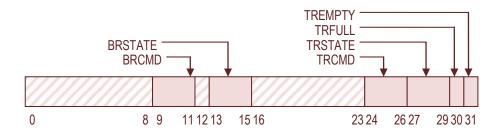

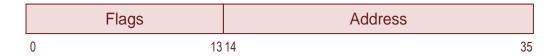

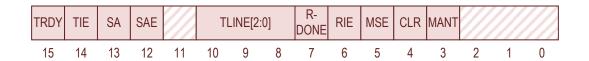

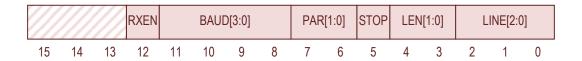

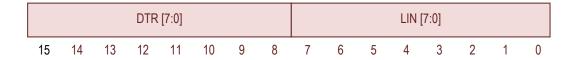

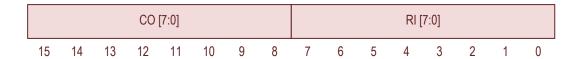

Figure 26 - DBUS Interface Diagram