# Compute Express Link m

# Compute Express Link<sup>TM</sup> (CXL<sup>TM</sup>)

Specification

*October 2020* Revision 2.0

### LEGAL NOTICE FOR THIS PUBLICLY-AVAILABLE SPECIFICATION FROM COMPUTE EXPRESS LINK CONSORTIUM, INC.

## © 2019-2020 COMPUTE EXPRESS LINK CONSORTIUM, INC. ALL RIGHTS RESERVED.

This CXL **Specification Revision 1.1** (this "<u>CXL Specification</u>" or this "<u>document</u>") is owned by and is proprietary to Compute Express Link Consortium, Inc., a Delaware nonprofit corporation (sometimes referred to as "<u>CXL</u>" or the "<u>CXL Consortium</u>" or the "<u>Company</u>") and/or its successors and assigns.

## NOTICE TO USERS WHO ARE MEMBERS OF THE CXL CONSORTIUM:

If you are a Member of the CXL Consortium (sometimes referred to as a "<u>CXL Member</u>"), and even if you have received this publicly-available version of this CXL Specification after agreeing to CXL Consortium's Evaluation Copy Agreement (a copy of which is available <u>typs://www.computeexpresslink.org/download-the-specification</u>, each such CXL Member must also be in compliance with all of the following CXL Consortium documents, policies and/or procedures (collectively, the "<u>CXL Governing Documents</u>") in order for such CXL Member's use and/or implementation of this CXL Specification to receive and enjoy all of the rights, benefits, privileges and protections of CXL Consortium membership: (i) CXL Consortium's Intellectual Property Policy; (ii) CXL Consortium's Bylaws; (iii) any and all other CXL Consortium policies and procedures; and (iv) the CXL Member's Participation Agreement.

## NOTICE TO NON-MEMBERS OF THE CXL CONSORTIUM:

If you are **not** a CXL Member and have received this publicly-available version of this CXL Specification, your use of this document is subject to your compliance with, and is limited by, all of the terms and conditions of the CXL Consortium's Evaluation Copy Agreement (a copy of which is available at <a href="https://www.computeexpresslink.org/download-the-specification">https://www.computeexpresslink.org/download-the-specification</a>).

In addition to the restrictions set forth in the CXL Consortium's Evaluation Copy Agreement, any references or citations to this document must acknowledge the Compute Express Link Consortium, Inc.'s sole and exclusive copyright ownership of this CXL Specification. The proper copyright citation or reference is as follows: "© 2019-2020 COMPUTE EXPRESS LINK CONSORTIUM, INC. ALL RIGHTS RESERVED." When making any such citation or reference to this document you are not permitted to revise, alter, modify, make any derivatives of, or otherwise amend the referenced portion of this document in any way without the prior express written permission of the Compute Express Link Consortium, Inc.

Except for the limited rights explicitly given to a non-CXL Member pursuant to the explicit provisions of the CXL Consortium's Evaluation Copy Agreement which governs the publicly-available version of this CXL Specification, nothing contained in this CXL Specification shall be deemed as granting (either expressly or impliedly) to any party that is <u>not</u> a CXL Member: (ii) any kind of license to implement or use this CXL Specification or any portion or content described or contained therein, or any kind of license in or to any other intellectual property owned or controlled by the CXL Consortium, including without limitation any trademarks of the CXL Consortium.; or (ii) any benefits and/or rights as a CXL Member under any CXL Governing Documents.

## LEGAL DISCLAIMERS FOR ALL PARTIES:

THIS DOCUMENT AND ALL SPECIFICATIONS AND/OR OTHER CONTENT PROVIDED HEREIN IS PROVIDED ON AN "AS IS" BASIS. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, COMPUTE EXPRESS LINK CONSORTIUM, INC. (ALONG WITH THE CONTRIBUTORS TO THIS DOCUMENT) HEREBY DISCLAIM ALL REPRESENTATIONS, WARRANTIES AND/OR COVENANTS, EITHER EXPRESS OR IMPLIED, STATUTORY OR AT COMMON LAW, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, VALIDITY, AND/OR NON-INFRINGEMENT.

In the event this CXL Specification makes any references (including without limitation any incorporation by reference) to another standard's setting organization's or any other party's ("<u>Third Party</u>") content or work, including without limitation any specifications or standards of any such Third Party ("<u>Third Party Specification</u>"), you are hereby notified that your use or implementation of any Third Party Specification: (i) is not governed by any of the CXL Governing Documents; (ii) may require your use of a Third Party's patents, copyrights or other intellectual property rights, which in turn may require you to independently obtain a license or other consent from that Third Party in order to have full rights to implement or use that Third Party Specification; and/or (iii) may be governed by the intellectual property policy or other policies or procedures of the Third Party which owns the Third Party Specification. Any trademarks or service marks of any Third Party which may be referenced in this CXL Specification is owned by the respective owner of such marks.

## NOTICE TO ALL PARTIES REGARDING THE PCI-SIG UNIQUE VALUE PROVIDED IN THIS CXL SPECIFICATION:

NOTICE TO USERS: THE UNIQUE VALUE THAT IS PROVIDED IN THIS CXL SPECIFICATION IS FOR USE IN VENDOR DEFINED MESSAGE FIELDS, DESIGNATED VENDOR SPECIFIC EXTENDED CAPABILITIES, AND ALTERNATE PROTOCOL NEGOTIATION ONLY AND MAY NOT BE USED IN ANY OTHER MANNER, AND A USER OF THE UNIQUE VALUE MAY NOT USE THE UNIQUE VALUE IN A MANNER THAT (A) ALTERS, MODIFIES, HARMS OR DAMAGES THE TECHNICAL FUNCTIONING, SAFETY OR SECURITY OF THE PCI-SIG ECOSYSTEM OR ANY PORTION THEREOF, OR (B) COULD OR WOULD REASONABLY BE DETERMINED TO ALTER, MODIFY, HARM OR DAMAGE THE TECHNICAL FUNCTIONING, SAFETY OR SECURITY OF THE PCI-SIG ECOSYSTEM OR ANY PORTION THEREOF (FOR PURPOSES OF THIS NOTICE, "**PCI-SIG ECOSYSTEM**" MEANS THE PCI-SIG SPECIFICATIONS, MEMBERS OF PCI-SIG AND THEIR ASSOCIATED PRODUCTS AND SERVICES THAT INCORPORATE ALL OR A PORTION OF A PCI-SIG SPECIFICATION AND EXTENDS TO THOSE PRODUCTS AND SERVICES INTERFACING WITH PCI-SIG MEMBER PRODUCTS AND SERVICES).

## **Contents**

| 1.0 | Intro | duction        |                                                    | 27 |

|-----|-------|----------------|----------------------------------------------------|----|

|     | 1.1   | Audience       | e                                                  | 27 |

|     | 1.2   | Termino        | logy / Acronyms                                    | 27 |

|     | 1.3   |                | e Documents                                        |    |

|     | 1.4   | Motivatio      | on and Overview                                    |    |

|     |       | 1.4.1          | Compute Express Link                               |    |

|     |       |                | Flex Bus                                           |    |

|     | 1.5   |                | Link Features                                      |    |

|     | 1.6   |                | Layering Overview                                  |    |

|     | 1.7   |                | nt Scope                                           |    |

| 2.0 |       |                | ss Link System Architecture                        |    |

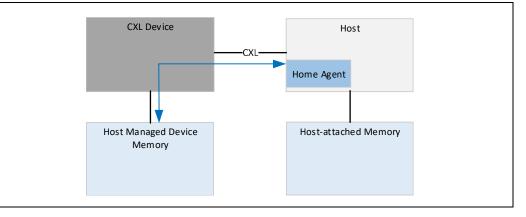

|     | 2.1   |                | XL Device                                          |    |

|     | 2.2   | •••            | XL Device                                          |    |

|     |       | 2.2.1          | Bias Based Coherency Model                         |    |

|     |       |                | 2.2.1.1 Host Bias<br>2.2.1.2 Device Bias           |    |

|     |       |                | 2.2.1.3 Mode Management                            |    |

|     |       |                | 2.2.1.4 Software Assisted Bias Mode Management     |    |

|     |       |                | 2.2.1.5 Hardware Autonomous Bias Mode Management   |    |

|     | 2.3   | Type 3 C       | XL Device                                          |    |

|     | 2.4   | Multi Log      | gical Device                                       | 44 |

|     |       | 2.4.1          | LD-ID for CXL.io and CXL.mem                       | 45 |

|     |       |                | 2.4.1.1 LD-ID for CXL.mem                          |    |

|     |       |                | 2.4.1.2 LD-ID for CXL.io                           |    |

|     |       |                | Pooled Memory Device Configuration Registers       |    |

|     | 2.5   |                | ice Scaling                                        |    |

| 3.0 |       |                | ss Link Transaction Layer                          |    |

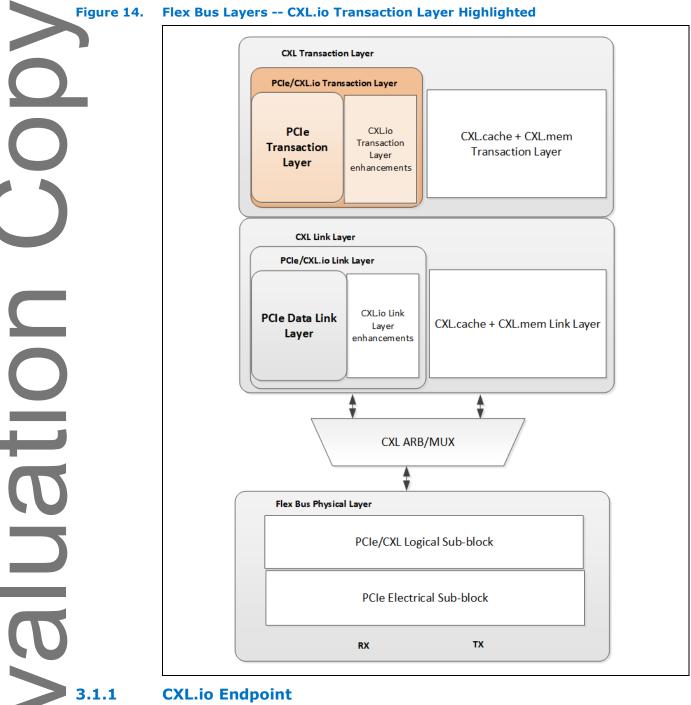

|     | 3.1   |                |                                                    |    |

|     |       |                | CXL.io Endpoint                                    |    |

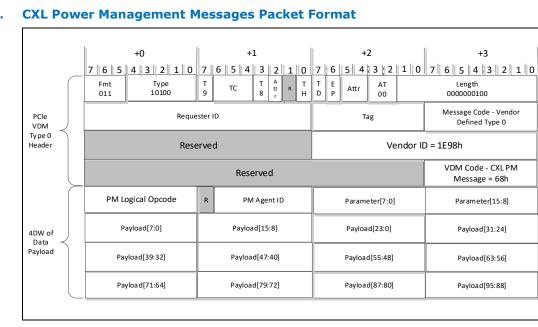

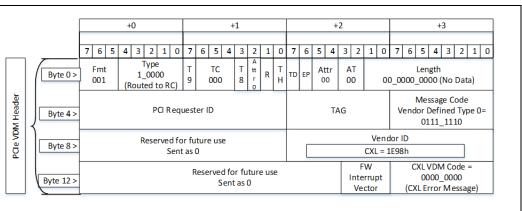

|     |       | 3.1.2          | CXL Power Management VDM Format                    |    |

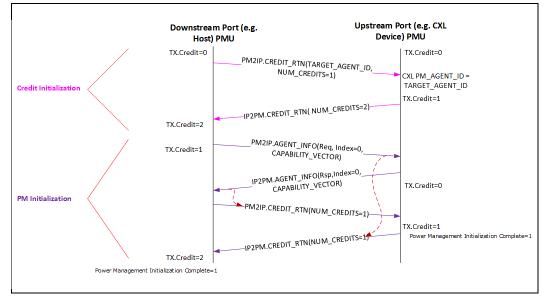

|     |       |                | 3.1.2.1 Credit and PM Initialization               |    |

|     |       |                | CXL Error VDM Format                               |    |

|     |       |                | Optional PCIe Features Required for CXL            |    |

|     |       | 3.1.5          | Error Propagation                                  |    |

|     |       | 3.1.6<br>3.1.7 | Memory Type Indication on ATS<br>Deferrable Writes |    |

|     | 3.2   | -              |                                                    |    |

|     | 5.2   | 3.2.1          | Overview                                           |    |

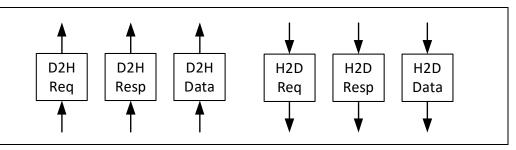

|     |       | -              | CXL.cache Channel Description                      |    |

|     |       | 5.2.2          | 3.2.2.1 Channel Ordering                           |    |

|     |       |                | 3.2.2.2 Channel Crediting                          |    |

|     |       | 3.2.3          | CXL.cache Wire Description                         |    |

|     |       |                | 3.2.3.1 D2H Request                                |    |

|     |       |                | 3.2.3.2 D2H Response                               |    |

|     |       |                | 3.2.3.3 D2H Data                                   | 61 |

|     |       |                | 3.2.3.4 H2D Request                                | 62 |

|     |       |                | 3.2.3.5 H2D Response                               |    |

|     |       |                | 3.2.3.6 H2D Data                                   |    |

|     |       | 3.2.4          | CXL.cache Transaction Description                  |    |

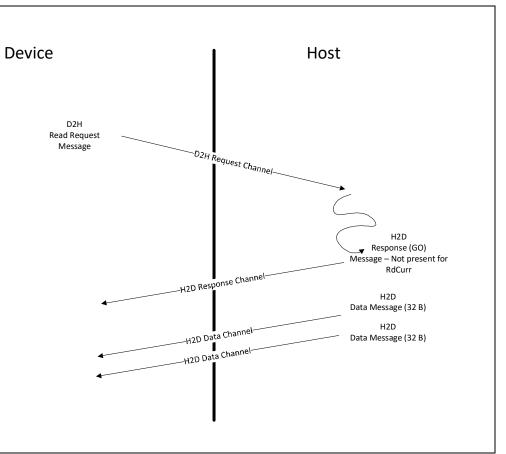

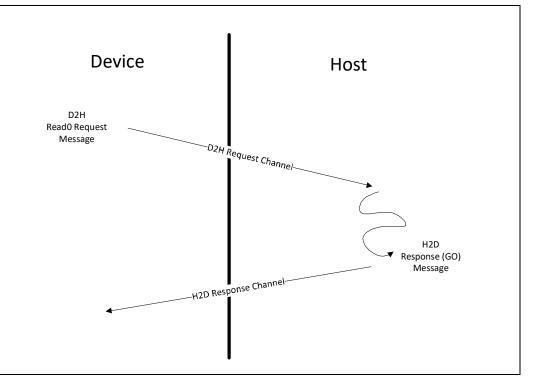

|     |       |                | 3.2.4.1 Device to Host Requests                    |    |

|     |       |                | 3.2.4.2 Device to Host Response                    |    |

|     |          |       | <ul><li>3.2.4.3 Host to Device Requests</li><li>3.2.4.4 Host to Device Response</li></ul>                     |          |

|-----|----------|-------|---------------------------------------------------------------------------------------------------------------|----------|

|     |          | 3.2.5 | Cacheability Details and Request Restrictions                                                                 |          |

|     |          | 5.E.5 | 3.2.5.1 GO-M Responses                                                                                        |          |

|     |          |       | 3.2.5.2 Device/Host Snoop-GO-Data Assumptions                                                                 |          |

|     |          |       | 3.2.5.3 Device/Host Snoop/WritePull Assumptions                                                               | 79       |

|     |          |       | 3.2.5.4 Snoop Responses and Data Transfer on CXL.cache Evicts                                                 |          |

|     |          |       | 3.2.5.5 Multiple Snoops to the Same Address                                                                   |          |

|     |          |       | 3.2.5.6 Multiple Reads to the Same Cache Line                                                                 |          |

|     |          |       | 3.2.5.7 Multiple Evicts to the Same Cache Line                                                                |          |

|     |          |       | 3.2.5.8 Multiple Write Requests to the Same Cache Line                                                        |          |

|     |          |       | <ul><li>3.2.5.9 Normal Global Observation (GO)</li><li>3.2.5.10 Relaxed Global Observation (FastGO)</li></ul> | 80<br>01 |

|     |          |       | 3.2.5.10 Relaxed Global Observation (FastGO)                                                                  |          |

|     |          |       | 3.2.5.12 Memory Type on CXL.cache                                                                             |          |

|     |          |       | 3.2.5.13 General Assumptions                                                                                  |          |

|     |          |       | 3.2.5.14 Buried Cache State Rules                                                                             |          |

|     | 3.3      | CXL.m | em                                                                                                            |          |

|     | 0.0      | 3.3.1 | Introduction                                                                                                  |          |

|     |          | 3.3.2 | QoS Telemetry for Memory                                                                                      |          |

|     |          | 0.012 | 3.3.2.1 QoS Telemetry Overview                                                                                |          |

|     |          |       | 3.3.2.2 Reference Model for Host Support of QoS Telemetry                                                     |          |

|     |          |       | 3.3.2.3 Memory Device Support for QoS Telemetry                                                               |          |

|     |          | 3.3.3 | M2S Request (Req)                                                                                             |          |

|     |          | 3.3.4 | M2S Request with Data (RwD)                                                                                   |          |

|     |          | 3.3.5 | S2M No Data Response (NDR)                                                                                    |          |

|     |          | 3.3.6 | S2M Data Response (DRS)                                                                                       |          |

|     |          | 3.3.7 | Forward Progress and Ordering Rules                                                                           |          |

|     | 3.4      |       | ction Ordering Summary                                                                                        |          |

|     | 3.5      |       | ction Flows to Device-Attached Memory                                                                         |          |

|     |          | 3.5.1 | Flows for Type 1 and Type 2 Devices                                                                           |          |

|     |          |       | 3.5.1.1 Notes and Assumptions                                                                                 |          |

|     |          |       | 3.5.1.2 Requests from Host                                                                                    |          |

|     |          |       | 3.5.1.3 Requests from Device in Host and Device Bias                                                          |          |

|     |          | 3.5.2 | Type 2 and Type 3 Memory Flows                                                                                |          |

|     |          |       | 3.5.2.1 Speculative Memory Read                                                                               |          |

|     | 3.6      | Flows | for Type 3 Devices                                                                                            |          |

|     | <b>C</b> |       |                                                                                                               |          |

| 4.0 | -        |       | ress Link Link Layers                                                                                         |          |

|     | 4.1      |       | Link Layer                                                                                                    |          |

|     | 4.2      |       | em and CXL.cache Common Link Layer                                                                            |          |

|     |          | 4.2.1 | Introduction                                                                                                  |          |

|     |          | 4.2.2 | 0                                                                                                             |          |

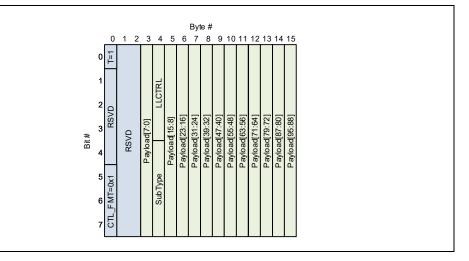

|     |          | 4.2.3 | Slot Format Definition                                                                                        |          |

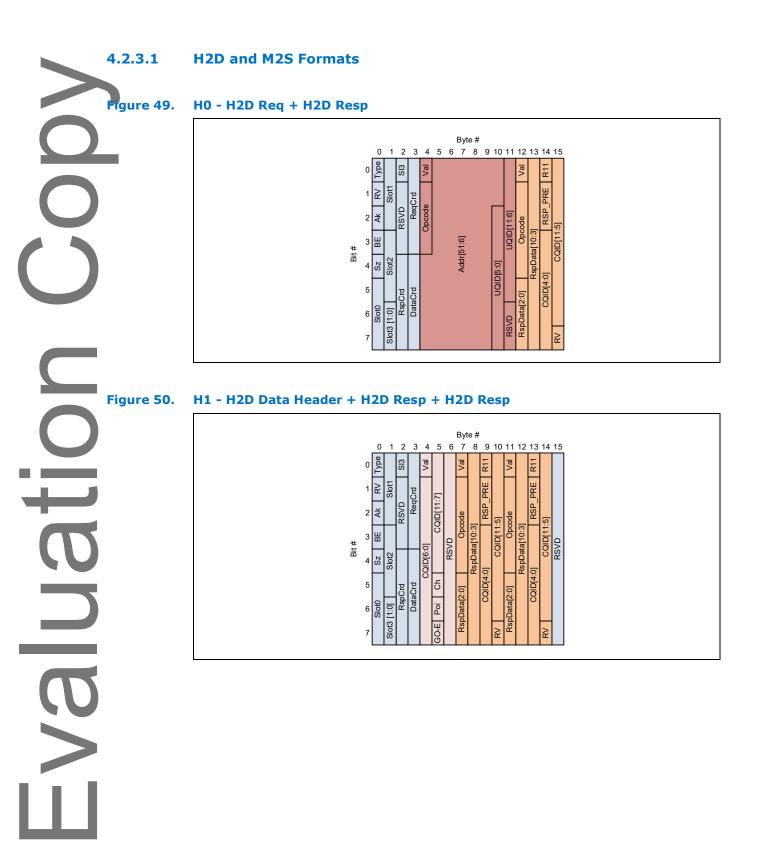

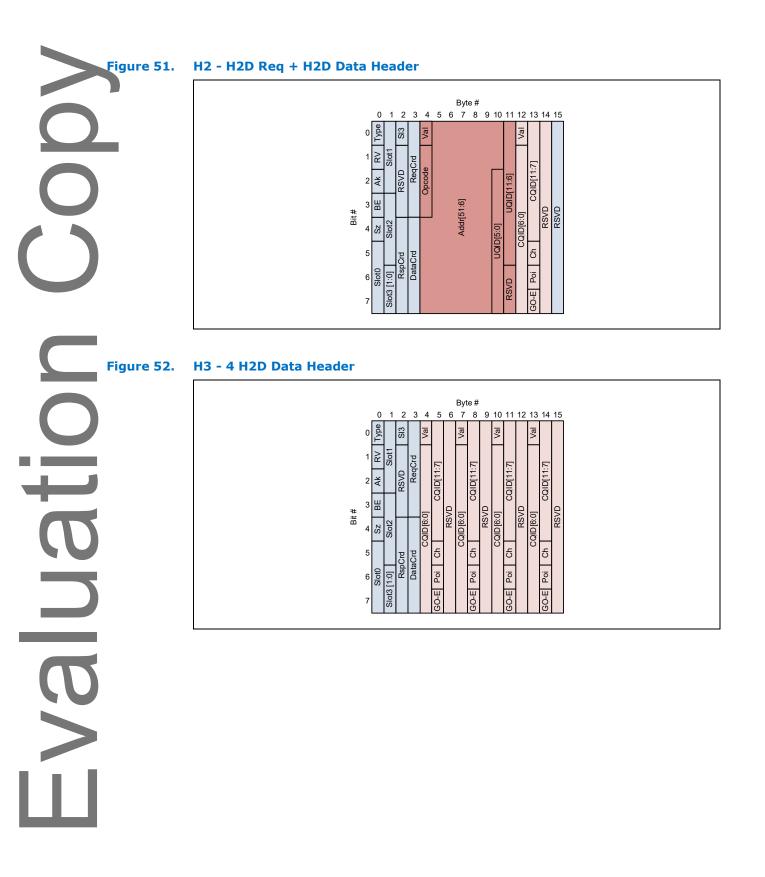

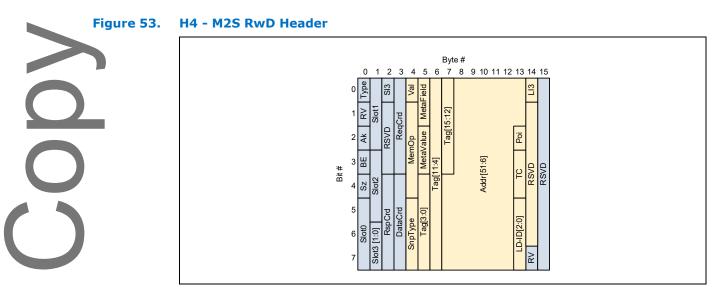

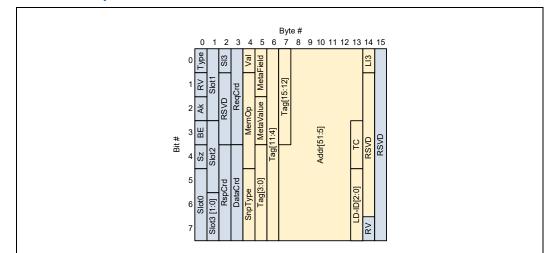

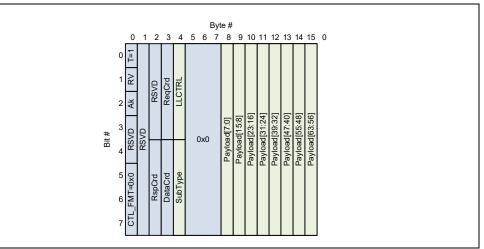

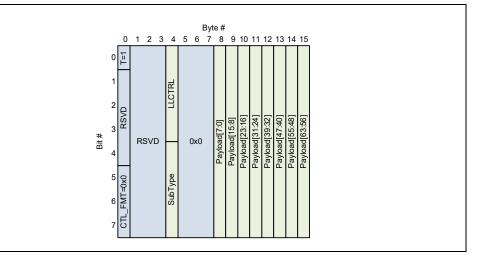

|     |          |       | 4.2.3.1 H2D and M2S Formats                                                                                   | -        |

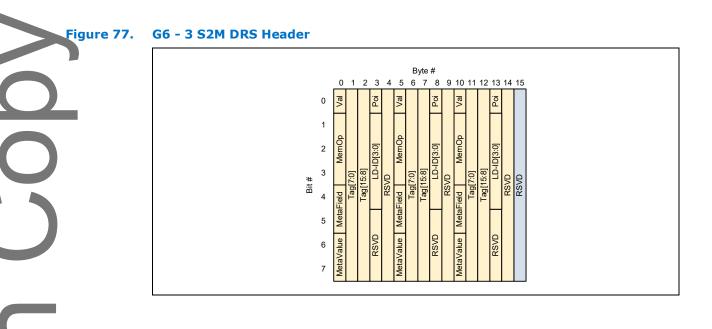

|     |          |       | 4.2.3.2 D2H and S2M Formats                                                                                   | -        |

|     |          | 4.2.4 | Link Layer Registers                                                                                          |          |

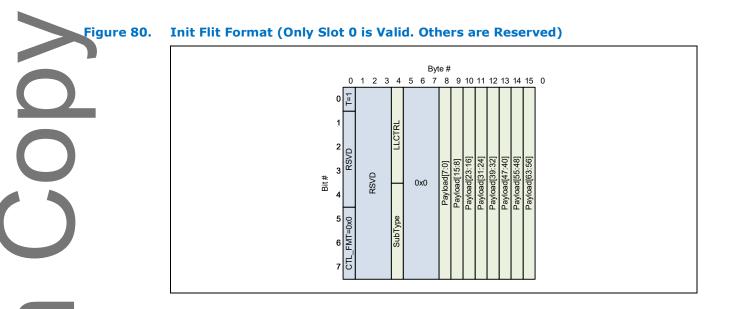

|     |          | 4.2.5 | Flit Packing Rules                                                                                            |          |

|     |          | 4.2.6 | Link Layer Control Flit                                                                                       |          |

|     |          | 4.2.7 | Link Layer Initialization                                                                                     |          |

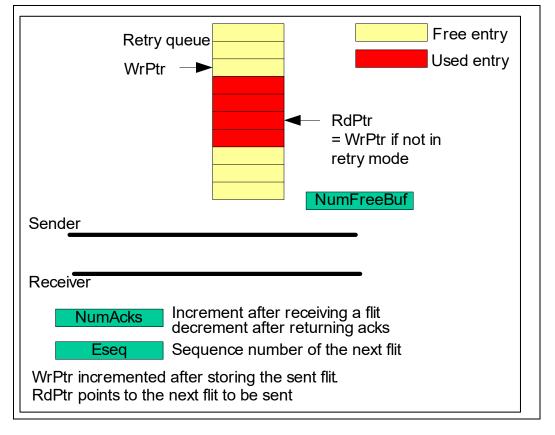

|     |          | 4.2.8 | CXL.cache/CXL.mem Link Layer Retry                                                                            |          |

|     |          |       | 4.2.8.1 LLR Variables                                                                                         |          |

|     |          |       | 4.2.8.2 LLCRD Forcing                                                                                         |          |

|     |          |       | 4.2.8.3 LLR Control Flits                                                                                     |          |

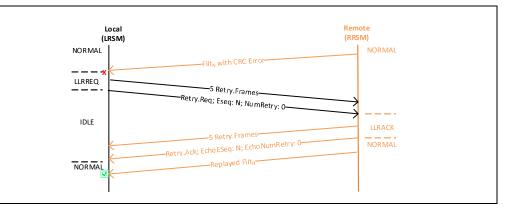

|     |          |       | 4.2.8.4 RETRY Framing Sequences                                                                               |          |

|     |          |       | 4.2.8.5 LLR State Machines                                                                                    |          |

|     |          |       | 4.2.8.6 Interaction with Physical Layer Reinitialization                                                      |          |

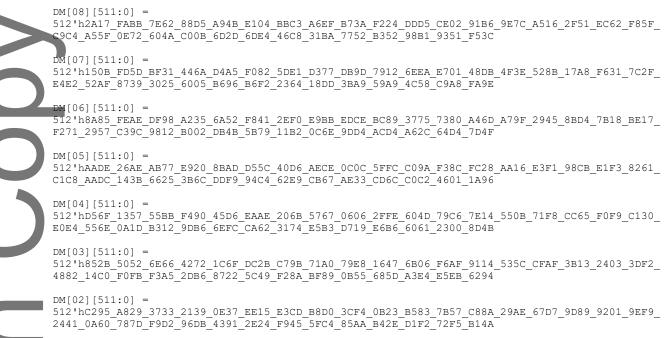

|     |              |                | 4.2.8.7            | CXL.cache/CXL.mem Flit CRC                                                 |     |

|-----|--------------|----------------|--------------------|----------------------------------------------------------------------------|-----|

|     |              | 4.2.9          |                    | d Viral                                                                    |     |

|     |              |                | 4.2.9.1            | Viral                                                                      |     |

| 5.0 | Com          | pute Expre     | ess Link AF        | 8B/MUX                                                                     |     |

|     | 5.1          | Virtual I      |                    |                                                                            |     |

|     |              | 5.1.1          |                    | l Rules for Local vLSM Transitions                                         |     |

|     |              | 5.1.2          | Rules for          | Virtual LSM State Transitions Across Link                                  |     |

|     |              |                | 5.1.2.1            | General Rules                                                              |     |

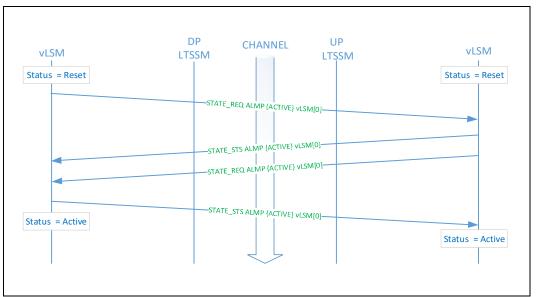

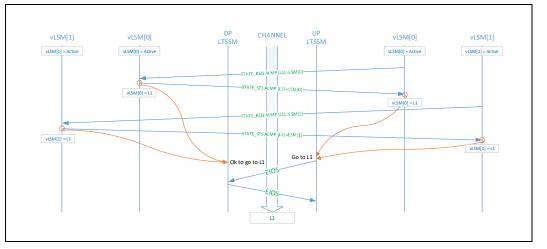

|     |              |                | 5.1.2.2            | Entry to Active Exchange Protocol                                          |     |

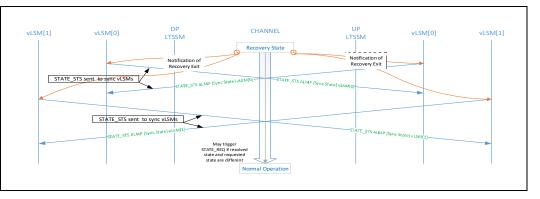

|     |              |                | 5.1.2.3            | Status Synchronization Protocol                                            |     |

|     |              |                | 5.1.2.4<br>5.1.2.5 | State Request ALMP<br>State Status ALMP                                    |     |

|     |              |                | 5.1.2.5            | Unexpected ALMPs                                                           |     |

|     |              | 5.1.3          |                    | ons of the vLSM State Transition Rules                                     |     |

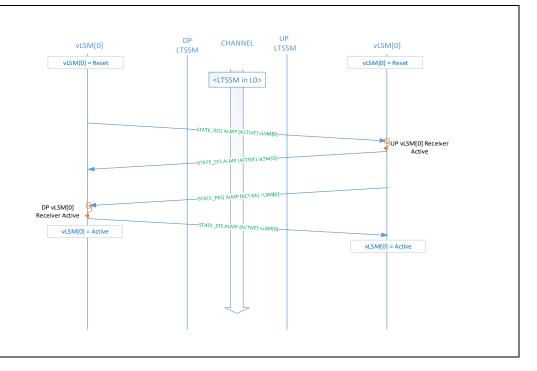

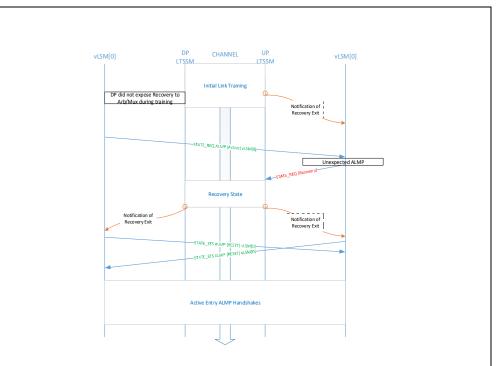

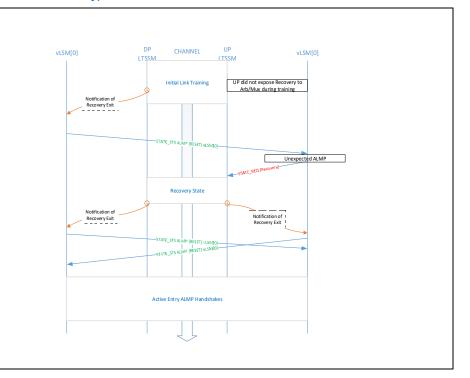

|     |              | 5.1.5          | 5.1.3.1            | Initial Link Training                                                      |     |

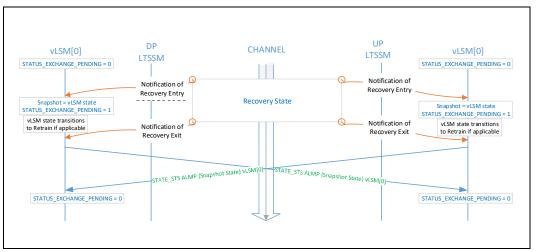

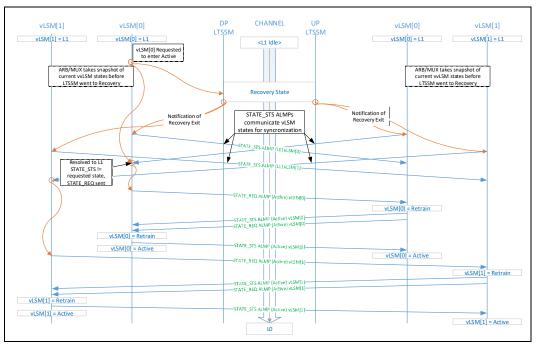

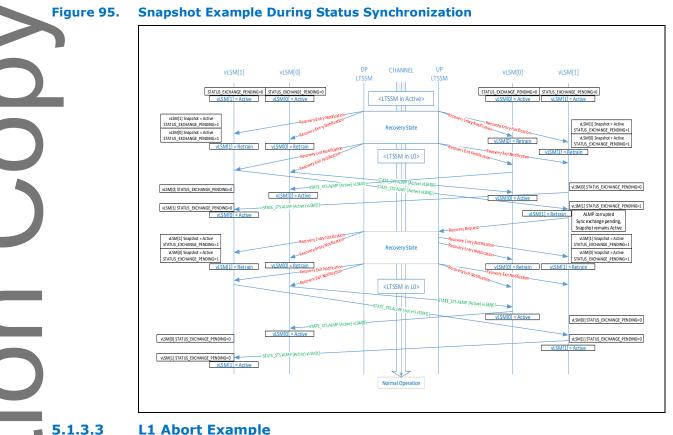

|     |              |                | 5.1.3.2            | Status Exchange Snapshot Example                                           |     |

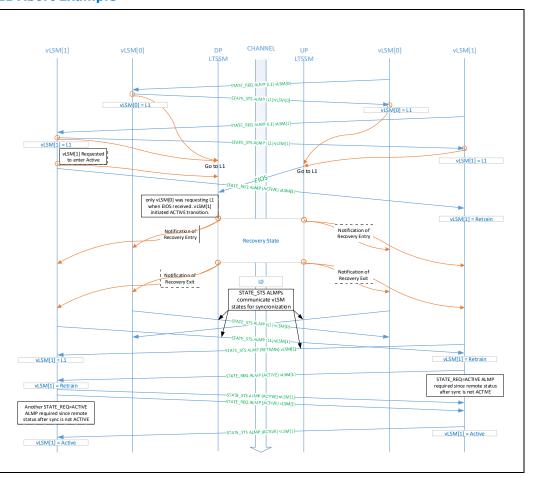

|     |              |                | 5.1.3.3            | L1 Abort Example                                                           |     |

|     | 5.2          | ARB/MU         | JX Link Mai        | nagement Packets                                                           |     |

|     |              | 5.2.1          |                    | Bypass Feature                                                             |     |

|     | 5.3          | Arbitrat       |                    | ta Multiplexing/Demultiplexing                                             |     |

|     | <b>F</b> law |                |                    |                                                                            |     |

| 6.0 |              |                |                    |                                                                            |     |

|     | 6.1          |                |                    | in a sel Develop La se se                                                  |     |

|     | 6.2          |                |                    | ing and Packet Layout                                                      |     |

|     |              | 6.2.1          |                    | Set Blocks and Data Blocks                                                 |     |

|     |              | 6.2.2          |                    | D[15:0]                                                                    |     |

|     |              | 6.2.3          |                    | et Layout                                                                  |     |

|     |              | 6.2.4          |                    | Layout                                                                     |     |

|     |              | 6.2.5          |                    | Layout                                                                     |     |

|     |              | 6.2.6<br>6.2.7 |                    | Layout                                                                     |     |

|     |              | 6.2.7          |                    | Layout<br>ase: CXL.io When a TLP Ends on a Flit Boundary                   |     |

|     |              | 6.2.8          |                    | •                                                                          |     |

|     | 6.3          |                | -                  | rrors                                                                      |     |

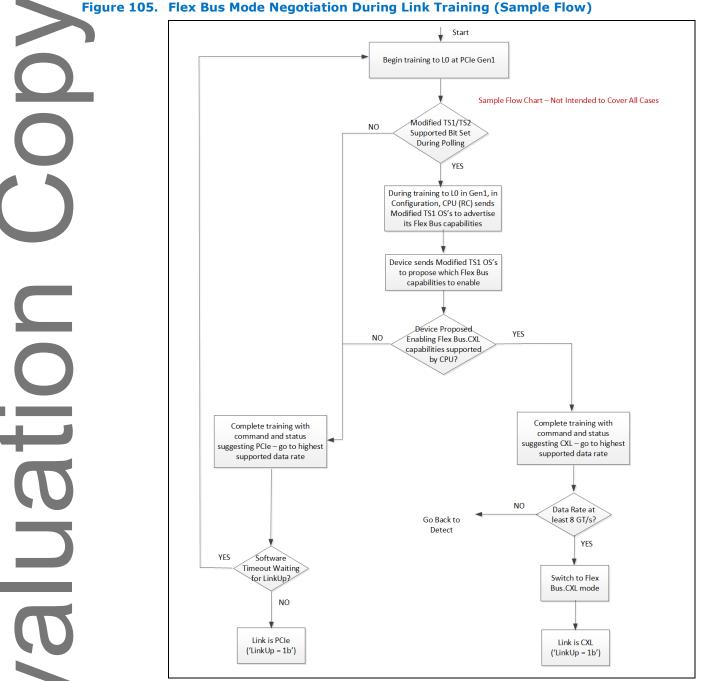

|     | 0.5          | 6.3.1          | 0                  | ex Bus.CXL Mode Selection                                                  |     |

|     |              | 0.5.1          | 6.3.1.1            |                                                                            |     |

|     |              |                | 6.3.1.1            | Hardware Autonomous Mode Negotiation<br>CXL 2.0 Versus CXL 1.1 Negotiation |     |

|     |              |                | 6.3.1.3            | Flex Bus.CXL Negotiation with Maximum Supported Link                       |     |

|     |              |                | 0.01110            | Speed of 8GT/s or 16GT/s                                                   |     |

|     |              |                | 6.3.1.4            | Link Width Degradation and Speed Downgrade                                 |     |

|     | 6.4          | Recover        | ry.Idle and        | Config.Idle Transitions to L0                                              |     |

|     | 6.5          |                |                    | ~                                                                          |     |

|     | 6.6          | Exit fror      | n Recovery         | ,                                                                          |     |

|     | 6.7          | Retimer        | 's and Low         | Latency Mode                                                               |     |

|     |              | 6.7.1          | SKP Orde           | red Set Frequency and L1/Recovery Entry                                    |     |

| 7.0 | Switz        | hing           |                    |                                                                            | 201 |

| 7.0 | 7.1          | -              |                    |                                                                            |     |

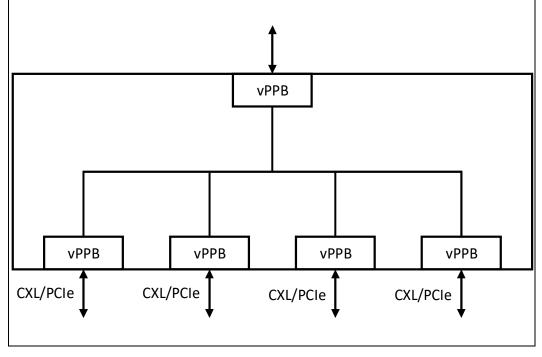

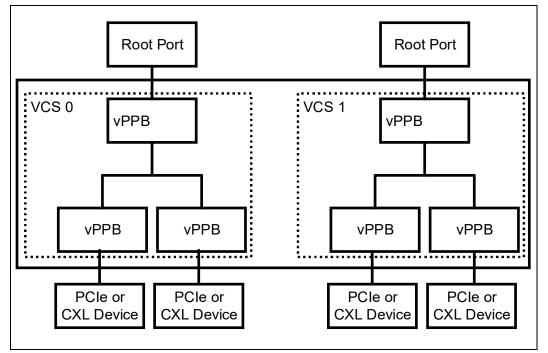

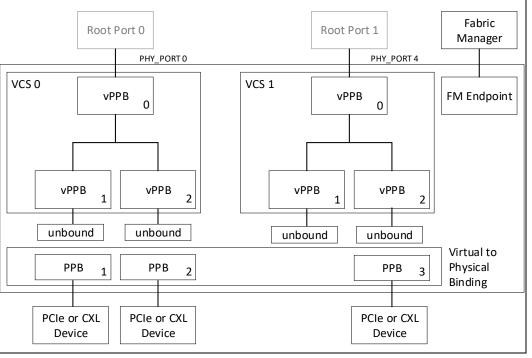

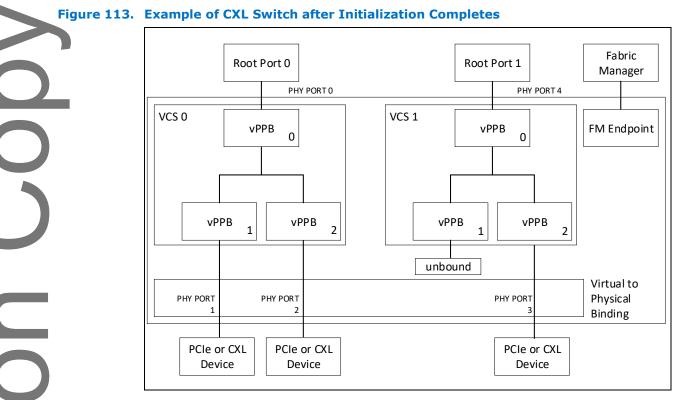

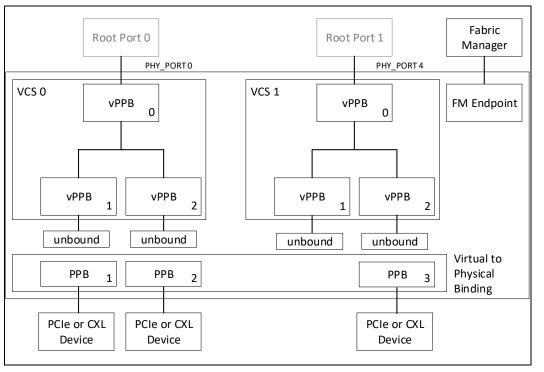

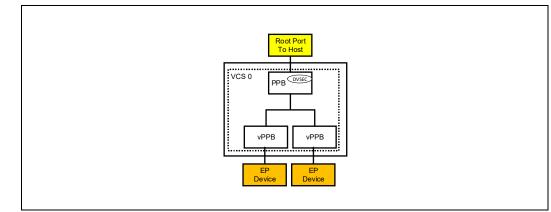

|     | 7.1          | 7.1.1          |                    | S Switch                                                                   |     |

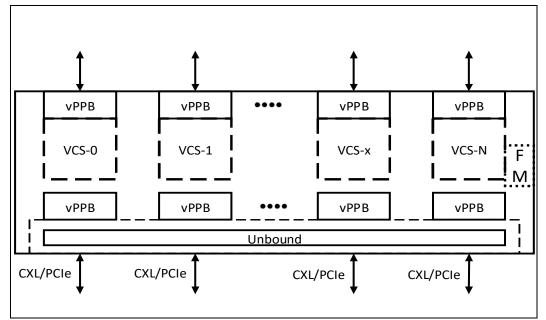

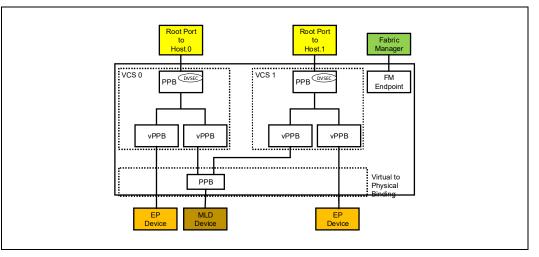

|     |              | 7.1.1          |                    | /CS Switch                                                                 |     |

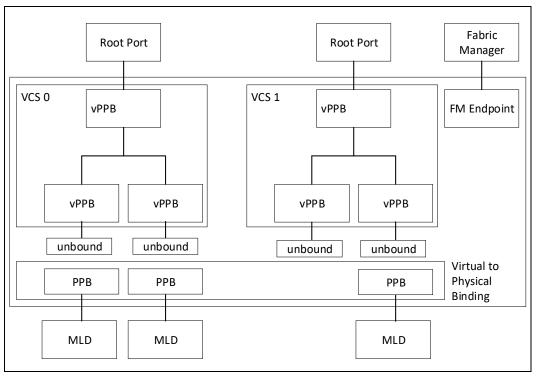

|     |              | 7.1.2          |                    | /CS Switch with MLD Ports                                                  |     |

|     | 7.2          | -              |                    | on and Composition                                                         |     |

|     | , . <b>L</b> | 7.2.1          | •                  | h Initialization Options                                                   |     |

|     |              |                | 7.2.1.1            | Static Initialization                                                      |     |

|     |              |                | 7.2.1.2            | Fabric Manager Boots First                                                 |     |

|     |              |                | 7.2.1.3            | Fabric Manager and Host Boot Simultaneously                                |     |

|     |              |                |                    |                                                                            |     |

|     | 7.2.2    | Sideband Signal Operation |                                                        |     |  |  |  |

|-----|----------|---------------------------|--------------------------------------------------------|-----|--|--|--|

|     | 7.2.3    | Binding a                 | nd Unbinding                                           | 209 |  |  |  |

|     |          | 7.2.3.1                   | Binding and Unbinding of a Single Logical Device Port  |     |  |  |  |

|     |          | 7.2.3.2                   | Binding and Unbinding of a Pooled Device               | 211 |  |  |  |

|     | 7.2.4    | PPB and v                 | /PPB Behavior for MLD Ports                            |     |  |  |  |

|     |          | 7.2.4.1                   | MLD Type 1 Configuration Space Header                  |     |  |  |  |

|     |          | 7.2.4.2                   | MLD PCI-Compatible Configuration Registers             |     |  |  |  |

|     |          | 7.2.4.3                   | MLD PCI Express Capability Structure                   |     |  |  |  |

|     |          | 7.2.4.4                   | MLD PPB Secondary PCI Express Capability Structure     |     |  |  |  |

|     |          | 7.2.4.5                   | MLD Physical Layer 16.0 GT/s Extended Capability       |     |  |  |  |

|     |          | 7.2.4.6                   | MLD Physical Layer 32.0 GT/s Extended Capability       |     |  |  |  |

|     |          | 7.2.4.7                   | MLD Lane Margining at the Receiver Extended Capability |     |  |  |  |

|     | 7.2.5    |                           | Extended Capability                                    |     |  |  |  |

|     | 7.2.6    |                           | Extended Capabilities                                  |     |  |  |  |

|     | 7.2.7    |                           | anced Error Reporting Extended Capability              |     |  |  |  |

|     | 7.2.8    |                           | Extended Capability                                    |     |  |  |  |

| 7.3 |          |                           | CXL.mem Decode and Forwarding                          |     |  |  |  |

|     | 7.3.1    |                           |                                                        |     |  |  |  |

|     |          | 7.3.1.1                   | CXL.io Decode                                          |     |  |  |  |

|     |          | 7.3.1.2                   | CXL 1.1 Support                                        |     |  |  |  |

|     | 7.3.2    |                           | 2                                                      |     |  |  |  |

|     | 7.3.3    | CXL.mem                   |                                                        |     |  |  |  |

|     |          | 7.3.3.1                   | CXL.mem Request Decode                                 |     |  |  |  |

|     |          | 7.3.3.2                   | CXL.mem Response Decode                                |     |  |  |  |

|     |          | 7.3.3.3                   | QoS Message Aggregation                                |     |  |  |  |

|     | 7.3.4    |                           | d PPB CXL Handling                                     |     |  |  |  |

| 7.4 |          |                           |                                                        |     |  |  |  |

|     | 7.4.1    |                           | h ASPM L1                                              |     |  |  |  |

|     | 7.4.2    |                           | h PCI-PM and L2                                        |     |  |  |  |

|     | 7.4.3    | CXL Swite                 | h Message Management                                   | 224 |  |  |  |

| 7.5 |          |                           |                                                        |     |  |  |  |

| 7.6 | Fabric M | 1anager Ap                | plication Programming Interface                        |     |  |  |  |

|     | 7.6.1    | CXL Fabri                 | c Management                                           | 226 |  |  |  |

|     | 7.6.2    | Fabric Ma                 | nagement Model                                         |     |  |  |  |

|     | 7.6.3    | FM Comm                   | nand Transport Protocol                                |     |  |  |  |

|     | 7.6.4    | CXL Swite                 | h Management                                           |     |  |  |  |

|     |          | 7.6.4.1                   | Initial Configuration                                  |     |  |  |  |

|     |          | 7.6.4.2                   | Dynamic Configuration                                  |     |  |  |  |

|     |          | 7.6.4.3                   | MLD Port Management                                    |     |  |  |  |

|     | 7.6.5    | MLD Com                   | ponent Management                                      |     |  |  |  |

|     | 7.6.6    | Managem                   | ent Requirements for System Operations                 | 230 |  |  |  |

|     |          | 7.6.6.1                   | Initial System Discovery                               | 230 |  |  |  |

|     |          | 7.6.6.2                   | CXL Switch Discovery                                   |     |  |  |  |

|     |          | 7.6.6.3                   | MLD and Switch MLD Port Management                     |     |  |  |  |

|     |          | 7.6.6.4                   | Event Notifications                                    |     |  |  |  |

|     |          | 7.6.6.5                   | Binding Ports and LDs on a Switch                      |     |  |  |  |

|     |          | 7.6.6.6                   | Unbinding Ports and LDs on a Switch                    |     |  |  |  |

|     |          | 7.6.6.7                   | Hot-Add and Managed Hot-Removal of Devices             |     |  |  |  |

|     |          | 7.6.6.8                   | Surprise Removal of Devices                            |     |  |  |  |

|     | 7.6.7    |                           | nagement Application Programming Interface             |     |  |  |  |

|     |          | 7.6.7.1                   | Switch Event Notifications Command Set                 |     |  |  |  |

|     |          | 7.6.7.2                   | Virtual Switch Command Set                             |     |  |  |  |

|     |          | 7.6.7.3                   | Unbind vPPB (Opcode 5202h)                             |     |  |  |  |

|     |          | 7.6.7.4                   | MLD Port Command Set                                   |     |  |  |  |

|     | 760      | 7.6.7.5                   | MLD Component Command Set                              |     |  |  |  |

|     | 7.6.8    |                           | nagement Event Records                                 |     |  |  |  |

|     |          | 7.6.8.1                   | Physical Switch Event Records                          | 252 |  |  |  |

| Control and Status Registers         256           8.1         Configuration Space Registers         257           8.1.2         CCL Express Designated Vendor-Specific Extended Capability (DVSEC) ID Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |      |            | 7.6.8.2     | Virtual CXL Switch Event Records                      |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------------|-------------|-------------------------------------------------------|-----|

| 8.1         Configuration Space Registers         257           8.1.1         PCIE Express Designated Vendor-Specific Extended Capability (DVSEC) ID Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |      |            | 7.6.8.3     | MLD Port Event Records                                | 254 |

| 8.1         Configuration Space Registers         257           8.1.1         PCIE Express Designated Vendor-Specific Extended Capability (DVSEC) ID Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8.0 | Cont | trol and S | tatus Regis | ters                                                  |     |

| 8.1.1         PCI Express Designated Vendor-Specific Extended Capability (DVSEC) ID Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |      |            |             |                                                       |     |

| 8.1.2         CXL Data Object Exchange (DOE) Type Assignment.         258           8.1.3         PCE DVSEC for CXL Device.         258           8.1.3         DVSEC CXL CApability (Offset 0Ah).         256           8.1.3         DVSEC CXL Canapolity (Offset 1Ah).         256           8.1.3         DVSEC CXL Canapolity (Offset 1Ah).         256           8.1.3         DVSEC CXL Range registers         256           8.1.4         Non-CXL Function Map Register 1 (Offset 0Ch).         256           8.1.4         Non-CXL Function Map Register 1 (Offset 1Ah).         270           8.1.4.4         Non-CXL Function Map Register 1 (Offset 1Ah).         270           8.1.4.5         Non-CXL Function Map Register 1 (Offset 1Ah).         270           8.1.4.4         Non-CXL Function Map Register 1 (Offset 1Ah).         270           8.1.4.5         Non-CXL Function Map Register 1 (Offset 1Ah).         270           8.1.4.4         Non-CXL Function Map Register 1 (Offset 2Ah).         271           8.1.5         Atternate Bus Limit (Offset 2Ah).         271                                                                                         |     |      | •          |             |                                                       |     |

| 8.1.3         PCIce DVSEC for CXL Device         256           8.1.3.1         DVSEC CXL Control (Offset OCh)         256           8.1.3.2         DVSEC CXL Control (Offset OCh)         256           8.1.3.4         DVSEC CXL Control (Offset OCh)         256           8.1.3.4         DVSEC CXL Control 2 (Offset 12h)         252           8.1.3.5         DVSEC CXL Control 2 (Offset 12h)         256           8.1.3.6         DVSEC CXL Control 2 (Offset 12h)         256           8.1.3.6         DVSEC CXL Canga registers         253           8.1.3.6         DVSEC CXL Canga registers         256           8.1.4         Non-CXL Function Map Register 1 (Offset 10h)         256           8.1.4.1         Non-CXL Function Map Register 1 (Offset 10h)         270           8.1.4.5         Non-CXL Function Map Register 1 (Offset 10h)         270           8.1.4.6         Non-CXL Function Map Register 1 (Offset 10h)         270           8.1.4.7         Non-CXL Function Map Register 1 (Offset 20h)         271           8.1.5         CXL 2 DExtensions DVSEC (for Ports         271           8.1.5         CXL 2 DExtensions (Offset 0Ch)         272           8.1.5         Atternate Bus Imit (Offset 12h)         271           8.1.5         Atternate Bus Imit (Of                                                                                                    |     |      | 8.1.2      |             |                                                       |     |

| 8.1.31         DVSEC CXL Capability (Offset 0Ah).         261           8.1.32         DVSEC CXL Capability (Offset 0Ch).         261           8.1.33         DVSEC CXL Status (Offset 12h).         262           8.1.34         DVSEC CXL Status (Offset 12h).         263           8.1.35         DVSEC CXL capability (Offset 12h).         263           8.1.36         DVSEC CXL capability (Offset 14h).         263           8.1.37         DVSEC CXL capability (Offset 14h).         263           8.1.38         DVSEC CXL capability (Offset 14h).         263           8.1.31         DVSEC CXL status (Offset 14h).         263           8.1.41         Non-CXL Function Map Register 1 (Offset 16h).         268           8.1.41         Non-CXL Function Map Register 1 (Offset 16h).         269           8.1.43         Non-CXL Function Map Register 1 (Offset 16h).         270           8.1.44         Non-CXL Function Map Register 1 (Offset 16h).         270           8.1.45         Non-CXL Function Map Register 1 (Offset 16h).         270           8.1.46         Non-CXL Function Map Register 1 (Offset 16h).         271           8.1.51         CXL POR Extensions Sout (Offset 0Ch).         272           8.1.51         CXL POR Extensions Sout (Offset 0Ch).         274                                                                                             |     |      | 8.1.3      |             |                                                       |     |

| 8.1.32         DVSEC CXL Control (Offset OCh)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |      |            |             | DVSEC CXL Capability (Offset 0Ah)                     |     |

| B.1.3.4         DVSEC CXL Control2 (Offset 10h)         262           B.1.3.5         DVSEC CXL Lock (Offset 14h)         263           B.1.4         DVSEC CXL Lock (Offset 14h)         263           B.1.3.8         DVSEC CXL Lock (Offset 14h)         263           B.1.4         Non-CXL Function Map Register 0 (Offset 0Ch)         269           B.1.4.1         Non-CXL Function Map Register 2 (Offset 10h)         269           B.1.4.2         Non-CXL Function Map Register 2 (Offset 10h)         269           B.1.4.4         Non-CXL Function Map Register 2 (Offset 10h)         269           B.1.4.4         Non-CXL Function Map Register 2 (Offset 10h)         270           B.1.4.4         Non-CXL Function Map Register 1 (Offset 10h)         270           B.1.4.4         Non-CXL Function Map Register 1 (Offset 20h)         271           B.1.5.2         Port Control Extensions Offset 0Ch)         272           B.1.5.1         CXL 2 0 Extensions Offset 0Ch)         273           B.1.5.4         Alternate Bus Goffset 0Ch)         274           B.1.5.5         Alternate Memory Base (Offset 10h)         274           B.1.5.6         Alternate Memory Base (Offset 10h)         275           B.1.5.6         Alternate Memory Dase (Offset 10h)         275           B.1                                                                                           |     |      |            | 8.1.3.2     | DVSEC CXL Control (Offset 0Ch)                        |     |

| 81.3.5         DVSEC CXL Log (Offset 12h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |      |            | 8.1.3.3     | DVSEC CXL Status (Offset 0Eh)                         |     |

| B.13.6         DVSEC CXL Lock (Offset 14h).         263           B.13.7         DVSEC CXL Range registers.         263           B.13.8         DVSEC CXL Range registers.         263           B.14.4         Non-CXL Function Map RVSEC         268           B.14.2         Non-CXL Function Map Register 1 (Offset 10h).         269           B.14.4         Non-CXL Function Map Register 2 (Offset 10h).         269           B.14.4         Non-CXL Function Map Register 2 (Offset 16h).         270           B.14.4         Non-CXL Function Map Register 2 (Offset 16h).         270           B.14.4         Non-CXL Function Map Register 6 (Offset 26h).         271           B.15.1         CXL 2.0 Extensions DVSEC OF Ports.         271           B.15.2         Port Control Extensions (Offset 06h).         272           B.15.3         Alternate Bus Base (Offset 06h).         272           B.15.5         Alternate Memory Base (Offset 10h).         274           B.15.5         Alternate Memory Base (Offset 10h).         274           B.15.6         Alternate Memory Base (Offset 10h).         275           B.15.6         Alternate Memory Base (Offset 10h).         275           B.15.6         Alternate Memory Base (Offset 10h).         276           B.15.7                                                                                                         |     |      |            |             | DVSEC CXL Control2 (Offset 10h)                       |     |

| 81.3.7         DVSEC CXL Capability2 (Offset 16h)         263           81.38         DVSEC CXL Rapper registers         263           81.41         Non-CXL Function Map Register 0 (Offset 0Ch)         266           81.42         Non-CXL Function Map Register 1 (Offset 16h)         269           81.43         Non-CXL Function Map Register 1 (Offset 16h)         260           81.44         Non-CXL Function Map Register 3 (Offset 16h)         270           81.45         Non-CXL Function Map Register 5 (Offset 26h)         270           81.45         Non-CXL Function Map Register 6 (Offset 26h)         270           81.45         Non-CXL Function Map Register 7 (Offset 28h)         271           81.51         CXL Port Extensions DVSEC for Ports         271           81.52         Port Control Extensions (Offset 0Ch)         273           81.53         Alternate Bus Base (Offset 0Ch)         274           81.54         Naternate Bus Base (Offset 0Ch)         274           81.55         Alternate Bus Base (Offset 0Ch)         274           81.54         Naternate Prefetchable Memory Base (Offset 16h)         275           81.55         Alternate Prefetchable Memory Date (Offset 16h)         275           81.51         CXL RCPB Base High (Offset 24h)         276                                                                                          |     |      |            |             |                                                       |     |

| 81.3.8         DVSEC CXL Range registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |      |            |             | DVSEC CXL Lock (Offset 14h)                           |     |

| 81.4         Non-CXL Function Map DySEC         268           81.4.1         Non-CXL Function Map Register 0 (Offset 0Ch)         269           81.4.2         Non-CXL Function Map Register 1 (Offset 10h)         269           81.4.3         Non-CXL Function Map Register 3 (Offset 16h)         270           81.4.4         Non-CXL Function Map Register 3 (Offset 16h)         270           81.4.5         Non-CXL Function Map Register 5 (Offset 20h)         270           81.4.6         Non-CXL Function Map Register 5 (Offset 20h)         270           81.4.7         Non-CXL Function Map Register 5 (Offset 20h)         270           81.4.7         Non-CXL Function Map Register 5 (Offset 20h)         271           81.5.1         CXL 20 Extensions DVSEC for Ports.         271           81.5.6         Alternate Bus Base (Offset 0Ch)         273           81.5.7         Alternate Bus Base (Offset 0Ch)         274           81.5.6         Alternate Prefetchable Memory Base (Offset 14h)         275           81.5.7         Alternate Prefetchable Memory Base (Offset 14h)         276           81.5.7         Alternate Prefetchable Memory Base (Offset 14h)         275           81.5.7         Alternate Prefetchable Memory Base (Iffset 14h)         275           81.5.8         Alternate Prefetchable Memo                                                        |     |      |            |             | DVSEC CXL Capability2 (Offset 16n)                    |     |

| 8.1.4.1         Non-CXL Function Map Register 1 (Offset OCh)         269           8.1.4.2         Non-CXL Function Map Register 2 (Offset 14h)         270           8.1.4.3         Non-CXL Function Map Register 2 (Offset 14h)         270           8.1.4.4         Non-CXL Function Map Register 3 (Offset 04h)         270           8.1.4.5         Non-CXL Function Map Register 3 (Offset 24h)         271           8.1.4.6         Non-CXL Function Map Register 3 (Offset 24h)         271           8.1.4.8         Non-CXL Function Map Register 3 (Offset 24h)         271           8.1.4.8         Non-CXL Function Map Register 3 (Offset 24h)         271           8.1.5.1         CXL 20 Extensions DVSEC for Ports         271           8.1.5.1         CXL 20 Extensions OVSEC for Ports         273           8.1.5.2         Port Control Extensions O(fiset 06h)         273           8.1.5.4         Alternate Bus Base (Offset 06h)         275           8.1.5.6         Alternate Memory Base (Offset 06h)         275           8.1.5.7         Alternate Memory Base (Offset 10h)         276           8.1.5.8         Alternate Memory Base (Offset 10h)         276           8.1.5.7         Alternate Memory Base (Offset 10h)         276           8.1.5.8         Alternate Memory Base (Offset 10h)         <                                                             |     |      | 014        |             |                                                       |     |

| 8.1.4.2         Non-CXL Function Map Register 1 (Offset 14h).         270           8.1.4.3         Non-CXL Function Map Register 3 (Offset 18h).         270           8.1.4.4         Non-CXL Function Map Register 3 (Offset 18h).         270           8.1.4.5         Non-CXL Function Map Register 3 (Offset 18h).         270           8.1.4.6         Non-CXL Function Map Register 3 (Offset 28h).         271           8.1.4.6         Non-CXL Function Map Register 3 (Offset 28h).         271           8.1.5         Non-CXL Function Map Register 3 (Offset 28h).         271           8.1.5         Non-CXL Function Map Register 3 (Offset 28h).         271           8.1.5         Non-CXL Function Map Register 3 (Offset 28h).         271           8.1.5         Register 1 (Offset 0Ch).         272           8.1.5.1         CXL Port Extensions (Offset 0Ch).         273           8.1.5.2         Alternate Memory Base (Offset 10h).         274           8.1.5.4         Alternate Memory Limit (Offset 12h).         274           8.1.5.5         Alternate Memory Limit (Offset 12h).         274           8.1.5.6         Alternate Memory Limit (Offset 12h).         275           8.1.5.8         Alternate Memory Limit Migh (Offset 16h).         275           8.1.5.9         Alternate Memory Limit Migh (Off                                                        |     |      | 0.1.4      |             |                                                       |     |

| Since State         8.1.4.3         Non-CXL Function Map Register 3(Offset 18h).         270           8.1.4.4         Non-CXL Function Map Register 3(Offset 18h).         270           8.1.4.5         Non-CXL Function Map Register 3(Offset 18h).         270           8.1.4.6         Non-CXL Function Map Register 3(Offset 24h).         271           8.1.4.7         Non-CXL Function Map Register 7(Offset 24h).         271           8.1.4.8         Non-CXL Function Map Register 7(Offset 28h).         271           8.1.5         CXL 2.0 Extensions DVSEC for POrts.         271           8.1.5         CXL 2.0 Extensions SUSEC for POrts.         271           8.1.5.2         Port Control Extensions (Offset 0Ch)         272           8.1.5.3         Alternate Bus Base (Offset 0Ch)         272           8.1.5.4         Alternate Bus Base (Offset 0Ch)         274           8.1.5.5         Alternate Prefetchable Memory Base (Offset 14h)         275           8.1.5.6         Alternate Prefetchable Memory Base (Offset 14h)         275           8.1.5.9         Alternate Prefetchable Memory Base (Offset 14h)         275           8.1.5.9         Alternate Prefetchable Memory Base (Offset 14h)         275           8.1.5.1         CXL RCRB Base (I0ffset 24h)         276           8.1.5.1 <t< td=""><td></td><td></td><td></td><td>-</td><td></td><td></td></t<> |     |      |            | -           |                                                       |     |

| Bit.4.4         Non-CXL Function Map Register 3 (Offset 18h).         270           Bit.4.5         Non-CXL Function Map Register 5 (Offset 20h).         270           Bit.4.6         Non-CXL Function Map Register 5 (Offset 20h).         270           Bit.4.7         Non-CXL Function Map Register 5 (Offset 20h).         270           Bit.4.8         Non-CXL Function Map Register 5 (Offset 20h).         270           Bit.5         CXL 2.0 Extensions DVSEC for Ports.         271           Bit.5.1         CXL 2.0 Extensions fuctors (Offset 0Ah).         272           Bit.5.2         Port Control Extensions fuctors (Offset 0Ah).         272           Bit.5.3         Alternate Bus Base (Offset 0Ch).         273           Bit.5.4         Alternate Bus Base (Offset 0Ch).         274           Bit.5.5         Alternate Memory Limit (Offset 10h).         274           Bit.5.6         Alternate Memory Limit (Offset 10h).         275           Bit.5.9         Alternate Memory Limit (Offset 10h).         275           Bit.5.1         Alternate Memory Limit (Offset 10h).         275           Bit.5.1         CXL RCRB Base High (Offset 0Ch).         277           Bit.6.1         GPF DVSEC for CXL Device.         278           Bit.7.1         GPF DVSEC for CXL Device.         279                                                                                 |     |      |            |             |                                                       |     |

| <b>B</b> 8.1.4.5         Non-CXL Function Map Register 5 (Offset 20h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |      |            |             | Non-CXL Function Map Register 3(Offset 18h)           |     |

| 8.1.4.6         Non-CXL Function Map Register 5 (Offset 20h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |      |            |             | Non-CXL Function Map Register 4 (Offset 1Ch)          |     |

| 8.1.4.7         Non-CXL Function Map Register 6 (Offset 24h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |      |            | 8.1.4.6     | Non-CXL Function Map Register 5 (Offset 20h)          |     |

| 81.5       CXL 2.0 Extensions DVSEC for Ports.       271         81.5.1       CXL POrt Extension Status (Offset 0Ah)       272         81.5.2       Port Control Extensions (Offset 0Ch)       273         81.5.3       Alternate Bus Base (Offset 0Ch)       274         81.5.4       Alternate Bus Limit (Offset 0Fh)       274         81.5.5       Alternate Bus Limit (Offset 0Fh)       274         81.5.7       Alternate Bus Limit (Offset 1Ch)       274         81.5.7       Alternate Presentable Memory Base (Offset 14h)       275         81.5.7       Alternate Presentable Memory Limit (Offset 16h)       275         81.5.10       Alternate Presentable Memory Limit (Offset 16h)       276         81.5.10       Alternate Presentable Memory Limit (Offset 16h)       276         81.5.11       CXL RCRB Base (Offset 20h)       276         81.5.11       CXL RCRB Base (Offset 20h)       277         81.6       GPF Phase 2 Control (Offset 0Ch)       277         81.7.1       GPF Phase 2 Duration (Offset 0Ch)       2                                                                                                                     |     |      |            | 8.1.4.7     | Non-CXL Function Map Register 6 (Offset 24h)          |     |

| 81.5.1         CXL Port Extension Status (Offset OAh)         272           81.5.2         Port Control Extensions (Offset OCh)         773           81.5.3         Alternate Bus Base (Offset OF)         774           81.5.4         Alternate Bus Built (Offset OFh)         774           81.5.5         Alternate Bus Limit (Offset OFh)         774           81.5.6         Alternate Memory Base (Offset 12h)         774           81.5.7         Alternate Memory Dimit (Offset 12h)         774           81.5.8         Alternate Prefetchable Memory Base (Offset 14h)         775           81.5.9         Alternate Prefetchable Memory Limit (Offset 16h)         775           81.5.10         Alternate Prefetchable Base High (Offset 12h)         776           81.5.11         CXL RCRB Base High (Offset 24h)         776           81.5.12         CXL RCRB Base High (Offset 24h)         776           81.6         GPF Phase 1 Control (Offset 0Ch)         777           81.6         GPF Phase 2 Control (Offset 0Ch)         777           81.7         GPF Phase 2 Duration (Offset 0Ch)         779           81.7         GPF Phase 2 Duration (Offset 0Ch)         779           81.7         GPF Phase 2 Duration (Offset 0Ah)         779           81.10         MLD DVSEC </td <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                     |     |      |            |             |                                                       |     |

| 81.5.2         Port Control Extensions (Offset 0Ch)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |      | 8.1.5      | CXL 2.0 E   |                                                       |     |

| 81.5.3       Alternate Bus Base (Offset 0E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |      |            |             | CXL Port Extension Status (Offset 0Ah)                |     |

| 81.5.4       Alternate Bus Limit (Offset 0Fh)       274         81.5.5       Alternate Memory Base (Offset 10h)       274         81.5.6       Alternate Memory Base (Offset 12h)       274         81.5.7       Alternate Memory Limit (Offset 12h)       274         81.5.7       Alternate Prefetchable Memory Limit (Offset 16h)       275         81.5.8       Alternate Prefetchable Memory Limit (Offset 18h)       275         81.5.9       Alternate Prefetchable Base High (Offset 18h)       275         81.5.10       Alternate Prefetchable Memory Limit High (Offset 18h)       275         81.5.10       Alternate Prefetchable Memory Limit High (Offset 18h)       275         81.5.10       Alternate Prefetchable Memory Limit High (Offset 18h)       275         81.5.11       CXL RCRB Base High (Offset 24h)       276         81.5.12       CXL RCRB Base High (Offset 24h)       276         81.6.1       GPF DVSEC for CXL Port.       276         81.6.2       GPF Phase 2 Control (Offset 0Ch)       279         81.7.1       GPF Phase 2 Duration (Offset 0Ah)       279         81.7.2       GPF Phase 2 Duration (Offset Varies)       281         81.9       Register Offset High (Offset Varies)       281         81.9       Register Offset High (Offset Varies)                                                                                                                   |     |      |            |             |                                                       |     |

| 81.5.5       Alternate Memory Base (Offset 10h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |      |            |             |                                                       |     |

| 8.1.5.6       Alternate Memory Limit (Offset 12h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |      |            |             | Alternate Bus Limit (Offset 0Fh)                      |     |

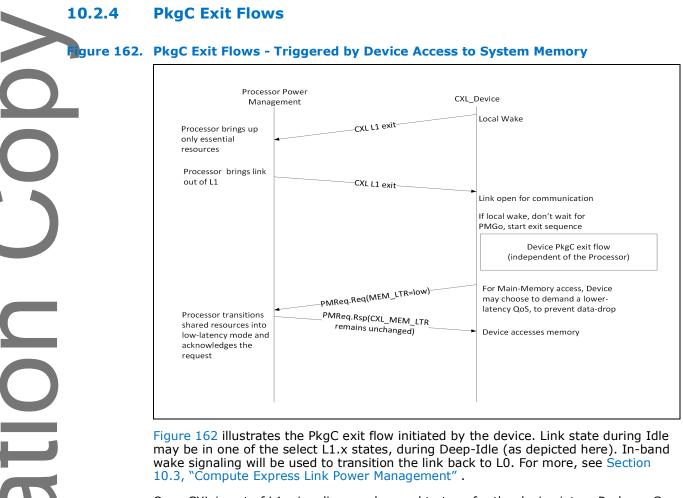

| 81.5.7       Alternate Prefetchable Memory Base (Offset 14h).       275         81.5.8       Alternate Prefetchable Memory Limit (Offset 16h).       275         81.5.9       Alternate Memory Prefetchable Base High (Offset 18h).       275         81.5.10       Alternate Prefetchable Memory Limit (Offset 18h).       275         81.5.10       Alternate Prefetchable Memory Limit High (Offset 18h).       275         81.5.11       CXL RCRB Base (Offset 20h).       276         81.5.12       CXL RCRB Base High (Offset 24h).       276         81.5.12       CXL RCRB Base High (Offset 24h).       276         81.5.12       GPF DVSEC for CXL Port.       276         81.6.1       GPF DVSEC for CXL Port.       276         81.6.1       GPF Phase 2 Control (Offset 0Ch).       277         81.6.2       GPF Phase 2 Duration (Offset 0Ah).       279         81.7.1       GPF Phase 2 Duration (Offset 0Ah).       279         81.8       PCle DVSEC for Flex Bus Port.       279         81.9       Register Offset Low (Offset Varies).       281         81.9.1       Register Offset Low (Offset Varies).       281         81.9.2       Register Offset High (Offset Varies).       282         81.10       MLD DVSEC.       281         81.10 </td <td></td> <td></td> <td></td> <td></td> <td>Alternate Memory Base (Offset 10h)</td> <td></td>                                              |     |      |            |             | Alternate Memory Base (Offset 10h)                    |     |