diff --git a/.github/workflows/make.yml b/.github/workflows/make.yml

index a90ad56..de5099b 100644

--- a/.github/workflows/make.yml

+++ b/.github/workflows/make.yml

@@ -38,15 +38,6 @@ jobs:

- boom_soc

- ispd16_example2

exclude:

- # Insufficient memory on GitHub Actions

- - router: hao3

- benchmark: mlcad_d181_lefttwo3rds

- - router: hao3

- benchmark: koios_dla_like_large

- - router: hao3

- benchmark: boom_soc

- - router: hao3

- benchmark: ispd16_example2

# NXRoute does not support LUT pin swapping

- router: nxroute-poc

lutpinswapping: true

@@ -75,12 +66,8 @@ jobs:

- env:

REPORT_ROUTE_STATUS_URL: ${{ secrets.REPORT_ROUTE_STATUS_URL }}

REPORT_ROUTE_STATUS_AUTH: ${{ secrets.REPORT_ROUTE_STATUS_AUTH }}

- # For certain benchmarks, wirelength_analyzer/CheckPhysNetlist requires more memory than that available in GitHub Actions

- WIRELENGTH_ANALYZER_MOCK_RESULT: ${{ matrix.benchmark == 'koios_dla_like_large' }}

- CHECK_PHYS_NETLIST_DIFF_MOCK_RESULT: ${{ matrix.benchmark == 'koios_dla_like_large' }}

RWROUTE_FORCE_LUT_PINSWAPPING: ${{ (matrix.router == 'rwroute' || matrix.router == 'hao3') && matrix.lutpinswapping }}

RWROUTE_FORCE_LUT_ROUTETHRU: ${{ (matrix.router == 'rwroute' || matrix.router == 'hao3') && matrix.lutroutethru }}

- timeout-minutes: 10

run: |

make ROUTER="${{ matrix.router }}" BENCHMARKS="${{ matrix.benchmark }}" VERBOSE=1

- name: Score summary

diff --git a/Makefile b/Makefile

index 7fabf0d..f56c4ea 100644

--- a/Makefile

+++ b/Makefile

@@ -53,8 +53,8 @@ else

endif

ifdef GITHUB_ACTIONS

- # Limit Java heap size inside GitHub Actions to 6G

- JVM_HEAP = -Xms6g -Xmx6g

+ # Limit Java heap size inside GitHub Actions to 14G

+ JVM_HEAP = -Xms14g -Xmx14g

else

# If not specified, limit Java heap size ~32G

JVM_HEAP ?= -Xms32736m -Xmx32736m

@@ -119,12 +119,7 @@ fpga-interchange-schema/interchange/capnp/java.capnp:

fi

%_$(ROUTER).wirelength: %_$(ROUTER).phys | setup-wirelength_analyzer

- if [[ "$(WIRELENGTH_ANALYZER_MOCK_RESULT)" == "true" ]]; then \

- echo "::warning file=$<::wirelength_analyzer not run because WIRELENGTH_ANALYZER_MOCK_RESULT is set"; \

- echo "Wirelength: inf" > $@; \

- else \

- python3 wirelength_analyzer/wa.py $< $(call log_and_or_display,$@); \

- fi

+ python3 wirelength_analyzer/wa.py $< $(call log_and_or_display,$@); \

.PHONY: score-$(ROUTER)

score-$(ROUTER): $(foreach b,$(BENCHMARKS),$b_$(ROUTER).wirelength $b_$(ROUTER).check)

diff --git a/RapidWright b/RapidWright

index a858134..425d89e 160000

--- a/RapidWright

+++ b/RapidWright

@@ -1 +1 @@

-Subproject commit a85813419f86412e34930232f4131a83c4eac0b4

+Subproject commit 425d89e28cce0df648e2236a950efd035450438c

diff --git a/alpha_submission/rwroute_container.def b/alpha_submission/rwroute_container.def

index c1ade60..71f77b3 100644

--- a/alpha_submission/rwroute_container.def

+++ b/alpha_submission/rwroute_container.def

@@ -1,5 +1,5 @@

BootStrap: docker

-From: eclipse-temurin:17 # Base image with Java VM 17 on Ubuntu

+From: eclipse-temurin:17-jdk-jammy # Base image with Java VM 17 on Ubuntu 22.04

%post

# Install remaining system dependencies

diff --git a/docs/benchmarks.md b/docs/benchmarks.md

index c453015..663a1ea 100644

--- a/docs/benchmarks.md

+++ b/docs/benchmarks.md

@@ -41,8 +41,8 @@ Available from [https://github.com/Xilinx/fpga24_routing_contest/releases/latest

|Source Benchmark Suite|Benchmark Name|LUTs|FFs|DSPs|BRAMs|OOC [1]|

|----------------------|--------------|----|---|----|-----|-------|

-| [RapidWright](https://github.com/Xilinx/RapidWright) |`picoblaze_array` (660 PicoBlaze cores) |76k |77k |0 |0 |Y |

-| [Corundum](https://github.com/corundum/corundum) |`100g` (ADM_PCIE_9V3 25G) |76k |104k |0 |290|N |

+| [RapidWright](https://github.com/Xilinx/RapidWright) |`picoblazearray` (660 PicoBlaze cores) |76k |77k |0 |660|Y |

+| [Corundum](https://github.com/corundum/corundum) |`100g` (ADM_PCIE_9V3 100G) |76k |104k |0 |290|N |

| [Koios 2.0](https://docs.verilogtorouting.org/en/latest/vtr/benchmarks/#koios-2-0-benchmarks) |`clstm_like_large` (clstm_like.large) |89k |184k |1289|370|Y |

| [Titan23](https://docs.verilogtorouting.org/en/latest/vtr/benchmarks/#titan-benchmarks) |`orig_gsm_x6` (Original gsm_switch replicated 6 times) |133k|160k |0 |432|Y |

| [CoreScore](https://github.com/olofk/corescore) |`900` (900 SERV cores) |174k|210k |0 |451|N |

diff --git a/docs/results.md b/docs/results.md

index 9aeb5f6..d9053cd 100644

--- a/docs/results.md

+++ b/docs/results.md

@@ -17,6 +17,9 @@ For an overview of the reuslts, please see these [slides](fpga24-contest-slides.

**Team members:** Dani Maarouf, Timothy Martin, Charlotte Barnes

**Advisors:** Shawki Areibi, Gary Grewal

+Publication:

+- [A High-Performance Routing Engine for Large-Scale FPGAs](https://doi.ieeecomputersociety.org/10.1109/FPL64840.2024.00017)

+

| Overview | Video |

| - | - |

| [](https://github.com/Xilinx/fpga24_routing_contest/assets/90657806/5b279fc6-6c58-43f1-9b51-a0aef72dcf86) | |

@@ -26,6 +29,12 @@ For an overview of the reuslts, please see these [slides](fpga24-contest-slides.

**Team members:** Xinshi Zang, Wenhao Lin, Shiju Lin, Qin Luo

**Advisor:** Evangeline F.Y. Young

+Open-source: https://github.com/xszang/parallel-routing ([integrated upstream](https://github.com/Xilinx/fpga24_routing_contest/tree/2nd-cufr))

+

+Publications:

+- [An Open-Source Fast Parallel Routing Approach for Commercial FPGAs](https://github.com/xszang/parallel-routing/blob/main/doc/glsvlsi24-camera-ready.pdf)

+- Potter: A Parallel Overlap-Tolerant Router for UltraScale FPGAs *(to appear)*

+

| Overview | Video |

| - | - |

| [](https://github.com/Xilinx/fpga24_routing_contest/assets/90657806/9242ce96-6517-44c1-829f-f5c8f2d28339) | |

@@ -36,6 +45,9 @@ For an overview of the reuslts, please see these [slides](fpga24-contest-slides.

**Advisor:** Guojie Luo*

*\*Peking University, +DeePoly Technology Inc.*

+Publication:

+- [AceRoute: Adaptive Compute-Efficient FPGA Routing with Pluggable Intra-Connection Bidirectional Exploration](https://xmwei.com/assets/pdf/wei2024aceroute.pdf)

+

| Overview | Video |

| - | - |

| [](https://github.com/Xilinx/fpga24_routing_contest/assets/90657806/9d7dc7b6-e31d-44df-8e30-90a3f1f19daa) | |

@@ -45,6 +57,8 @@ For an overview of the reuslts, please see these [slides](fpga24-contest-slides.

**Team members:** Jiarui Wang, Xun Jiang, Chunyuan Zhao

**Advisor:** Yibo Lin

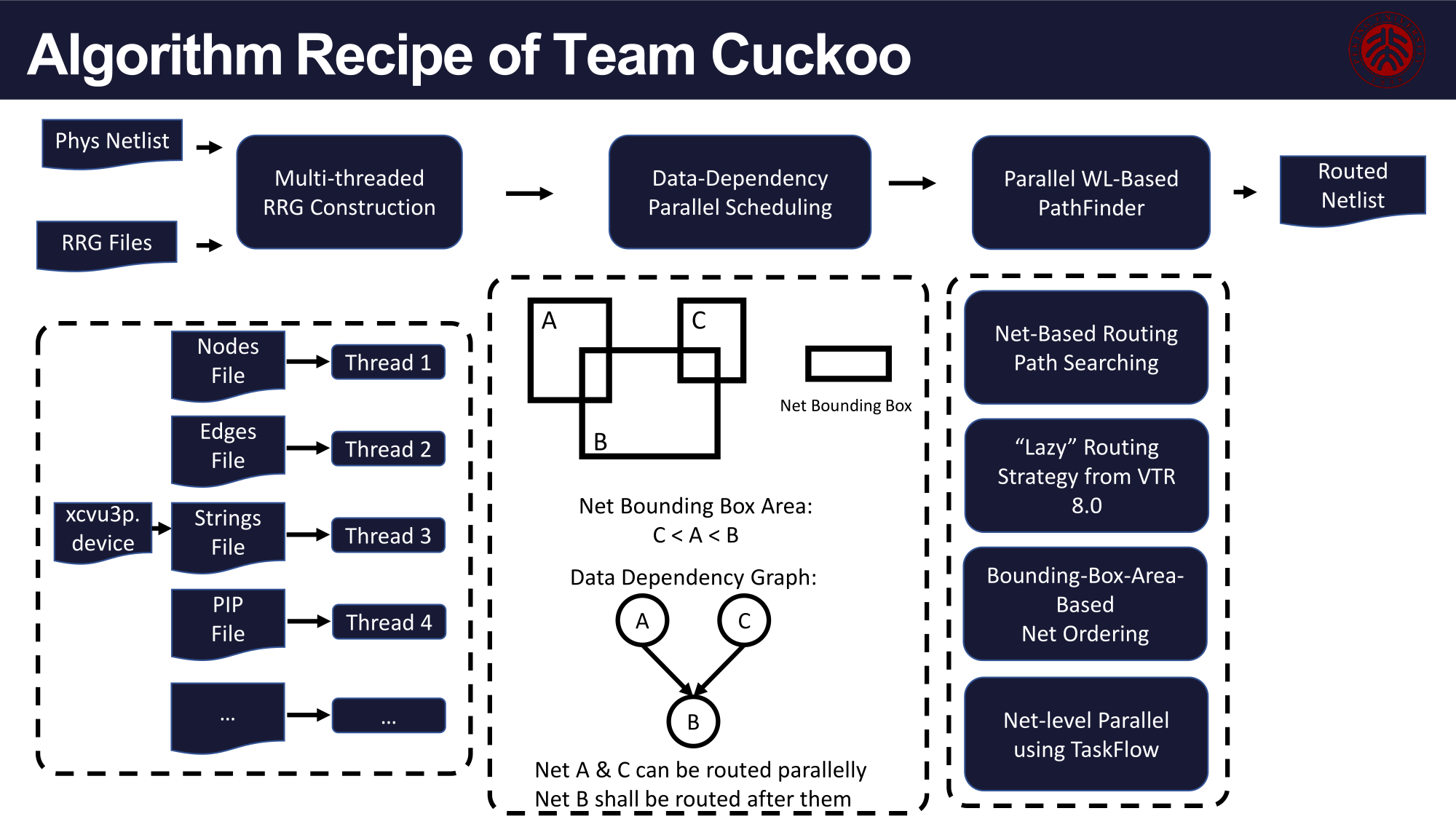

+Open-source: https://github.com/PKU-IDEA/OpenPARF/tree/master/fpga24contest ([integrated upstream](https://github.com/Xilinx/fpga24_routing_contest/tree/4th-cuckoo))

+

| Overview | Video |

| - | - |

| [](https://github.com/Xilinx/fpga24_routing_contest/assets/90657806/6483ab18-be08-4be3-ad46-8b69a5d13a55) | |

@@ -54,6 +68,8 @@ For an overview of the reuslts, please see these [slides](fpga24-contest-slides.

**Team members:** Wenbin Teng, Qianyu Cheng, Zhendong Zheng, Binze Jiang, Yixuan Zhu, Zihan Wang

**Advisors:** Chao Wang, Teng Wang

+Open-source: https://github.com/Reconfigurable-Computing/RapidWright ([integrated upstream](https://github.com/Xilinx/fpga24_routing_contest/tree/5th-hao3))

+

| Overview | Video |

| - | - |

| [](https://github.com/Xilinx/fpga24_routing_contest/assets/90657806/14b148e3-55a4-48e8-a0ee-88f19498b253) | |

diff --git a/final_submission/rwroute_container.def b/final_submission/rwroute_container.def

index 66df688..2bfa99d 100644

--- a/final_submission/rwroute_container.def

+++ b/final_submission/rwroute_container.def

@@ -1,5 +1,5 @@

BootStrap: docker

-From: eclipse-temurin:17 # Base image with Java VM 17 on Ubuntu

+From: eclipse-temurin:17-jdk-jammy # Base image with Java VM 17 on Ubuntu 22.04

%files

## Example copy of /dir1 into /opt inside container

diff --git a/src/com/xilinx/fpga24_routing_contest/CheckPhysNetlist.java b/src/com/xilinx/fpga24_routing_contest/CheckPhysNetlist.java

index fbc8b76..b3c23f7 100644

--- a/src/com/xilinx/fpga24_routing_contest/CheckPhysNetlist.java

+++ b/src/com/xilinx/fpga24_routing_contest/CheckPhysNetlist.java

@@ -57,17 +57,12 @@ public static void main(String[] args) throws IOException, InterruptedException

// Read the routed and unrouted Physical Netlists

Design routedDesign = PhysNetlistReader.readPhysNetlist(args[1]);

- int numDiffs = 0;

- if ("true".equals(System.getenv("CHECK_PHYS_NETLIST_DIFF_MOCK_RESULT"))) {

- System.out.println("::warning file=" + args[1] + "::CheckPhysNetlist's DesignComparator not run because CHECK_PHYS_NETLIST_DIFF_MOCK_RESULT is set");

- } else {

- Design unroutedDesign = PhysNetlistReader.readPhysNetlist(args[2]);

+ Design unroutedDesign = PhysNetlistReader.readPhysNetlist(args[2]);

- DesignComparator dc = new DesignComparator();

- // Only compare PIPs on static and clock nets

- dc.setComparePIPs((net) -> net.isStaticNet() || net.isClockNet());

- numDiffs = dc.compareDesigns(unroutedDesign, routedDesign);

- }

+ DesignComparator dc = new DesignComparator();

+ // Only compare PIPs on static and clock nets

+ dc.setComparePIPs((net) -> net.isStaticNet() || net.isClockNet());

+ int numDiffs = dc.compareDesigns(unroutedDesign, routedDesign);

if (numDiffs == 0) {

System.out.println("INFO: No differences found between routed and unrouted netlists");

} else {