# **Research Project Report**

# Design, Implementation and Test of a Networks-on-Chip (NoC) Router using VHDL

| Course Code CSE215 | Course Name Electronic Design Automation |                                |  |

|--------------------|------------------------------------------|--------------------------------|--|

|                    | Semester<br>Spring 2020                  | Date of Submission<br>3/6/2020 |  |

| # | Student ID | Grade (PASS/FAIL) |

|---|------------|-------------------|

| 1 | 17P5026    |                   |

| 2 | 17P6069    |                   |

| 3 | 17P8182    |                   |

| 4 | 17P3061    |                   |

| 5 | 17P8042    |                   |

In case of group research; list all students IDs. DO NOT WRITE STUDENTS NAMES

"I certify that this report is my own work, based on my personal study and/or research and that I have acknowledged all material and sources used in its preparation, whether they are books, articles, reports, lecture notes, and any other kind of document, electronic or personal communication. I also certify that this report has not been previously been submitted for assessment for another course. I certify that I have not copied in part or whole or otherwise plagiarized the work of other students and / or persons."

#### # Student ID **Student Signature** Ahmed Khaled Aly 1 17P5026 2 Andrew Yasser Shaker 17P6069 3 17P8182 George Emad Younan 4 17P3061 Karim Mikhael Farid 17P8042 Youssef Emad 5

### STUDENTS MUST SIGN THIS PAGE. ELECTRONIC SIGNATURE IS ACCEPTED.

In case of group research; list all students IDs. DO NOT WRITE STUDENTS NAMES

# Table of Contents:

| N | Section                                    | Covered ILOs               |

|---|--------------------------------------------|----------------------------|

| 1 | Introduction                               | c2                         |

| 2 | Design Flow                                | a1, a3, a6, a7             |

| 3 | Literature Review                          | a1, a6, a7, b4, c2, d1, d2 |

| 4 | Design Implementation                      | a1, a2, a4, b3, c1         |

| 5 | Schedular Design and FSM<br>Implementation | a2, a4, a5, b1, b2, b3     |

| 6 | Test and Simulation Results                | a1, a4, b3, b4             |

| 7 | Conclusion                                 | a5, b1, c1                 |

| 8 | Task Distribution List                     |                            |

# **1.0 Introduction:**

This project is aimed to design and implement a tested simple router using a synthesizable VHDL code. routers are used in computer networks applications, by forwarding data in packets format across a network toward the desired destinations using a process called "routing" that use headers and forwarding tables to guarantee the best path for the packets to be forwarded according to design requirements.

The paradigm of Network on chip provides an integrated solution for achieving shorter delays in communication and efficient interconnection between process elements, but have limited silicon area, this makes it sort of a difficult task to design NoC-based systems.

The categorization of NOC Routers is done based on two different characteristics: The location of queues and buffers within the router, and the switch fabric type. There are four main types of routers:

- 1. Input-queue routers

- 2. Output-queue routers

- 3. Shared-queue routers

- 4. Input/output-queue routers

The position of queues inside the routers is crucial; as it directly affects the delay of the router, quality of service, and packet loss.

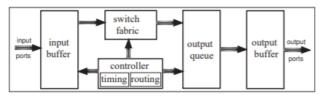

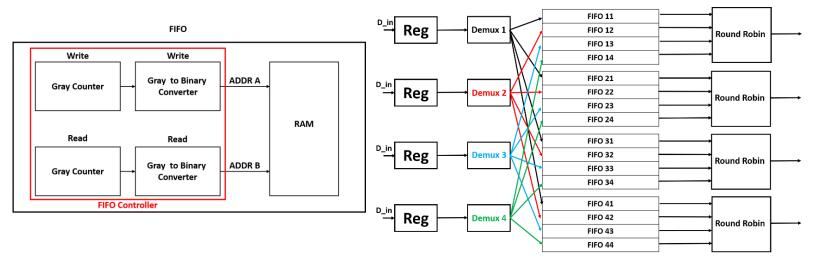

The router has 4 main building blocks: the input buffer – the switch fabric – the output queue – the output buffer. The data packets are stored at the input buffer once it arrives asynchronously with packet ready signal indicator (PR).

Then controller reads the packet header and configures the SF to direct the packet to the suitable queue (output buffer), which is a bunch of FIFOs buffers synchronized with both clock edges. The controller does the routing tables and timing synchronization. the output buffer delivers the packet from the FIFOs to output ports depending on target destination availability using a round robin scheduler algorithm.

Fig#1.1: Block diagram for an output-queue router

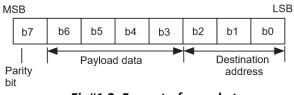

This RR algorithm serves the waiting queues one after the other in a fixed order at the output, using a signal called receive ready which indicates the availability of the target destination. Packets are sent to the next hop with Packet Sent (PS) signal for synchronization purposes. The packet is an eight bits data represented in the form of: first three bits represents the destination address; the following four bits has the sent data and the most significant bit is for parity check for errors.

Fig#1.2: Format of a packet

This project consists of several modules that combine to make the router: 8 bits register – 8 bit Demux – Block Ram – a Gray counter – Gray to binary converter – FIFO module – FIFO controller – Round Robin Schedular – A Module to combine these modules. The Gray code is used here to facilitate error detection.

During this project, It was assumed that:

- A round robin schedular was used

- The packet input is already in the desired format

- Write ready turns to 0 after clock cycle

• In the packet header, 2 bits only are use as there are 4 output buffers only The project was done on Xilinx ISE CAD tool starting from the design specification and was coded in VHDL language and passed through behavioral simulation then synthesis process then the post synthesis simulation down to placing and routing and time analysis simulation to generate the bit file.

# 2.0 Design Flow:

There are two types of technology when we think about chip design and production: FPGA & AISEC.

The AISEC: Application specific integrated circuit technology, which mostly being used in critical systems where security is crucial, is an expensive technology. However, it can be used where mass producing chips is requested.

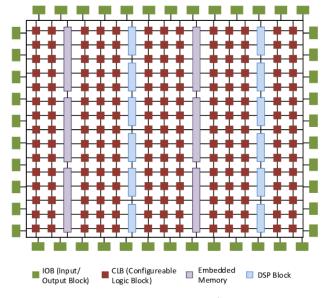

The FPGA: field programmable chips that has logic blocks, I/O bloc, memory elements and high resources unlike CPLDs that have lower resources.

Fig#2.1: Architecture of FPGA

FPGA can be reprogrammed to provide different functionalities as requested. It also can be easily tested. It can't be used in mass productions.

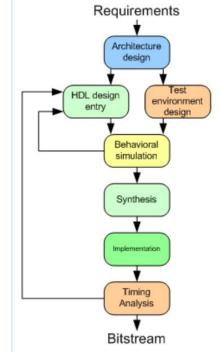

There are 4 main phases in the FPGA design flow: Design – simulation – synthesis, analysis and verification – layout, manufacturing preparation.

# **Design:**

The design flow is started with the design (high-level design) phase that use specification sheet to define: the input ports size, datatypes, restrictions on waveforms entering the input, required clock frequency, time constraints in general that defines the relations of these signals with each other , the output required size and data types and synchronization with clock details; the block functionality of the project in between which helps the designer to detect a design approach to help executing the required function.

These languages (VHDL or Verilog) are used to isolate the designers from the details of the hardware implementation compared to other techniques. Some designs can be described using system level languages to describe the transactions that happens in hardware.

Some designs can be described by its schematic connections between components using schematic entry or table entry to give much more visibility into the hardware. IP integrators can be used to connect components in design to construct the system, making it easier to modify components, it is considered as semi-automated design as the IPs are already designed and is just integrated.

# **Behavioral Simulation:**

After the high-level design, comes the behavioral simulation (RTL Simulation) to check if the design meets the exploitations from the functional view (check for the functionality of the design). If it passes then we take the design to synthesis, which finds out equivalent hardware gates or components that represent the hardware description written in the code.

### Synthesis :

the synthesis Process takes inputs the VHDL or Verilog code and outputs a netlist that defines every basic component (gates, flip flops, etc...) chosen from desired technology and connections. This can be made using VHDL or Verilog or spice, or many options and there are many different tools for synthesis are based on the chosen technology, and the area of silicon is detected to know if it can fit in wafer or FPGA according to target implementation, it also gives timing, and power consumption analysis.

# Verification techniques:

One of the verification techniques is gate comparison is comparing the output of the synthesis tools against the RTL gates. This helps proving that there is no change happened when synthesis happened. This is made before fabrication.

Other verification techniques are code coverage analysis, assertion analysis, functional coverage analysis, constraints random simulations. Those help to prove that testcases asserted in simulation covered all parts in the code and all the implementations or gates that are produced in synthesis, also makes sure that there is no part in the code is not relevant to the design as a security factor and quality assurance.

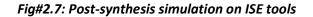

# Post synthesis simulation:

After synthesis the target technology is detected and the timing information of this technology is added e.g. setup time, hold time, and propagation delay of combinational logic. Post synthesis simulation is done to know if the design meets requirements after those parameters are added or not. Then equivalent gate count of design is precisely detected. This is used to compare implementation of different technologies.

# Layout phases:

After this comes placement and routing (physical synthesis) to put the components in their physical places in chip and the files (GPS for ASIC or bit stream for FPGA. After placement and routing a third simulation **(Static Timing Analysis)** is done considering additional factor of placement and routing on chip, as the transition of data within the micrometer of chip (signal path) can cause certain delays that may affect the critical path in circuit. So, simulation of signals is done three times in total. A bitstream file containing the programming information of FPGA is generated. Then Bit code is placed on the FPGA when I connect the cable to the computer. Then comes planning of Flip flop and the auto flow of the placement and route.

# Additional procedures that can be done:

Another model is the emulation which is making one of the

components in design as logic analyzer (internal logic analyzer) that its pins are connected to test points internally in chip. and the output is serial to serial port to be read on software tool. This allows us to enter in depth and point some parameters that can't be inspected easily. this happens at runtime, sampling and waveforms occur at simulator to check for the signals.

Thermal simulations for chips while working by color coding the amount of dissipated power can be detected along with the hotspot in the chip.it is very important to balance that dissipation (heat sinks or fans needed).

Points or tracks in chip which has high clock frequency may have different fabrication techniques to prevent interference by shielding or changing the layout to meet design specs using transmission line models to model those tracks. This helps seeing the effect on near tracks. BIT file is generated to be used to configure the target FPGA device using a cable.

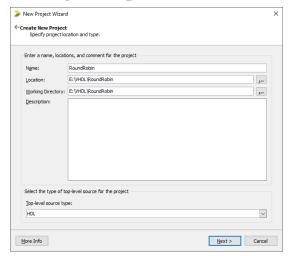

CAD tools like the Xilinx ISE help to go develop designs through various

#### design flow phases:

| elect the device and design flow for the p | roject              |   |

|--------------------------------------------|---------------------|---|

| Property Name                              | Value               |   |

| Evaluation Development Board               | None Specified      | ~ |

| Product Category                           | All                 | ~ |

| Family                                     | Spartan6            | ~ |

| Device                                     | XC6SLX4             | ~ |

| Package                                    | TQG144              | ~ |

| Speed                                      | -3                  | ~ |

| Top-Level Source Type                      | HDL                 |   |

| Synthesis Tool                             | XST (VHDL/Verilog)  | ~ |

| Simulator                                  | ISim (VHDL/Verilog) | ~ |

| Preferred Language                         | VHDL                | ~ |

| Property Specification in Project File     | Store all values    | ~ |

| Manual Compile Order                       |                     |   |

| VHDL Source Analysis Standard              | VHDL-93             | ~ |

| Enable Message Filtering                   |                     |   |

Fig#2.3: Creating new project on ISE

Fig#2.4: determining family from Spartan, Vertex, Kintex & Artix

The tool allows renaming files and choosing the input and output ports (names & types) and choosing the type of files from various types like: VHDL or Verilog module, Testbench module, User constraint files or even embedded processors. In addition to many facilities like syntax checking in addition to all three types of simulations.

| Elle name: Andrew Logation: E:WHDL RoundRobin |

|-----------------------------------------------|

|                                               |

| Define Module<br>Specify ports | for module. |         |        |     |     |     |   |

|--------------------------------|-------------|---------|--------|-----|-----|-----|---|

| Entity name                    | Fifo        |         |        |     |     |     | _ |

| Architecture name              | Behavioral  |         |        |     |     |     | _ |

|                                | Port Name   | Directi | on     | Bus | MSB | LSB |   |

| a                              |             | in      | $\sim$ |     |     |     |   |

| b                              |             | in      | $\sim$ |     |     |     |   |

| c                              |             | out     | $\sim$ |     |     |     |   |

| d                              |             | inout   | $\sim$ |     |     |     |   |

|                                |             | in      | $\sim$ |     |     |     |   |

|                                |             | in      | $\sim$ |     |     |     |   |

|                                |             | in      | $\sim$ |     |     |     |   |

|                                |             | in      | $\sim$ |     |     |     |   |

|                                |             | in      | $\sim$ |     |     |     |   |

|                                |             | in      | _      | _   |     |     |   |

Fig#2.6: Creating new file and choosing type

Fig#2.5: Creating new file and choosing type

# **Simulations with Xilinx ISE:**

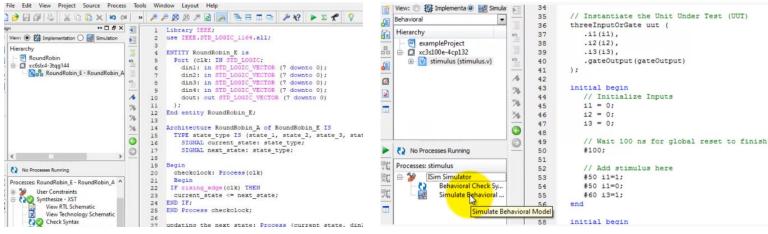

**behavioral Simulation** or RTL Simulation is performed before synthesis process to check for the functionality of the design. It can be performed on VHDL or Verilog codes. In this process, signals and variables are observed, procedures and functions are traced carefully. It is a quick simulation that allows t to change the code. This happens if the design does not perform the required functionality. As this happens before the process of synthesis, timing and resource usage properties are not known.

**Post synthesis Simulation** is the second step that gives information about the logic operation of the circuit. to know if the design meets requirements after the target technology is detected and the

timing information of this technology is added after the translate process. If the functionality is not as expected, then the designer has to modify the code and follow the design flow steps again.

**Static Timing Analysis**, which is the third step can be done after MAP or Place and route processes. After mapping process, a timing report lists delays of signal paths taken from the design logic. Post Place and Route timing report shows information about timing delays to provide a useful summary of timing of the design.

Fig#2.8: syntax Check process on RR module by ISE tools

Fig#2.10: example of behavioral simulation results on ISE

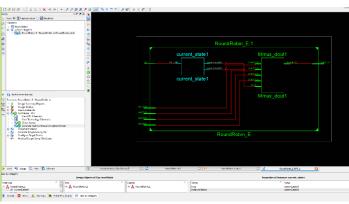

Fig#2.11: RTL schematic of Round Robin on ISE

The ISE Xilinx tools allow us to define constraints. This is assigning the ports in the design to the physical elements (ex. pins, switches, buttons) of the device & specifying time requirements of the design and the info is stored in UCF file (user constraints file).

Fig#2.12: UCF file in ISE tool

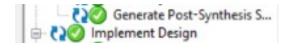

The process of Synthesis Implementation is done on three steps on the ISE:

1. Translate: The input constraints and netlists are added together in a logic design file

2. Map: to fit the defined logic, which is Combinational Logic Blocks (CLB), Input Output Blocks (IOB). It generates a file which physically represents the design mapped to the components of FPGA.

3. Place and Route: places the sub blocks from the map process into logic blocks according to the constraints and connects the logic blocks.

Fig#2.13: Implementation steps of Round Robin module on ISE tool

|                                                                                  | Organize 👻 New folder         | l≡ • 🔟 (                                                |

|----------------------------------------------------------------------------------|-------------------------------|---------------------------------------------------------|

| Ele Edit View Ogerations Qutput Debug Window Help                                |                               |                                                         |

|                                                                                  | This PC Name                  | Date modified Type                                      |

| ACT Flows ↔ □ ♂ ×<br>Standary Scan Standary Scan                                 | 3D Objects                    | 5/31/2020 11:22 AM File folder                          |

| Soundary Scan     SystemACE     SystemACE     Create PROM File (PROM File Format | Desktop                       | 5/31/2020 11:26 AM File folder                          |

| Create PROM File (PROM File Format     TDI                                       | Documents ipcore_dir          | 5/31/2020 11:19 AM File folder                          |

|                                                                                  | iseconfig                     | 5/31/2020 11:16 AM File folder                          |

| xc6sk4<br>mrou08.bit                                                             | Downloads netgen              | 5/31/2020 11:23 AM File folder                          |

| TDO                                                                              | Music                         | 5/31/2020 11:22 AM File folder                          |

|                                                                                  | Fictures xst                  | 5/31/2020 11:22 AM File folder                          |

|                                                                                  | 🔐 Videos 🚺 mrou08.bit         | 5/31/2020 11:25 AM BIT File                             |

|                                                                                  | 🏪 Local Disk (C:)             |                                                         |

|                                                                                  | Local Disk (E:)               |                                                         |

| CT Processes ++ D & ×<br>ilable Operations are:                                  | Local Disk (F:)               |                                                         |

| Japie Operations are:<br>Program<br>Get Device ID                                | 💣 Network 🗸 <                 |                                                         |

| Get Device Signature/Usercode<br>Read Device Status                              | File <u>n</u> ame: mrou08.bit | <ul> <li>All Design Files (*.jed *.bit *.rbt</li> </ul> |

| One Step SVF<br>One Step XSVF<br>Read Device DNA                                 |                               | <u>Open</u> Cancel                                      |

Fig#2.14: of 8-bits

register module on ISE tool

Fig#2.15: saving bit file of 8-bits register module on ISE tool

# 3.0 Literature Review:

- We will sort the References including papers and books that contains useful data about "NOC Routers implementation" in chronological order:

- 1- L. Benini and G. D. Micheli, "Networks on chips: A new SoC paradigm," IEEE Computer Magazine, vol. 35, no. 1, pp. 70–78, Jan. 2002.

In this article the problems of SOC (System-on-chip) is discussed, and the article introduces the NOC (Networks-on-chip) as a borrowed concept from the network engineers to get over the problems of the SOC.

- 2- LogicCore. (2004, Nov. 11,) Xilinx Technical Document, Asynchronous FIFO v6.1.

Product Specification DS232

In this article, an Asynchronous FIFO is implemented and illustrated, diagrams and tables are also implemented.

- 3- Haytham El Miligi, "Networks-on-Chips: Modeling, Analysis, and Design Methodologies," Victoria, B.C., Canada: 2011

- 4- Minakshi M. Wanjari, Pankaj Agrawal, R. V. Kshirsagar "Design of NoC Router Architecture using VHDL," India: International Journal of Computer Applications (0975 – 8887) Volume 115 – No. 4, April 2015.

In this paper, NoC router architecture is presented, which has low latency and requires less area. Also, a design is implemented in VHDL and simulated.

5- Benini and G. D. Micheli returned again in 2017 with a new article: "Networks on Chips: 15 Years Later" to discuss their article from 2002 (mentioned above), and how virtually all large-scale chips are now designed with this paradigm (NOC).

# **4.0 Design Implementation:**

#### **The Register Module:**

This module has 4 inputs, and one output, the input datat\_in is entered in the registered and outputted if and only if Clock\_En = 1 AND Reset = 0. (and its outputted when the clock edge is positive). If the reset clock edge is 1 the output is set to zeros. And if the Clock\_En is zero the current output value remains as it is.

The register module was implemented by using a simple If condition, if the reset is equal to 1 then the data\_out is zeros, else if the clock is on the rising edge and the clock enable is equal to 1 then the data is outputted (data\_out = data\_in)

## The 8-bit DeMux:

A vector of 8 bits is inputted in the demux and outputted if the En = 1, but if the En is 0 the port keeps its value. But its outputted to the port depending on the selector of the demux. There are 4 output ports and therefore the selector is 2 bits. (00 for the  $1^{st}$  output, 01 for the  $2^{nd}$ ..etc). The demux is implemented using an if condition and a switch case, if the enable is 1 then we navigate to the switch case, when the selection is 00 the first data is selected, when the selection is 01 the  $2^{nd}$  is selected..etc. the sensitivity list of the process is the enable, the data in and the selection.

#### **Block Ram:**

This module receives data (a vector of 7 bits) and it has another 3 parameters for read and 3 for write. So the first parameter is the enable, where if its equal to 1 its going to allow reading/writing. Then the address port (read/write) can be set to whatever value desired to be read from or written to. The reason why the address port is 3 bits is because there are 8 slots in the ram. And 3 bits can express 8 values.

So whenever the clock of read/write hits 1, and the read/write enabled, the read/write happens to the address selected from the 8 addresses. The code of the block ram was implemented using 2 processes, their sensitivity list is the CLKS (A,B). If the clk's triggered, then we check if the Write/read is enabled, then by a simple switch cases, we select which slot of the ram to read or write according to the pointer value.

#### **Gray Counter:**

This module is a simple counter. It increments on the rising edge of a clock whenever the Enable signal is set to 1. The reset sets it to 0. And it also counts in a gray code manner: 000, 001,011,010,110,111,101,100. The counter is implemented by using a process of a sensitivity list clock and reset, if the reset is equal to 1 then the output is restarted, else if both the clock is triggered and the enable is equal to 1, a switch case is executed, where for each case, the output is that case + 1, so if its 000 the output is 001...etc.

# **Gray Converter:**

This module converts the output of the counter to binary, because the ram, FIFO controller works in binary and not gray. It simply changes the truth table

000, 001,011,010,110,111,101,100 To 000,001,010,011,100,101,110,111. The gray converter was implemented through a very simple mapping 3 line code, the most significant bit on the output is equal to the most significant bit of the input, the 2<sup>nd</sup> most significant bit on the output Is equal to the most significant bit in the input XORed with the 2<sup>nd</sup> most significant bit on the input. And the last bit on the output is the 3 bits of the input XORed together.

### **FIFO Controller:**

This module contains 2 previous components discussed, converter and counter.

Whenever the reset signal is 1 the module restarts, meaning write and read valids are equal to 0, pointers are zeroed, empty is set to 1 and full is set to 0.

Only when the read/write clock is 1, the module is capable to perform read/write operations. So the module receives read/write requests. And it can't perform reading if the FIFO is empty, simultaneously it cannot write to a full FIFO. And this is what sets the read / write valid signals. The code implementation here was done by creating 2 components (instantiations) of a counter, and 2 components of a converter, one for the read and one for the write, each with their counters connected to the gray to binary converter, and then connected to the pointers, the main process of the fifo controller has the signals: read request, write request and reset in the sensitivity list. There are 2 if conditions. The first one is written for the write request and the 2<sup>nd</sup> is for the read request, so concerning the first one, if the reset is equal 1 then full is 0 and empty is 1, else if the request is 1 then we check if the read pointer is equal to the write pointer + 1 (which means that the FIFO is full). So the request is neglected and the valid is set to 0, and full is set to 1 else the valid is set to 1. Concerning the 2<sup>nd</sup>, if the reset is equal to 1 then full is 0 and empty to 1, else if the request is 1 then we check if the 2 pointers are equal, and if they are then the FIFO is empty and there is nothing to read from it. And the read valid is set to 0/ empty set to 1 in that case, else the read valid is set to 1.

## FIFO:

This module contains the FIFO Controller and the Ram. The datain is written into the FIFO (of course following the restrictions based on the FIFO controller) and gets read using the dataout signal (also accordingly with the FIFO controller). The rclk and wclk are mapped with the rdclk and wrclk of the FIFO controller, respectively. And the rreq wreq signals are mapped with the r\_req and w\_req signals, respectively. Read/write pointers of the fifo controller are connected to the ram's read/write addresses (through the converter and the counter).

As for the implementation of this module, it didn't contain any logic. It was just mapping the 2 components FIFO controller and Ram. So basically we create 2 components. We map all of the FIFO's signals to the controller except the data\_in, which gets mapped to the ram. The read and write pointers also gets into the ram from the fifo, and the write valid read valid which are outputted from the fifo controller gets into the ram as the enables. The clocks get into the ram as well. And the ram's main output is the data\_out which is mapped to the FIFO's main output.

#### **Round Robin Schedular:**

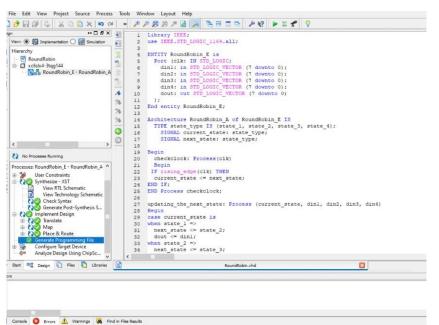

This module is a round robin schedular that takes 4 inputs. Each rising edge of the clock the output differs from the 4 FIFOs. Meaning at the first clock cycle the output is taken from d\_in(1), and at the second clock cycle the output is d\_in(2). The schedular was implemented by using a two process moore implementation. One for checking the clock , and one for updating the next state and checks for the current state.

#### **Router:**

The router contains 4 registers, 4 demuxes, 4 round robin schedular and 16 FIFOs. The data gets into the registers, in the form of a packet, the register is just a buffer. So if the register receives clock en, it outputs the data, if it gets a reset, it zeroes the data. The demux receives a selection line (which is discussed earlier) from the first 2 bits in the data, which is going to select the where is the destination of the output. Every demux has 4 FIFOs connected. A FIFO for each output. The data is transferred from the demux to the FIFO. The Rclock (R-request) is designed so that every clock cycle a type of FIFO works, There are 4 types of FIFOs, for every port there is a type FIFOs 1,2,3,4 connected

to output ports 1,2,3,4. For example, every clock cycle a FIFO with no. 11,21,31,41 works, (with one at the end), because they are connected to different round robins. Round robin takes the data from 4 FIFOs, and the data is outputted through one output.

The implementation was by creating 4 components of registers, 4 components of demux, 4 components of Round Robins, and 16 Components of FIFOs, then they were mapped as shown in the figure.

### The router module's logic has 4 processes:

In the first process, the sensitivity list is the selection variables of all the demuxes, so that the demux can choose which FIFO the packet should go to. The second process is responsible for syncing the demuxes, by using the wclock as a sensitivity signal. So whenever its on its rising edge, the write request happens throughout the FIFOs, only when 3 things happens, the write signal is 1, the reset is not 0, and the enable is available. The third process checks for the readclock, and reset, if the reset is 1 the state is the same, if the clock is triggered, the state is transitioned. The fourth process is responsible for the read syncing (round robin). Its implemented by switch case, where the variable is the current state, so at a given state, the current state increments to the next state, and the read sync is updated.

Fig#4.1: created block Diagram of FIFO

Fig#4.2: created block Diagram of router

## **5.0 Schedular Design and FSM Implementation:**

#### **Scheduler Design:**

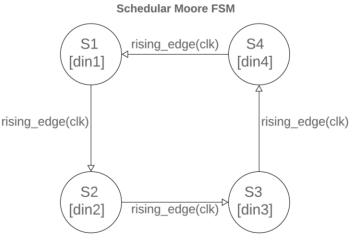

The scheduler is implemented using Moore way, as the output is generated depending on the current state only unlike Mealy which needs the current state and the input value. In the scheduler, the output is equal to the right din (input) according to the state the FSM is in right now. The scheduler is shown in the figure.

#### **Different Implementation Styles:**

Finite state machines can be implemented in VHDL by doing certain 4 tasks which are:

- 1) Asynchronous Reset (RS), 2) Update current state (CS),

- 3) <u>Determine next state (NS)</u>, 4) <u>Generate output (OP)</u>.

These tasks can be implemented in three different styles which are:

- One process: All 4 tasks are made in one process which has sensitivity list of (clock, reset, current state, inputs) for Mealy or (clock, reset, current state) for Moore. This style is not preferred as it is less readable from the others, but it is easier to debug.

- Two processes: The tasks are divided on two processes. The first do the RS and CS while the other do NS and OP. The sensitivity list of P1 is (clock, reset) while P2 is (current state, inputs) in a Mealy or Moore FSM.

- Three processes: P1 do RS and CS, P2 do NS and P3 do OP. Sensitivity list of P1 and P2 is the same for Mealy or Moore which is (clock, reset) for P1 and (current state, inputs) for P2 while P3 is (current state) for Moore and (current state, inputs) for Mealy.

#### Synthesis analysis:

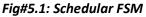

The scheduler code is synthesized into:

- Flip flop: As in the updating current state process there is an if condition that checks the <u>rising edge</u> of the clock and the sensitivity list is on the <u>clock</u>, so a flipflop is infered.

- 2) Two multiplexers: As there is a switch case on the present state which make two things, which are determine next state and generate the output. Therefore, they are two MUXs that have current state as selectors.

The flip flop gets the next state as input and with the rising edge of clock it produces the current state which acts as a selector for the 2 MUXs, so that the first one produces the selected next state that goes into the flip flop while the second MUX

produces the right output from the selected input.

| s the<br>utput |                   | 2b01 st<br>2b10 st<br>2b11 st | tate_1<br>tate_2<br>tate_3 |                                          |                      |

|----------------|-------------------|-------------------------------|----------------------------|------------------------------------------|----------------------|

| the            | /roundrobin_e/clk |                               |                            | state_1<br>state_2<br>state_3<br>default | > /roundrobin_e/dout |

Fig#5.2: Schedular Schematic

# **Timing Analysis:**

#### $T_{C} \geq t_{pcq} + t_{pd} + t_{setup}$

The clock time should be bigger than or equal to the propagation delay of the combinational circuit **plus** the clock to output propagation delay plus the setup time of the flip flop.

In the scheduler the critical pass is the one between the flip flop and next state MUX.

Fig#5.3: Schedular's critical path

Therefore, the minimum cock cycle can be is  $\mathbf{t}_{pcq}$  of flip flop +  $t_{pd}$  of the MUX +  $t_{setup}$  of flip flop.

While  $t_{hold}$  of flip-flop must be less than or equal  $t_{cd}$  of the MUX plus  $t_{ccq}$  of flip flop. Lastly, slack = Tc - tsetup - tpcq + tpd.

# **Timing Report**

NOTE: THESE TIMING NUMBERS ARE ONLY A SYNTHESIS ESTIMATE.

FOR ACCURATE TIMING INFORMATION PLEASE REFER TO THE TRACE REPORT

GENERATED AFTER PLACE-and-ROUTE.

#### **Clock Information:**

|              | +     | +                   |

|--------------|-------|---------------------|

| Clock Signal | •     | fer(FF name)   Load |

| clk          | BUFGP | 2                   |

|              | ++    | +                   |

Asynchronous Control Signals Information:

-----

No asynchronous control signals found in this design

**Timing Summary:**

-----

Speed Grade: -3

Minimum period: 2.190ns (Maximum Frequency: 456.663MHz)

Minimum input arrival time before clock: No path found Maximum output required time after clock: 5.021ns Maximum combinational path delay: 5.402ns

Timing Details:

-----

All values displayed in nanoseconds (ns)

Timing constraint: Default period analysis for Clock 'clk'

Clock period: 2.190ns (frequency: 456.663MHz) Total number of paths / destination ports: 3 / 2

| Delay:        | 2.190ns (Levels of Logic = 1) |

|---------------|-------------------------------|

| Source:       | current_state_FSM_FFd2 (FF)   |

| Destination:  | current_state_FSM_FFd2 (FF)   |

| Source Clock: | clk rising                    |

| Destination C | lock: clk rising              |

Data Path: current\_state\_FSM\_FFd2 to current\_state\_FSM\_FFd2

Gate Net

Cell:in->out fanout Delay Delay Logical Name (Net Name)

------ ------

FD:C->Q 10 0.447 0.856 current\_state\_FSM\_FFd2 (current\_state\_FSM\_FFd2)

| INV:I->O 1 0.206 0.579 current_state_FSM_FFd2-<br>In1_INV_0 (current_state_FSM_FFd2-In)<br>FD:D 0.102 current_state_FSM_FFd2                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Total 2.190ns (0.755ns logic, 1.435ns route)<br>(34.5% logic, 65.5% route)                                                                                                                                  |

| Timing constraint: Default OFFSET OUT AFTER for Clock 'clk'<br>Total number of paths / destination ports: 16 / 8                                                                                            |

| Offset:5.021ns (Levels of Logic = 2)Source:current_state_FSM_FFd2 (FF)Destination:dout<7> (PAD)Source Clock:clk rising                                                                                      |

| Data Path: current_state_FSM_FFd2 to dout<7><br>Gate Net                                                                                                                                                    |

| Cell:in->out fanout Delay Delay Logical Name (Net Name)                                                                                                                                                     |

| FD:C->Q 10 0.447 1.221<br>current_state_FSM_FFd2 (current_state_FSM_FFd2)<br>LUT6:I0->O 1 0.203 0.579 Mmux_dout11<br>(dout_0_OBUF)<br>OBUF:I->O 2.571 dout_0_OBUF (dout<0>)                                 |

| Obol 120         2.371         dout_0_0bol (dout<02)           Total         5.021ns (3.221ns logic, 1.800ns route)         (64.2% logic, 35.8% route)                                                      |

| Timing constraint: Default path analysis<br>Total number of paths / destination ports: 32 / 8                                                                                                               |

| Delay: 5.402ns (Levels of Logic = 3)<br>Source: din2<7> (PAD)<br>Destination: dout<7> (PAD)                                                                                                                 |

| Data Path: din2<7> to dout<7><br>Gate Net<br>Cell:in->out fanout Delay Delay Logical Name (Net                                                                                                              |

| Name)                                                                                                                                                                                                       |

| IBUF:I->O       1       1.222       0.827       din2_7_IBUF         (din2_7_IBUF)       1       0.203       0.579       Mmux_dout81         (dout 7_0PUE)       1       0.203       0.579       Mmux_dout81 |

| (dout_7_OBUF)<br>OBUF:I->O 2.571 dout_7_OBUF (dout<7>)                                                                                                                                                      |

| Total          | 5.402ns (3.996ns logic, 1.406ns route)<br>(74.0% logic, 26.0% route) |

|----------------|----------------------------------------------------------------------|

| Creas Cleak D  |                                                                      |

| Cross Clock De | omains Report:                                                       |

|                |                                                                      |

| Clock to Setup | o on destination clock clk                                           |

| +-             | +                                                                    |

| Src            | :Rise  Src:Fall  Src:Rise  Src:Fall                                  |

| Source Clock   | Dest:Rise Dest:Rise Dest:Fall Dest:Fall                              |

-----+

clk | 2.190| | |

Total REAL time to Xst completion: 15.00 secs Total CPU time to Xst completion: 14.98 secs -->

Total memory usage is 4492644 kilobytes Number of errors : 0 ( 0 filtered) Number of warnings : 0 ( 0 filtered) Number of infos : 0 ( 0 filtered

| Tested           |      |      |      | <u>Inputs</u> |    |    |    |    | <u>Outputs</u> |          |          |          |       |  |  |  |

|------------------|------|------|------|---------------|----|----|----|----|----------------|----------|----------|----------|-------|--|--|--|

| <u>feature</u>   | Data | Data | Data | Data          | wr | wr | wr | w  | Dataout1       | Dataout2 | Dataout3 | Dataout4 | -     |  |  |  |

|                  | 1    | 2    | 3    | 4             | 1  | 2  | 3  | r4 |                |          |          |          |       |  |  |  |

|                  | 1000 | 1000 | 1001 | 1010          | 1  | 1  | 1  | 1  |                |          |          | 10000111 |       |  |  |  |

| <u>Output</u>    | 0111 | 1011 | 0011 | 0011          |    |    |    |    |                |          |          |          |       |  |  |  |

| buffer4          |      |      |      |               |    |    |    |    |                |          |          | 10001011 | 40 ns |  |  |  |

| <u>(Testcase</u> |      |      |      |               |    |    |    |    |                |          |          | 10010011 |       |  |  |  |

| <u>1)</u>        |      |      |      |               |    |    |    |    |                |          |          | 10100011 |       |  |  |  |

| <u>Output</u>    | 1000 | 1000 | 1000 | 1000          | 1  | 1  | 1  | 1  |                |          | 10000110 |          |       |  |  |  |

| <u>buffer3</u>   | 0110 | 0110 | 0110 | 0110          |    |    |    |    |                |          |          |          |       |  |  |  |

| (Testcase        |      |      |      |               |    |    |    |    |                |          | 10000110 |          | 40 ns |  |  |  |

| <u>1)</u>        |      |      |      |               |    |    |    |    |                |          | 10000110 |          |       |  |  |  |

|                  |      |      |      |               |    |    |    |    |                |          | 10000110 |          |       |  |  |  |

| <u>Output</u>    | 1000 | 1000 | 1000 | 1000          | 1  | 1  | 1  | 1  |                | 10000101 |          |          |       |  |  |  |

| buffer2          | 0101 | 0101 | 0101 | 0101          |    |    |    |    |                |          |          |          |       |  |  |  |

| <u>(Testcase</u> |      |      |      |               |    |    |    |    |                | 10000101 |          |          | 40 ns |  |  |  |

| <u>3)</u>        |      |      |      |               |    |    |    |    |                | 10000101 |          |          |       |  |  |  |

|                  |      |      |      |               |    |    |    |    |                | 10000101 |          |          |       |  |  |  |

| <u>Output</u>    | 1000 | 1000 | 1000 | 1000          | 1  | 1  | 1  | 1  | 10000100       |          |          |          |       |  |  |  |

| <u>buffer1</u>   | 0100 | 0100 | 0100 | 0100          |    |    |    |    |                |          |          |          |       |  |  |  |

| <u>(Testcase</u> |      |      |      |               |    |    |    |    | 10000100       |          |          |          | 40 ns |  |  |  |

| <u>4)</u>        |      |      |      |               |    |    |    |    | 10000100       |          |          |          |       |  |  |  |

|                  |      |      |      |               |    |    |    |    | 10000100       |          |          |          |       |  |  |  |

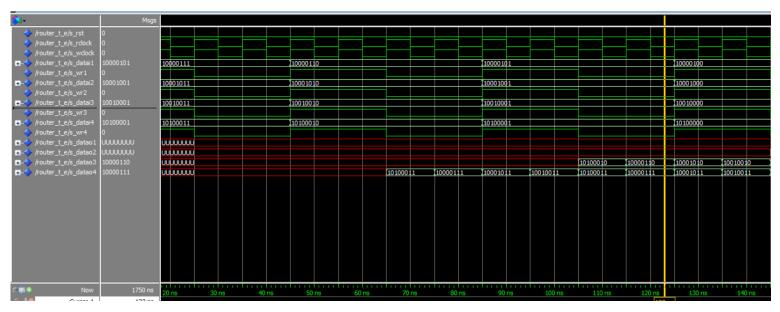

#### **<u>6.0 Test and Simulation results:</u>**

Fig#6.1: Test Plan

We used the exhaustive testing strategy. May be the exhaustive is not the best answer at all time, but in our case, we used it because by the 16 case we tested we have tested every input and output, so it is a not a waste of time, and 16 case is not that large number

of test cases relatively. At the end we have only increased the test case code by 3 lines for each case. so overall, we increased it by 12 lines of codes only.

#### 7.0 Conclusion:

In conclusion, mapping the signals in router module was a challenge. The implementation was done by instancing of four register and demuxes and 16 FiFOs and 4 RR schedulers. The best implementation style for the FSM schedular is a two process Moore. Because the output doesn't depend on anything except on the current state. Also, two process because choosing 1 wouldn't offer as much organization as a one process style. Concerning the timing results: The time report: Minimum period: 2.190ns (Maximum Frequency: 456.663 MHz). For future work. We may consider working with other FSM styles. We may use mealy as its generally faster. (Although more is more stable and safer). An exhaustive test strategy was used.

#### **<u>8. Task Distribution List:</u>**

| # | Student ID | Tasks                         |

|---|------------|-------------------------------|

| 1 | 17P5026    |                               |

| 2 | 17P6069    | the project workload is       |

| 3 | 17P8182    | distributed equally among all |

| 4 | 17P3061    | team members                  |

| 5 | 17P8042    |                               |

# <u>Appendix A – <<VHDL Model Source Code>></u>

#### 8-bit register:

library IEEE; USE IEEE.STD\_Logic\_1164.all;

ENTITY IB\_E is Port ( Data\_in: in std\_logic\_vector( 7 downto 0); Clock\_En: in std\_logic; Clock: in std\_logic; Reset: in std\_logic; Data\_out: out std\_logic\_Vector ( 7 downto 0 ) ); END IB\_E;

Architecture IB\_A of IB\_E is begin PROCESS (Clock, Reset) begin

if Reset = '1' then Data\_out <= "00000000";

elsif rising\_edge(Clock) and Clock\_En = '1' then Data\_out <= Data\_in;

else null; end if; end PROCESS ; end IB\_A;

#### **Demux:**

library ieee; use ieee.std\_logic\_1164.all; use ieee.std\_logic\_arith.all; use ieee.std\_logic\_unsigned.all;

ENTITY demux\_e IS PORT(d\_in: IN std\_logic\_vector (7 downto 0); -- input data vector sel: IN std\_logic\_vector (1 downto 0); -- 2 selesction bits en: IN std\_logic; -- enable flag -- output data vectors d\_out1: OUT std\_logic\_vector (7 downto 0); d\_out2: OUT std\_logic\_vector (7 downto 0); d\_out3: OUT std\_logic\_vector (7 downto 0); d\_out4: OUT std\_logic\_vector (7 downto 0)); END ENTITY demux\_e;

ARCHITECTURE demux\_a of demux\_e is BEGIN P1:PROCESS(en,d\_in,sel) IS BEGIN -- sensitivity list contains all inputs if en = '1' THEN case sel is -- all cases of selection bits are dealt with when "00" => d\_out1 <= d\_in; when "01" => d\_out2 <= d\_in; when "10" => d\_out3 <= d\_in; when others => d\_out4 <= d\_in; end case; end if; END PROCESS P1; END ARCHITECTURE demux\_a;

#### **Block Ram:**

```

Library IEEE;

use IEEE.STD_LOGIC_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity BlockRam E is

Port (d_in: IN STD_LOGIC_VECTOR (7 downto 0);

ADDRA: IN STD_LOGIC_VECTOR (2 downto 0);

ADDRB: IN STD LOGIC VECTOR (2 downto 0);

WEA, REA, CLKA, CLKB: IN STD LOGIC;

d out: OUT STD LOGIC VECTOR (7 downto 0)

);

END entity BlockRam E;

Architecture block ram A of BlockRam E is

Signal Reg0: STD LOGIC VECTOR (7 downto 0);

Signal Reg1: STD_LOGIC_VECTOR (7 downto 0);

Signal Reg2: STD LOGIC VECTOR (7 downto 0);

Signal Reg3: STD LOGIC VECTOR (7 downto 0);

Signal Reg4: STD_LOGIC_VECTOR (7 downto 0);

Signal Reg5: STD_LOGIC_VECTOR (7 downto 0);

Signal Reg6: STD LOGIC VECTOR (7 downto 0);

Signal Reg7: STD LOGIC VECTOR (7 downto 0);

-- creating 8 registers

Begin

write: Process(CLKA) IS BEGIN -- responsible for write

IF rising_edge (CLKA) THEN -- check that clock A is rising

IF WEA = '1' THEN -- check that write is enabled

case ADDRA is

when "000" =>

Reg0 \le d in;

when "001" =>

Reg1 <= d in;

when "010" =>

```

```

Reg2 <= d_in;

when "011" =>

Reg3 <= d in;

when "100" =>

Reg4 <= d_in;

when "101" =>

Reg5 <= d_in;

when "110" =>

Reg6 <= d_in;

when others =>

Reg7 <= d in;

end case;

end if;

end if;

END Process write;

read: Process (CLKB) IS BEGIN -- responsible for read

IF rising_edge(CLKB) THEN -- check that clock A is rising

IF REA = '1' THEN -- check that read is enabled

case ADDRB is

when "000" =>

d_out <= Reg0;

when "001" =>

d_out <= Reg1;

when "010" =>

d_out <= Reg2;

when "011" =>

d_out <= Reg3;

when "100" =>

d out <= Reg4;

when "101" =>

d_out <= Reg5;

when "110" =>

d out <= Reg6;

when others =>

d_out <= Reg7;

end case;

end if;

end if;

END Process read;

END block_ram_A;

```

#### **Gray counter:**

LIBRARY ieee; USE ieee.std\_logic\_1164.ALL;

ENTITY gray\_counter IS PORT( En,clock,Reset : IN std\_logic; Count\_out: OUT std\_logic\_vector (2 downto 0)); END ENTITY gray\_counter;

```

ARCHITECTURE behav OF gray counter IS

signal s_out :std_logic_vector (2 downto 0):="000";

BEGIN

Count out <= s out;

cs: PROCESS (clock, Reset) is begin

IF Reset = '1' THEN

s out <= "000";

ELSIF (rising edge(clock)and En = '1') THEN

case s_out is

when "000" => s_out <= "001";

when "001" => s_out <= "011";

when "011" => s out <= "010";

when "010" => s_out <= "110";

when "110" => s_out <= "111";

when "111" => s out <= "101";

when "101" => s out <= "100";

when "100" => s out <= "000";

when others => s_out <= "000";

end case;

```

END IF;

END PROCESS cs; END ARCHITECTURE behav;

#### Gray to binary converter:

```

-- Code for Gray to binary converter

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity gray_to_binary is

Port (gray_in : in STD_LOGIC_VECTOR (2 downto 0); -- Gray code input

bin_out : out STD_LOGIC_VECTOR (2 downto 0)); -- Binary code output

end gray_to_binary;

architecture Behavioral of gray_to_binary is begin

bin out(2) \le gray in(2);

-- most significant bit remains the same

bin out(1) \le gray in(2) xor gray in(1);

-- b(i) = b(i+1) xor g(i)

bin_out(0)<= gray_in(2) xor gray_in(1) xor gray_in(0);</pre>

-- repeat until least significant bit

end Behavioral;

```

#### **Fifo controller:**

LIBRARY IEEE; USE IEEE.Std\_logic\_1164.ALL; USE ieee.numeric std.ALL; ENTITY FIFO C IS PORT ( reset : IN STD LOGIC; rdclk : IN STD\_LOGIC; wrclk : IN STD LOGIC; r req : IN STD LOGIC; w req : IN STD LOGIC; write\_valid : OUT STD\_LOGIC; read\_valid : OUT STD\_LOGIC; wr ptr: OUT STD LOGIC VECTOR (2 DOWNTO 0); rd ptr: OUT STD LOGIC VECTOR (2 DOWNTO 0); empty : OUT STD LOGIC; full : OUT STD\_LOGIC); END FIFO\_C; Architecture FIFO\_C\_ARC OF FIFO\_C IS COMPONENT gray to binary PORT (gray in : in STD LOGIC VECTOR (2 downto 0); -- Gray code input bin\_out : out STD\_LOGIC\_VECTOR (2 downto 0)); -- Binary code output END COMPONENT; COMPONENT gray counter PORT( En, clock, Reset : IN std logic; Count out: OUT std logic vector (2 downto 0)); END COMPONENT; signal R valid : STD LOGIC; signal W valid : STD LOGIC; signal R\_PTR: STD\_LOGIC\_VECTOR (2 DOWNTO 0); signal W\_PTR : STD\_LOGIC\_VECTOR (2 DOWNTO 0); signal gray in write : STD LOGIC VECTOR (2 DOWNTO 0); signal gray\_in\_read : STD\_LOGIC\_VECTOR (2 DOWNTO 0); BEGIN -- gray counter gc read : gray counter PORT MAP(R valid, rdclk, reset, gray in read); gc\_write : gray\_counter PORT MAP(W\_valid,wrclk,reset,gray\_in\_write); -- gray to binary convertor gtb\_read : gray\_to\_binary PORT MAP(gray\_in\_read,R\_PTR); gtb\_write : gray\_to\_binary PORT MAP(gray\_in\_write,W\_PTR); -- connections wr ptr <= W PTR ;</pre> rd ptr <= R PTR; write\_valid <= W\_valid;</pre>

```

read_valid <= R_valid;</pre>

main : process(r req,w req,reset) IS

begin

IF(reset = '1') THEN

full <= '0';

empty \leq '1';

ELSIF(w_req = '1') THEN

IF( (std logic vector( unsigned(W PTR) + 1) = R PTR) or (W PTR = "111" and R PTR="000")) THEN--

cheacking if the memory is full

full <= '1';

empty \le '0';

W valid <='0';

ELSE

full <= '0';

empty <= '0';

W valid <='1';

END IF;

ELSIF(r_req = '1')THEN

IF(R_PTR = W_PTR)THEN-- checking if the memory is empty

empty \leq 1';

full <= '0' ;

R_valid <='0';

Else

full <= '0';

empty \le '0';

R valid <='1';

END IF;

ELSE

W valid \leq 0';

R valid <='0';

END IF;

END PROCESS main;

END ARCHITECTURE FIFO C ARC;

```

#### FiFO:

```

LIBRARY IEEE;

USE IEEE.Std_logic_1164.ALL;

USE ieee.numeric_std.ALL;

ENTITY FIFO_E IS

PORT (

reset : IN STD_LOGIC;

rclk : IN STD_LOGIC;

wclk : IN STD_LOGIC;

wreq : IN STD_LOGIC;

datain : IN STD_LOGIC;

dataout : OUT STD_LOGIC_VECTOR (7 downto 0);

dataout : OUT STD_LOGIC_VECTOR (7 downto 0);

empty : OUT STD_LOGIC;

full : OUT STD_LOGIC;

END FIFO_E;

```

Architecture FIFO A OF FIFO E IS COMPONENT FIFO C IS PORT ( reset : IN STD LOGIC; rdclk : IN STD LOGIC; wrclk : IN STD LOGIC; r\_req : IN STD\_LOGIC; w reg : IN STD LOGIC; write\_valid : OUT STD\_LOGIC; read\_valid : OUT STD\_LOGIC; wr ptr: OUT STD LOGIC VECTOR (2 DOWNTO 0); rd ptr: OUT STD LOGIC VECTOR (2 DOWNTO 0); empty : OUT STD LOGIC; full : OUT STD\_LOGIC); END COMPONENT FIFO\_C; COMPONENT BlockRam E is Port (d in: IN STD LOGIC VECTOR (7 downto 0); ADDRA: IN STD\_LOGIC\_VECTOR (2 downto 0); ADDRB: IN STD LOGIC VECTOR (2 downto 0); WEA, REA, CLKA, CLKB: IN STD LOGIC; d\_out: OUT STD\_LOGIC\_VECTOR (7 downto 0) ); END COMPONENT BlockRam\_E; -- SIGNALS SIGNAL SIGNAL s\_reset : STD\_LOGIC; SIGNAL s rclk: STD LOGIC; SIGNAL s wclk: STD LOGIC; SIGNAL s\_rreq : STD\_LOGIC; SIGNAL s wreq: STD LOGIC; SIGNAL s datain : STD LOGIC VECTOR (7 downto 0); SIGNAL s\_dataout : STD\_LOGIC\_VECTOR (7 downto 0); SIGNAL s\_empty : STD\_LOGIC; SIGNAL s full : STD LOGIC; SIGNAL s write valid : STD LOGIC; SIGNAL s read valid: STD LOGIC; SIGNAL s\_wr\_ptr : STD\_LOGIC\_VECTOR (2 DOWNTO 0); SIGNAL s\_rd\_ptr: STD\_LOGIC\_VECTOR (2 DOWNTO 0); BEGIN -- connections --inputs s\_reset <= reset;</pre> s\_rclk <= rclk;</pre> s wclk <= wclk; s rreq <= rreq;</pre> s wreq <= wreq; s\_datain <= datain;</pre> --outputs dataout <= s dataout; empty <= s\_empty;</pre> full <= s\_full; -----

fifocont: FIFO\_C PORT MAP(s\_reset, s\_rclk, s\_wclk, s\_rreq, s\_wreq,s\_write\_valid, s\_read\_valid, s\_wr\_ptr, s\_rd\_ptr, s\_empty, s\_full);

memoryram: BlockRam\_E PORT MAP(s\_datain, s\_wr\_ptr, s\_rd\_ptr, s\_write\_valid, s\_read\_valid, s\_wclk, s\_rclk, s\_dataout); END ARCHITECTURE FIFO A;

#### **Round Robin:**

```

Library IEEE;

use IEEE.STD LOGIC 1164.all;

ENTITY RoundRobin E is

Port (clk: IN STD LOGIC;

din1: in STD_LOGIC_VECTOR (7 downto 0);

din2: in STD_LOGIC_VECTOR (7 downto 0);

din3: in STD LOGIC VECTOR (7 downto 0);

din4: in STD LOGIC VECTOR (7 downto 0);

dout: out STD_LOGIC_VECTOR (7 downto 0)

);

End entity RoundRobin_E;

Architecture RoundRobin A of RoundRobin E IS

TYPE state_type IS (state_1, state_2, state_3, state_4);

SIGNAL current_state: state_type;

SIGNAL next_state: state_type;

Begin

checkclock: Process(clk)

Begin

IF rising_edge(clk) THEN

current state <= next state;

END IF;

END Process checkclock;

updating_the_next_state: Process (current_state, din1, din2, din3, din4)

Begin

case current state is

when state 1 =>

next_state <= state_2;</pre>

dout \leq din1;

when state 2 =>

next state <= state 3;</pre>

dout \leq din2;

when state 3 =>

next_state <= state_4;</pre>

dout <= din3;

when others =>

next_state <= state_1;</pre>

dout <= din4;

END case;

END Process updating the next state;

END RoundRobin A;

```

#### **Router:**

```

LIBRARY IEEE;

USE IEEE.Std_logic_1164.ALL;

USE ieee.numeric std.ALL;

ENTITY Router E IS

PORT (

rst : IN STD LOGIC;

rclock : IN STD LOGIC;

wclock : IN STD LOGIC;

datai1 : IN STD LOGIC VECTOR (7 downto 0);

wr1: IN STD LOGIC;

datai2 : IN STD LOGIC VECTOR (7 downto 0);

wr2 : IN STD_LOGIC;

datai3 : IN STD_LOGIC_VECTOR (7 downto 0);

wr3: IN STD LOGIC;

datai4 : IN STD LOGIC VECTOR (7 downto 0);

wr4: IN STD LOGIC;

datao1 : OUT STD_LOGIC_VECTOR (7 downto 0);

datao2 : OUT STD_LOGIC_VECTOR (7 downto 0);

datao3 : OUT STD LOGIC VECTOR (7 downto 0);

datao4 : OUT STD_LOGIC_VECTOR (7 downto 0));

END Router E;

Architecture Router A OF Router E IS

COMPONENT FIFO E IS

PORT (

reset : IN STD LOGIC;

rclk : IN STD_LOGIC;

wclk: IN STD LOGIC;

rreg : IN STD LOGIC;

wreq: IN STD LOGIC;

datain : IN STD LOGIC VECTOR (7 downto 0);

dataout : OUT STD_LOGIC_VECTOR (7 downto 0);

empty : OUT STD LOGIC;

full : OUT STD LOGIC);

END COMPONENT FIFO E;

COMPONENT RoundRobin E is

Port (clk: IN STD LOGIC;

din1: in STD LOGIC VECTOR (7 downto 0);

din2: in STD_LOGIC_VECTOR (7 downto 0);

din3: in STD LOGIC VECTOR (7 downto 0);

din4: in STD LOGIC VECTOR (7 downto 0);

dout: out STD LOGIC VECTOR (7 downto 0)

);

End COMPONENT RoundRobin E;

COMPONENT demux e IS

PORT(d_in: IN std_logic_vector (7 downto 0); -- input data vector

sel: IN std logic vector (1 downto 0); -- 2 selesction bits

en: IN std logic; -- enable flag

-- output data vectors

d_out1: OUT std_logic_vector (7 downto 0);

```

d\_out2: OUT std\_logic\_vector (7 downto 0); d out3: OUT std logic vector (7 downto 0); d out4: OUT std logic vector (7 downto 0)); END COMPONENT demux e; COMPONENT IB E is Port (Data in: in std logic vector(7 downto 0); Clock\_En: in std\_logic; Clock: in std logic; Reset: in std logic; Data\_out: out std\_logic\_Vector (7 downto 0) ); END COMPONENT IB E; SIGNAL s rst: STD LOGIC; SIGNAL s\_rclock : STD\_LOGIC; SIGNAL s\_wclock : STD\_LOGIC; SIGNAL s datai1 : STD LOGIC VECTOR (7 downto 0); SIGNAL s wr1: STD LOGIC; SIGNAL s\_datai2 : STD\_LOGIC\_VECTOR (7 downto 0); SIGNAL s wr2 : STD LOGIC; SIGNAL s datai3 : STD LOGIC VECTOR (7 downto 0); SIGNAL s wr3: STD LOGIC; SIGNAL s\_datai4 : STD\_LOGIC\_VECTOR (7 downto 0); SIGNAL s\_wr4 : STD\_LOGIC; SIGNAL s\_datao1 : STD\_LOGIC\_VECTOR (7 downto 0); SIGNAL s datao2 : STD LOGIC VECTOR (7 downto 0); SIGNAL s datao3 : STD LOGIC VECTOR (7 downto 0); SIGNAL s datao4 : STD LOGIC VECTOR (7 downto 0); -----/FIFO EMPTY&FULL/------SIGNAL s FIFO11 empty : STD LOGIC; SIGNAL s FIFO11 full : STD LOGIC; SIGNAL s FIFO12 empty : STD LOGIC; SIGNAL s FIFO12 full : STD LOGIC; SIGNAL s FIFO13 empty : STD LOGIC; SIGNAL s FIFO13 full : STD LOGIC; SIGNAL s FIFO14 empty : STD LOGIC; SIGNAL s\_FIFO14\_full : STD\_LOGIC; \_\_\_\_\_ SIGNAL s FIFO21 empty : STD LOGIC; SIGNAL s\_FIFO21\_full : STD\_LOGIC; SIGNAL s FIFO22 empty : STD LOGIC; SIGNAL s\_FIFO22\_full : STD\_LOGIC; SIGNAL s\_FIFO23\_empty : STD\_LOGIC; SIGNAL s FIFO23 full : STD LOGIC; SIGNAL s FIFO24 empty : STD LOGIC; SIGNAL s FIFO24 full : STD LOGIC; SIGNAL s FIFO31 empty : STD LOGIC; SIGNAL s FIFO31 full : STD LOGIC; SIGNAL s\_FIFO32\_empty : STD\_LOGIC; SIGNAL s\_FIFO32\_full : STD\_LOGIC; SIGNAL s FIFO33 empty : STD LOGIC;

SIGNAL s FIFO33 full : STD LOGIC; SIGNAL s FIFO34 empty : STD LOGIC; SIGNAL s FIFO34 full : STD LOGIC; \_\_\_\_\_ SIGNAL s FIFO41 empty : STD LOGIC; SIGNAL s FIFO41 full : STD LOGIC; SIGNAL s\_FIFO42\_empty : STD\_LOGIC; SIGNAL s FIFO42 full : STD LOGIC; SIGNAL s FIFO43 empty : STD LOGIC; SIGNAL s\_FIFO43\_full : STD\_LOGIC; SIGNAL s FIFO44 empty : STD LOGIC; SIGNAL s FIFO44 full : STD LOGIC; -----/FIFO request signals/-----SIGNAL s\_FIFO11\_read\_request : STD\_LOGIC; SIGNAL s\_FIFO11\_write\_request : STD\_LOGIC; SIGNAL s FIFO12 read request : STD LOGIC; SIGNAL s FIFO12 write request : STD LOGIC; SIGNAL s\_FIFO13\_read\_request : STD\_LOGIC; SIGNAL s FIFO13 write request : STD LOGIC; SIGNAL s FIFO14 read request : STD LOGIC; SIGNAL s FIFO14 write request : STD LOGIC; SIGNAL s\_FIFO21\_read\_request : STD\_LOGIC; SIGNAL s FIFO21 write request : STD LOGIC; SIGNAL s FIFO22 read request : STD LOGIC; SIGNAL s FIFO22 write request : STD LOGIC; SIGNAL s FIFO23 read request : STD LOGIC; SIGNAL s\_FIFO23\_write\_request : STD\_LOGIC; SIGNAL s FIFO24 read request : STD LOGIC; SIGNAL s FIFO24 write request : STD LOGIC; \_\_\_\_\_ SIGNAL s\_FIFO31\_read\_request : STD\_LOGIC; SIGNAL s FIFO31 write request : STD LOGIC; SIGNAL s FIFO32 read request : STD LOGIC; SIGNAL s FIFO32 write request : STD LOGIC; SIGNAL s\_FIFO33\_read\_request : STD\_LOGIC; SIGNAL s FIFO33 write request : STD LOGIC; SIGNAL s FIFO34 read request : STD LOGIC; SIGNAL s\_FIFO34\_write\_request : STD\_LOGIC; -----SIGNAL s FIFO41 read request : STD LOGIC; SIGNAL s\_FIFO41\_write\_request : STD\_LOGIC; SIGNAL s FIFO42 read request : STD LOGIC; SIGNAL s FIFO42 write request : STD LOGIC; SIGNAL s FIFO43 read request : STD LOGIC; SIGNAL s\_FIFO43\_write\_request : STD\_LOGIC; SIGNAL s FIFO44 read request : STD LOGIC; SIGNAL s FIFO44 write request : STD LOGIC; -----/syncronize signals/-----TYPE state\_type IS (state\_1, state\_2, state\_3, state\_4); SIGNALs current state: state type;

SIGNAL s\_next\_state: state\_type; SIGNALs current read sync : STD LOGIC VECTOR (3 downto 0); -----/IB Outputs/------SIGNAL s reg1 datao : STD LOGIC VECTOR (7 downto 0); SIGNAL s\_reg2\_datao : STD\_LOGIC\_VECTOR (7 downto 0); SIGNAL s reg3 datao : STD LOGIC VECTOR (7 downto 0); SIGNAL s\_reg4\_datao : STD\_LOGIC\_VECTOR (7 downto 0); -----/DeMux ENABLE/------SIGNAL s demux1 en : STD LOGIC; SIGNAL s\_demux2\_en : STD\_LOGIC; SIGNAL s demux3 en : STD LOGIC; SIGNAL s demux4 en : STD LOGIC; -----/DeMux Inputs/------SIGNAL s\_demux1\_datai : STD\_LOGIC\_VECTOR (7 downto 0); SIGNAL s\_demux2\_datai : STD\_LOGIC\_VECTOR (7 downto 0); SIGNAL s demux3 datai : STD LOGIC VECTOR (7 downto 0); SIGNAL s\_demux4\_datai : STD\_LOGIC\_VECTOR (7 downto 0); -----/DeMux\_1 Outputs/------SIGNAL s demux1 datao1: STD LOGIC VECTOR (7 downto 0); SIGNAL s demux1 datao2 : STD LOGIC VECTOR (7 downto 0); SIGNAL s\_demux1\_datao3 : STD\_LOGIC\_VECTOR (7 downto 0); SIGNAL s\_demux1\_datao4 : STD\_LOGIC\_VECTOR (7 downto 0); -----/DeMux 2 Outputs/-----SIGNAL s\_demux2\_datao1 : STD\_LOGIC\_VECTOR (7 downto 0); SIGNAL s demux2 datao2 : STD LOGIC VECTOR (7 downto 0); SIGNAL s demux2 datao3 : STD LOGIC VECTOR (7 downto 0); SIGNAL s demux2 datao4 : STD LOGIC VECTOR (7 downto 0); -----/DeMux\_3 Outputs/------SIGNAL s demux3 datao1 : STD LOGIC VECTOR (7 downto 0); SIGNAL s demux3 datao2 : STD LOGIC VECTOR (7 downto 0); SIGNAL s\_demux3\_datao3 : STD\_LOGIC\_VECTOR (7 downto 0); SIGNAL s\_demux3\_datao4 : STD\_LOGIC\_VECTOR (7 downto 0); -----/DeMux 1 Outputs/-----SIGNAL s demux4 datao1 : STD LOGIC VECTOR (7 downto 0); SIGNAL s demux4 datao2 : STD LOGIC VECTOR (7 downto 0); SIGNAL s\_demux4\_datao3 : STD\_LOGIC\_VECTOR (7 downto 0); SIGNAL s\_demux4\_datao4 : STD\_LOGIC\_VECTOR (7 downto 0); -----/FIFO outputs/-----SIGNAL s\_FIFO11\_datao : STD\_LOGIC\_VECTOR (7 downto 0); SIGNAL s FIFO12 datao : STD LOGIC VECTOR (7 downto 0); SIGNAL s FIFO13 datao : STD LOGIC VECTOR (7 downto 0); SIGNAL s\_FIFO14\_datao : STD\_LOGIC\_VECTOR (7 downto 0); SIGNAL s FIFO21 datao : STD LOGIC VECTOR (7 downto 0); SIGNAL s FIFO22 datao : STD LOGIC VECTOR (7 downto 0); SIGNAL s\_FIFO23\_datao : STD\_LOGIC\_VECTOR (7 downto 0); SIGNAL s FIFO24 datao : STD LOGIC VECTOR (7 downto 0); SIGNAL s FIFO31 datao : STD LOGIC VECTOR (7 downto 0); SIGNAL s\_FIFO32\_datao : STD\_LOGIC\_VECTOR (7 downto 0); SIGNAL s FIFO33 datao : STD LOGIC VECTOR (7 downto 0);

SIGNAL s\_FIFO34\_datao : STD\_LOGIC\_VECTOR (7 downto 0);

\_\_\_\_\_

```

SIGNAL s FIFO41 datao : STD LOGIC VECTOR (7 downto 0);

SIGNAL s FIFO42 datao : STD LOGIC VECTOR (7 downto 0);

SIGNAL s_FIFO43_datao : STD_LOGIC_VECTOR (7 downto 0);

SIGNAL s FIFO44 datao : STD LOGIC VECTOR (7 downto 0);

-----/DeMux selection lines/-----

SIGNAL s_demux1_sel : STD_LOGIC_VECTOR (1 downto 0);

SIGNAL s_demux2_sel : STD_LOGIC_VECTOR (1 downto 0);

SIGNAL s_demux3_sel : STD_LOGIC_VECTOR (1 downto 0);

SIGNAL s demux4 sel : STD LOGIC VECTOR (1 downto 0);

-----/scheduler output signals/-----

SIGNAL s_scheduler1_datao : STD_LOGIC_VECTOR (7 downto 0);

SIGNAL s_scheduler2_datao : STD_LOGIC_VECTOR (7 downto 0);

SIGNAL s_scheduler3_datao : STD_LOGIC_VECTOR (7 downto 0);

SIGNAL s scheduler4 datao : STD LOGIC VECTOR (7 downto 0);

-----/FIFO write selctor/------

SIGNAL s_FIFO1_en : STD_LOGIC_VECTOR (3 downto 0);

SIGNAL s FIFO2 en : STD LOGIC VECTOR (3 downto 0);

SIGNAL s_FIFO3_en : STD_LOGIC_VECTOR (3 downto 0);

SIGNAL s_FIFO4_en : STD_LOGIC_VECTOR (3 downto 0);

```

#### BEGIN

-----/connections/----s rst <= rst; s rclock <= rclock;</pre> s wclock <= wclock;</pre> -----s datai1 <= datai1;</pre> s datai2 <= datai2; s\_datai3 <= datai3; s datai4 <= datai4; ----datao1 <= s datao1;</pre> datao2 <= s datao2; datao3 <= s\_datao3; datao4 <= s\_datao4;</pre> ----s\_wr1 <= wr1; s wr2 <= wr2; s wr3 <= wr3; s\_wr4 <= wr4; s demux1 datai <= s reg1 datao; s\_demux2\_datai <= s\_reg2\_datao;</pre> s\_demux3\_datai <= s\_reg3\_datao;</pre> s demux4 datai <= s reg4 datao; \_\_\_\_\_ s\_demux1\_en <= (s\_wr1 and s\_wclock);</pre> s\_demux2\_en <= (s\_wr2 and s\_wclock);</pre> s demux3 en <= (s wr3 and s wclock);

s\_demux4\_en <= (s\_wr4 and s\_wclock);</pre> ----s datao1 <= s scheduler1 datao;</pre> s datao2 <= s scheduler2 datao; s datao3 <= s scheduler3 datao; s datao4 <= s scheduler4 datao; \_\_\_\_\_ s FIFO11 read request <= (s current read sync(0) and (not s FIFO11 empty)); s\_FIFO21\_read\_request <= (s\_current\_read\_sync(0) and (not s\_FIFO21\_empty));</pre> s\_FIFO31\_read\_request <= (s\_current\_read\_sync(0) and (not s\_FIFO31\_empty));</pre> s FIFO41 read request <= (s current read sync(0) and (not s FIFO41 empty)); \_\_\_\_\_ s\_FIFO12\_read\_request <= (s\_current\_read\_sync(1) and (not s\_FIFO12\_empty));</pre> s\_FIFO22\_read\_request <= (s\_current\_read\_sync(1) and (not s\_FIFO22\_empty));</pre> s\_FIFO32\_read\_request <= (s\_current\_read\_sync(1) and (not s\_FIFO32\_empty));</pre> s FIFO42 read request <= (s current read sync(1) and (not s FIFO42 empty)); s\_FIFO13\_read\_request <= (s\_current\_read\_sync(2) and (not s\_FIFO13\_empty));</pre> s FIFO23 read request <= (s current read sync(2) and (not s FIFO23 empty)); s FIFO33 read request  $\leq$  (s current read sync(2) and (not s FIFO33 empty)); s\_FIFO43\_read\_request <= (s\_current\_read\_sync(2) and (not s\_FIFO43\_empty));</pre> s\_FIFO14\_read\_request <= (s\_current\_read\_sync(3) and (not s\_FIFO14\_empty)); s\_FIFO24\_read\_request <= (s\_current\_read\_sync(3) and (not s\_FIFO24\_empty));</pre> s\_FIFO34\_read\_request <= (s\_current\_read\_sync(3) and (not s\_FIFO34\_empty)); s\_FIFO44\_read\_request <= (s\_current\_read\_sync(3) and (not s\_FIFO44\_empty));</pre> \_\_\_\_\_ --/DeMux selection lines Connections/-s demux1 sel(0) <= s datai1(0);</pre> s demux1 sel(1) <= s datai1(1);</pre> ----s\_demux2\_sel(0) <= s\_datai2(0);</pre> s demux2 sel(1) <= s datai2(1);</pre> \_\_\_\_\_ s demux3 sel(0) <= s datai3(0);</pre> s\_demux3\_sel(1) <= s\_datai3(1);</pre> ----s demux4 sel(0) <= s datai4(0);</pre> s\_demux4\_sel(1) <= s\_datai4(1);</pre> -----/Input Buffers/-----IB\_1 : IB\_E PORT MAP(s\_datai1,s\_wr1,s\_wclock,s\_rst,s\_reg1\_datao); IB\_2 : IB\_E PORT MAP(s\_datai2,s\_wr2,s\_wclock,s\_rst,s\_reg2\_datao); IB 3 : IB E PORT MAP(s datai3, s wr3, s wclock, s rst, s reg3 datao); IB\_4 : IB\_E PORT MAP(s\_datai4,s\_wr4,s\_wclock,s\_rst,s\_reg4\_datao); -----/Demux/------DeMux\_1 : demux\_e PORT

MAP(s\_demux1\_datai,s\_demux1\_sel,s\_demux1\_en,s\_demux1\_datao1,s\_demux1\_datao2,s\_demux1\_datao3,s\_demux1\_datao4);

DeMux\_2 : demux\_e PORT

MAP(s\_demux2\_datai,s\_demux2\_sel,s\_demux2\_en,s\_demux2\_datao1,s\_demux2\_datao2,s\_demux2\_datao3,s\_demux2\_datao4);

DeMux 3: demux e PORT MAP(s demux3 datai,s demux3 sel,s demux3 en,s demux3 datao1,s demux3 datao2,s demux3 datao3,s de mux3 datao4); DeMux 4: demux e PORT MAP(s demux4 datai,s demux4 sel,s demux4 en,s demux4 datao1,s demux4 datao2,s demux4 datao3,s de mux4 datao4); FIFO 11: FIFO E PORT MAP(s rst,s rclock,s wclock,s FIFO11 read request,s FIFO11 write request,s demux1 datao1,s FIFO11 datao, s\_FIFO11\_empty,s\_FIFO11\_full); FIFO 12 : FIFO E PORT MAP(s rst,s rclock,s wclock,s FIFO12 read request,s FIFO12 write request,s demux2 datao1,s FIFO12 datao, s FIFO12 empty, s FIFO12 full); FIFO 13: FIFO E PORT MAP(s\_rst,s\_rclock,s\_wclock,s\_FIFO13\_read\_request,s\_FIFO13\_write\_request,s\_demux3\_datao1,s\_FIFO13\_datao, s FIFO13 empty, s FIFO13 full); FIFO 14: FIFO E PORT MAP(s\_rst,s\_rclock,s\_wclock,s\_FIFO14\_read\_request,s\_FIFO14\_write\_request,s\_demux4\_datao1,s\_FIFO14\_datao, s FIFO14 empty, s FIFO14 full); \_\_\_\_\_ \_\_\_\_\_ FIFO 21: FIFO E PORT MAP(s\_rst,s\_rclock,s\_wclock,s\_FIFO21\_read\_request,s\_FIFO21\_write\_request,s\_demux1\_datao2,s\_FIFO21\_datao, s FIFO21 empty,s FIFO21 full); FIFO 22: FIFO E PORT MAP(s rst,s rclock,s wclock,s FIFO22 read request,s FIFO22 write request,s demux2 datao2,s FIFO22 datao, s FIFO22 empty,s FIFO22 full); FIFO 23: FIFO E PORT MAP(s\_rst,s\_rclock,s\_wclock,s\_FIFO23\_read\_request,s\_FIFO23\_write\_request,s\_demux3\_datao2,s\_FIFO23\_datao, s FIFO23 empty, s FIFO23 full); FIFO 24 : FIFO E PORT MAP(s rst,s rclock,s wclock,s FIFO24 read request,s FIFO24 write request,s demux4 datao2,s FIFO24 datao, s FIFO24 empty, s FIFO24 full); \_\_\_\_\_ FIFO 31: FIFO E PORT MAP(s rst,s rclock,s wclock,s FIFO31 read request,s FIFO31 write request,s demux1 datao3,s FIFO31 datao, s\_FIFO31\_empty,s\_FIFO31\_full); FIFO 32 : FIFO E PORT MAP(s\_rst,s\_rclock,s\_wclock,s\_FIFO32\_read\_request,s\_FIFO32\_write\_request,s\_demux2\_datao3,s\_FIFO32\_datao, s FIFO32 empty, s FIFO32 full); FIFO 33: FIFO E PORT MAP(s rst,s rclock,s wclock,s FIFO33 read request,s FIFO33 write request,s demux3 datao3,s FIFO33 datao, s FIFO33\_empty,s\_FIFO33\_full); FIFO 34 : FIFO E PORT MAP(s rst,s rclock,s wclock,s FIFO34 read request,s FIFO34 write request,s demux4 datao3,s FIFO34 datao, s FIFO34 empty, s FIFO34 full); FIFO 41: FIFO E PORT

MAP(s\_rst,s\_rclock,s\_wclock,s\_FIFO41\_read\_request,s\_FIFO41\_write\_request,s\_demux1\_datao4,s\_FIFO41\_datao, s\_FIFO41\_empty,s\_FIFO41\_full);

```

FIFO 42 : FIFO E PORT

MAP(s_rst,s_rclock,s_wclock,s_FIFO42_read_request,s_FIFO42_write_request,s_demux2_datao4,s_FIFO42_datao,

s FIFO42 empty, s FIFO42 full);

FIFO 43: FIFO E PORT

MAP(s rst,s rclock,s wclock,s FIFO43 read request,s FIFO43 write request,s demux3 datao4,s FIFO43 datao,

s FIFO43_empty,s_FIFO43_full);

FIFO 44 : FIFO E PORT

MAP(s rst,s rclock,s wclock,s FIFO44 read request,s FIFO44 write request,s demux4 datao4,s FIFO44 datao,

s FIFO44 empty, s FIFO44 full);

-----/scheduler/------

scheduler 1: RoundRobin E PORT

MAP(s rclock, s FIFO11 datao, s FIFO12 datao, s FIFO13 datao, s FIFO14 datao, s scheduler1 datao);

scheduler 2: RoundRobin E PORT

MAP(s_rclock,s_FIFO21_datao,s_FIFO22_datao,s_FIFO23_datao,s_FIFO24_datao,s_scheduler2_datao);

scheduler_3 : RoundRobin_E PORT

MAP(s rclock, s FIFO31 datao, s FIFO32 datao, s FIFO33 datao, s FIFO34 datao, s scheduler3 datao);

scheduler 4: RoundRobin E PORT

MAP(s_rclock,s_FIFO41_datao,s_FIFO42_datao,s_FIFO43_datao,s_FIFO44_datao,s_scheduler4_datao);

-----/sync read request/-----

FIFO_SEL : PROCESS(s_demux1_sel,s_demux2_sel,s_demux3_sel,s_demux4_sel)

BEGIN

case s demux1 sel is

when "00" => s_FIFO1_en <= "0001";

when "01" => s_FIFO1_en <= "0010";

when "10" => s FIFO1 en <= "0100";

when "11" => s FIFO1 en <= "1000";

when others => s FIFO1 en <= "0000";

end case;

case s demux2 sel is

when "00" => s FIFO2 en <= "0001";

when "01" => s FIFO2 en <= "0010";

when "10" => s FIFO2 en <= "0100";

when "11" => s FIFO2 en <= "1000";

when others => s FIFO2 en <= "0000";

end case;

case s_demux3_sel is

when "00" => s FIFO3 en <= "0001";

when "01" => s FIFO3 en <= "0010";

when "10" => s_FIFO3_en <= "0100";

when "11" => s FIFO3 en <= "1000";

when others => s FIFO3 en <= "0000";

end case;

case s demux4 sel is

when "00" => s_FIFO4_en <= "0001";

when "01" => s FIFO4 en <= "0010";

when "10" => s_FIFO4_en <= "0100";

when "11" => s FIFO4 en <= "1000";

when others => s FIFO4 en <= "0000";

end case;

END PROCESS FIFO SEL;

write sync demux1: PROCESS(s wclock)

```

#### Begin

if rising edge(s wclock) THEN

```

s FIFO11 write request <= (s wr1 and (not s FIFO11 full) and (not s rst) and s FIFO1 en(0));

s FIFO21 write request <= (s wr1 and (not s FIFO21 full) and (not s rst) and s FIFO1 en(1));

s FIFO31 write request <= (s wr1 and (not s FIFO31 full) and (not s rst) and s FIFO1 en(2));

s FIFO41 write request <= (s wr1 and (not s FIFO41 full) and (not s rst) and s FIFO1 en(3));

s FIFO12 write request <= (s wr2 and (not s FIFO12 full) and (not s rst) and s FIFO2 en(0));

s FIFO22 write request <= (s wr2 and (not s FIFO22 full) and (not s rst) and s FIFO2 en(1));

s_FIFO32_write_request <= (s_wr2 and (not s_FIFO32_full) and (not s_rst) and s_FIFO2_en(2));

s FIFO42 write request <= (s wr2 and (not s FIFO42 full) and (not s rst) and s FIFO2 en(3));

_____

s_FIFO13_write_request <= (s_wr3 and (not s_FIFO13_full) and (not s_rst) and s FIFO3 en(0));

s_FIFO23_write_request <= (s_wr3 and (not s_FIFO23_full) and (not s_rst) and s_FIFO3_en(1));

s_FIFO33_write_request <= (s_wr3 and (not s_FIFO33_full) and (not s_rst) and s_FIFO3_en(2));

s FIFO43 write request <= (s wr3 and (not s FIFO43 full) and (not s rst) and s FIFO3 en(3));

s_FIFO14_write_request <= (s_wr4 and (not s_FIFO14_full) and (not s_rst) and s_FIFO4_en(0));

s FIFO24 write request <= (s wr4 and (not s FIFO24 full) and (not s rst) and s FIFO4 en(1));

s FIFO34 write request <= (s wr4 and (not s FIFO34 full) and (not s rst) and s FIFO4 en(2));

s_FIFO44_write_request <= (s_wr4 and (not s_FIFO44_full) and (not s_rst) and s_FIFO4_en(3));

END if;

END PROCESS write_sync_demux1;

checkclock: Process(s rclock, s rst)

Begin

IF s rst = '1' THEN

s_current_state <= state_1;</pre>

ELSIF rising edge(s rclock) THEN

s current state <= s next state;

END IF;

END Process checkclock;

read sync: Process (s current state, s current read sync)

Begin

case s current state is

when state_1 =>

s next state <= state 2;

s_current_read_sync <= "0001";</pre>

when state 2 =>

s next state <= state 3;

s current read sync <= "0010";

when state_3 =>

s next state <= state 4;

s current read sync <= "0100";

when others =>

s_next_state <= state_1;</pre>

s current read sync <= "1000";

END case;

```

END Process read sync;

END ARCHITECTURE Router A;

# <u>Appendix B – <<VHDL Test Bench Source Code>></u>

LIBRARY IEEE; USE IEEE.Std\_logic\_1164.ALL; USE ieee.numeric std.ALL; ENTITY Router\_T\_E IS END Router\_T\_E; Architecture Router\_T\_A OF Router\_T\_E IS COMPONENT Router\_E IS PORT ( rst : IN STD\_LOGIC; rclock : IN STD\_LOGIC; wclock : IN STD\_LOGIC; datai1 : IN STD\_LOGIC\_VECTOR (7 downto 0); wr1 : IN STD\_LOGIC; datai2 : IN STD\_LOGIC\_VECTOR (7 downto 0); wr2 : IN STD\_LOGIC; datai3 : IN STD\_LOGIC\_VECTOR (7 downto 0); wr3 : IN STD\_LOGIC; datai4 : IN STD\_LOGIC\_VECTOR (7 downto 0); wr4 : IN STD\_LOGIC; datao1 : OUT STD\_LOGIC\_VECTOR (7 downto 0); datao2 : OUT STD\_LOGIC\_VECTOR (7 downto 0); datao3 : OUT STD\_LOGIC\_VECTOR (7 downto 0); datao4 : OUT STD\_LOGIC\_VECTOR (7 downto 0)); END COMPONENT Router\_E; SIGNAL s\_rst : STD\_LOGIC; SIGNAL s\_rclock : STD\_LOGIC; SIGNAL s\_wclock : STD\_LOGIC; SIGNAL s\_datai1 : STD\_LOGIC\_VECTOR (7 downto 0); SIGNALs wr1: STD LOGIC; SIGNAL s\_datai2 : STD\_LOGIC\_VECTOR (7 downto 0); SIGNAL s\_wr2 : STD\_LOGIC;

```

SIGNAL s_datai3 : STD_LOGIC_VECTOR (7 downto 0);

SIGNAL s_wr3 : STD_LOGIC;

SIGNAL s_datai4 : STD_LOGIC_VECTOR (7 downto 0);

SIGNAL s_wr4 : STD_LOGIC;

SIGNAL s_datao1 : STD_LOGIC_VECTOR (7 downto 0);

SIGNAL s_datao2 : STD_LOGIC_VECTOR (7 downto 0);

SIGNAL s_datao3 : STD_LOGIC_VECTOR (7 downto 0);

SIGNAL s_datao4 : STD_LOGIC_VECTOR (7 downto 0);

BEGIN

ROUTER : Router_E PORT

MAP(s rst,s rclock,s wclock,s datai1,s wr1,s datai2,s wr2,s datai3,s wr3,s datai4,s wr4,s datao1,s datao2,s

datao3,s_datao4);

read_clock: PROCESS IS

BEGIN

s_rclock <= '0' , '1' AFTER 5 ns;

WAIT FOR 10 ns;

END PROCESS read_clock;

write_clock: PROCESS IS

BEGIN

s_wclock <= '0' , '1' AFTER 5 ns;

WAIT FOR 10 ns;

END PROCESS write_clock;

--test case 1 : reset && input data from all input buffers to output buffer 4

p1: process is begin

s_rst <= '1';

WAIT FOR 5 ns;

s_rst <= '0';

s_datai1 <= "10000111"; --FIFO41

s_datai2 <= "10001011"; --FIFO42

s_datai3 <= "10010011"; --FIFO43