<u>SCENARIO</u> – Two simulations involving AIB to AIB traffic. One simulation behaving correctly according to spec. One simulation broken due to half cycle data misalignment.

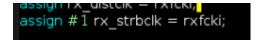

## <u>Code Block in Question</u> -- <u>aib\_ioring.sv</u>

## WORKING SIMULATION

- INCLK transitions to 0 (falling edge)

- IO\_PAD transitions to 0 on the falling edge

- As a result, iopad\_nreg transitions to 0

| D− inclk     |  |  |  |  |

|--------------|--|--|--|--|

| 👁 io_pad     |  |  |  |  |

| 🛛 iopad_nreg |  |  |  |  |

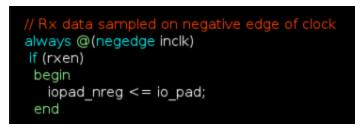

## **BROKEN SIMULATION**

- INCLK transitions to 0 (falling edge)

- IO\_PAD transitions to 0 on the falling edge

- iopad\_nreg transitions to 1 (race condition!)

| Name          | 4 1 1 1 1 1 1 1 1 1 | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 63774300p0 63773 |

|---------------|---------------------|---------------------------------------|------------------|

| aib_io_buffer |                     |                                       |                  |

| - D- inclk    |                     |                                       |                  |

| beq_oi ⊕ …    |                     |                                       |                  |

| 🛛 iopad_nreg  |                     |                                       |                  |

**SOLUTION** – Adding the following modification to aib\_io\_buffer.sv fixed the race condition presenting itself within iopad\_nreg on the receive clock. However, one of our architects noted that the receive-side DLL in the AIB block should delay fs\_fwd\_clk by 90 degrees before using it to sample io\_pad. Can you please investigate this and provide a more permanent solution?