## **DBI Background**

Spec update was done to fix the DBI location bits

|                 | - 3   | 20 | NOVELL XXXIII SPECIFICATION FOR FILE OFFI TO YOU Z            |

|-----------------|-------|----|---------------------------------------------------------------|

| 4/8/2021        | 2.0.1 | 26 | Updated CONF_DONE description                                 |

| ASAC ACTIVISION |       | 27 | Updated ns. mac_rdy description                               |

|                 |       | 28 | Clarified reset and standby conditions                        |

|                 |       | 29 | Updated dual, mode, select description                        |

|                 | _     | 31 | Corrected Word Mark bit recommended location                  |

|                 |       | 32 | Added detail about the DBI bit location in the full rate word |

According to this the location should be as shown below (half rate example):

|                              | 159 | 158 | 157    | 156  | 120    | 119 | 118 | 117   | 80    | 79      | 78   | 77     | 76    | 40    | 39  | 38  | 37    | 2      | 1      | 0      |

|------------------------------|-----|-----|--------|------|--------|-----|-----|-------|-------|---------|------|--------|-------|-------|-----|-----|-------|--------|--------|--------|

| Leader to Follower 297b with | DBI | DBI | Mark=1 | D[29 | 6:260] | DBI | DBI | D[259 | :122] | DBI     | DBI  | Mark=0 | D[221 | :185] | DBI | DBI | D[184 | 1:149] | Strobe | D[148] |

| TVALID on AIB2.0Gen2 Half    |     |     |        |      |        |     |     |       | AIB   | Channel | N+1  |        |       |       |     |     |       |        |        |        |

| Rate                         | 159 | 158 | 157    | 156  | 120    | 119 | 118 | 117   | 80    | 79      | 78   | 77     | 76    | 40    | 39  | 38  |       | 2      | 1      | 0      |

|                              | DBI | DBI | Mark=1 | D[14 | 7:111] | DBI | DBI | D[11  | 0:73] | DBI     | DBI  | Mark=0 | D[72  | :36]  | DBI | DBI | D[3   | 5:0]   | Strobe | Push   |

|                              |     |     |        |      |        |     |     |       | Ale   | Channe  | el N |        |       |       |     |     |       |        |        |        |

As described in spec the data comes on AIB/IO as even, odd, even, odd format.

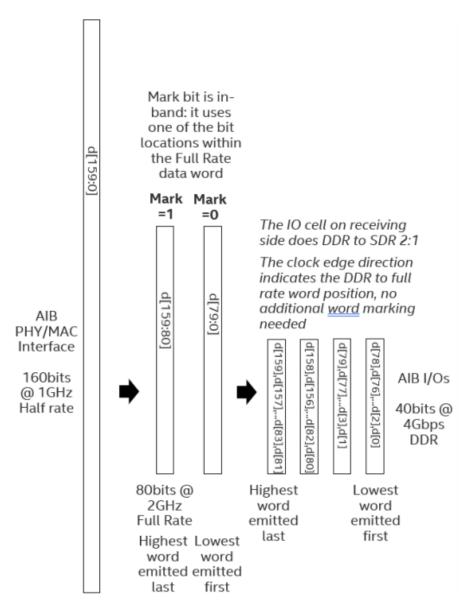

Figure 31. Word Marking Example, Half Rate PC Mode, 40 Tx Bits per Channel

DBI bits are present on the DDR'ed bits. AIB IO 19 and 39 are physical DBI IOs but the logical bit location corresponding to this D[38], D[39], D[78]. D[79], as shown below (**correct mapping**)

|     | AIB Chan | nel Data |    |                   | 10    |

|-----|----------|----------|----|-------------------|-------|

| 159 | 158      | 79       | 78 | $\leftrightarrow$ | 10 39 |

| 157 | 156      | 77       | 76 | $\leftrightarrow$ | 10 38 |

| 155 | 154      | 75       | 74 | $\leftrightarrow$ | 10 37 |

| 153 | 152      | 73       | 72 | $\leftrightarrow$ | 10 36 |

| 151 | 150      | 71       | 70 | $\leftrightarrow$ | 10 35 |

| 149 | 148      | 69       | 68 | $\leftrightarrow$ | 10 34 |

| 147 | 146      | 67       | 66 | $\leftrightarrow$ | 10 33 |

| 145 | 144      | 65       | 64 | $\leftrightarrow$ | 10 32 |

| 143 | 142      | 63       | 62 | $\leftrightarrow$ | IO 31 |

| 141 | 140      | 61       | 60 | $\leftrightarrow$ | 10 30 |

| 139 | 138      | 59       | 58 | $\leftrightarrow$ | 10 29 |

| 137 | 136      | 57       | 56 | $\leftrightarrow$ | 10 28 |

| 135 | 134      | 55       | 54 | $\leftrightarrow$ | 10 27 |

| 133 | 132      | 53       | 52 | $\leftrightarrow$ | 10 26 |

| 131 | 130      | 51       | 50 | $\leftrightarrow$ | 10 25 |

| 129 | 128      | 49       | 48 | $\leftrightarrow$ | 10 24 |

| 127 | 126      | 47       | 46 | $\leftrightarrow$ | 10 23 |

| 125 | 124      | 45       | 44 | $\leftrightarrow$ | 10 22 |

| 123 | 122      | 43       | 42 | $\leftrightarrow$ | IO 21 |

| 121 | 120      | 41       | 40 | $\leftrightarrow$ | 10 20 |

| 119 | 118      | 39       | 38 | $\leftrightarrow$ | 10 19 |

| 117 | 116      | 37       | 36 | $\leftrightarrow$ | IO 18 |

| 115 | 114      | 35       | 34 | $\leftrightarrow$ | 10 17 |

| 113 | 112      | 33       | 32 | $\leftrightarrow$ | 10 16 |

| 111 | 110      | 31       | 30 | $\leftrightarrow$ | 10 15 |

| 109 | 108      | 29       | 28 | $\leftrightarrow$ | IO 14 |

| 107 | 106      | 27       | 26 | $\leftrightarrow$ | IO 13 |

| 105 | 104      | 25       | 24 | $\leftrightarrow$ | IO 12 |

| 103 | 102      | 23       | 22 | $\leftrightarrow$ | IO 11 |

| 101 | 100      | 21       | 20 | $\leftrightarrow$ | IO 10 |

| 99  | 98       | 19       | 18 | $\leftrightarrow$ | 10 9  |

| 97  | 96       | 17       | 16 | $\leftrightarrow$ | 10 8  |

| 95  | 94       | 15       | 14 | $\leftrightarrow$ | 10 7  |

| 93  | 92       | 13       | 12 | $\leftrightarrow$ | 10 6  |

| 91  | 90       | 11       | 10 | $\leftrightarrow$ | 10 5  |

| 89  | 88       | 9        | 8  | $\leftrightarrow$ | 10 4  |

| 87  | 86       | 7        | 6  | $\leftrightarrow$ | 10 3  |

| 85  | 84       | 5        | 4  | $\leftrightarrow$ | 10 2  |

| 83  | 82       | 3        | 2  | $\leftrightarrow$ | IO 1  |

| 81  | 80       | 1        | 0  | $\leftrightarrow$ | 10 0  |

Section 2.2.4 in the spec is with respect to the IOs so it is consistent with the logical location shown above

## 2.2.4 Data Bus Inversion

Data Bus Inversion (DBI) is intended to reduce the power delivery network load of an AIB PHY by limiting the number of AIB data bits that can switch between immediate data transfer cycles. In Gen2 mode (DDR data transfers), AIB shall support DBI-AC in groups of 20 RX and 20 TX data wires. Channels may have multiple DBI data groups, for example a channel with 40 RX and 40 TX has a total of 4 DBI data groups. DBI shall be configurable on or off. When DBI is configured on, the AIB adapter shall process both RX and TX data for DBI. With DBI off, the data inside RX and TX are unaffected.

With DBI on, DBI bits replace certain data bits. The example below shows a 40 bit TX channel. RX wires have DBI at the same bit locations. Channels with more IOs continue with same 19 data bits + 1 DBI bit increment.

```

DBI Off: TX[39:0] = data[39:0]

DBI On: TX[39:0] = {DBI[1], data[38:20], DBI[0], data[18:0]}

```

The MAC data\_in and data\_out (section 1.3.5) contains even and odd bits that are multiplexed at the DDR transmitter and demultiplexed at DDR receiver (sections 2.1.1, 2.1.2 and 2.1.3). The "data" in the above example is selected from the MAC data\_in, anticipating DDR transmission. With DBI On, the data bits at the DBI locations are not used.

## 2.2.4.1 TX DBI with DBI Enabled

Within a group of 19 data signals, the TX DBI logic calculates the DBI bit based on the number of data signals changing from their previous state on the AIB data bus.

The DBI logic below uses "+" to indicate arithmetic addition, "^" to indicate exclusive OR, and "?" as a ternary IF. "Current" refers to the new data word being prepared for sending on TX. "Prev" refers to the data immediately preceding the current data, that is the data issued onto the AIB bus before the current data.

```

DBIcurrent = ((data[18]current ^ data[18]prev)

+ (data[17]current ^ data[17]prev)

...

+ (data[1]current ^ data[1]prev)

+ (data[0]current ^ data[0]prev)) > 9 ? 1 : 0);

```

Within a group of 19 data signals, if the DBI bit=1 then the TX DBI logic inverts the data signals. Each calculated DBI bit replaces one data bit in TX as described previously.

## <u>Issue</u>

aib-phy-hardware/v2.0/rev1/rtl/aib\_adapttxdbi\_txdp.v uses non-DDR version which should be fixed (incorrect mapping shown below)

|     | AIB Chan |    | 10 |                   |       |

|-----|----------|----|----|-------------------|-------|

| 159 | 139      | 79 | 59 | $\leftrightarrow$ | 10 39 |

| 158 | 138      | 78 | 58 | $\leftrightarrow$ | 10 38 |

| 157 | 137      | 77 | 57 | $\leftrightarrow$ | 10 37 |

| 156 | 136      | 76 | 56 | $\leftrightarrow$ | 10 36 |

| 155 | 135      | 75 | 55 | $\leftrightarrow$ | 10 35 |

| 154 | 134      | 74 | 54 | $\leftrightarrow$ | 10 34 |

| 153 | 133      | 73 | 53 | $\leftrightarrow$ | 10 33 |

| 152 | 132      | 72 | 52 | $\leftrightarrow$ | 10 32 |

| 151 | 131      | 71 | 51 | $\leftrightarrow$ | IO 31 |

| 150 | 130      | 70 | 50 | $\leftrightarrow$ | 10 30 |

| 149 | 129      | 69 | 49 | $\leftrightarrow$ | 10 29 |

| 148 | 128      | 68 | 48 | $\leftrightarrow$ | 10 28 |

| 147 | 127      | 67 | 47 | $\leftrightarrow$ | 10 27 |

| 146 | 126      | 66 | 46 | $\leftrightarrow$ | 10 26 |

| 145 | 125      | 65 | 45 | $\leftrightarrow$ | 10 25 |

| 144 | 124      | 64 | 44 | $\leftrightarrow$ | 10 24 |

| 143 | 123      | 63 | 43 | $\leftrightarrow$ | IO 23 |

| 142 | 122      | 62 | 42 | $\leftrightarrow$ | 10 22 |

| 141 | 121      | 61 | 41 | $\leftrightarrow$ | IO 21 |

| 140 | 120      | 60 | 40 | $\leftrightarrow$ | IO 20 |

| 119 | 99       | 39 | 19 | $\leftrightarrow$ | IO 19 |

| 118 | 98       | 38 | 18 | $\leftrightarrow$ | IO 18 |

| 117 | 97       | 37 | 17 | $\leftrightarrow$ | IO 17 |

| 116 | 96       | 36 | 16 | $\leftrightarrow$ | IO 16 |

| 115 | 95       | 35 | 15 | $\leftrightarrow$ | IO 15 |

| 114 | 94       | 34 | 14 | $\leftrightarrow$ | IO 14 |

| 113 | 93       | 33 | 13 | $\leftrightarrow$ | IO 13 |

| 112 | 92       | 32 | 12 | $\leftrightarrow$ | IO 12 |

| 111 | 91       | 31 | 11 | $\leftrightarrow$ | IO 11 |

| 110 | 90       | 30 | 10 | $\leftrightarrow$ | IO 10 |

| 109 | 89       | 29 | 9  | $\leftrightarrow$ | 10 9  |

| 108 | 88       | 28 | 8  | $\leftrightarrow$ | 10 8  |

| 107 | 87       | 27 | 7  | $\leftrightarrow$ | 10 7  |

| 106 | 86       | 26 | 6  | $\leftrightarrow$ | 10 6  |

| 105 | 85       | 25 | 5  | $\leftrightarrow$ | 10 5  |

| 104 | 84       | 24 | 4  | $\leftrightarrow$ | 10 4  |

| 103 | 83       | 23 | 3  | $\leftrightarrow$ | 10 3  |

| 102 | 82       | 22 | 2  | $\leftrightarrow$ | 10 2  |

| 101 | 81       | 21 | 1  | $\leftrightarrow$ | 101   |

| 100 | 80       | 20 | 0  | $\leftrightarrow$ | 10 0  |