# INTEL® SERIAL VOLTAGE IDENTIFICATION (SVID) PROTOCOL TRAINING-101

Intel Corporation Data Center Platform Application Engineering Apr 2020 Reference Number: 621792 Revision Number: 0.9 Intel Confidential

### Legal Disclaimer

Notice: This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at Intel.com, or from the OEM or retailer..

No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Tests document performance of components on a particular test, in specific systems. Differences in hardware, software, or configuration will affect actual performance. Consult other sources of information to evaluate performance as you consider your purchase. For more complete information about performance and benchmark results, visit <a href="http://www.intel.com/performance">http://www.intel.com/performance</a>.

Cost reduction scenarios described are intended as examples of how a given Intel- based product, in the specified circumstances and configurations, may affect future costs and provide cost savings. Circumstances will vary. Intel does not guarantee any costs or cost reduction.

Results have been estimated or simulated using internal Intel analysis or architecture simulation or modeling, and provided to you for informational purposes. Any differences in your system hardware, software or configuration may affect your actual performance.

Intel does not control or audit third-party benchmark data or the web sites referenced in this document. You should visit the referenced web site and confirm whether referenced data are accurate.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or by visiting www.intel.com/design/literature.htm.

Intel, the Intel logo and Xeon are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2020, Intel Corporation. All Rights Reserved.

Reference Number: 621792 Intel Confidential

A Real Case: System Hang with MSMI\_N(or CATERR#) triggered during enter/exit PkgC6

- Any error log?

- Power issue?

- SVID transaction error?

- SVID DC electrical parameter or AC timing violated ?

- VRTT test passed or failed?

- What kind of SVID decoder tool can use?

Note: SVID = Intel<sup>®</sup> Serial Voltage Identification

# Agenda

#### 1. Overview

#### 2. SVID specification

- Physical Layer

- Data Link Layer

- Function Layer

- 3. SVID issue debug tool and flow

### What SVID can be used to?

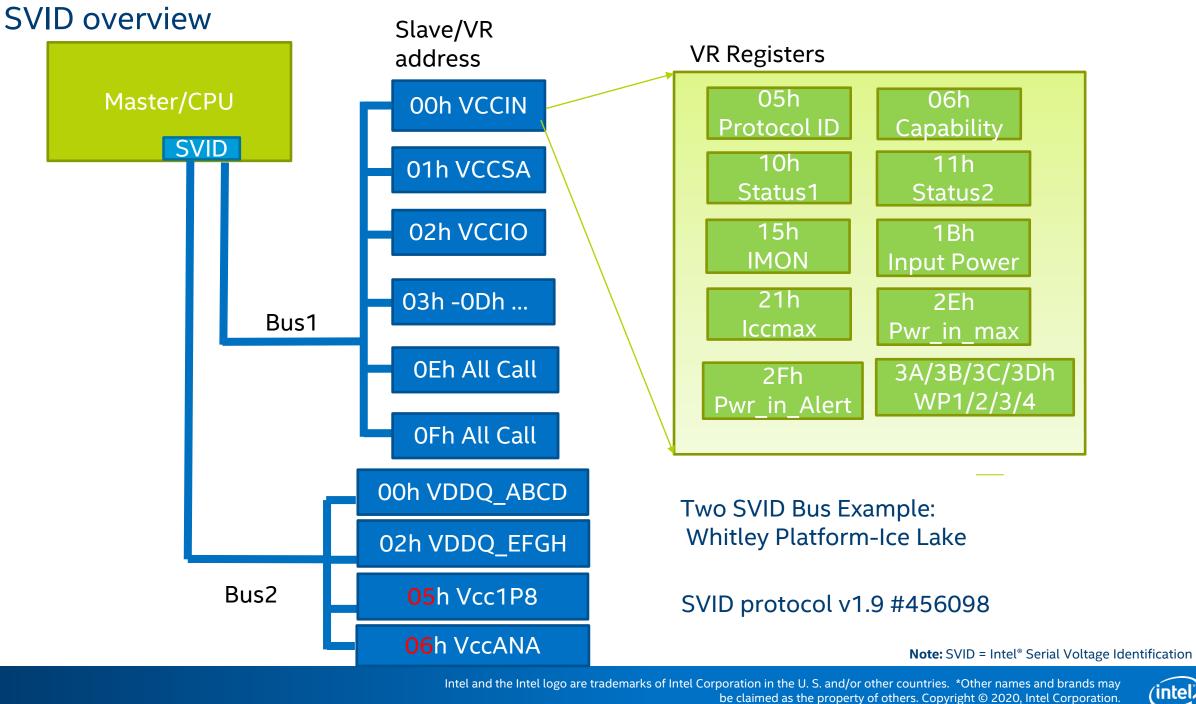

The SVID interface can be connected to multiple slaves. Slaves are identified by a unique address. The SVID master can address a command to either an individual slave or it can broadcast a command to multiple slaves.

The SVID interface is used primarily to

- Control dynamic voltage regulators (VRs)-DVID

- Read back telemetry information from VRs or dedicated power sensors-Monitor current/power

- Configure the VRs or dedicated power sensors-Configure VR

- Communicate alert-conditions interrupts the SoC-Alert response

Note: SVID = Intel<sup>®</sup> Serial Voltage Identification

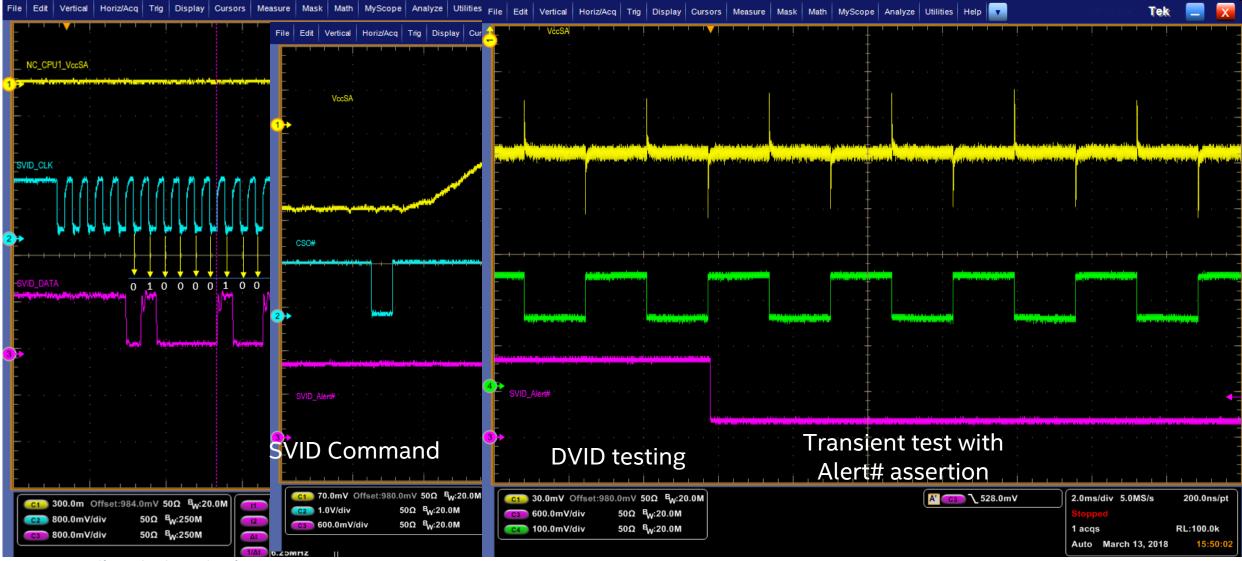

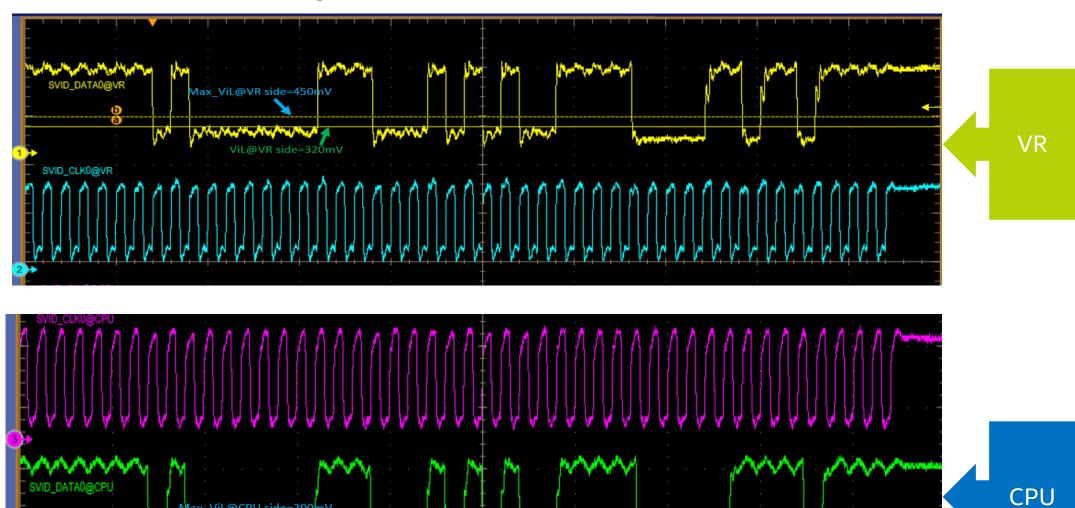

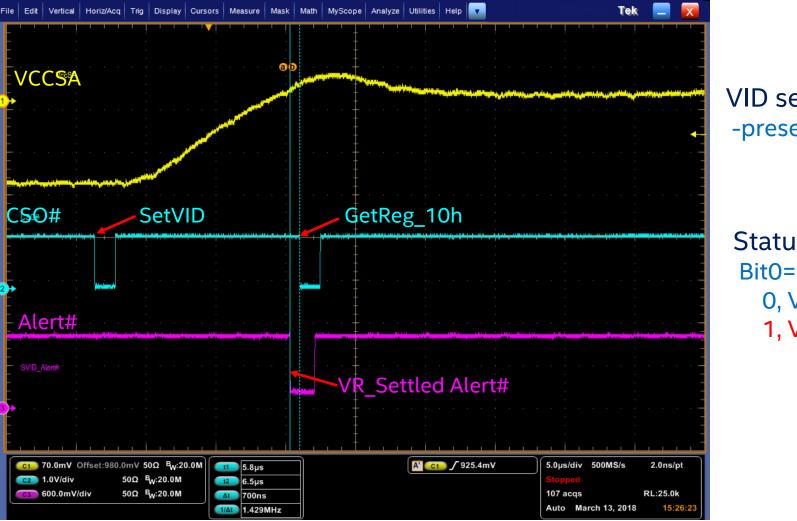

### Waveform during debug or VRTT test

Note: SVID = Intel<sup>®</sup> Serial Voltage Identification

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may

be claimed as the property of others. Copyright © 2020, Intel Corporation.

Reference Number: 621792 Intel Confidential

idential

Revision: 0.9

intel

Reference Number: 621792

Intel Confidential

**Revision: 0.9**

# **SVID SPECIFICATION**

**Note:** SVID = Intel<sup>®</sup> Serial Voltage Identification

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

## Physical/Data/Function Layer

The SerialVID specification is separated into layers, patterned after the Open Systems Interconnection (OSI) network model. The layers are:

- Physical Layer specifies how individual bits are communicated across the SerialVID link. The physical layer specifications are found in the PWM specifications.

- Data Link Layer specifies how bits are bound together into transactions that are used to send the command and response data between the SVID master and the SVID slaves.

- Functional Layer specifies how the commands are interpreted by the slave VRs and the responses are interpreted by the master. (Command Set)

# **PHYSICAL LAYER**

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Reference Number: 621792 Intel Confidential

Revision: 0.9

#### **Typical SVID Daisy Chain Topologies**

#### **Note:** SVID = Intel<sup>®</sup> Serial Voltage Identification

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation. Intel Confidential Revision: 0.9

(intel)

11

Reference Number: 621792

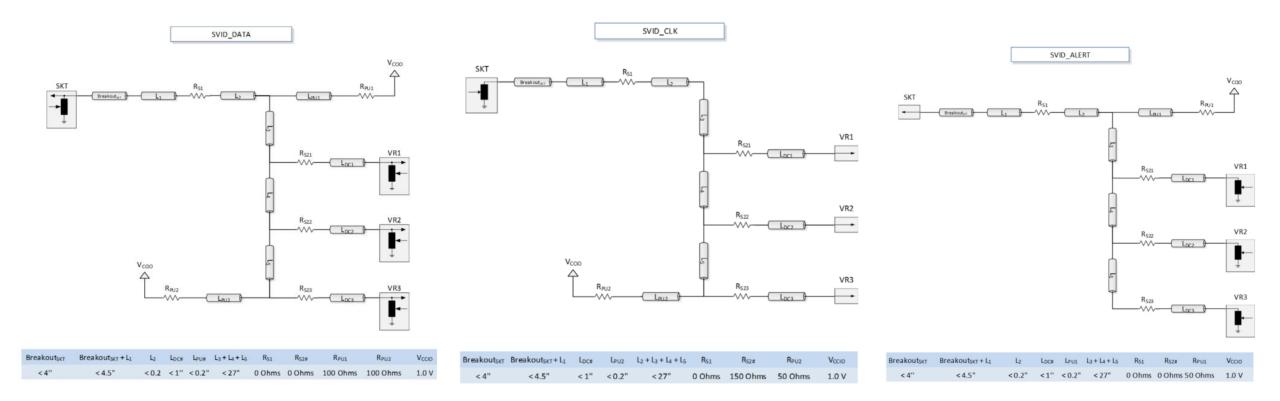

## **SVID** Routing Guide

- Refer to SVID routing guide in PDG (for Purley, Chapter 6.9 of PDG #546835)

- Highlight:

- ✓ SVID must be ground reference. Do not route SVID bus signals under phase nodes or high side MOSFET nodes that generate electrical noise.

- ✓ Low inductance path for VIO termination voltage to termination resistors (10 mils is the minimum trace width allowed). Bypass termination voltage as close as possible to termination resistor with 10 µF and 0.1 µF capacitors to ground (bypass is required unless supplied from a full plane).

- Trace length matching must be used between the Clock and Data lines to ensure a length difference of no more than 250 mils;

Microstrip (MS) and Stripline (SL) routing are allowed. Spacing of 13.5 mils on MS and 12 mils on SL within the Clock and Data signals, and 15 mils to all other non-static lines. For 10 mils of spacing on SL, do not exceed this spacing for more than 2.5 inches. An exception is for the breakout regions where spacing between lines can drop to 4 mils for coupling lengths less than 0.5 inches.

Note: SVID = Intel<sup>®</sup> Serial Voltage Identification

### Model and Collaterals

#### SKL MISC SI Models/Decks

- Document RDC#: 566889-skl-misc-si-model-566889-rev0-9  $\bigcirc$

- Folders : SVID\_Lowloss and SVID\_Midloss under "\miscio\_decks \miscio\_purley\" Ο

- Deck : Hspice format "purley svid daisy 3vr clk data r1p0a.sp" Ο

- Model User Guide (MUG) : SKL\_MISC\_IO\_556993\_Rev0.9.pdf Ο

- SVID Data Daisy Chain Topology

- Suggest to do SI post-layout simulation (Use third tool to extract PCB models) of VCLK, VDIO and VALT N nets).

### **SVID DC Electrical Parameters**

544905\_VR13\_and\_VR13HC\_rev\_1.3

546834-skx-eds-vol3

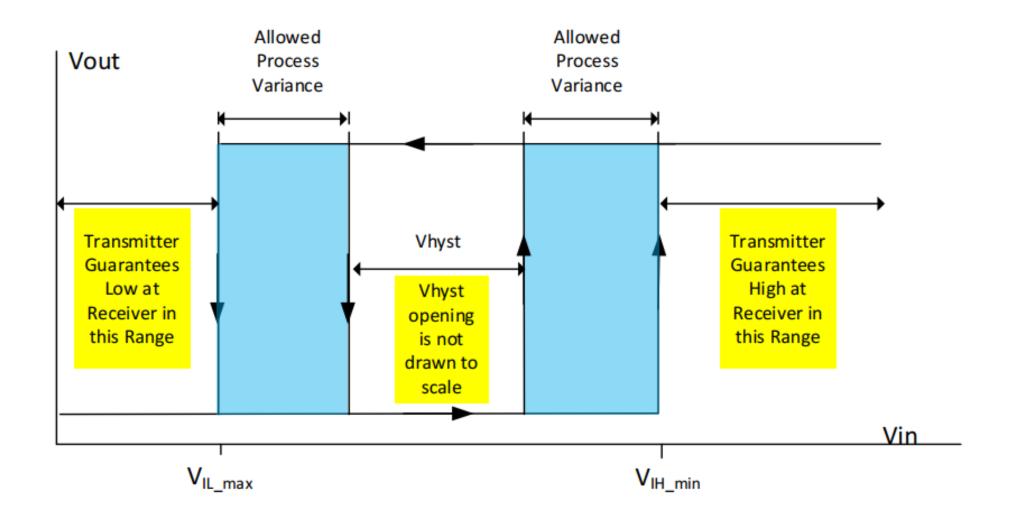

| Symbol          | Parameter                                          | Min             | Тур          | Max             | Units      |   |     |

|-----------------|----------------------------------------------------|-----------------|--------------|-----------------|------------|---|-----|

| VcclO           | CPU I/O voltage (also known as VccIO)              | 0.90            | 0.95 to 1.05 | 1.1             | V          |   |     |

| V <sub>IL</sub> | Input low voltage                                  | -               | -            | 0.45            | V          |   |     |

| V <sub>IH</sub> | Input high voltage                                 | 0.65            | -            | -               | V          |   | VR  |

| Vhyst           | Hysteresis voltage                                 | 0.05            | -            | -               | V          |   |     |

|                 |                                                    |                 |              |                 |            | - |     |

| Symbol          | Parameter                                          | Min             | Тур          | Max             | Units      |   |     |

| Symbol<br>VccIO | Parameter<br>CPU I/O voltage (also known as VccIO) | Min<br>VcclO-5% | Тур<br>1.0   | Max<br>VcclO+5% | Units<br>V |   |     |

|                 |                                                    |                 |              |                 |            |   |     |

| VcclO           | CPU I/O voltage (also known as VccIO)              |                 |              | VcclO+5%        | V          |   | CPU |

VIL, VIH are critical parameters that need to be measured and verified on the customer board. If there is a violation of VIL, tune the pullup and termination resistors.

#### Note: SVID = Intel<sup>®</sup> Serial Voltage Identification

### Waveform Example of VIL

Max\_ViL@CPU side=300mV

area and an article and and a second second

ViL@CPU side=270mV

A Converter

D

10 - 10 M

200

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation. Intel Confidential Reference Number: 621792 Revision: 0.9

for the start of the set of the set

#### Input Buffer Variance and Hysteresis

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Reference Number: 621792 Intel Confidential

Revision: 0.9

(intel)

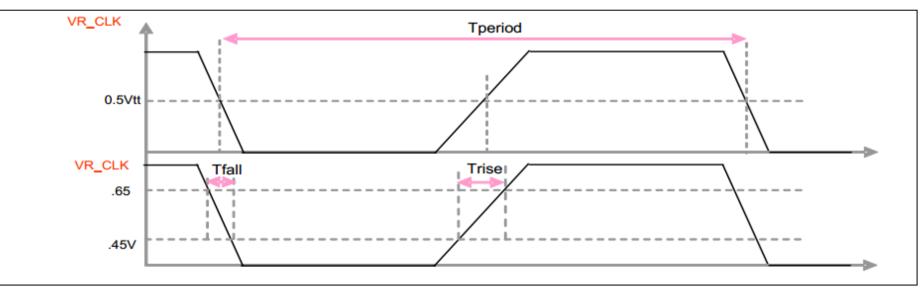

## SVID CLK AC timing

#### Table 3-3 **VCLK AC Timing Parameters**

40ns 38.1ns 100ns

| Symbol | Parameter                                             | Min  | Тур | Max    | Units | Notes     |

|--------|-------------------------------------------------------|------|-----|--------|-------|-----------|

|        | VCLK Frequency based on system BCLK/4, BCLK/6, BCLK/8 | 10   | 25  | 26. 25 | MHz   | 1, 4,5, 6 |

| Trise  | VCLK Rise Time (@VR Pad )                             | 0.25 |     | 5.5    | ns    | 2         |

| Tfall  | VCLK Fall Time (@VR Pad )                             | 0.25 |     | 5.5    | ns    | 2         |

|        | Duty Cycle                                            | 40   |     | 60     | %     | 1, 4      |

#### Figure 3-2 Measurement Points for VCLK high, low, rise, and fall time, Tperiod

**Note:** SVID = Intel<sup>®</sup> Serial Voltage Identification

Reference Number: 621792

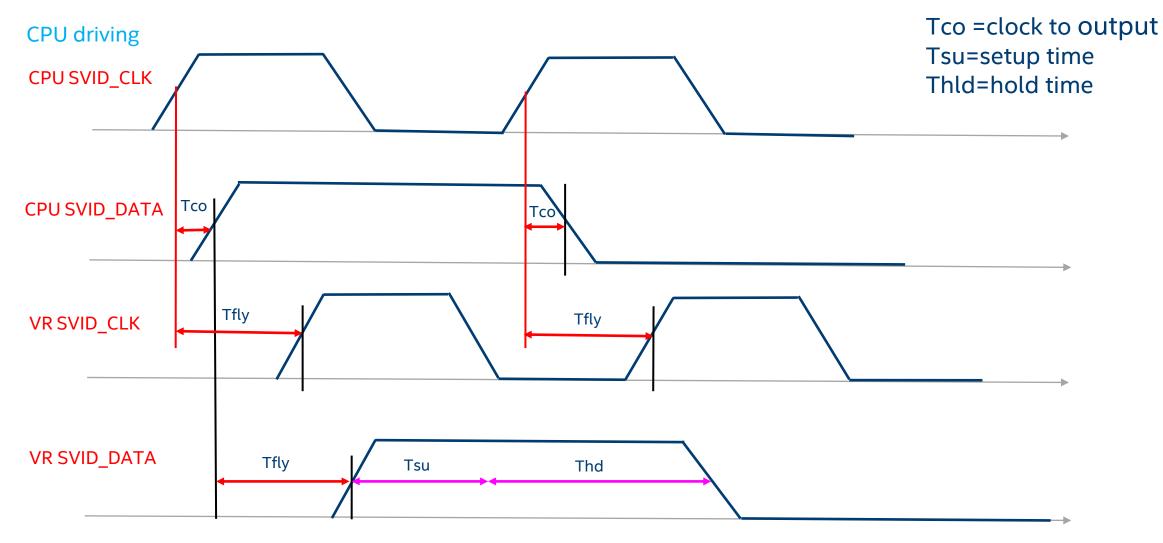

#### Platform Bus Timing-all market segments

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Reference Number: 621792 Intel Confidential

Revision: 0.9

(intel)

#### Platform Bus Timing-all market segments (Cont.)

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Reference Number: 621792 Intel Confidential

Revision: 0.9

bration.

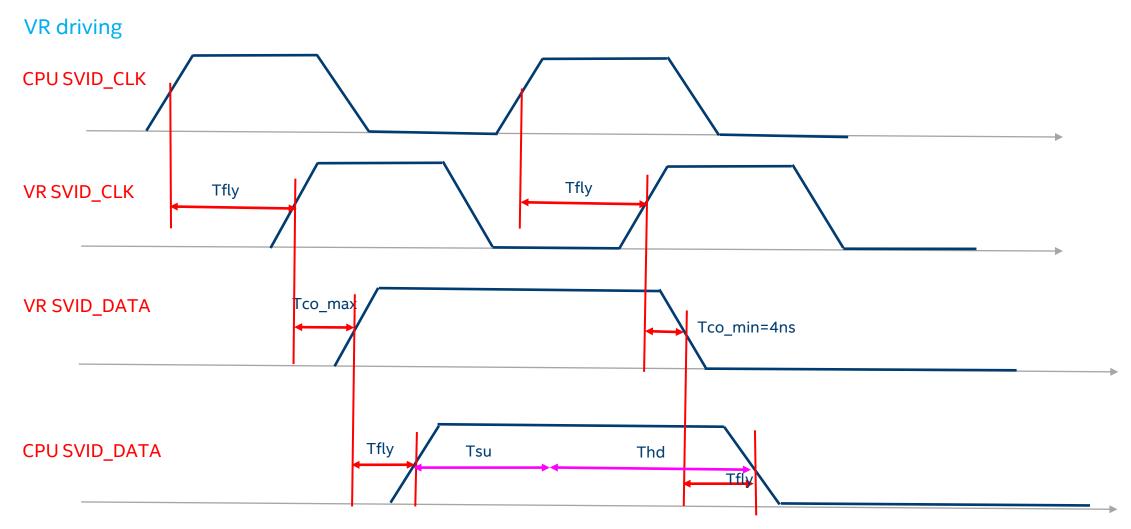

#### Platform Bus Timing-all market segments (Cont.)

- Tco\_max\_VR Clock to data delay = 12 ns

- Tco\_min VR clock to data delay = 4 ns

- Tsu\_VR Setup time of signal VDIO at VR side = 7 ns

- Thld\_VR Hold time of signal VDIO at VR side = 14 ns

- Tco\_max\_CPU Clock to data delay @bump = 0.65 ns

- Tco\_min\_CPU Clock to data delay @bump= -3.6 ns

- Tsu\_CPU Setup time of signal VDIO at CPU side = 1 ns

- Thld\_CPU Hold time of signal VDIO at CPU side = 3 ns

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Revision: 0.9

ifidential Rev

# DATA LINK LAYER

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

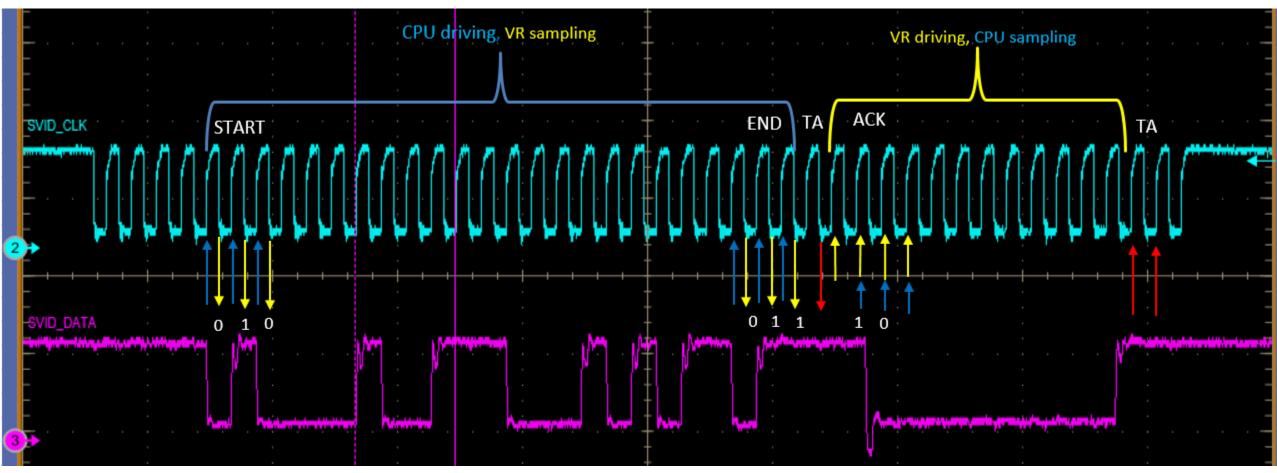

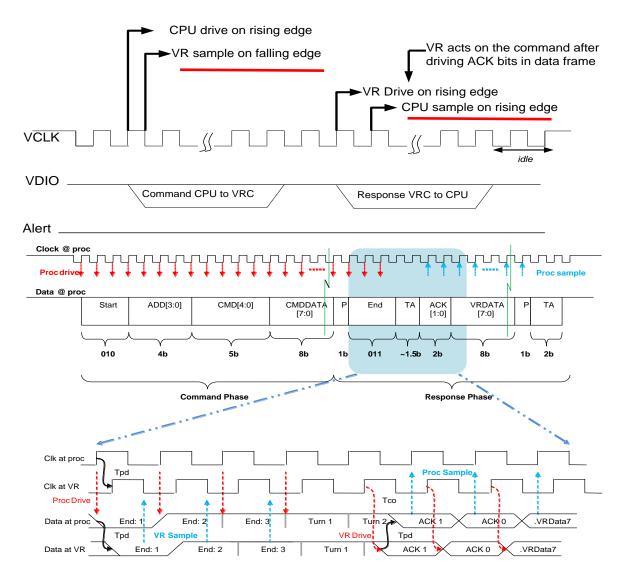

## SVID link Layer-Clock and Data Driving

**Command CPU to VRC, Response VRC to CPU**

- **Command**: CPU drive on **rising** edge, VR sample on **falling** edge

- Response: VR driving at rising edge, CPU sample on next rising edge

Note: SVID = Intel<sup>®</sup> Serial Voltage Identification

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may

Reference Number: 621792

Intel Confidential

Revision: 0.9

be claimed as the property of others. Copyright © 2020, Intel Corporation.

## SVID link Layer- Alert Line

#### • VR\_SETTLED Alert and VID setting commands

VID setting (31h) -present VID value(tracking)

Status1 Register (10h) Bit0=

0, VR is not at target voltage;1, VR is at target voltage

Note: SVID = Intel<sup>®</sup> Serial Voltage Identification

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Reference Number: 621792 Intel Confidential

Revision: 0.9

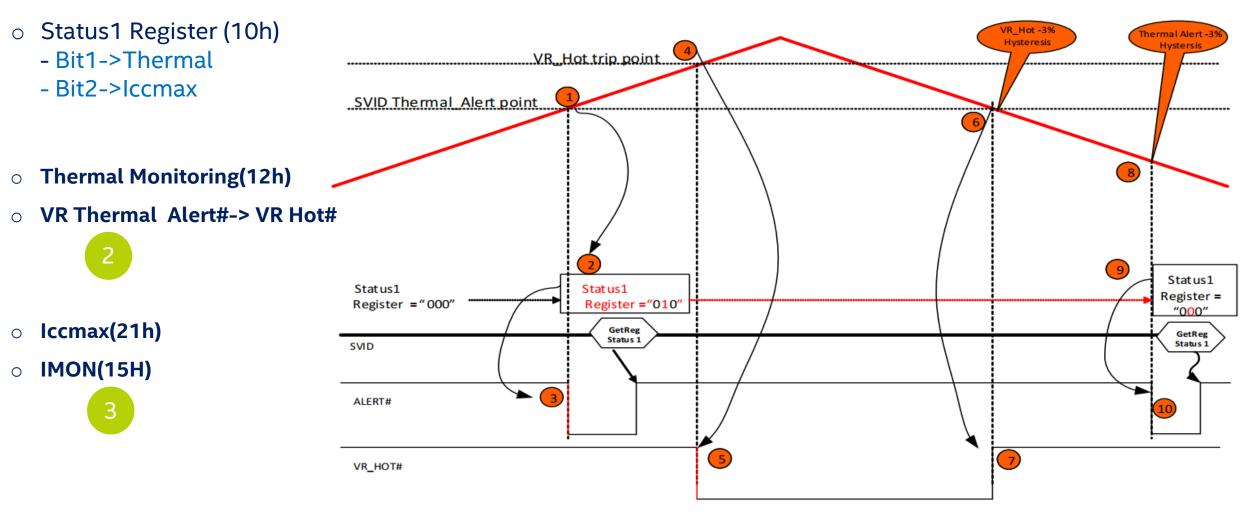

# SVID link Layer- Alert Line

#### Thermal Alert and IccMAX Alert

#### Note: SVID = Intel<sup>®</sup> Serial Voltage Identification

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Reference Number: 621792 Intel Confidential

Revision: 0.9

24

inte

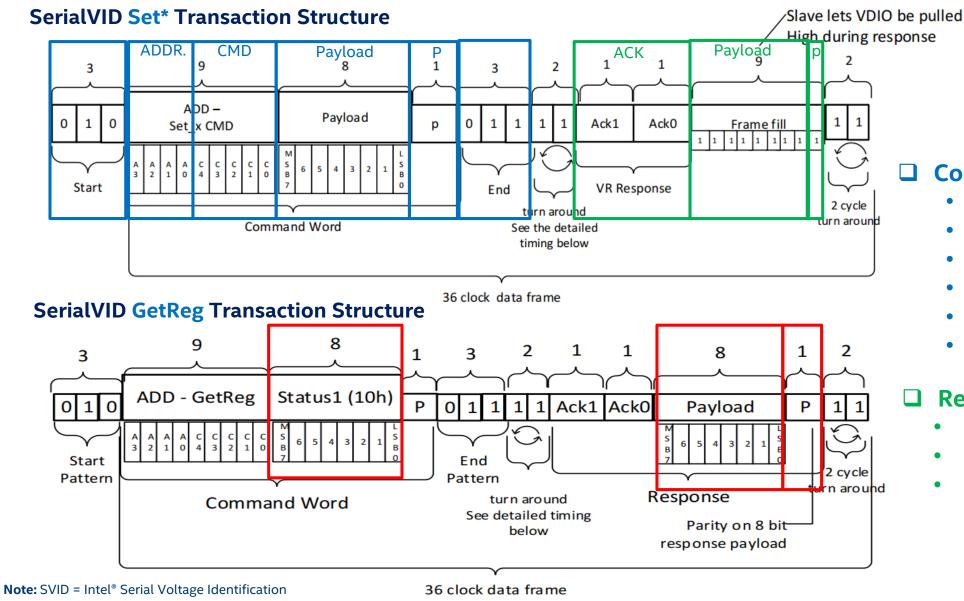

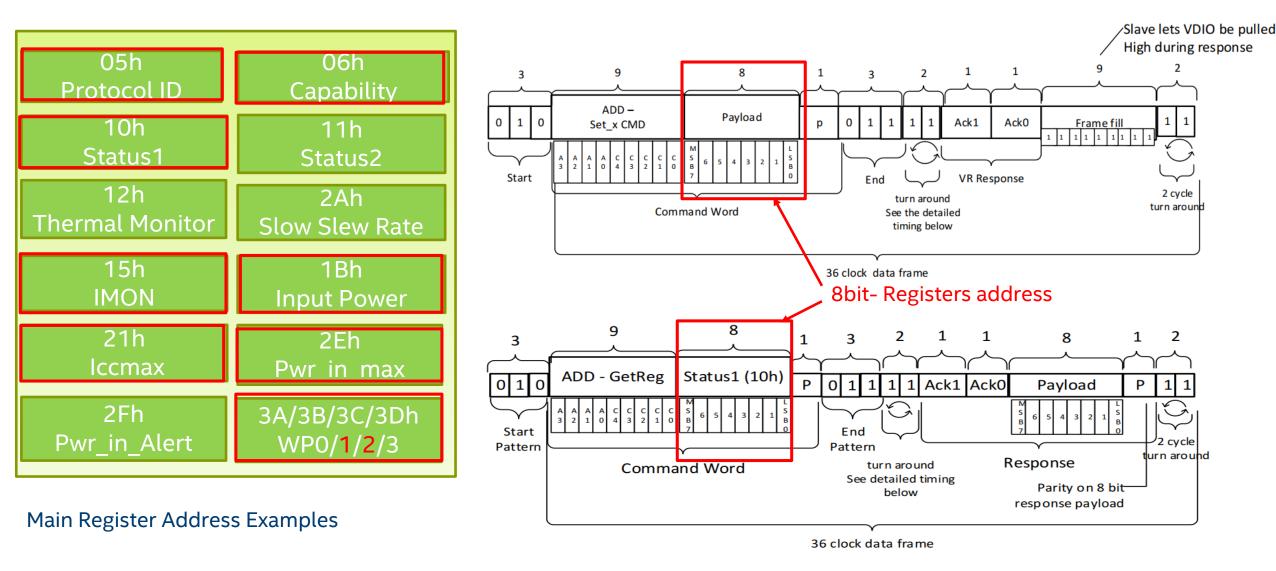

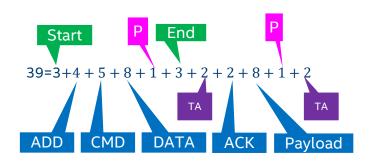

### Data Link Layer- Command Structure

#### **Command Word Encoding**

- 3-bit Start pattern(010)

- 4-bit Slave address ۲

- 5-bit command index ۲

- 8-bit command payload

- 1-bit of parity

- 3-bit End pattern(011)

#### **Response Encoding**

- 2-bit acknowledgement

- 8-bits response data

- 1-bit of parity

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

26

Reference Number: 621792 Intel Confidential

Revision: 0.9

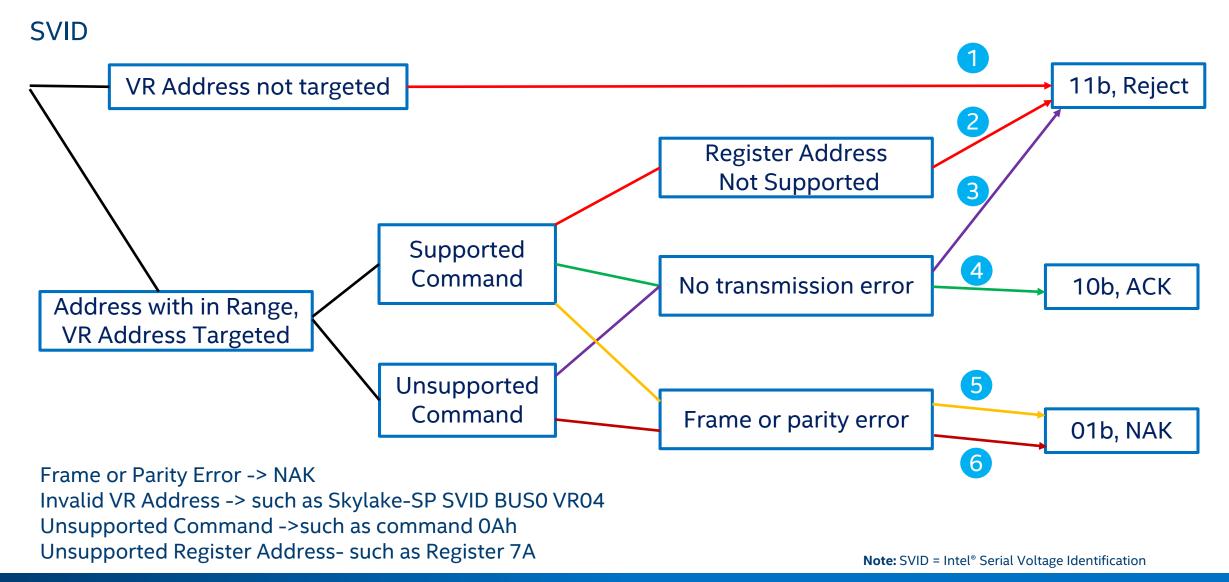

## Data Link Layer-Structure(cont.)-Acknowledge Type

| Acknowledge Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Ack1 | Ack0 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| MIXED Error on an All-Call rail access, such as SetWP<br>Results from wired-AND of simultaneous NAK and ACK responses being driven onto the open-drain<br>SVID bus by two or more SVID slaves.<br>ACK-ing slaves executes the command<br>NAK-ing slaves do not execute the command                                                                                                                                                                                                                                      | 0    | 0    |

| NAK (Not-Acknowledge)<br>Returned on transmission error, parity error, an unsupported command request to an All-Call address,<br>or a GetReg, SetRegAddr, or SetRegData command to an All-Call address Slave may log parity or frame<br>error if applicable, does not execute command.                                                                                                                                                                                                                                  | 0    | 1    |

| ACK (Acknowledge)<br>Transmission received correctly, Slave carries out command                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1    | 0    |

| <ul> <li>REJ (Reject)</li> <li>Returned for either Inactive SVID slave address or individually addressed SVID slave with command or register not supported.</li> <li>Cannot be used in most active All-Call address response since an ACK would hide any REJ after the wired-AND.</li> <li>Exceptions allow for an active All-Call command to REJ exist for (a) when LockVIDPS == 1, (b) for unset working point (WP), and (c) Unknown command number.</li> <li>Slave does nothing, does not execute command</li> </ul> | 1    | 1    |

**Note:** SVID = Intel<sup>®</sup> Serial Voltage Identification

#### Acknowledge Type(Cont.)

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may

Reference Number: 621792 Intel Confidential

Revision: 0.9

be claimed as the property of others. Copyright © 2020, Intel Corporation.

#### Exercise

| NC_CPU1_VccSA | an air an du thi da an air an an an air an |         |                 |                    |

|---------------|--------------------------------------------|---------|-----------------|--------------------|

|               |                                            |         |                 |                    |

|               | ллллллл                                    | <u></u> | ллаллаал        | ากกกกกกกกก         |

| 2             |                                            |         |                 |                    |

|               |                                            |         |                 |                    |

| 3             | art ADD[01] CMD<br>- VSA -Get              |         | rity END TA ACK | Data<br>-0A Parity |

|               |                                            |         |                 |                    |

#### Test point at VR side

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Reference Number: 621792 Intel Confidential

Revision: 0.9

# **FUNCTION LAYER**

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Reference Number: 621792 Intel Confidential Revision: 0.9

#### SVID function Layer-command set

Slave lets VDIO be pulled 1. SetVID\_Fast (01h) High during response 8 1 1 3 1 2 3 SetVID\_Slow (02h) 2. ADD -Pavload 0 1 0 0 1 Ack1 Ack0 Frame fill Set x CMD р 1 1 1 1 1 1 1 1 SetVID Decay (03h) 3. Start VR Response End 2 cycle turn around turn around Command Word 4. SetPS (04h) See the detailed timing below SetRegAddr variants (05h) 5. 36 clock data frame 5bit-Command index SetRegData variants (06h) 6. 8 9 2 1 1 2 8 3 1 ADD -GetReg Status1 (10h) GetReg variants (07h) 0 1 0 7. Ρ 0 1 Ack1 Ack0 Payload Ρ 1 1 1 Start End TestMode (08h) 8. 2 cvcle Pattern Pattern turn arouhd Response turn around Command Word See detailed timing Parity on 8 bit-SetWP (09h) 9. below response payload

36 clock data frame

#### Note: SVID = Intel<sup>®</sup> Serial Voltage Identification

Revision: 0.9

## Main Address Space Registers

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Reference Number: 621792 Intel Confidential

Revision: 0.9

intel

#### Protocol ID (05h)

This 8-bit read-only register identifies the protocol ID by which the slave address is communicating. It is possible that this may be reconfigurable via NVM or other means for a given product to make it applicable to a larger market segment.

| Protocol ID[7:0] | Definition               |

|------------------|--------------------------|

| 01h              | VR12.0, IMVP7            |

| 02h              | VR12.5                   |

| 03h              | VR12.6                   |

| 04h              | VR13, 10mV VID table     |

| 05h              | IMVP8                    |

| 06h              | VR12.1                   |

| <mark>07h</mark> | VR13, 5mV VID table      |

| 08h              | IMVP9                    |

| 09h              | VR14 VR 5mV VID table    |

| 0Ah              | VR14 VR 10mV VID table   |

| 0Bh              | VR14 VR custom VID table |

| 0Ch              | VR14 Psys device         |

| 0Dh              | IMVP9 Psys device        |

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Reference Number: 621792 Intel Confidential

Revision: 0.9

# Capability (06h)

| Capability Register, a 1b indicates digitize data is supported |                          |    |                  |    |    |               |               |

|----------------------------------------------------------------|--------------------------|----|------------------|----|----|---------------|---------------|

| b7                                                             | b6                       | b5 | b4               | b3 | b2 | b1            | b0            |

| lout/<br>Jout<br>format<br>(15h)                               | Tempe<br>rature<br>(17h) |    | input V<br>(1Ah) |    |    | Vout<br>(16h) | lout<br>(15h) |

| Description                     | Intel® Xeon® Se | rver CPU dom    | ains            | Memory                | Microserver<br>SOC 1  | Notes                                                                                                                         |

|---------------------------------|-----------------|-----------------|-----------------|-----------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------|

|                                 | 00h             | 01h             | 02h & 03h       | Multiple<br>addresses | Multiple<br>addresses |                                                                                                                               |

| Capability ( <mark>06h</mark> ) | X<br>1x1x xxx1b | X<br>1xxx xxx1b | X<br>1xxx xxx1b | X<br>1x1x xxx1b       | X<br>1x1x xxx1b       | Bit 5 = Pin supported<br>Bit 7 = IMON supported<br>Refer to the SVID protocol<br>specification for additional<br>information. |

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation. Reference Number: 621792 Intel Confidential Revision: 0.9

### Status1 Register (10h)

#### Table 7-13. SVID Status1 Register

| Bit | Name          | Description                                |

|-----|---------------|--------------------------------------------|

| 7   | ReadStatus2   | 0= No need to read Status2 register        |

|     |               | 1= Go read status2 register                |

| 6:5 | Reserved      | Return 0                                   |

| 4   | (VR14)        | (VR14)                                     |

|     | CalOpComplete | 0= No status update from IMON calibration  |

|     |               | 1= Check IMON calibration status registers |

|     | (Others)      | (Others)                                   |

|     | Reserved      | Return 0                                   |

| 3   | VID_DAC_high  | 0= VID DAC is not >30mV above VID target   |

|     |               | 1= VID DAC is >30mV above VID target       |

| 2   | IccMaxAlert   | 0= I_out in normal current range           |

|     |               | 1= I_out is over-current (latched value)   |

| 1   | ThermAlert    | 0= Not over-temperature                    |

|     |               | 1= Over-temperature                        |

| 0   | VR_Settled    | 0= VR is not at target voltage             |

|     |               | 1= VR is at target voltage                 |

**Note:** Default values for each bit are 0, indicating flag not set.

**Note:** SVID = Intel<sup>®</sup> Serial Voltage Identification

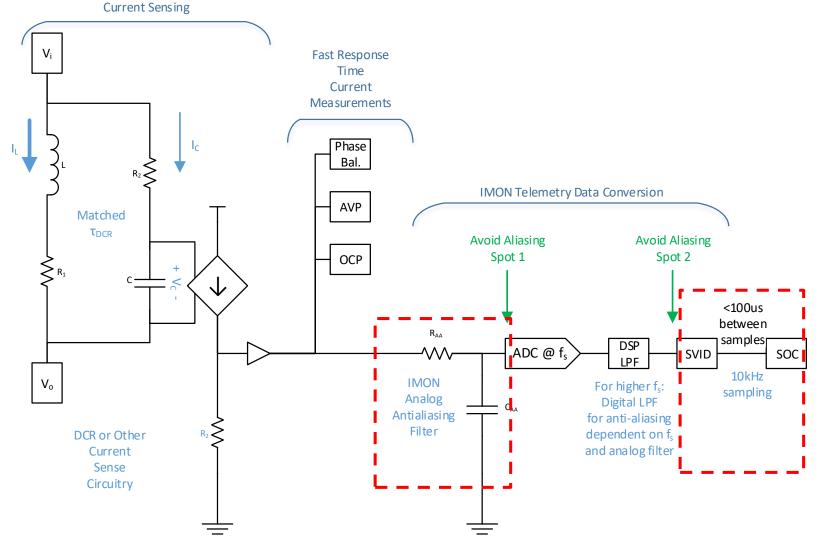

### IMON (15h) /ICC\_MAX(21h)

| Index | Register<br>Name         | Description<br>Note see detailed<br>paragraph for each<br>register                                                                                                                                                                                                         | Access         | Default                                                | Generational<br>VR Usage                                                                                                     |

|-------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 15h   | Output Current<br>(Iout) | Averaged output current.<br>For averaging and update/read<br>rates see VR PWM<br>specification.<br>Left justified, scaled to<br>Icc_max = ADC full range. IE<br>8 bit ADC, FFh=Icc_max or a<br>6 bit ADC, 3Fh = Icc_max,<br><b>TABLET</b><br>lower 8 bits of 10 BIT ADC,   | R-M<br>W-PWM   | Actual Iout<br>measured<br>after start<br>up<br>Note 2 | VR12 server<br>Required<br>IMVP7 Optional<br>VR12.5 Required<br>VR12.6 Required<br>VR13/IMVP8<br>Required<br>Tablet Required |

| 21h   | ICC_MAX                  | Data register containing the<br>Icc max the platform supports.<br>The platform design engineer<br>programs this value during the<br>design process. Binary Coded<br>Decimal format in amps, IE<br>100A = 64h. This data is used<br>with the Iout (15h) register<br>scaling | RO<br>platform | 00h<br>Note 2                                          | VR12/IMVP7<br>Required<br>VR12.5 Required<br>VR12.6 Required<br>Tablet Undefined<br>VR13/IMVP8<br>Required                   |

$$Imon = Iout(15h) \times \frac{IccMax(21h)}{255}$$

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may

Reference Number: 621792 Intel Confidential

Revision: 0.9

be claimed as the property of others. Copyright © 2020, Intel Corporation.

# **IMON Accuracy Targets**

Accuracy is a function of the PWM internal circuits, and measurement technique: either external inductor (or shunt) and NTC temperature coefficient matching network, or integrated MOSFET sensing in the power stage

- > Typical RSS 3 sigma platform accuracy targets

- > **Tighter tolerance** on current reporting will yield a platform with better turbo performance.

- IMON accuracy is needed for RAPL consistency. If accuracy is poor, the spread for PL1 and memory RAPL will be greater than a board with tighter IMON distribution curve. It is up to the ODM/OEM designer to do the cost, performance tradeoff between inductor sensing and MOSFET sensing.

- CPU power management regulation points such as PL1 (TDP) and PL2 depend on the IMON accuracy. Wide variation in IMON tolerance will have a direct impact on customer's TDP level.

Underreporting IMON results in higher CPU thermal dissipation; over-reporting IMON results in lower thermal dissipation and lower CPU performance. The accuracy targets at lighter loads are important for RAPL power capping algorithms

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation. Reference Number: 621792 Intel Confidential Revision: 0.9

# **Telemetry Anti-aliasing Example**

- Platform Power Management requires the VR to report a digitized value of output current over the SVID bus.

- The output current is to be sensed in a similar manner as **VR load line** and **phase current balance**.

- IMON support is required in all power states and every VID including OV.

- Aliasing can be avoided by a proper combination of analog filtering and digital filtering prior each of the two points.

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may

be claimed as the property of others. Copyright  $\ensuremath{\mathbb{C}}$  2020, Intel Corporation.

Reference Number: 621792 Intel Confidential

Revision: 0.9

39

íntel

### PWR\_IN (1Bh) /Pwr\_in\_Max (2Eh)

| Index | Register<br>Name        | Description<br>Note see detailed<br>paragraph for each<br>register                                                                                                    | Access       | Default | Generational<br>VR Usage                                                                                  |

|-------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------|-----------------------------------------------------------------------------------------------------------|

| 1Bh   | Input Power<br>PWR_IN   | Averaged Input Power or Psys.<br>For averaging and update/read<br>rates see VR PWM<br>specification. Averaging,<br>update interval same as Iout<br>(15h)              | R-M<br>W-PWM | Note 2  | VR12.0/IMVP7<br>Optional Note 3<br>VR12.5 Optional<br>VR13 Required<br>IMVP8 Required<br>Tablet Required  |

|       |                         | Left justified, scaled to<br>Pwr_In_max (2Eh) = ADC full<br>range.                                                                                                    |              |         |                                                                                                           |

|       | Tablet<br>Input Power L | Tablet<br>lower 8 bits of 10 BIT ADC of<br>Pin data                                                                                                                   |              |         |                                                                                                           |

| 2Eh   | Pwr_in_Max              | Input power sensor scaling for<br>Input Power(1Bh) register<br>Programmed by Platform<br>designer to the rating of the<br>Input Power Sensor.<br>Programmed as 2W/LSB |              |         | VR12/IMVP7<br>Undefined<br>VR12.5<br>Undefined<br>VR12.6<br>Undefined<br>IMVP8 undefined<br>VR13 required |

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation. Reference Number: 621792 Intel Confidential Revision: 0.9

#### Thermal Monitoring (12h) VR\_Hot# and Thermal Alert

- Bit6- Thermal Alert#, Bit7 VR\_Hot#

- VR\_Hot# is required to be routed to the processors PROCHOT# input pin for all market segments, to initiate thermal throttle low power state of the CPU to protect the VR from overheating.

- VR\_Hot# may also be routed to various system thermal management controllers

Temperature zone register and example

| Bit 7                                                           | Bit 6        | Bit 5                                                                             | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit O |  |  |  |

|-----------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------|--------|-------|-------|-------|-------|--|--|--|

| 100 %                                                           | 97 %         | 94 %                                                                              | 91 %   | 88 %  | 85 %  | 82 %  | 75 %  |  |  |  |

| VR_HOT#                                                         | ThermAlert   | Thermal indicator assertions occur as zone increases into the range bits 6 and 7. |        |       |       |       |       |  |  |  |

| Example t                                                       | hresholds fo | or 100°C                                                                          | temp m | ıax.  |       |       |       |  |  |  |

| 100°C 97°C 94°C 91°C 88°C 85°C 82°C 75°C                        |              |                                                                                   |        |       |       |       |       |  |  |  |

| Example register contents for 95°C temperature, 100°C temp max. |              |                                                                                   |        |       |       |       |       |  |  |  |

| 0                                                               | 0            | 1                                                                                 | 1      | 1     | 1     | 1     | 1     |  |  |  |

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may

be claimed as the property of others. Copyright © 2020, Intel Corporation.

Reference Number: 621792Intel ConfidentialRevision: 0.9

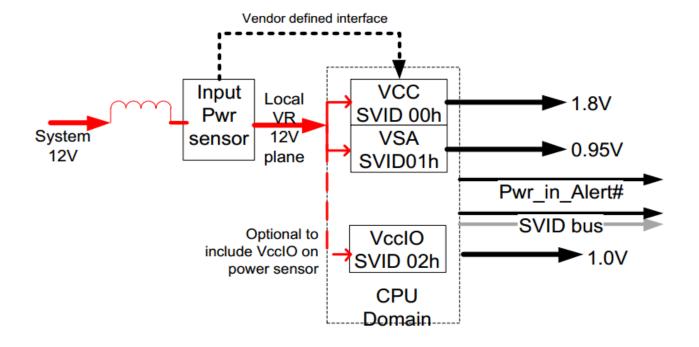

# Input Power sensor(1Bh)

This requirement applies to **both** CPU domains and memory domains. The sense element will be placed between the 12 V input filter inductor and bulk capacitors placed on the local 12 V plane feeding the domain voltage regulator circuits

- Pwr\_in Alert# used to change the state of the CPU from a PMax condition down to PL2 condition

- ➤ The goal of the PWR\_in Alert# is to reduce the PMax detection interval from 600us (3X IMON averaging time constant) to typical < 100 µs to reduce peak power stress on the input power supply 12V and the amount of 12V buffering capacitance.</p>

- Provide single point for RAPL power measurement for memory systems that mix both 12V NVDIMMs and standard DDR4 DIMMs

Note: CPU uses IMON data on the various rails and not the input sensor for RAPL and power limit calculations.

# Pwr\_in\_alert (2Fh)

This 8-bit read-write register is by default the same value Power In Max(address 2Eh), but can be set by the SVID master to any value lower than Power In Max. If an attempt is made to set the effective Power In Alert threshold higher than the effective Power In Max value, it will be acknowledged and stored, but the PWR\_IN\_ALERT# function will be disabled.

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation. intel

Reference Number: 621792 Intel Confidential Revision: 0.9

#### Slow slew rate and VR13.HC support (2Ah)

| Bit | Mode           | Name        | Default      | Definition                                                                                                                                                                                |

|-----|----------------|-------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Read-<br>only  | HC_SUPPORT* | See<br>Right | 0=VR13.HC mode not supported<br>1=VR13.HC mode supported                                                                                                                                  |

| 6   | Read-<br>write | HC_ACTIVE*  | 0            | 0=VR13.HC mode not active<br>1=VR13.HC mode activated                                                                                                                                     |

| 5   | Rsvd           | Reserved    | 0            | Default to 0                                                                                                                                                                              |

| 4   | Rsvd           | Reserved    | 0            | Default to 0                                                                                                                                                                              |

| 3:0 | Read-<br>Write | SlowSR_Ctrl | 2h           | 1XXX = Set Slow SR to Fast SR/16<br>01XX = Set Slow SR to Fast SR/8<br>001X = Set Slow SR to Fast SR/4<br>0001 = Set Slow SR to Fast SR/2<br>0000 = Leave Slow SR at its prior<br>setting |

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Reference Number: 621792 Intel Confidential

## VR13 High Current Support (VR13.HC)

- Existing VR13.0 platforms (ex. Purley) are capped at IccMax = 255A (IMON limit)

- Desired Objectives:

- IccMax > 255A would enable additional performance in future processors

- Minimize enabling work required to provide such a feature

- Maintain backwards compatible to the existing VR13.0 CPU (even if it's unaware of VR13.HC mode)

- Solution: Adds FIVE new registers to the SVID Protocol

- 1. HC Support bit (2Ah bit7) Indicates if VR can support beyond 255A

- 2. HC Mode Active bit (2Ah bit6) Write 1 bit to switch IMON I<sub>out</sub> and P<sub>in</sub> scaling from 255A to IccMax

- 3. IccMaxAdditional (50h) Amount of max(I<sub>out</sub>) beyond 255A, encoded at 2A/LSB. Iccmax(21h)

- **4.** PwrInMaxAdditional (51h) Amount of max(P<sub>in</sub>) beyond 510W, encoded at 4W/LSB.

PwrInMax(2Eh)

- PwrInThreshAdditional (52h) Amount to add to P<sub>jn</sub> threshold beyond 510W, encoded at 4W/LSB. PwrInTresh(2Fh)

Note: SVID = Intel<sup>®</sup> Serial Voltage Identification

### New in VR13.HC

The VR13.HC specification is designed to support up to 765A output current and 1530W input power telemetry.

#### VR13 High-Current mode example

| Setting         | HC_ACTIVE==0   | HC_ACTIVE == 1                   |

|-----------------|----------------|----------------------------------|

| Output Current  | IccMax         | ( IccMax + 2* IccMaxAdd )        |

| Full Range      | Amps           | Amps                             |

| Input Power     | (2*PwrInMax)   | (2*PwrInMax + 4*PwrInMaxAdd)     |

| Full Range      | Watts          | Watts                            |

| Input Power     | (2*PwrInAlert) | (2*PwrInAlert + 4*PwrInAlertAdd) |

| Alert Threshold | Watts          | Watts                            |

Intel Confidential

Where:

- IccMax = Register 21h.

- PwrInMax = Register 2Eh.

- PwrInAlert = Register 2Fh.

IccMaxAdd = Register 50h (VR13.HC only)

- PwrInMaxAdd = Register 51h (VR13.HC only)

- PwrInAlertAdd = Register 52h (VR13.HC only)

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Reference Number: 621792

Revision: 0.9

s the property of others. Copyright © 2020, Intel Corpor

# **SVID DEBUG TOOL AND COMMON ISSUE**

**Note:** SVID = Intel<sup>®</sup> Serial Voltage Identification

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

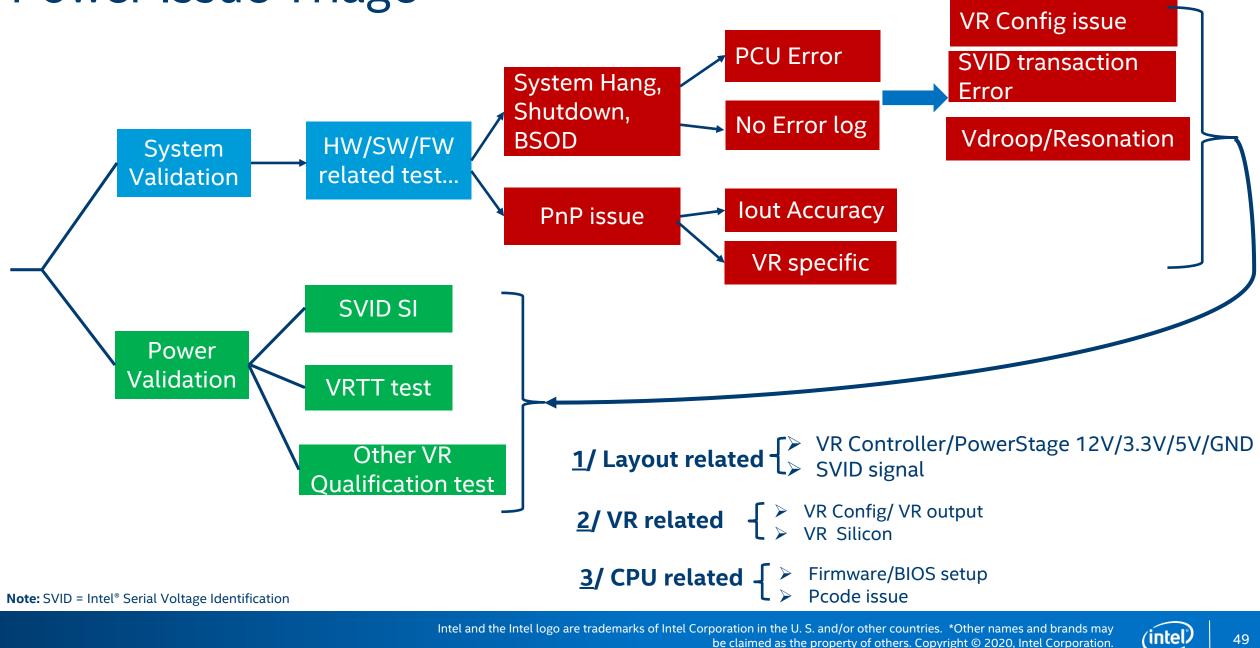

## Power Issue Triage

Reference Number: 621792 Intel Confidential

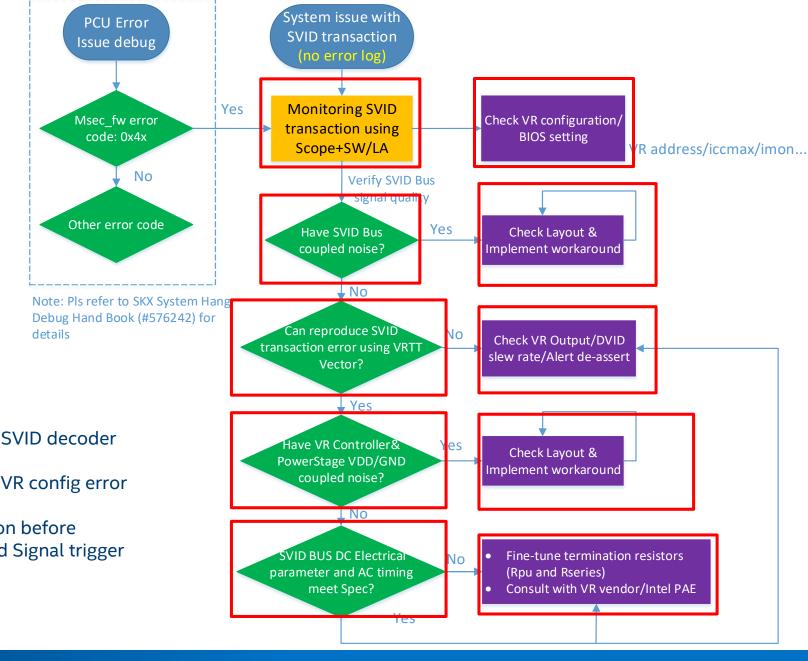

#### Suggested SVID Debug Flow

Note: SVID = Intel<sup>®</sup> Serial Voltage Identification

#### Note:

- 1. "SW" in Scope+SW means Scope SVID decoder or Intel SVID decoder checker;

- 2. PCU error can help to filter out its VR config error or SVID transaction error

- 3. Longer duration of SVID transaction before Processor Asynchronous Sideband Signal trigger need to be monitoring.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may

Reference Number: 621792 Intel Confidential

Revision: 0.9

be claimed as the property of others. Copyright © 2020, Intel Corporation.

#### PCU errors- MCA bank4 mc-status registers: Bits[31:24] (msec\_fw)

- 0x40 = MCA\_SVID\_VCCIN\_VR\_ICC\_MAX\_FAILURE; Fused CPU Icc-max exceeds Vccin VR's limit

- 0x41 = MCA\_SVID\_COMMAND\_TIMEOUT; SVID command timeout (busy bit was not cleared fast enough)

- 0x42 = MCA\_SVID\_VCCIN\_VR\_VOUT\_FAILURE; Fused CPU boot voltage exceeds Vccin VR's limit

- 0x43 = MCA\_SVID\_CPU\_VR\_CAPABILITY\_ERROR; A CPU VR found that does not support IOUT (IMON polling)

- **0x44 = MCA\_SVID\_CRITICAL\_VR\_FAILED;** Failure of critical VR detected during reset.

- 0x45 = MCA\_SVID\_SA\_ITD\_ERROR; Failure updating SA VR VID for ITD

- **0x46 = MCA\_SVID\_READ\_REG\_FAILED; SVID command to read a register failed**

- **0x47 = MCA\_SVID\_WRITE\_REG\_FAILED; SVID command to write a register failed**

- 0x48 = MCA\_SVID\_PKGC\_INIT\_FAILED; SVID initialization of PkgC support (at reset) failed

- 0x49 = MCA\_SVID\_PKGC\_CONFIG\_FAILED; SVID enable/disable of PkgC support (at runtime) failed

- **0x4a = MCA\_SVID\_PKGC\_REQUEST\_FAILED; SVID Pkgc request failed**

- 0x4b = MCA\_SVID\_IMON\_REQUEST\_FAILED; SVID IMON request failed

- 0x4c = MCA\_SVID\_ALERT\_REQUEST\_FAILED; SVID ALERT request failed

- **0x4d = MCA\_SVID\_MCP\_VR\_RAMP\_ERROR; MCP VR failed to ramp**

### SVID debug tools

- 1. 540269\_SVID\_Decoder\_Protocol\_Checker

- CSV or txt file from Scopes

- 2. Scopes support SVID protocol Firmware

- Contact local vendor's FAE for support

- 3. Third Party Logic Analyzer

- Support long data streams and triggering models

- More flexible to decode

These tools can be used to monitor the SVID signals and convert SVID binary traffic into readable format to aide in SVID or platform debug

Note: SVID = Intel<sup>®</sup> Serial Voltage Identification

### How to decode the SVID protocol?

- Logic Analyzer Only

- More details in following slides

- Pros: easy, simple to use

- Cons: signal quality not able to check

- Scope Only

- How to calculate by eye balls correctly?

- Rising edge or falling edge?

- Pros: signal quality can be checked

- Cons: One protocol at a time and takes time to decode by eye ball check

- Scope+LA

- Use LA to do protocol trigger and can check signal quality at the same time

Note: SVID = Intel<sup>®</sup> Serial Voltage Identification

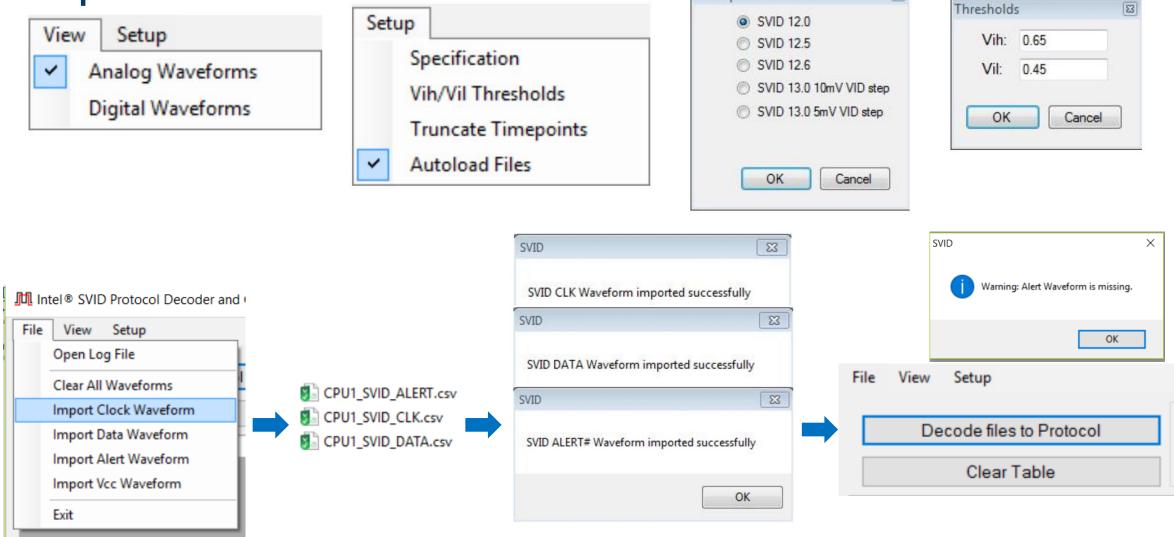

# Intel<sup>®</sup> Serial Voltage Identification Decode Tool Use

### Steps

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

**SVID** Specification

8

ion.

Reference Number: 621792 Intel Confidential

# Intel<sup>®</sup> Serial Voltage Identification Decode Tool Result Example

| File View Se  | tup                 |         |                      |                      |           |              |     |     |                                                                   |           |        |  |

|---------------|---------------------|---------|----------------------|----------------------|-----------|--------------|-----|-----|-------------------------------------------------------------------|-----------|--------|--|

| Deco          | le files to Protoco | Logging | Inactive             |                      |           |              |     |     |                                                                   |           |        |  |

|               | Clear Table         |         | C Active             |                      |           |              |     |     |                                                                   |           |        |  |

| TIME          | START               | ADDRESS | COMMAND              | M. PAYLOAD           | M. PARITY | M.PAR RESULT | END | ACK | S. PAYLOAD                                                        | S. PARITY | ALERT  |  |

| 6.380268e-003 | Start               | 04H     | 07h - GetReg (Rea    | 15h - Output Current | 1         | 0            | End | Ack | 01H                                                               | 1         | -      |  |

| 6.383470e-003 | Start               | 02H     | 07h - GetReg (Rea    | 15h - Output Current | 1         | 0            | End | Ack | 01H                                                               | 1         | -      |  |

| 6.922570e-003 | Start               | 00H     | 01h - SetVID-fast sl | 0.855V               | 0         | 0            | End | Ack | -                                                                 |           | -      |  |

| 6.924674e-003 | -                   |         | -                    | -                    | -         | -            | -   | -   | -                                                                 | -         | H to L |  |

| 6.926012e-003 | Start               | 00H     | 07h - GetReg (Rea    | 10h - Status_1       | 0         | 0            | End | Ack | 01H <vr at="" target<="" td=""><td>1</td><td>-</td><td></td></vr> | 1         | -      |  |

| 6.927128e-003 | -                   | -       | -                    | -                    |           |              | -   |     | -                                                                 | -         | L to H |  |

| 6.944112e-003 | Start               | 00H     | 04h - SetPS (Powe    | Light Load           | 0         | 0            | End | Ack | -                                                                 |           | -      |  |

| 6.957690e-003 | Start               | 00H     | 01h - SetVID-fast sl | 0.850V               | 0         | 0            | End | Ack | -                                                                 | -,        |        |  |

| 6.959686e-003 | -                   | -       | -                    | -                    | -         | -            | -   | -   | -                                                                 | -         | H to L |  |

| 6.961054e-003 | Start               | 00H     | 07h - GetReg (Rea    | 10h - Status_1       | 0         | 0            | End | Ack | 01H <vr at="" target<="" td=""><td>1</td><td>-</td><td></td></vr> | 1         | -      |  |

| 5.962172e-003 | -                   | -       |                      | -                    | -         | -            | -   | -   | -                                                                 | -         | L to H |  |

| 6.962698e-003 | Start               | 00H     | 04h - SetPS (Powe    | Light Load           | 0         | 0            | End | Ack | -                                                                 |           | -      |  |

| 6.977514e-003 | Start               | 00H     | 01h - SetVID-fast sl | 0.845V               | 1         | 0            | End | Ack |                                                                   | -         |        |  |

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may

be claimed as the property of others. Copyright © 2020, Intel Corporation.

55

Reference Number: 621792 Intel Confidential

#### SVID Transactions During System Boot up and Running

Intel Confidential

#### GetReg\*

- Vendor ID (Reg 0x00)

- Product ID (Reg 0x01)

- Product Revision (Reg 0x02)

- Product Date Code (Reg 0x03)

- Lot Code (Reg 0x04)

- Protocol ID (Reg 0x05)

- Capability ID (Reg 0x06)

- ICC Max (Reg 0x21)

- Loadline resistance (Reg 0x23)

- Fast/slow VID slopes (Regs 0x24 0x25)

- Pin\_MAX(Reg 0x2E)- BUS2/Memory

- Vout max VID (Reg 0x30)

- Status1 (Reg 0x10) -- clearing Alert# from Vboot

- SetRegADR/SetRegDAT

- SetVID\_Slow

#### **Boot Up**

Note: SVID = Intel<sup>®</sup> Serial Voltage Identification

GetReg 15h

SetVID\_Slow/Fast

GetReg 10h

SetWP1/2

GetReg 10h

#### System Running

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Reference Number: 621792

Revision: 0.9

(intel)

#### **Replicate SVID Transaction using VRTT Vector Features**

|    |          |           |                     |      |        |       |              | I     | Expect | ed       |     | Ac  | tual |      | F | Results | ÷ |        |

|----|----------|-----------|---------------------|------|--------|-------|--------------|-------|--------|----------|-----|-----|------|------|---|---------|---|--------|

| AI | FrStart  | VR Addr   | Command             | Data | Parity | FrEnd | Delay (Clks) | Ack   | Dat    | Par      | Ack | Dat | Par  | PErr | ſ | P/F     |   |        |

| 1  | 2 -      | 0 -       | 01 (Set VID Fast) 🔻 | 85 🝷 | Auto 🝷 | 3 🔹   | 33 🌲         | 10 🔻  | FF 🔻   | 1 -      | 10  | FF  | 1    | 1    |   | Ρ       |   |        |

|    | Stop Clk | Between ( | mds                 |      | 1      | ÷ DEL | AY (usec)    | 📃 Sto | Clk Du | ring Cmd |     |     |      |      |   |         |   |        |

| 2  | 2 -      | 0 -       | 01 (Set VID Fast) 🔻 | 6F - | Auto 🝷 | 3 🕶   | 2000 ≑       | 10 🔻  | FF 🔻   | 1 -      | 10  | FF  | 1    | 1    |   | Ρ       |   |        |

| 3  | 7 2 -    | 0 -       | 01 (Set VID Fast) 🔹 | 7E 🔻 | Auto 🝷 | 3 🕶   | 500 ≑        | 10 🔻  | FF 🔻   | 1 -      | 10  | FF  | 1    | 1    |   | Ρ       |   | SetVID |

| 4  | 2 •      | 0 -       | 07 (Get Reg) 🔹      | 10 - | Auto 🝷 | 3 🔹   | 2 🌲          | 10 🔻  | 01 🝷   | 1 🕶      | 10  | 01  | 1    | 0    |   | Ρ       |   |        |

|                               |                                | Expected            | Actual         | Results |

|-------------------------------|--------------------------------|---------------------|----------------|---------|

| All 📃 FrStart VR Addr Command | Data Parity FrEnd Delay (Clks) | Ack Dat Par Ack     | k Dat Par PErr | P/F     |

| 1 🔽 2 ▼ F ▼ 09 (SetWP) ▼      | 21 • Auto • 3 • 125 🜩          | 10 • FF • 1 • 10    | 0 FF 1 1       | P       |

| Stop Clk Between Cmds         | 1 😔 DELAY (usec)               | Stop Clk During Cmd |                |         |

| 2 🔽 2 💌 2 💌 07 (Get Reg) 💌    | 10 • Auto • 3 • 75 🚔           | 10 - 01 - 1 - 10    | 0 01 1 0       | P SetWP |

| 3 🔽 2 💌 0 💌 07 (Get Reg) 💌    | 10 • Auto • 3 • 175 🜩          | 10 • 01 • 1 • 10    | 0 01 1 0       | P       |

| 4 🔽 2 ▼ 1 ▼ 07 (Get Reg) ▼    | 10 • Auto • 3 • 2 🛬            | 10 • 01 • 1 • 10    | 0 01 1 0       | P       |

#### Tips:

- 1. Increase static current loading to target rails

- 2. Adjusting output voltage to target rails

Note: SVID = Intel<sup>®</sup> Serial Voltage Identification

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Reference Number: 621792 Intel 0

Intel Confide<u>ntial</u>

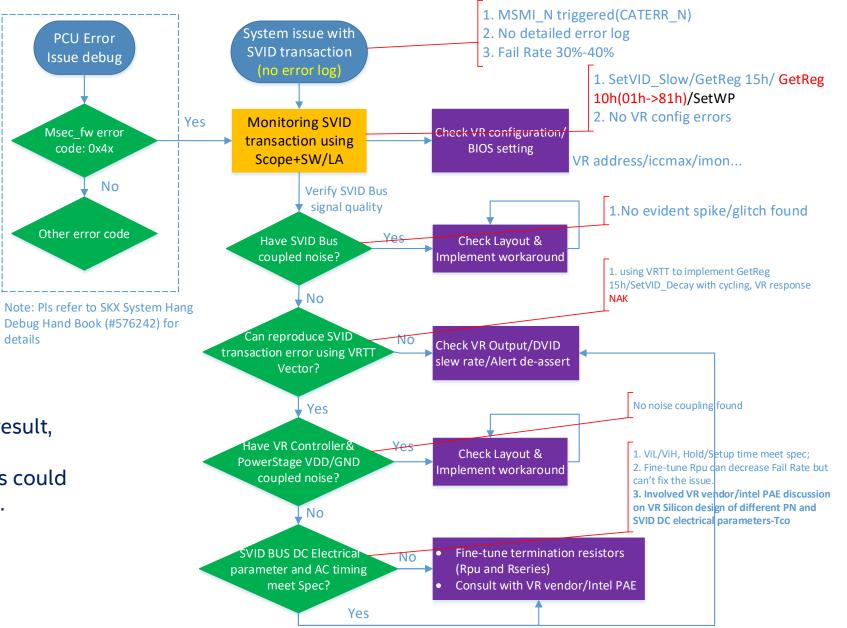

### Real case

Case1. System Hang with MSMI\_N(or CATERR\_N) triggered during enter/exit PkgC6

Case2. System hang issue with IERR during OS installation

Case3. Purley EP2S system hang during C state transition

#### Notes:

- 1) Take note of each experiment, test result, waveforms

- 2) Hypothesis, experiment and theories could be revised based on actual test data.

Note: SVID = Intel<sup>®</sup> Serial Voltage Identification

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may

Reference Number: 621792 Intel Confidential

Revision: 0.9

be claimed as the property of others. Copyright © 2020, Intel Corporation.

## SVID Errors That Cause CPU to Hang

- REJ/NAK of initial SVID GETREG on VccIN VR

- No VR present or bus not working, CPU halt

- Icc\_Max (21h) mismatch to CPU rating during initialization

CPU halts, issues CATERR# (Catastrophic Error Signal)

- SVID communication error checking

- Occurs when CPU receives NAK or REJ or parity error

- CPU retries same command 3 times, if all fail CPU halts, issues CATERR# signal

- If multiple retries are observed, check SVID bus signal integrity and pull-up values to meet VIO, VIL levels

- VR failing to return Alert# after a SetVID\_Fast or SetVID\_Slow command from low voltage to higher voltage

- O CPU may hang or stay in low performance mode, no CATERR# issued

Note: SVID = Intel<sup>®</sup> Serial Voltage Identification

# BACKUP

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Reference Number: 621792 Intel Confidential

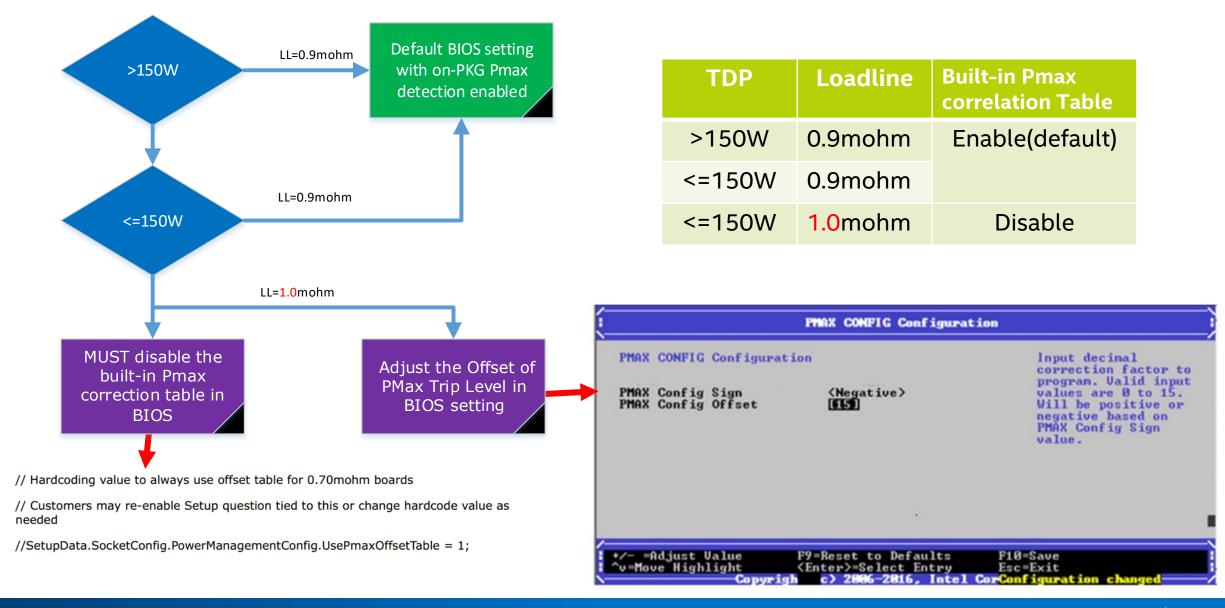

#### BIOS setting for On-Package Pmax detection at different SKU -Purley

Reference Number: 621792

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may

be claimed as the property of others. Copyright © 2020, Intel Corporation. Intel Confidential Revision: 0.9

#### Data Sampling and Timing Analysis

- CPU drive on rising edge, VR sample on failing edge

- VR acts on the command after driving ACK bits in data frame

- VR drive on rising edge, CPU sample on failing edge

Measurement tips:

• Probe SVID signals at VR side or CPU side?

Tco = clock to data delay Tpd= propagation delay on clk/data signal trace

#### Note: SVID = Intel<sup>®</sup> Serial Voltage Identification

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Reference Number: 621792 Intel Confidential

Revision: 0.9