# 2.4G SOC HW2171B

# **Data Sheet**

- Product Introduction

- Data Sheet

- Specifications

Shanghai Neusoft carrier Microelectronics Co., Ltd.

2019 year 4 month twenty two day

### **Ordering Information**

| Part NO.         | Operating Voltage | ОТР              | SRAM           | 1/0 | ADC | Timer     | Package Type |

|------------------|-------------------|------------------|----------------|-----|-----|-----------|--------------|

| HW2171BP4SD 2.1V | ~ 3.6V 2K Words 6 | 4 Bytes 8 + 1INF | UT 12-bit X 6c | h   |     | 8-bit X 2 | SOP16        |

Ground Address: Long Cao Road, Shanghai, China 299 No. Tianhua Information Science and Technology

Park 2A floor 5 Post office Code: 200235 E-mail : support@essemi.com

Electricity Tel: + 86-21-60910333 pass Fax: + 86-21-60914991 network site: <u>http://www.essemi.com</u>

all rights reserved ©

#### Shanghai Neusoft carrier Microelectronics Co., Ltd.

The information content Microelectronics Co., Ltd. Shanghai Neusoft carrier on the basis of existing data and carefully compiled seek accurate, examples described in this document to the correct use and operation of the standard as a precondition, the application of the consumer Please give full consideration to the instance and other various external conditions, Neusoft carrier Shanghai Microelectronics Co., Ltd. does not warrant or confirm the suitability of such examples in the use side, adequacy or completeness, nor Microelectronics Co., Ltd. Shanghai Neusoft carrier resulting from the use of consumer All contents of this information may have been or risks or consequences of any liability. Based on the content of this document is more complete and other reasons, Shanghai Neusoft carrier Microelectronics Limited reserves the right to make changes without notice. Consumer For the latest product information, please feel free to contact the above contact details Co., Ltd. and Shanghai Neusoft carrier microelectronics.

## revise history

| version | Modified Date            | Change Summary                                                                                                                                                              |

|---------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V1.0    | 2018-9-14 First edition. |                                                                                                                                                                             |

| V1.1    | 2019-3-14                | <ol> <li>increase IAP Operation and interrupt enable bit GIE The supplement;</li> <li>RF New register list PKG_RSSI Register Description;</li> <li>change Logo .</li> </ol> |

| V1.2    | 2019-4-22 change ACK     | Number of retransmissions will be described.                                                                                                                                |

3/145

## table of Contents

## **Content Directory**

| The first 1 cha | pter   | Chip Introduction                                           | 13          |

|-----------------|--------|-------------------------------------------------------------|-------------|

| 1.1             |        | Outline                                                     | 13          |

| 1.2             |        | System Block Diagram                                        | 16          |

| 1.3             |        | Pin allocation map                                          |             |

|                 | 1. 3.1 | Pin Description                                             |             |

|                 | 1.3.2  | Pin Multiplexing description                                |             |

|                 | 1. 3.3 | Interconnector                                              |             |

|                 | 1. 3.4 | MCU Note dangling feet                                      |             |

|                 | 1. 3.5 | HW2171B with HW2171 Differences pin control                 | 20          |

| The first 2 cha | pter   | MCU- Core Features                                          | twenty one  |

| twenty          | one    | CPU Core Overview                                           | twenty one  |

| twenty          | two    | The system clock cycle and machine                          | twenty one  |

| twenty          | three  | Instruction Set Overview                                    | twenty one  |

| twenty          | four   | Special Function Register                                   | twenty two  |

| The first 3 cha | pter   | MCU- Storage resources                                      | twenty four |

| 3.1             |        | Outline                                                     | twenty four |

| 3.2             |        | Program Memory                                              | twenty four |

|                 | 3. 2.1 | Outline                                                     | twenty four |

|                 | 3. 2.2 | Program address map schematic                               | twenty four |

|                 | 3. 2.3 | Program Counter ( PC )                                      | twenty four |

|                 | 3. 2.4 | Program stack                                               |             |

| 3.3             |        | IAP access OTP operating                                    |             |

|                 | 3. 3.1 | OTP Memory                                                  |             |

|                 | 3. 3.2 | Table read instruction                                      |             |

|                 | 3. 3.3 | IAP program                                                 |             |

|                 | 3. 3.4 | Special Function Registers                                  |             |

| 3.4             |        | Data Memory                                                 |             |

|                 | 3. 4.1 | Outline                                                     |             |

|                 | 3. 4.2 | Data address map                                            |             |

|                 | 3. 4.3 | General data memory                                         |             |

|                 | 3. 4.4 | Special Function Registers                                  |             |

|                 | 3. 4.5 | Addressing                                                  |             |

|                 | 3. 4.6 | Special Function Registers                                  |             |

| The first 4 cha | pter   | MCU- Input / output ports                                   | 33          |

| 4.1             |        | Outline                                                     |             |

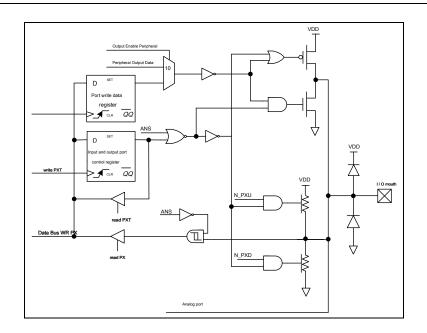

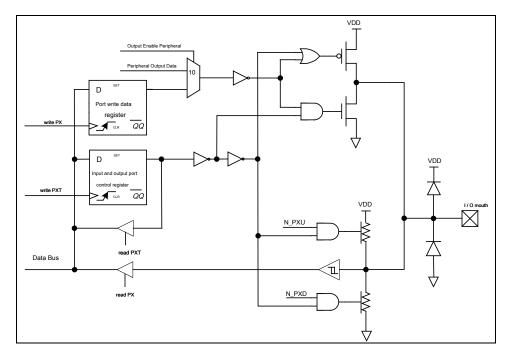

| 4.2             |        | Structure diagram                                           |             |

| 4.3             |        | I / O Port feature set                                      |             |

|                 | 4. 3.1 | I / O Port Input / Output Control                           | 34          |

|                 | 4.3.2  | I / O Weak pull-up on the port, the weak pull-down function |             |

|                 | 4. 3.3 | I / O Port Large current control function                   |             |

|                 | 4. 3.4 | I / O Port analog / digital type selection function         |             |

|                | 4. 3.5 | I / O Port multiplexing function                    | 35 |

|----------------|--------|-----------------------------------------------------|----|

| 4.4            | 4. 0.0 | Port Interrupt                                      |    |

| т.т            | 4.4.1  | Key interrupt ( KINT )                              |    |

|                | 4. 4.2 | External port interrupt ( PINT )                    |    |

| 4.5            |        | I / O Port Handling Precautions                     |    |

| 4.6            |        | Special Function Register                           |    |

| The first 5 ch | antor  | MCU- Special features and operating characteristics |    |

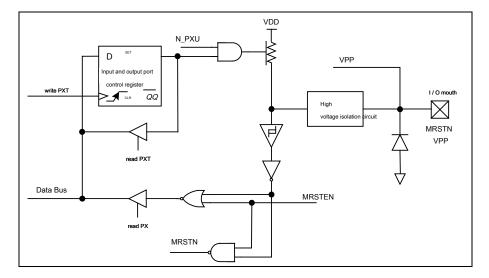

| 5.1            |        | The system clock oscillator                         |    |

| 0.1            | 5. 1.1 | Outline                                             |    |

|                | 5. 1.2 | Clock Source                                        |    |

|                | 5. 1.3 | Switching system clock                              |    |

|                | 5. 1.4 | The system clock divider                            |    |

|                | 5. 1.5 | Special Function Registers                          |    |

| 5.2            | 00     | Watchdog Timer                                      |    |

| 0.2            | 5. 2.1 | Outline                                             |    |

|                | 5. 2.2 | e                                                   |    |

|                | 5. 2.3 | WDT Timer                                           |    |

|                | 5. 2.4 | Special Function Registers                          |    |

| 5.3            |        | Reset module                                        |    |

|                | 5. 3.1 | Outline                                             | 51 |

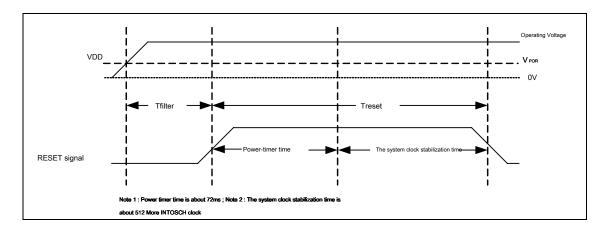

|                | 5. 3.2 | Power-On Reset                                      | 51 |

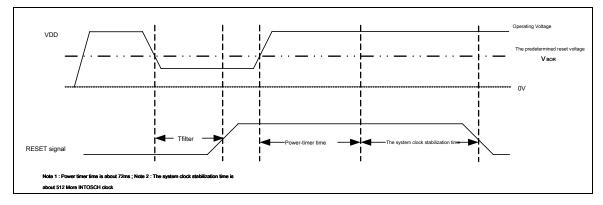

|                | 5. 3.3 | Under power-on reset                                | 51 |

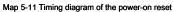

|                | 5. 3.4 | external MRSTN Reset pin                            | 52 |

|                | 5. 3.5 | Watchdog timer overflow reset                       | 53 |

|                | 5. 3.6 | RST Reset command                                   | 54 |

|                | 5. 3.7 | Special Function Registers                          | 55 |

| 5.4            |        | Low-power operation                                 | 56 |

|                | 5. 4.1 | MCU Low-power mode                                  | 56 |

|                | 5. 4.2 | Low power mode configuration                        | 56 |

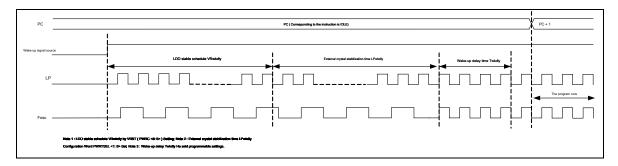

|                | 5. 4.3 | IDLE Wake-up configuration                          | 57 |

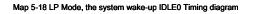

|                | 5. 4.4 | Wake timing diagram                                 | 57 |

|                | 5. 4.5 | Special Function Registers                          | 59 |

| The first 6 ch | apter  | MCU- Peripherals                                    | 60 |

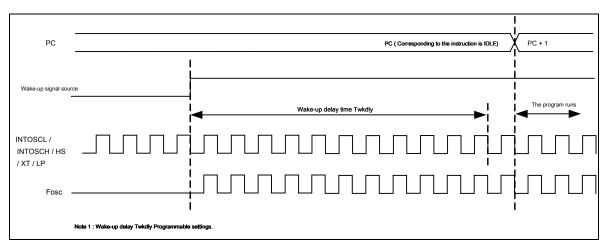

| 6.1            |        | 8 Place PWM Base Timer ( T8P1 / T8P2 )              | 60 |

|                | 6. 1.1 | Outline                                             | 60 |

|                | 6. 1.2 | e                                                   |    |

|                | 6. 1.3 | Operating mode                                      | 61 |

|                | 6.1.4  | Prescaler and divider                               | 61 |

|                | 6. 1.5 | Timer Mode                                          | 62 |

|                | 6. 1.6 | PWM Output Mode                                     | 63 |

|                | 6. 1.7 | PWM Average precision extension                     | 65 |

|                | 6. 1.8 | PWM Multiplexed output port                         | 65 |

|                | 6. 1.9 | Special Function Registers                          | 66 |

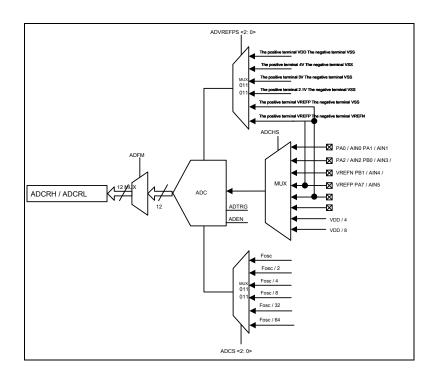

| 6.2            |        | A / D converter module ( ADC )                      |    |

|                |        |                                                     |    |

| 6. 2.1               | Outline                                       |     |

|----------------------|-----------------------------------------------|-----|

| 6. 2.2               | ADC e                                         | 70  |

| 6. 2.3               | ADC Configuration                             | 71  |

| 6. 2.4               | ADC Conversion step                           |     |

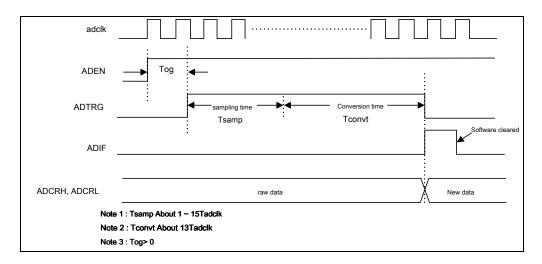

| 6. 2.5               | AD Timing Characteristics schematic           |     |

| 6. 2.6               | ADC Application routines                      |     |

| 6. 2.7               | Special Function Registers                    | 74  |

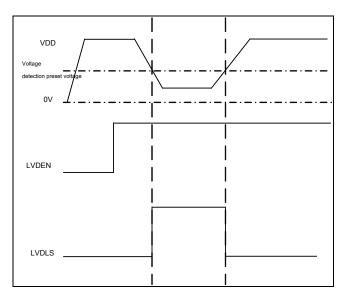

| 6.3                  | Low voltage detection module ( LVD )          |     |

| 6. 3.1               | Outline                                       |     |

| 6.3.2                | LVD operating                                 |     |

| 6. 3.3               | Special Function Registers                    |     |

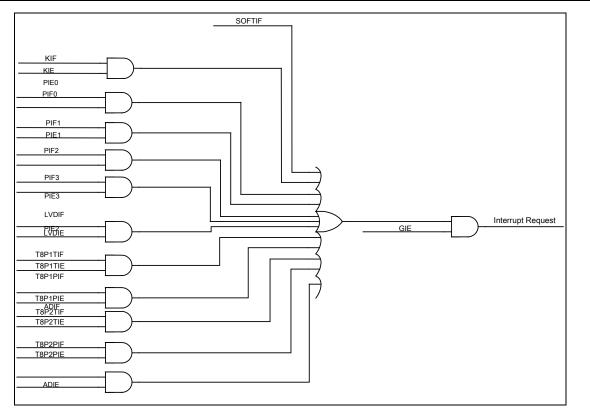

| The first 7 chapter  | MCU- Interrupt processing                     |     |

| 7.1                  | Outline                                       |     |

| 7.2                  | Internal structure                            |     |

| 7. 2.1               | The default interrupt mode                    |     |

| 7.3                  | Interrupt Context                             |     |

| 7.4                  | Interrupt operation                           |     |

| 7. 4.1               | Interrupt enable bit GIE Operations           |     |

| 7. 4.2               | External Interrupt                            | 80  |

| 7.4.3                | External Key interrupt                        | 80  |

| 7.4.4                | T8Pn (T8P1 / T8P2) Timer interrupt            | 80  |

| 7.4.5                | T8Pn (T8P1 / T8P2) Periodic interrupt         | 80  |

| 7.4.6                | ADC Interrupt                                 |     |

| 7.4.7                | LVD Interrupt                                 |     |

| 7. 4.8               | Interrupt Handling Precautions                | 81  |

| 7.5                  | Special Function Register                     | 82  |

| The first 8 chapter  | MCU- Chip configuration word                  |     |

| The first 9 chapter  | MCU-Instruction Set                           |     |

| 9.1                  | Outline                                       |     |

| 9.2                  | Operation instruction register                |     |

| 9.3                  | Program Control Instructions                  |     |

| 9.4                  | Arithmetic / logic operation instructions     |     |

| The first 10 chapter | MCU- Special Function Registers Summary Table |     |

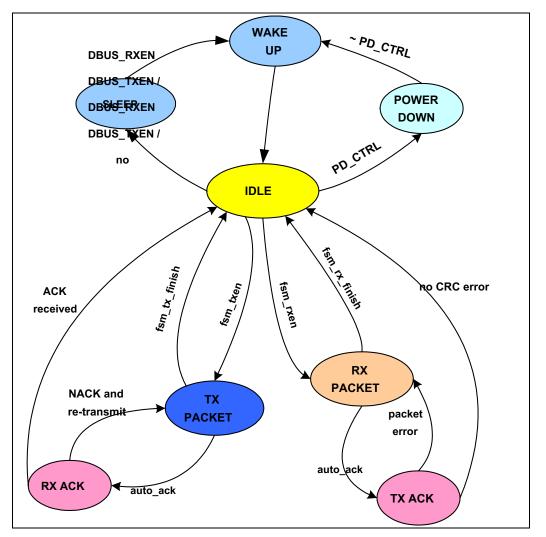

| The first 11 chapter | RF Transceiver - the operating mode control   |     |

| 11.1                 | POWER DOWN mode                               |     |

| 11.2                 | SLEEP mode                                    |     |

| 11.3                 | IDLE mode                                     |     |

| 11.4                 | TX mode                                       |     |

| 11.5                 | RX mode                                       |     |

| The first 12 chapter | RF Transceivers - packet structure            |     |

| 12.1                 | PTX Transmission packet structure             |     |

| 12.2                 | PRX send ACK Packet structure                 | 100 |

| The first 13 chapter | RF Transceiver - Link Control mode            | 101 |

| 13.1                 | Hardware link control                         |     |

| 13.2                         | Software Link Control mode                                               | 101 |

|------------------------------|--------------------------------------------------------------------------|-----|

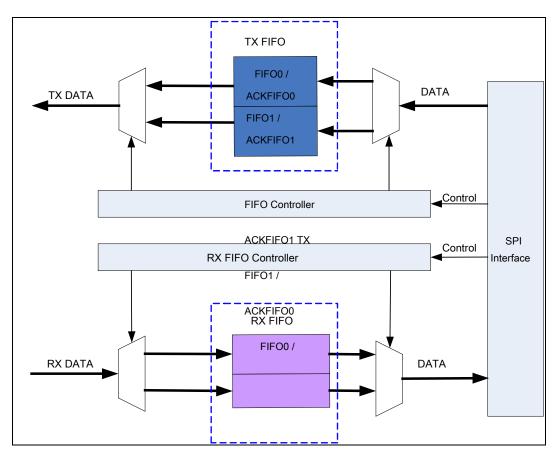

| The first 14 chapter         | RF Transceivers - and more PIPE Logical Channel                          | 102 |

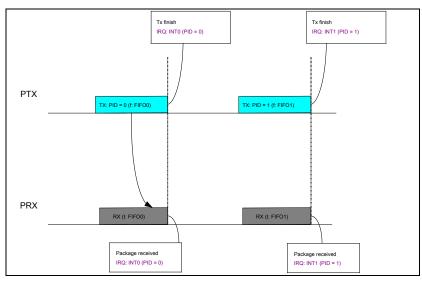

| The first 15 chapter         | RF Transcelver - Automatic Response ACK And automatic retransmission ART | 103 |

| 15.1                         | ACK Without ACK PAYLOAD                                                  | 103 |

| 15.2                         | ACK band ACK PAYLOAD                                                     | 103 |

| The first 16 chapter         | RF Transceivers - Data and control interface                             | 104 |

| 16.1                         | FIFO                                                                     | 104 |

| 16.2                         | Interrupt                                                                | 105 |

| 16. 2.1                      | Link control hardware interrupts                                         | 105 |

| 16. 2.2                      | Link Control software interrupt                                          | 109 |

| 16.3                         | SPI Communication Interface                                              | 109 |

| 16. 3.1                      | SPI Frame format                                                         | 109 |

| 16. 3.2                      | Register Access Timing                                                   | 110 |

| 16. 3.3                      | FIFO Access Timing                                                       | 110 |

| 16. 3.4                      | SPI Timing Parameters                                                    | 111 |

| The first 17 chapter         | RF Transceiver - Other functions provided                                | 112 |

| 17.1                         | RF Transceiver reset                                                     | 112 |

| 17.2                         | Frequency settings                                                       | 112 |

| 17.3                         | Automatic offset correction ( AFC)                                       | 112 |

| 17.4                         | Software offset correction                                               | 112 |

| 17.5                         | The preamble instructions                                                | 112 |

| 17.6                         | RSSI Features                                                            | 113 |

| 17.7                         | Carrier detect indication ( Carrier Detect) Features                     | 113 |

| 17.8                         | FEC , CRC , SCRAMBLE Features                                            | 113 |

| The first 18 chapter         | RF Transceivers - Register                                               | 115 |

| 18.1                         | Register List                                                            | 115 |

| 18.2                         | Register Description                                                     | 116 |

| The first 19 chapter         | RF Transceivers - Explanation of terms                                   | 131 |

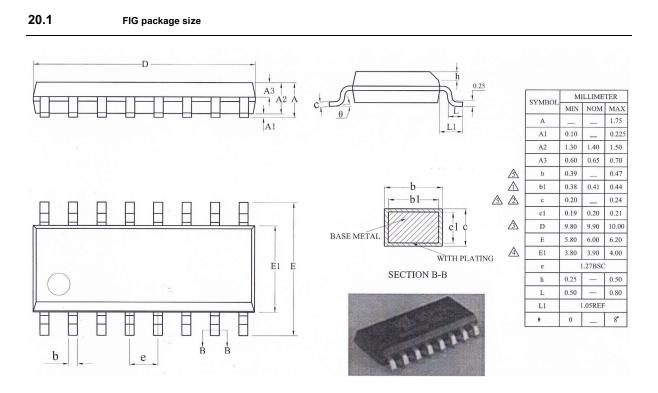

| The first 20 chapter         | FIG package size                                                         | 132 |

| 20.1                         | FIG package size                                                         | 132 |

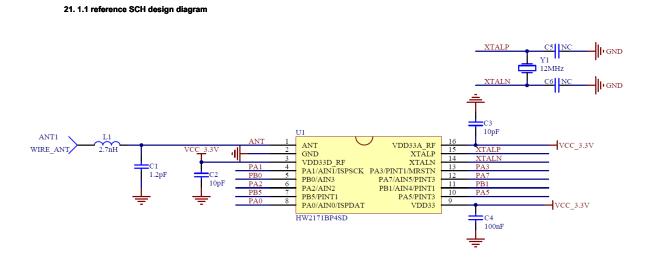

| The first twenty one chapter | Application Reference Design                                             | 133 |

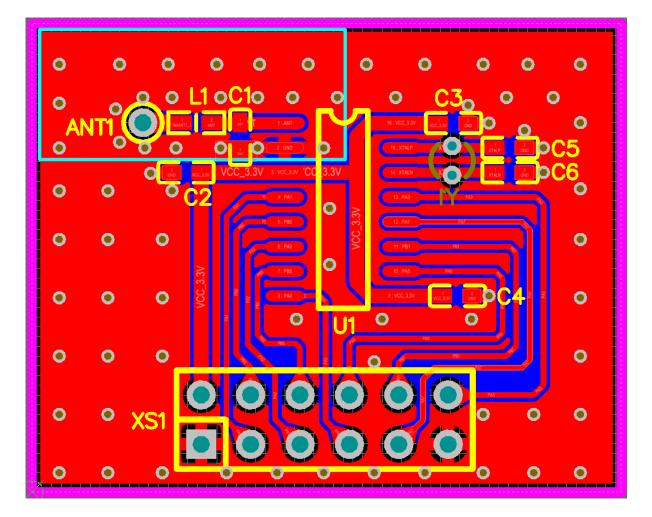

| 21.1                         | Typical Application Reference PCB design                                 | 133 |

| 21. 1.1                      | reference SCH design diagram                                             | 133 |

| 21. 1.2                      | Reference Design SCH Considerations                                      | 133 |

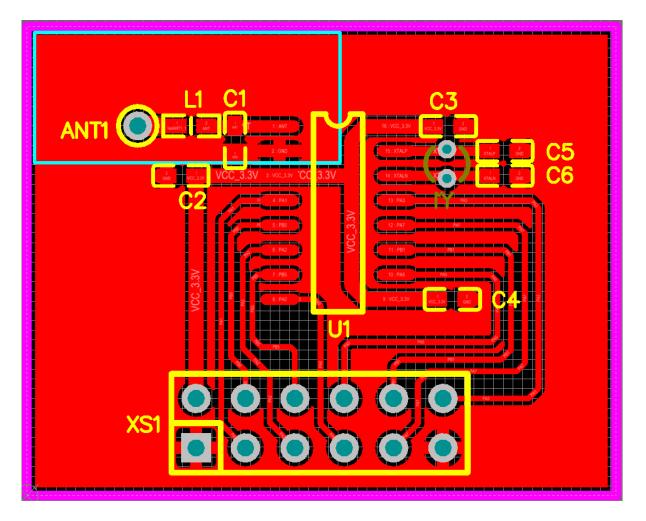

| 21.2                         | reference PCB design                                                     | 134 |

| 21. 2.1                      | Single panel PCB                                                         | 134 |

| 21. 2.2                      | Single panel PCB Design Considerations                                   | 134 |

| 21. 2.3                      | Double panel PCB                                                         | 135 |

| 21. 2.4                      | Double panel PCB Design Considerations                                   | 135 |

| The first twenty two chapter | Electrical Characteristics                                               | 136 |

| 22.1                         | MCU Electrical Characteristics                                           | 136 |

| 22. 1.1                      | The maximum nominal value                                                | 136 |

| 22. 1.2                      | Power Parameters                                                         | 136 |

| 22. 1.3                      | Input port parameters                                                    | 137 |

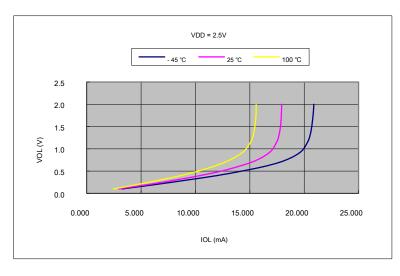

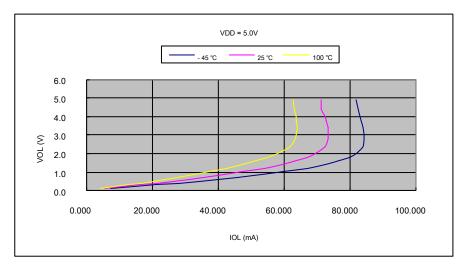

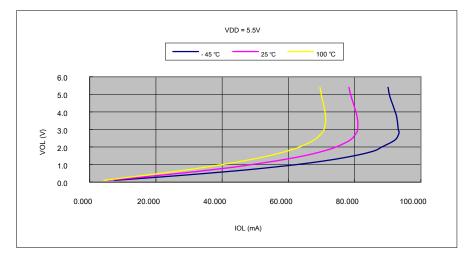

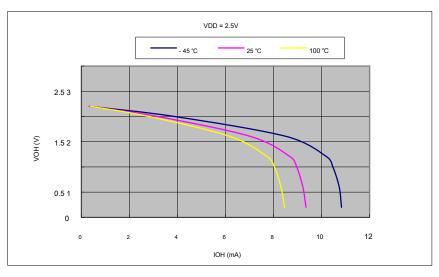

| 22. 1.4                       | Output port parameters                                                                  | 138 |

|-------------------------------|-----------------------------------------------------------------------------------------|-----|

| 22. 1.5                       | System clock parameters                                                                 | 138 |

| 22. 1.6                       | internal 16MHz RC Clock calibration parameters                                          | 138 |

| 22. 1.7                       | ADC AC parameters                                                                       | 138 |

| 22. 1.8                       | ADC Conversion time parameters                                                          | 139 |

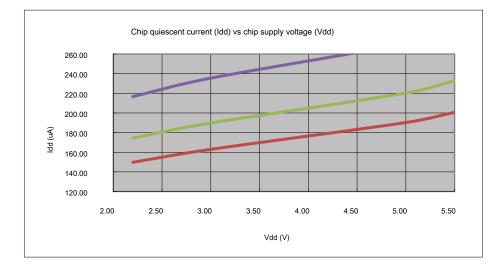

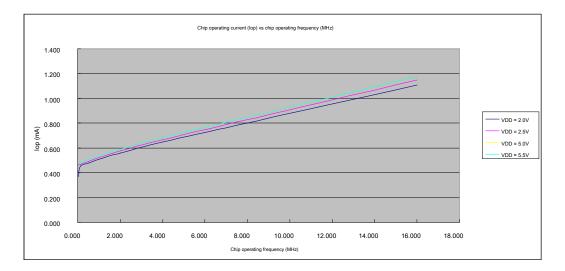

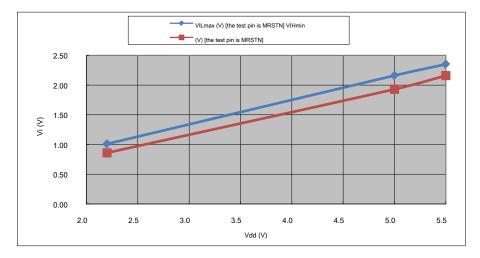

| 22.2                          | MCU FIG characteristic parameter                                                        | 140 |

| 22.3                          | RF Transceiver Electrical Characteristics                                               | 144 |

|                               |                                                                                         |     |

| 22. 3.1                       | Power Parameters                                                                        | 144 |

| 22. 3.1<br>22. 3.2            | Power Parameters                                                                        |     |

|                               |                                                                                         |     |

| 22. 3.2                       | The basic parameters of Communications                                                  |     |

| 22. 3.2<br>22. 3.3            | The basic parameters of Communications                                                  |     |

| 22. 3.2<br>22. 3.3<br>22. 3.4 | The basic parameters of Communications<br>Transmitter parameters<br>Receiver parameters |     |

List of Figures

| Map 1-1 System block diagram showing the internal structure                            | 16          |

|----------------------------------------------------------------------------------------|-------------|

| Map 1-2 Pin allocation map                                                             | 17          |

| Map 3-1 Program address map                                                            | twenty four |

| Map 3-2 Stack schematic                                                                | 26          |

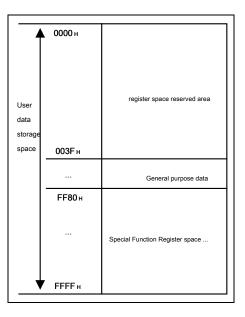

| Map 3-3 A schematic view of a data address map                                         | 29          |

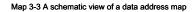

| Map 3-4 Special Function Register space                                                | 30          |

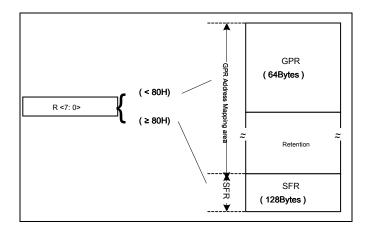

| Map 3-5 Direct addressing schematic general                                            | 31          |

| Map 3-6 Indirect schematic                                                             |             |

| Map 4-1 Input / output port configuration diagram - PA0 ~ PA2, PA7, PB0 ~ PB1          |             |

| Map 4-2 Input / output port configuration diagram - PA4 ~ PA6, PB2 ~ PB5               |             |

| Map 4-3 FIG input port structure - PA3                                                 |             |

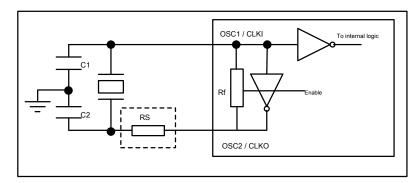

| Map 5-1 The system clock internal structure of FIG.                                    | 40          |

| Map 5-2 Crystal / resonator mode ( HS , XT , LP mode)                                  | 41          |

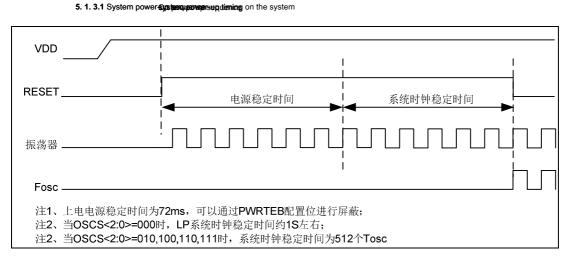

| Map 5-3 System power timing chart                                                      |             |

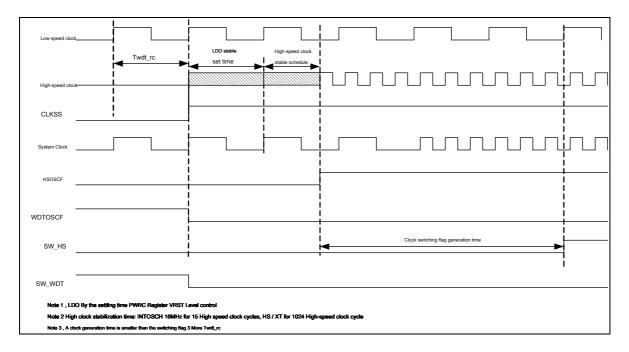

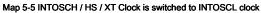

| Map 5-4 INTOSCL Clock is switched to INTOSCH / HS / XT clock                           | 43          |

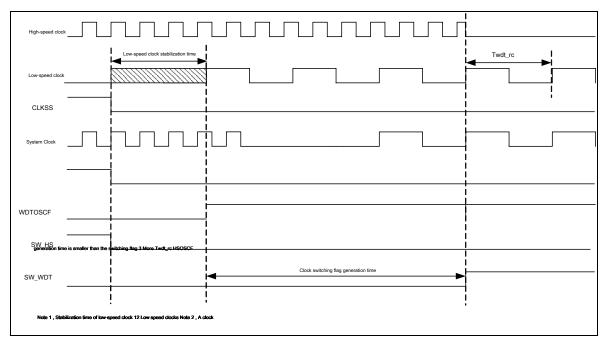

| Map 5-5 INTOSCH / HS / XT Clock is switched to INTOSCL clock                           |             |

| Map 5-6 Low Speed LP Clock is switched to INTOSCH clock                                | 44          |

| Map 5-7 INTOSCH Clock is switched to a low speed LP clock                              |             |

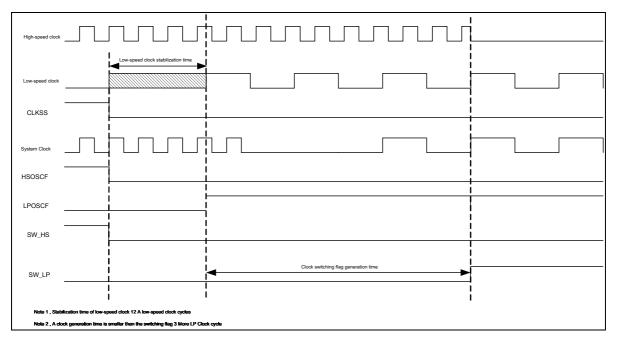

| Map 5-8 Watchdog timer internal structure                                              | 48          |

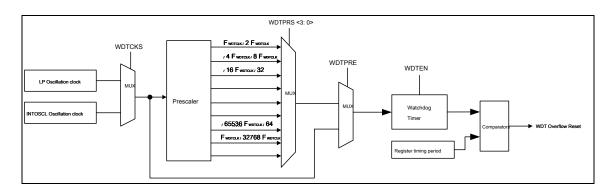

| Map 5-9 Schematic chip reset                                                           |             |

| Map 5-10 Timing diagram of power-on reset                                              |             |

| Map 5-11 Timing diagram of the power-on reset                                          |             |

| Map 5-12 external MRSTN Reset pin                                                      |             |

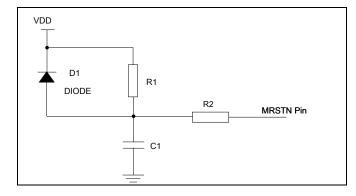

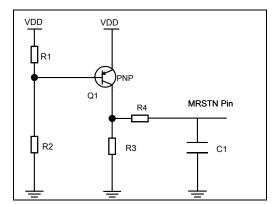

| Map 5-13 MRSTN Reset circuit diagram of a reference 1                                  |             |

| Map 5-14 MRSTN Reset circuit diagram of a reference 2                                  |             |

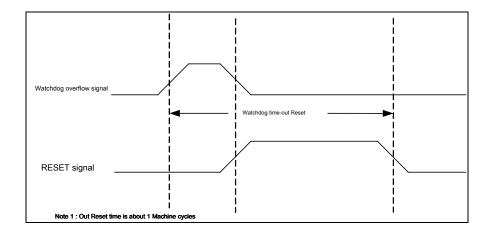

| Map 5-15 Watchdog Time-out Reset                                                       |             |

| Map 5-16 RST Reset command                                                             |             |

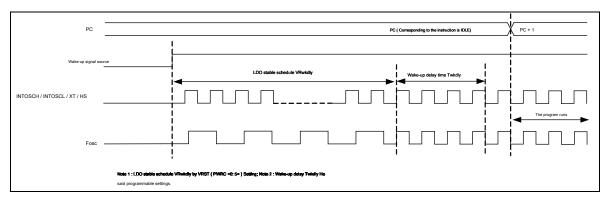

| . Map 5-17 HS / XT / INTOSCO / INTOSC Mode, the system wake-up IDLE0 Timing diagram    |             |

| Map 5-18 LP Mode, the system wake-up IDLE0 Timing diagram                              |             |

| Map 5-19 HS / XT / INTOSCO / INTOSC / LP Mode, the system wake-up IDLE1 Timing diagram |             |

| Map 6-1 T8P1 / T8P2 e                                                                  |             |

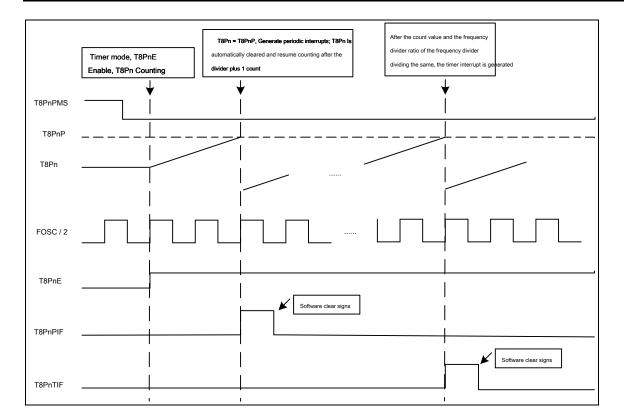

| ' Map 6-2 T8Pn Timer Mode Timing Chart                                                 |             |

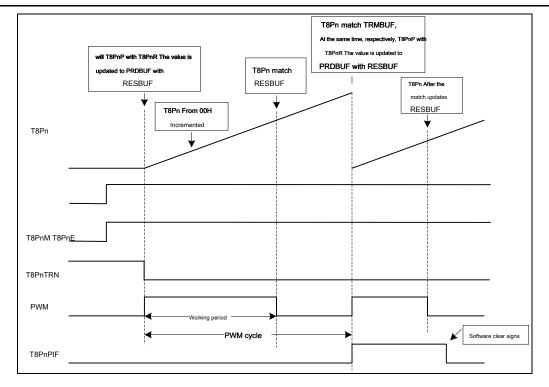

| Map 6-3 T8Pn PWM Schematic model                                                       |             |

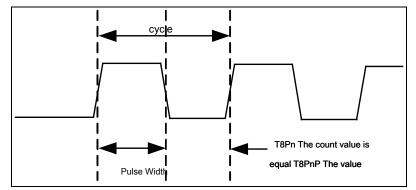

| Map 6-4 PWM Output schematic                                                           |             |

| Map 6-5 PWM Extended precision schematic                                               |             |

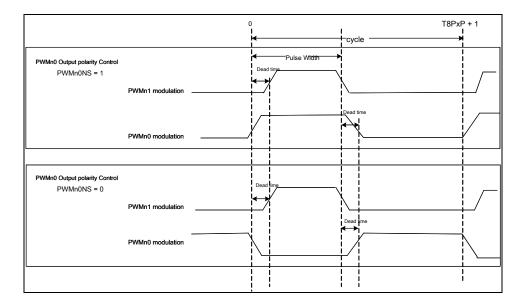

| Map 6-6 With dead complementary PWM Output schematic                                   |             |

| Map 6-7 ADC e                                                                          |             |

| Map 6-8 ADC Timing Characteristics schematic                                           |             |

| Map 6-9 LVD Operation Timing Chart                                                     |             |

| Map 7-1 Interrupt control logic                                                        |             |

| Map 11-1 RF A schematic view of the operating mode control Transceiver                 |             |

| Map 14-14 road PIPE Communication schematic                                            |             |

| Map 16-1 FIFO Control schematic                                                        |             |

9/145

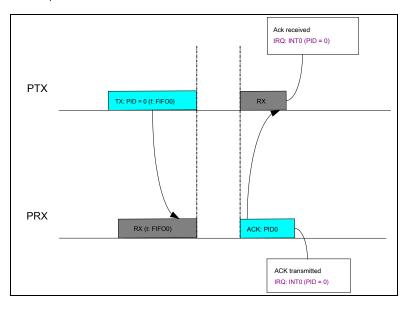

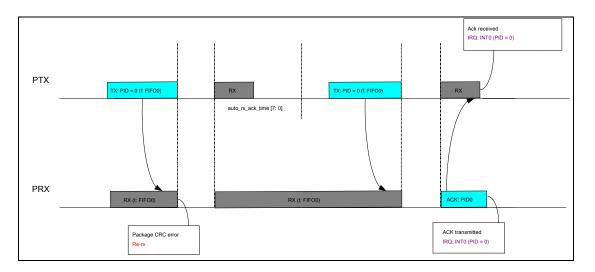

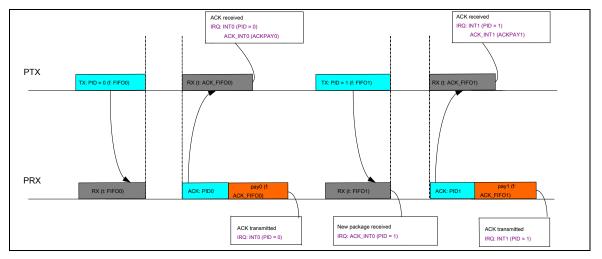

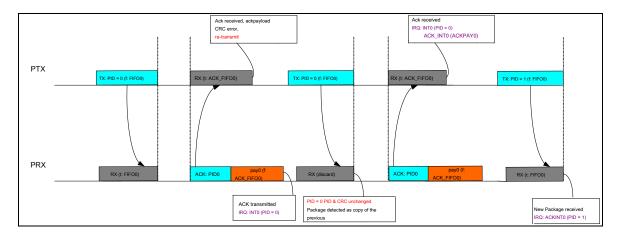

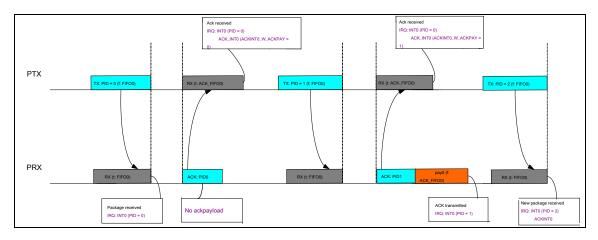

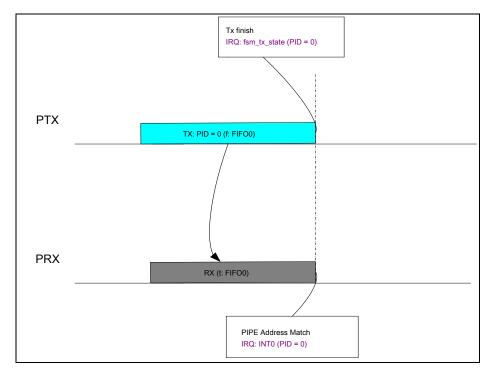

| Map 16-2 ACK Not enable interruption schematic                                                                                  | 105   |     |

|---------------------------------------------------------------------------------------------------------------------------------|-------|-----|

| Map 16-3 ACK Enable without ACK PAYLOAD Interrupt schematic                                                                     | 105   |     |

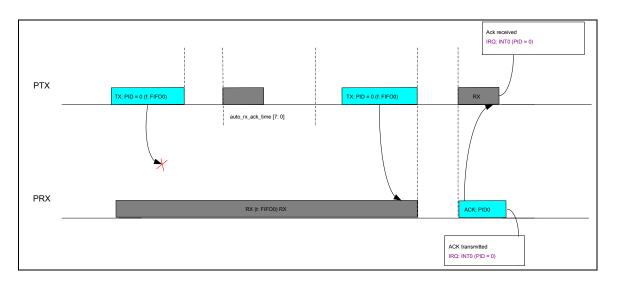

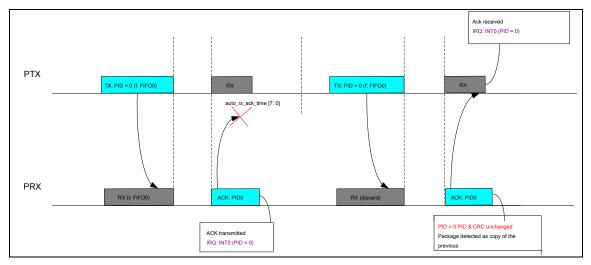

| Map 16-4 PTX Automatic retransmission situation 1 Interrupt schematic                                                           | 106   |     |

| Map 16-5 PTX Automatic retransmission situation 2 Interrupt schematic                                                           | 106   |     |

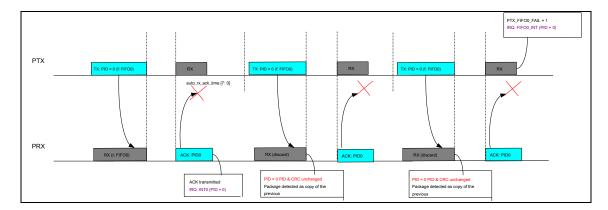

| Map 16-6 PTX Automatic retransmission situation 3 Interrupt schematic (retransmission timeout, the number of retransmissions of | ıf 2) | 107 |

| Map 16-7 PRX Automatic Re-entry interrupt schematic                                                                             | 107   |     |

| Map 16-8 ACK band ACK PAYLOAD Interruption schematic                                                                            | 108   |     |

| Map 16-9 PTX receive ACK CRC ERROR Interruption schematic                                                                       | 108   |     |

| Map 16-10 PRX No satisfy the conditions ACK PAYLOAD Send interruption schematic                                                 | 108   |     |

| Map 16-11 Illustration software interrupt link control                                                                          | . 109 |     |

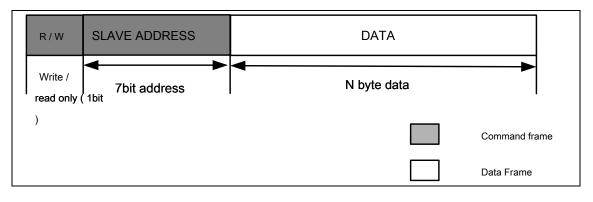

| Map 16-12 SPI Frame format                                                                                                      | . 109 |     |

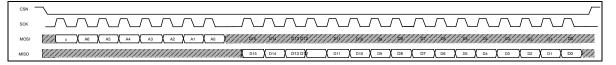

| Map 16-13 SPI Write register Timing                                                                                             | . 110 |     |

| Map 16-14 SPI Read register Timing                                                                                              | . 110 |     |

| Map 16-15 SPI write FIFO Timing                                                                                                 | . 110 |     |

| Map 16-16 SPI read FIFO Timing                                                                                                  | . 110 |     |

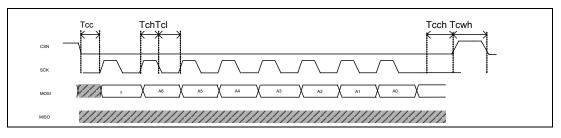

| Map 16-17 SPI Diagram of timing parameters                                                                                      | 111   |     |

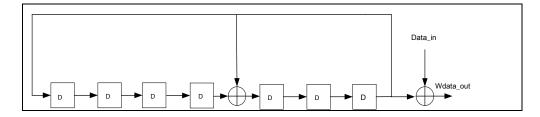

| Map 17-1 Data scrambler generator                                                                                               | 114   |     |

| Map 20-1 SOP16 FIG package size                                                                                                 | . 132 |     |

| Map 21-1 Typical Application Reference Design SCH Map                                                                           | 133   |     |

| Map 21-2 Reference design of a single panel PCB Map                                                                             | 134   |     |

| Map 21-3 Reference Design double panel PCB Map                                                                                  | . 135 |     |

|                                                                                                                                 |       |     |

## List of Tables

| table 1-1 Pin Description table                                             | 18  |

|-----------------------------------------------------------------------------|-----|

| table 1-2 Pin Description                                                   | 19  |

| table 1-3 Interconnector                                                    | 20  |

| table 1-4 MCU The extending table Description                               | 20  |

| table 1-5 Differences in the two versions of the chip pins comparison table | 20  |

| table 4-1 I / O Port weak pull                                              |     |

| table 4-2 I / O Weak Pull-Down                                              | 35  |

| table 4-3 Key interrupt                                                     | 36  |

| table 4-4 External interrupt port                                           | 36  |

| table 5-1 Crystal Oscillator capacitance parameter reference table          | 41  |

| table 5-2 Oscillation mode select switch                                    | 43  |

| table 5-3 The reset voltage point configuration table                       | 52  |

| table 5-4 Low power mode configuration table                                | 56  |

| table 5-5 Wake-up table                                                     | 57  |

| table 5-6 Wake-up schedule                                                  | 58  |

| table 6-1 T8Pn Working Mode Configuration Table                             | 61  |

| table 6-2 T8P1 / T8P2 After the divider configuration table                 | 62  |

| table 7-1 The default mode interrupt logic interrupt table                  |     |

| table 9-1 Register operation instruction table                              | 87  |

| table 9-2 Program control instructions table                                | 88  |

| table 9-3 Arithmetic / logic operation instruction list                     |     |

| table 16-1 SPI Timing Parameters                                            | 111 |

| table 18-1 Register List                                                    | 115 |

| table 18-2 PKTCTRL Register Description                                     | 116 |

| table 18-3 TRCTL Register Description                                       | 116 |

| table 18-4 CHANNR Register Description                                      | 117 |

| table 18-5 MISC0 Register Description                                       | 117 |

| table 18-6 FOCCFG Register Description                                      | 118 |

| table 18-7 FREQBASE Register Description                                    | 118 |

| table 18-8 DS_PE Register Description                                       | 118 |

| table 18-9 THRES Register Description                                       | 119 |

| table 18-10 MISC1 Register Description                                      | 119 |

| table 18-11 MISC2 Register Description                                      | 120 |

| table 18-12 PKG_RSSI Register Description                                   | 120 |

| table 18-13 CDTH Register Description                                       | 120 |

| table 18-14 RSSI Register Description                                       | 120 |

| table 18-15 STATUS0 Register Description                                    | 120 |

| table 18-16 STATUS1 Register Description                                    | 121 |

| table 18-17 FIX_LEN_EN Register Description                                 | 121 |

| table 18-18 FIFO0DATA Register Description                                  | 121 |

| table 18-19 FIFO1DATA Register Description                                  | 404 |

|                                                                             | 121 |

| table 18-20 ACKFIFO0DATA Register Description                               |     |

| table 18-22 FIFO0CTRL Register Description 12    | 23 |

|--------------------------------------------------|----|

| table 18-23 FIFO1CTRL Register Description 12    | 24 |

| table 18-24 ACKFIFO0CTRL Register Description 12 | 24 |

| table 18-25 ACKFIFO1CTRL Register Description 12 | 25 |

| table 18-26 FIFOSTATUS Register Description 12   | 26 |

| table 18-27 CLEAR Register Description 1         | 26 |

| table 18-28 PIPECTRL Register Description 12     | 27 |

| table 18-29 INT Register Description 12          | 28 |

| table 18-30 P0ADDR0 Register Description 12      | 29 |

| table 18-31 P0ADDR1 Register Description 12      | 29 |

| table 18-32 P0ADDR2 Register Description 12      | 29 |

| table 18-33 P1ADDR0 Register Description 12      | 29 |

| table 18-34 P1ADDR1 Register Description 12      | 29 |

| table 18-35 P1ADDR2 Register Description 13      | 30 |

| table 18-36 P2ADDR Register Description 13       | 30 |

| table 18-37 P3ADDR Register Description 13       | 30 |

| table 19-1 Terminology 13                        | 31 |

### The first 1 Chapter chip Introduction

## 1.1 Outline

HW2171B It is a low cost, highly integrated 2.4GHZ ISM Band wireless SOC Chip, may be applied to the radio led

Dimming, wireless HM, intelligent home, and other wireless data transmission and remote control and other fields. Integrated on-chip high-performance, low power consumption RF Transceivers and MCU.

a RF A peripheral circuit of the transceiver is simple, only few external passive components to form a complete 2.4G Wireless transceiver system.

RF Transceiver to transmit power up 8dBm , Receiver sensitivity can reach - 93dBm @ 250Kbps - 89dBm @ 1Mbps .

a MCU The low power consumption, comprising 2K Words of OTP Program memory space.

#### Chip features:

- Working conditions

- Operating voltage range: 2.1V ~ 3.6V

- range of working temperature:- 40 to 85 °C

- Package

- SOP16

#### MCU characteristic:

- Kernel

- HR7P RISC CPU Kernel

- 79 Article RISC

- Machine cycle 2 System clock cycles

- Reset vector is 000 H , Interrupt vector is located 004 H

- Support for interrupt handling, 12 Interrupt sources

- CPU Maximum operating frequency

- 2MHz (VDD = 2.1 ~ 5.5V)

- 20MHz (VDD = 3.0 ~ 5.5V)

- Storage resources

- 2K Words OTP Program memory, 8 Level program stack

- 64 Bytes SRAM Data Memory

- Direct addressing the program memory, the relative addressing and read look-up table

- Direct data memory addressing and indirect addressing support

- I / O port

- Support for up to an available port 13 One (12 More I / O with 1 Input). Wherein the external ports are available 9 One (8 More I / O with 1 Inputs)

- external PA port 6 One (PA0 ~ PA3, PA5, PA7)

- external PB port 3 One (PB0, PB1, PB5)

- Even within the port 4 One ( PA6 , PB2 ~ PB4 )

- It is not a vacant internal port (PA4)

- stand by 4 External interrupt port PINT0 ~ PINT3

- stand by 1 External key interrupt KINT Up support 8 Inputs (KIN0 ~ KIN7). Note: externally available

6 Input terminal, KIN4 with KIN6 unavailable.

- Arranged on a support independent internal weak / down input port

- At room temperature, the matching accuracy  $\pm$  3% Within ( VDD = 5V )

- It can be configured to support high-current ports

- Reset and Clock

- A reset circuit embedded POR

- The reset circuit embedded BOR

- Embedded low voltage detection interrupt circuit

- Support for external reset

- Support independent hardware watchdog timer

- stand by WDT Cycle Match Count register

- Support internal high-frequency 16MHz RC Oscillation clock source

- Frequency selection within the support section, the lowest frequency to be divided 32KHz

- Factory calibrated accuracy of ± 2% (At room temperature 25 °C)

- Support internal low 32KHz RC Oscillator source (as WDT Clock source, and may be configured as a system clock source)

- Support external oscillator

- Supports clock frequency range 32KHz ~ 20MHz

- Support system clock is switched high and low

- Peripherals

- 2 road 8 Place PWM Base Timer T8P1 / T8P2

- Timer Mode

- After the support can be configured and configurable prescaler divider

- The initial value of the counter may be arranged

- It supports up to 9 Place PWM Output Accuracy

- stand by PWM Complementary outputs and dead-time software configurable

- Support interrupt generation

- ADC ADC

- stand by 12 Bit digital conversion accuracy

- stand by 6 Analog input channels

- Support supply voltage detection, an optional power supply voltage division ratio

- Support for external reference source

- Support internal reference source (reference source VDD / 4V / 3V / 2.1V Optional)

- Support interrupt generation

- Low power consumption

- IDLE Electric current

- 3uA@5.0V , BOR / WDT Enable, 25 °C, Typical Values

- Dynamic current

- 20uA @ 32KHz , 3.0V , 25 °C, Typical Values

## - 2mA @ 16MHz , 5.0V , 25 °C, Typical Values

- Programming and debugging interface

- Support online programming ( ISP )interface

- Support programming code encryption protection

#### RF Transceiver characteristics:

•

•

- Communication Features

- The use of internationally accepted 2.4GHz ISM Working frequency 2402MHz ~ 2483MHz

- stand by GFSK Modulation

- stand by 250Kbps / 1Mbps Two data rates

- Digital support RSSI measuring

- stand by 4 PIPE Multiple logical channel transmission

- Receiver sensitivity ( 0.1% BER )

- -89dBm @ 1Mbps

- -9 3dBm @ 250Kbps

- Transmitter Output Power

- Support transmitter output power controlled manually or automatically: 40dBm ~ + 8dBm

- Power Features

- Transmitter output power 0dBm When the chip power consumption is about 23mA

- The receiver and the chip power consumption is about 20mA

- IDLE Mode current is about 1.7mA

- SLEEP Mode current is about 25uA

- POWER DOWN Mode current is about 1.5uA

- Clock circuit

- stand by 12 / 16MHz Crystal Oscillator

V1.2

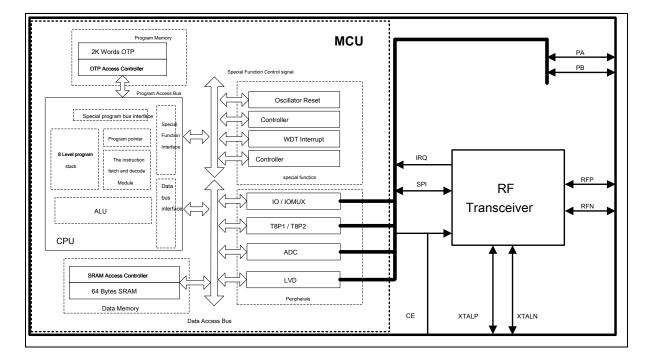

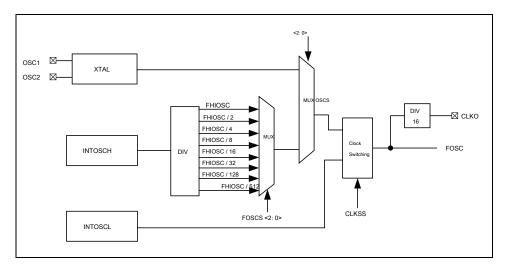

## 1.2 System Block Diagram

HW2171B The overall system diagram is shown below:

Map 1-1 System block diagram showing the internal structure

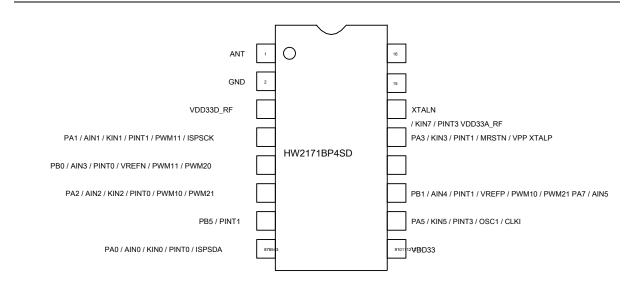

## 1.3 Pin allocation map

Map 1-2 Pin allocation map

### 1. 3.1 Pin Description

| Pin<br>Number | Pin Name                                                         | Pin Function                   | Pin Description                                                                                                         |

|---------------|------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 1             | ANT                                                              | RF end                         | RF RF transceiver end interface, external RF Matching network                                                           |

| 2             | GND                                                              | Ground                         | Ground ( 0V )                                                                                                           |

| 3             | VDD33D_RF                                                        | Digital Power Input RF D       | gital input power transceiver                                                                                           |

| 4             | PA1 / AIN1 / KIN1 / PINT1 / PWM11 / ISPSCK General Purpose Input | Output I SP Serial programmin  | g / debugging clock input, multiplexed with<br>ADC Input, external interrupt input, PWM Output, etc.                    |

| 5             | PB0 / AIN3 / PINT0 / VREFN / PWM11 / PWM20 General Purpose Input | Output General IO , Reusable   | as ADC Input, external interrupt inputs<br>In, PWM Output, etc.                                                         |

| 6             | PA2 / AIN2 / KIN2 / PINT0 / PWM10 / PWM21 General Purpose Input  | Dutput General IO , Reusable : | as ADC Input, external interrupt inputs<br>In, PWM Output, etc.                                                         |

| 7             | PB5 / PINT1                                                      | General Purpose Input Ou       | put General IO , Reusable external interrupt inputs, etc.                                                               |

| 8             | PA0 / AIN0 / KIN0 / PINT0 / ISPSDA                               | General Purpose Input Ou       | put ISP Serial programming / debugging data input and output, reusable<br>for ADC Input, external interrupt input, etc. |

| 9             | VDD33                                                            | Digital Power Input MCU        | igital power input terminal                                                                                             |

| 10            | PA5 / KIN5 / PINT3 / OSC1 / CLKI                                 | General Purpose Input Ou       | put General IO , Can be used as an external interrupt input, input externa crys<br>And so on into the                   |

| 11            | PB1 / AIN4 / PINT1 / VREFP / PWM10 / PWM21 General Purpose Input | Output General IO , Reusable   | as ADC Input, external interrupt inputs<br>In, PWM Output, etc.                                                         |

| 12            | PA7 / AIN5 / KIN7 / PINT3                                        | General Purpose Input Ou       | tput General IO Can be used for ADC Input, external interrupt input,<br>Wait                                            |

| 13            | PA3 / KIN3 / PINT1 / MRSTN / VPP                                 | Universal input Univers        | al input, the reusable external reset input, ed<br>Cheng high voltage input, an external interrupt input, etc.          |

| 14            | XTALN                                                            | Analog Output                  | RF The transceiver output of crystal oscillator                                                                         |

| Pin<br>Number | Pin Name  | Pin Function            | Pin Description                            |

|---------------|-----------|-------------------------|--------------------------------------------|

| 15            | XTALP     | Analog Input            | RF Input of transceiver crystal oscillator |

| 16            | VDD33A_RF | Analog Power Input RF A | alog input power transceiver               |

table 1-1 Pin Description table

## 1.3.2 Pin Multiplexing description

## Here are multiplexed pins Specific Multiplexing Happening:

| Pin name                              | Input Output Pin | Multiplexing Type | Type A / D |         | Port Description                  | Remark                            |

|---------------------------------------|------------------|-------------------|------------|---------|-----------------------------------|-----------------------------------|

|                                       | PA0              | TTL               | CMOS       | D       | Common I / O                      |                                   |

|                                       | AIN0             | -                 | - A        |         | ADC Analog channels 0             |                                   |

| PA0 / AIN0 / KIN0 / PINT0 /<br>ISPSDA | KIN0             | TTL               | - D        |         | External key wake-up input 0      | Weak separately<br>enabled / down |

| ISPODA                                | PINT0            | TTL               | - D        |         | External interrupt input port 0   | enabled / down                    |

|                                       | ISPSDA           | TTL               | CMOS       | D Seria | data input and output programming |                                   |

|                                       | PA1              | TTL               | CMOS       | D       | Common I / O                      |                                   |

|                                       | AIN1             | -                 | - A        |         | ADC Analog channels 1             |                                   |

| PA1 / AIN1 / KIN1 / PINT1 /           | KIN1             | TTL               | - D        |         | External key wake-up input 1      | Weak separately                   |

| PWM11 / ISPSCK                        | PINT1            | TTL               | - D        |         | External interrupt input port 1   | enabled / down                    |

|                                       | <u>PWM11</u>     | - CMOS            |            | D       | T8P1 PWM Export                   |                                   |

|                                       | ISPSCK           | TTL               | - D        |         | Serial Programming Clock input    |                                   |

|                                       | PA2              | TTL               | CMOS       | D       | Common I / O                      |                                   |

|                                       | AIN2             | -                 | - A        |         | ADC Analog channels 2             |                                   |

| PA2 / AIN2 / KIN2 / PINT0 / P         | KIN2             | TTL               | - D        |         | External key wake-up input 2      | Weak separately                   |

| WM10 / PWM21                          | PINT0            | TTL               | - D        |         | External interrupt input port 0   | enabled / down                    |

|                                       | PWM10            | - CMOS            |            | D       | T8P1 PWM Complementary Output     |                                   |

|                                       | PWM21            | - CMOS            |            | D       | T8P2 PWM Export                   |                                   |

|                                       | PA3              | TTL               | CMOS       | D       | Common I                          |                                   |

|                                       | KIN3             | TTL               | - D        |         | External key wake-up input 3      |                                   |

|                                       | PINT1            | TTL               | - D        |         | External interrupt input port 1   |                                   |

|                                       | MRSTN            | TTL               | - D        |         | Master reset input                |                                   |

| PA3 / KIN3 / PINT1 / MRSTN / VPP      | VPP              | Power             | -          | - OTP P | ogramming high voltage input      | Can be individually               |

|                                       | KIN4             | TTL               | - D        |         | External key wake-up input 4      | enabled weak pull                 |

|                                       | PINT2            | TTL               | - D        |         | External interrupt input port 2   |                                   |

|                                       | OSC2             | - CMOS            |            | А       | Crystal / resonator output        |                                   |

|                                       | CLKO             | - CMOS            |            | D       | Fosc / 16 Reference clock output  |                                   |

|                                       | PA5              | TTL               | CMOS       | D       | Common I / O                      |                                   |

|                                       | KIN5             | TTL               | - D        |         | External key wake-up input 5      |                                   |

| PA5 / KIN5 / PINT3 / OSC1 / CLKI      | PINT3            | TTL               | - D        |         | External interrupt input port 3   | Weak separately                   |

|                                       | OSC1             | TTL               | - A        |         | Crystal / resonator input         | enabled / down                    |

|                                       | CLKI             | TTL               | -          | A/D     | Clock input                       |                                   |

| Pin name                     | Input Output Pin | Multiplexing Type | Type A / D |   | Port Description                          | Remark               |

|------------------------------|------------------|-------------------|------------|---|-------------------------------------------|----------------------|

|                              | PA7              | TTL               | CMOS       | D | Common I / O                              |                      |

|                              | AIN5             | -                 | - A        |   | ADC Analog channels 5                     | Weak separately      |

| PA7 / AIN5 / KIN7 / PINT3    | KIN7             | TTL               | - D        |   | External key wake-up input 7              | enabled / down       |

|                              | PINT3            | TTL               | - D        |   | External interrupt input port 3           |                      |

|                              | PB0              | TTL               | CMOS       | D | Common I / O                              |                      |

|                              | AIN3             | -                 | - A        |   | ADC Analog channels 3                     |                      |

| PB0 / AIN3 / PINT0 / VREFN / | PINT0            | TTL               | - D        |   | External interrupt input port 0           | Weak separately      |

| PWM11 / PWM20                | VREFN            | -                 | - A        |   | ADC External negative reference voltage   | terminaalbled / down |

|                              | PWM11            | - CMOS            |            | D | T8P1 PWM Export                           |                      |

|                              | PWM20            | - CMOS            |            | D | T8P2 PWM Complementary Output             |                      |

|                              | PB1              | TTL               | CMOS       | D | Common I / O                              |                      |

|                              | AIN4             | -                 | - A        |   | ADC Analog channels 4                     |                      |

|                              | PINT1            | TTL               | - D        |   | External interrupt input port 1           |                      |

| PB1 / AIN4 / PINT1 / VREFP / | VREFP            | -                 | - A        |   | ADC External reference voltage positive t |                      |

| PWM10 / PWM21                | PWM10            | - CMOS            |            | D | T8P1 PWM Complementary Output             | enabled / down       |

|                              | PWM21            | - CMOS            |            | D | T8P2 PWM Export                           |                      |

|                              | PINT1            | TTL               | - D        |   | External interrupt input port 1           |                      |

|                              | PB5              | TTL               | CMOS       | D | Common I / O                              | Weak separately      |

| PB5 / PINT1                  | PINT1            | TTL               | - D        |   | External interrupt input port 1           | enabled / down       |

| VDD                          | VDD              | Power             | -          | - | power supply                              | -                    |

| VSS                          | VSS              | Power             | -          | - | , The 0V Reference Point                  | -                    |

table 1-2 Pin Description

Note 1 : A = simulation, D = digital; MRSTN It represents active low; Note 2 :except PA3 In addition, all common data I / O Are TTL Schmitt input and CMOS Output

drive, PA3 for TTL Input; Note 3 : T8P1 , T8P2 of PWM Output and complementary output ports can be configured to output;

V1.2

#### 1. 3.3 Interconnector

## MCU with RF Digital Transceiver Interface is a direct Internal connection, internal connection relation shown in the following table:

| No. RF trans | ceiver( I / O) | <u>MCU (I / O)</u> | Explanation                                                                                                                        |

|--------------|----------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 1            | CSN (I)        | PA6 (O)            | RF transceiver SPI The chip select input (active low), and internal MCU<br>of PA6 Connected, PA6 Should be set to the output port. |

| 2            | SCK (I)        | PB2 (O)            | RF transceiver SPI A clock input port, and an internal MCU of PB2 Connected, PB2 Should be se<br>to the output port.               |

| 3            | MOSI (I)       | PB3 (O)            | RF transceiver SPI Input port, and an internal MCU of PB3 Connected,<br>PB3 Should be set to the output port.                      |

| 4            | MISO (O)       | PB4 (I)            | RF transceiver SPI Output port, and an internal MCU of PB4 Connected,<br>PB4 Should be set to the input port.                      |

| 5            | IRQ (O)        | -                  | RF Transceiver internal interrupt output floating, so the interrupt can not be used, with the only access query.                   |

| 6            | CE (I)         | -                  | RF Transceiver chip enable input terminal, connected to the internal 3.3V Power supply terminal,<br>i.e., enabled by default.      |

table 1-3 Interconnector

## 1. 3. 4 MCU Note dangling feet

requires attention MCU Internal floating foot initial programming, the output should be set to a low level, in order to ensure the normal operation of the chip.

DESCRIPTION floating foot the following table:

| No. MCU The | extending Name Set status Sp | ecial register < bit> |         |

|-------------|------------------------------|-----------------------|---------|

| 1           | PA4                          | Output low            | PBT <4> |

table 1-4 MCU The extending table Description

### 1. 3. 5 HW2171B with HW2171 Differences pin control

HW2171B Connected to the upper portion of a pin plate HW2171 Different, need to pay attention when in use. Differences control pin given below,

## The following table Below:

| Pin name | HW2171B                                     | HW2171                                                                       |

|----------|---------------------------------------------|------------------------------------------------------------------------------|

| PA4      | Internal floating                           | External connections                                                         |

| PB5      | External connections                        | Internal floating                                                            |

| CE       | An internal power source terminal connected | The external connection may be connected GPIO Port or a power supply termina |

table 1-5 Differences in the two versions of the chip pins comparison table

## The first 2 chapter MCU - Core Features

## 2. 1 CPU Core Overview

- Core Features

- Harvard-type high-performance RISC CPU Kernel

- 79 Article RISC

- The system clock frequency of up to 20MHz

- Machine cycle 2 System clock cycles

- Support for interrupt handling, a total of 12 Interrupt sources

### twenty two The system clock cycle and machine

System clock frequency (Fosc) Up to 20MHz. Two system clock cycles to generate two quadrature clocks do not overlap within the chip by the clock generator phase1 (p1), phase2 (p2).

Two non-overlapping quadrature clock cycles one machine cycle. If the system clock frequency is 4MHz , A machine cycle time 500ns .

#### twenty three Instruction Set Overview

### use HR7P series 79 Article RISC system.

Apart from some conditional jump instructions and program flow control is bis (machine) cycle instruction, other instructions are single (machine) cycle instruction.

Specific Instruction set details, see " 9 chapter MCU- Instruction Set".

V1.2

## twenty four Special Function Register

CPU Related register comprising 11-bit Program Counter PCRL / PCRH Program status word register PSW And accumulators A register AREG. Wherein the program status register PSW For storing various status flags, including a program pop / push overflow, negative flag, overflow flag, a zero flag, Digit carry / borrow bit half and full carry or borrow bit full like.

| PSW : Program status word register |   |    |    |     |     |     |     |             |

|------------------------------------|---|----|----|-----|-----|-----|-----|-------------|

| Bit                                | 7 | 6  | 5  | 4   | 3   | 2   | 1   | 0           |

| Name                               | - | UF | OF | Ν   | OV  | Z   | DC  | С           |

| R/W                                | - | R  | R  | R/W | R/W | R/W | R/W | R/W         |

| POR                                | х | 0  | 0  | х   | х   | х   | x   | x "x" :unkn |

| Bit 7 | Reserved for future use                                     |

|-------|-------------------------------------------------------------|

| Bit 6 | UF : Program Stack Overflow flag                            |

|       | 0 : The program does not overflow the stack                 |

|       | 1 : Program Stack Overflow                                  |

| Bit 5 | OF : Program push-out flag                                  |

|       | 0 : The program does not overflow onto the stack            |

|       | 1 : Overflow program push                                   |

| Bit 4 | N : Negative flag                                           |

|       | 0 : Signed arithmetic or logic operation result is positive |

|       | 1 : The result is negative                                  |

| Bit 3 | OV : Overflow flag                                          |

|       | 0 : Signed arithmetic overflow does not occur               |

|       | 1 : Overflow                                                |

| Bit 2 | Z : Zero flag                                               |

|       | 0 : Arithmetic or logic operation result is not zero        |

|       | 1 : Result of arithmetic or logic operation is zero         |

| Bit 1 | DC : Half Carry or Borrow flag                              |

|       | 0 : Low nibble Carry or borrow from the low nibble          |

|       | 1 : Low nibble bits or lower four no borrow                 |

| Bit 0 | C : All carry or borrow bit full                            |

|       | 0 : Carry or borrow                                         |

|       | 1 : There is no carry or borrow                             |

|       |                                                             |

Note 1: Only part of the instruction PSW Write to a register, comprising JDEC, JINC, SWAP, BCC, BSS, BTT, MOVA with SETR. Other instructions PSW Write register operation, affects only the corresponding status flag according to the operation result. Note 2: OF with UF Flag bit is read, only the power-on reset, reset command, and MRSTN Reset will be cleared, reset does not affect the other two flag.

| AREG :accumulator A register |     |             |     |     |     |     |     |             |

|------------------------------|-----|-------------|-----|-----|-----|-----|-----|-------------|

| Bit                          | 7   | 6           | 5   | 4   | 3   | 2   | 1   | 0           |

| Name                         |     | AREG <7: 0> |     |     |     |     |     |             |

| R/W                          | R/W | R/W         | R/W | R/W | R/W | R/W | R/W | R/W         |

| POR                          | x   | x           | x   | х   | x   | х   | х   | x "x" :unkn |

## Bit 7 ~ 0 AREG <7: 0> : The value of the accumulator

| PCRL : Program Counter Low 8 Place |     |            |     |     |     |     |     |     |

|------------------------------------|-----|------------|-----|-----|-----|-----|-----|-----|

| Bit                                | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

| Name                               |     | PCR <7: 0> |     |     |     |     |     |     |

| R/W                                | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

| POR                                | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 0   |

Bit 7 ~ 0

PCR <7: 0> : Program Counter Low 8 Place

| PCRH : Program Counter High 3 Place |   |   |   |   |         |   |                         |     |

|-------------------------------------|---|---|---|---|---------|---|-------------------------|-----|

| Bit                                 | 7 | 6 | 5 | 4 | 3       | 2 | 1                       | 0   |

| Name                                | - | - | - | - | -       | н | P <u>CR &lt;10: 8</u> > |     |

| R/W                                 | - | - | - | - | - R / W |   | R/W                     | R/W |

| POR                                 | 0 | 0 | 0 | 0 | 0       | 0 | 0                       | 0   |

Bit 7 ~ 3

Reserved for future use

Bit 2 ~ 0 PCR <10: 8> : Program Counter High 3 Place

### The first 3 chapter MCU - Storage Resource

## 3.1 Outline

This chip bus Harvard architecture, the program address space and the data address spaces independent of each other.

Chip memory resources include:

- 2K Words OTP A program memory;

- 64 byte SRAM

among them OTP The program memory is mapped into the address space of the program, SRAM Data memory is mapped into the data address space.

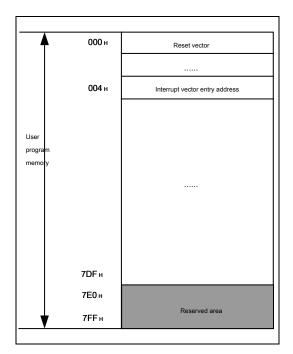

### 3.2 Program Memory

#### 3. 2.1 Outline

OTP A program memory for storing a user program. Since the bit width of the chip instruction 16 Bit (2 Bytes), thus 2K Words OTP The program memory is mapped into the address space of the program 000 H - 7FF H, among them 7E0 H - 7FF H Reserved area. Each address corresponds access 16 Bits wide (2 Bytes) of the memory cell. by 11 Bit program counter PC Procedural addressing.

Reset vector is 000 H Interrupt vector address is located 004 H ,stand by 8 Level hardware stack.

3. 2.2 Program address map schematic

#### Map 3-1 Program address map

### 3. 2.3 Program Counter ( PC )

The program counter is stored in the address of the next instruction to be executed. PC Are automatically added to each instruction cycle 1 ,unless PC Value is rewritten exception or an interrupt. 11 Bit program counter PC <10: 0> No actual physical address, can not be read, addressable 2K Program memory space 000 H- 7FF H Beyond the address range can cause PC Cycle (and from 000 H Began a visit). PC <7: 0> accessible PCRL Register read / write operation for reading / writing, and PC <10: 8> by PCRH Register indirect (e.g. RCALL, CALL, GOTO And other instructions) assignment.

When the chip is reset, PCRL, PCRH with PC It will be cleared. PC Hardware stack operation does not affect PCRH Value.

Note: all kinds of instructions PC Impact:

Eastsoft essemi

1. Modified by direct instruction PC When the value of PCRL Is the destination, the operation can be directly modified PC <7: 0> , which is PC <7: 0> = PCRL <7: 0> ;

The operation PC <7: 0> But also the implementation of PC <10: 8> = PCRH <2: 0> Therefore, modifications PC When, should be modified PCRH <2: 0>, And then modify PCRL <7: 0>.

2. carried out RCALL Instruction, PC <7: 0> To register R The value; and PC <10: 8> = PCRH <2: 0> .

3. carried out CALL, GOTO Instruction, PC <10: 0> For the instruction 11 Bit immediate I (Operand).

4. carried out LCALL When the instruction, which is a two-word instructions Total 16 Bit immediate I (Operand). PC <10: 0> Modified to the 16 Bit immediate I

Low value 11 Bit; at the same time PCRH <2: 0> It is modified I <10: 8> Value.

5. carried out AJMP When the instruction, which is a two-word instructions Total 16 Bit immediate I (Operand). PC <10: 0> Modified to the 16 Bit immediate I

Low value 11 Bits, while PCRH <2: 0> change into I <10: 8> Value.

6. carried out PAGE Instruction, PCRH <7: 3> The value is the number of the instruction immediately I replace. (The size of this chip program memory is 2K Words,

therefore PCRH <7: 3> Is fixed to all zeros, execute PAGE After instruction PC Values are not affected)

7. The implementation of other instructions, PC Automatic value 1 .

### Application examples: The PCRL Instructions for the application target register

..... MOVI

|      | pageaddr  |                                      |

|------|-----------|--------------------------------------|

| MOVA | PCRH      | ; Set the table page address         |

| MOVI | tableaddr | ; Offset is set to A register        |

| CALL | TABLE     | ; Subroutine call mode look-up table |

|      |           |                                      |

## TABLE:

| ADD   | PCRL, F | ; PC Plus the offset, the address of the access point |

|-------|---------|-------------------------------------------------------|

| RETIA | 0X01    |                                                       |

| RETIA | 0X02    |                                                       |

| RETIA | 0X03    |                                                       |

|       |         |                                                       |

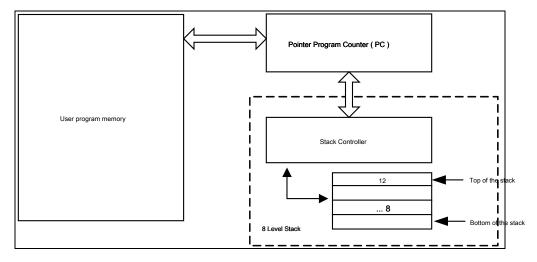

#### 3. 2.4 Program stack

There chip 8 Level program stack (hardware stack), and the stack bit wide PC Equal bits wide, for PC The push and pop. carried out CALL, LCALL with RCALL After interruption of instructions or in response, PC Automatically pushed onto the stack; when performed RET,

RETIA or RETIE Instruction, the stack will push the value of a recent return to PC .

Program stack only supports 8 Level buffer operation, that only saves the last program stack 8 PUSH value, for continuously for more than 8 Second push operation, the first 9 Data so that the first push times 1 Times push data loss. Similarly, more than 8 Times in a row out of the stack, the first 9 Ci pop operations, so that the program flow may be uncontrollable. After reset, the stack pointer points to the top of the stack again.

### Map 3-2 Stack schematic

### 3. 3 IAP access OTP operating

### 3. 3. 1 OTP Memory

OTP The memory is a programmable memory, in VPP Multiplexing application of high pressure port 8.45V When, by IAP For unprogrammed off OTP Address unit control programming software. IAP Word write operation ( Word ) As a unit, by FRA

(FRAH, FRAL) Addressing. when OTP Memory IAP When a write operation CPU Core suspended, the software needs to close the global interrupt enable bit GIE (INTG <7>), And judges GIE Whether the register is cleared successfully, if not cleared, you need software to perform clear operation again until cleared successfully, peripherals can be preset state to continue running, peripheral interrupt request will set the corresponding interrupt flag. when IAP When the writing operation is completed, CPU Core resumes execution, the software then enables the global interrupt enable bit GIE, The corresponding interrupt handling.

#### 3. 3.2 Table read instruction

HR7P 79 Instruction set includes 8 Article table read instructions.

Look-up table read instructions:

Table look-up read command for FRA ( FRAH , FRAL ) Pointed OTP A cell address word ( Word ) Read ROMD ( ROMDH , ROMDL )in.

- TBR

- TBR # 1

- TBR\_1

- TBR1 #

Look-up table write instructions: This chip look-up table write instruction reserved for future use.

- TBW

- TBW # 1

- TBW\_1

- TBW1 #

The specific operation may refer to the table read instruction "on 9 chapter MCU- Instruction Set"

## 3. 3. 3 IAP program

IAP By programming operation IAPC Control register ROMD (ROMDH, ROMDL Content) is written FRA

(FRAH, FRAL) Points OTP Address unit. IAP Programmatic access to address space 200 H- 7DF H. Recommends that each address programming is complete,

look-up table read verification is successful, if unsuccessful needs to return to the program operation until the read verification is successful then the

follow-up program address space. Single address programming, programming for at least 2ms .

| Application routin  | es 1 : IAP program       |                                                              |

|---------------------|--------------------------|--------------------------------------------------------------|

| MOVI                | 0x02                     | ;will 55AAH Write OTP of 0210 H Address unit                 |

| MOVA                | FRAH                     |                                                              |

| MOVI                | 0x10                     |                                                              |

| MOVA                | FRAL                     |                                                              |

| MOVI                | 0xAA                     |                                                              |

| MOVA                | ROMDL                    |                                                              |

| MOVI                | 0x55                     |                                                              |

| MOVA                | ROMDH                    |                                                              |

| BCC                 | INTG, GIE                | ; Close the global interrupt                                 |

| JBC                 | INTG, GIE                | ; Determine whether the global interrupt cleared             |

| GOTO                | \$ -2                    |                                                              |

| BSS                 | IAPC, IAPEN              | ;Enable IAP operating                                        |

| BSS                 | IAPC, IAPGO              | ;trigger IAP operating                                       |

| WAIT:               |                          |                                                              |

| JBC                 | IAPC, IAPGO              |                                                              |

| GOTO WAI            | T BSS                    |                                                              |

|                     | INTG, GIE                | ; Open global interrupt                                      |

|                     |                          |                                                              |

| lication routines 2 | : IAP Read look-up table |                                                              |

| MOVI                | 0x02                     | ; Read a data memory 0210 н unit                             |

| MOVA                | FRAH                     |                                                              |

| MOVI                | 0X10                     |                                                              |

| MOVA                | FRAL                     |                                                              |

| TBR                 |                          | ; Table look-up read command to read data ROMDH / L register |

| MOV                 | ROMDH, 0                 |                                                              |

| MOV                 |                          |                                                              |

|                     | ROMDL, 0                 |                                                              |

|                     |                          |                                                              |

... 3. 3.4 Special Function Register

FRAL : Low lookup table address register 8 Place 2 Bit 6 Name FRA <7: 0> R/W R/W R/W R/W R/W R/W R/W R/W R/W POR х х х х х х х

V1.2

0

х

27/145

" x ":unknown

# Bit 7 ~ 0 FRA <7: 0> : Low address look-up table 8 Place

| FRAH : Look-up table address register high 8 Place |     |                             |   |   |   |   |   |     |  |

|----------------------------------------------------|-----|-----------------------------|---|---|---|---|---|-----|--|

| Bit                                                | 7   | 7 6 5 4 3 2 1 0             |   |   |   |   |   |     |  |

| Name                                               |     | FRA <15: 8>                 |   |   |   |   |   |     |  |

| R/W                                                | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   | R/W |  |

| POR                                                | х   | х                           | х | х | х | х | х | x   |  |

" x ":unknown

## Bit 7 ~ 0 FRA <15: 8> : High Address look-up table 8 Place

| ROMDL : Low lookup data register 8 Place |             |     |     |     |     |     |     |     |  |  |

|------------------------------------------|-------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| Bit                                      | 7           | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

| Name                                     | ROMD <7: 0> |     |     |     |     |     |     |     |  |  |

| R/W                                      | R/W         | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| POR                                      | x           | х   | х   | х   | х   | x   | х   | x   |  |  |

" x ":unknown

## Bit 7 ~ 0 ROMD <7: 0> : Low data look-up table 8 Place

| ROMDH : High lookup data register 8 Place |     |                             |   |   |   |   |   |     |  |

|-------------------------------------------|-----|-----------------------------|---|---|---|---|---|-----|--|