# Vitis Unified Software Platform Documentation

# **Application Acceleration Development**

UG1393 (v2019.2) February 28, 2020

# **Revision History**

The following table shows the revision history for this document.

| Section                                                                                                                                                                                                                                           | Revision Summary                                                                                                                                                                                                   |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 02/27/2020 V                                                                                                                                                                                                                                      | ersion 2019.2                                                                                                                                                                                                      |  |

| Update to 2019.2 documentation                                                                                                                                                                                                                    | Removed the Data Center Accelerator Card Platforms chapter. For specifications of each accelerator card and available target platforms, refer to Alveo Data Center Accelerator Card Platforms User Guide (UG1120). |  |

| 12/19/2019 Version 2019.2                                                                                                                                                                                                                         |                                                                                                                                                                                                                    |  |

| Update to 2019.2 documentation                                                                                                                                                                                                                    | Profile_Summary report additions and content update xbutil status update xbutil flash deprecation message Updates to support the following Alveo™ accelerator cards:  U50 U200 and U25 QDMA                        |  |

| 11/11/2019 Version 2019.2                                                                                                                                                                                                                         |                                                                                                                                                                                                                    |  |

| Vitis 2019.2 Software Platform Release Notes                                                                                                                                                                                                      | Updated content.                                                                                                                                                                                                   |  |

| Vitis Software Platform Installation                                                                                                                                                                                                              | Updated content.<br>Removed licensing information.                                                                                                                                                                 |  |

| 10/30/2019 V                                                                                                                                                                                                                                      | ersion 2019.2                                                                                                                                                                                                      |  |

| Entire document                                                                                                                                                                                                                                   | Updated for public release with additional content and updated figures.                                                                                                                                            |  |

| <ul> <li>Vitis 2019.2 Software Platform Release Notes</li> <li>xbmgmt Utility</li> <li>Understanding the Vitis Analyzer</li> <li>Data Center Accelerator Card Platforms</li> <li>Section VIII: Embedded Processor Platform Development</li> </ul> | Added new chapters.                                                                                                                                                                                                |  |

| Section IX: Migrating Embedded Processor Applications from SDSoC to Vitis                                                                                                                                                                         |                                                                                                                                                                                                                    |  |

| 10/01/2019 Version 2019.2                                                                                                                                                                                                                         |                                                                                                                                                                                                                    |  |

| Initial release                                                                                                                                                                                                                                   | N/A                                                                                                                                                                                                                |  |

# **Table of Contents**

| evision History                                                |     |

|----------------------------------------------------------------|-----|

| Section I: Introduction to the Vitis Unified Software Platform | 112 |

| Chapter 1: Vitis 2019.2 Software Platform Release Notes        | 13  |

| What's in the Vitis Software Platform                          | 13  |

| Supported Platforms                                            | 14  |

| Changed Behavior                                               | 14  |

| Known Issues                                                   | 15  |

| Chapter 2: Installation                                        | 16  |

| Installation Requirements                                      |     |

| Vitis Software Platform Installation                           | 18  |

| Chapter 3: Introduction to the Vitis Environment for           |     |

| Acceleration                                                   | 23  |

| Introduction and Overview                                      | 23  |

| Execution Model                                                | 25  |

| Build Process                                                  | 27  |

| Tutorials and Examples                                         | 29  |

| Chapter 4: Methodology for Accelerating Applications with      | 1   |

| the Vitis Software Platform                                    | 31  |

| Introduction                                                   | 31  |

| Methodology for Architecting a Device Accelerated Application  |     |

| Methodology for Developing C/C++ Kernels                       | 47  |

| Section II: Developing Applications                            | 61  |

| Chapter 5: Programming Model                                   | 62  |

| Device Topology                                                | 62  |

| Kernel Properties                                              | 62  |

| Chapter 6: Host Application                            | 66  |

|--------------------------------------------------------|-----|

| Setting Up the OpenCL Environment                      | 66  |

| Executing Commands in the FPGA                         | 71  |

| Post- Processing and FPGA Cleanup                      | 82  |

| Summary                                                | 82  |

| Chapter 7: C/C++ Kernels                               | 84  |

| Data Types                                             |     |

| Interfaces                                             |     |

| Loops                                                  | 90  |

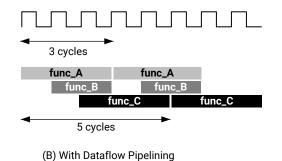

| Dataflow Optimization                                  | 96  |

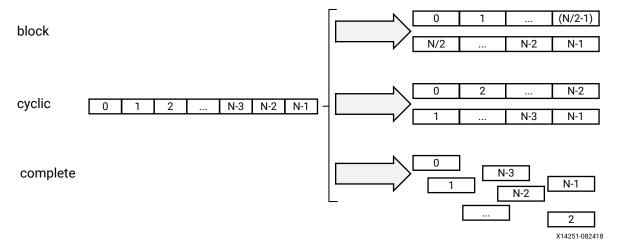

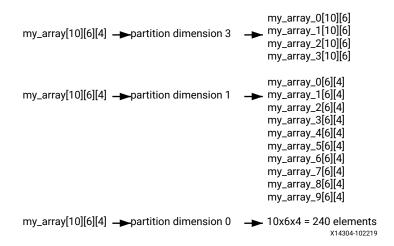

| Array Configuration                                    | 99  |

| Function Inlining                                      | 103 |

| Summary                                                | 103 |

| Chapter 8: RTL Kernels                                 | 105 |

| Requirements of an RTL Kernel                          | 105 |

| RTL Kernel Development Flow                            | 108 |

| RTL Kernel Wizard                                      | 114 |

| Design Recommendations for RTL Kernels                 | 131 |

| Chapter 9: Streaming Connections                       | 136 |

| Streaming Data Between the Host and Kernel (H2K)       | 136 |

| Streaming Data Transfers Between Kernels (K2K)         | 141 |

| Free-running Kernel                                    | 143 |

| Chapter 10: OpenCL Kernels                             | 145 |

| Chapter 11: Best Practices for Acceleration with Vitis | 147 |

| Section III: Building and Running the Application      | 149 |

| Chapter 12: Setting up the Vitis Environment           | 150 |

| Chapter 13: Build Targets                              | 151 |

| Software Emulation                                     |     |

| Hardware Emulation                                     |     |

| System Hardware Target                                 |     |

| Chapter 14: Building the Host Program            |                     |

|--------------------------------------------------|---------------------|

| Compiling and Linking for x86                    | 154                 |

| Compiling and Linking for Arm                    | 155                 |

| Chapter 15: Building the FPGA Binary             | 157                 |

| Compiling Kernels with Vitis Compiler            |                     |

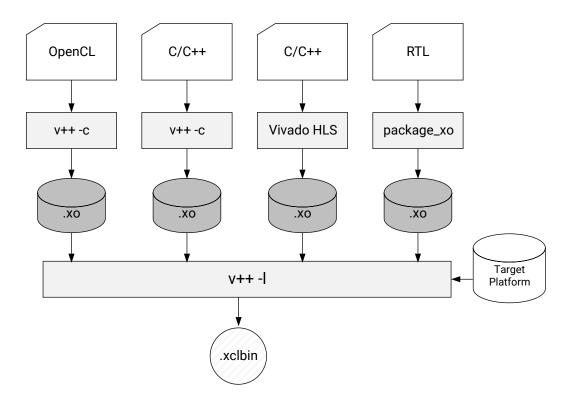

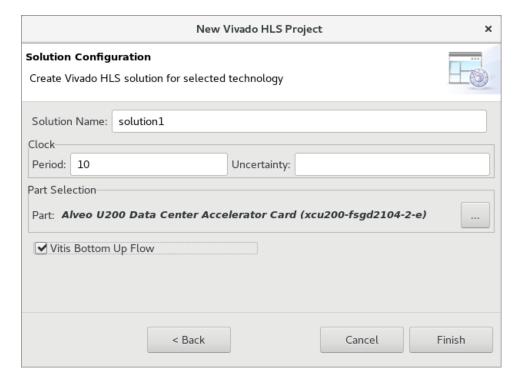

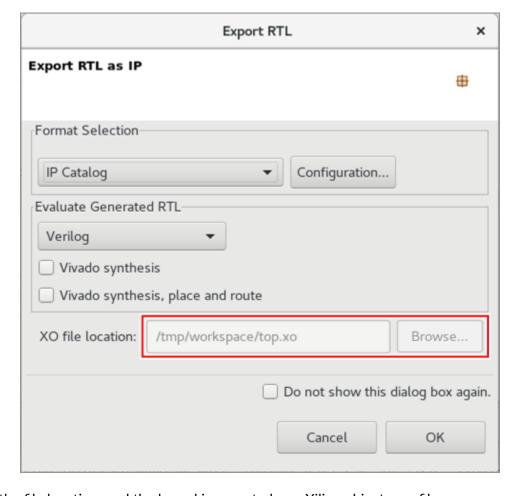

| Compiling Kernels Directly in Vivado HLS         | 159                 |

| Packaging RTL Kernels with package_xo            | 163                 |

| Linking the Kernels                              | 164                 |

| Controlling Report Generation                    | 174                 |

| Chapter 16: Directory Structure                  | 176                 |

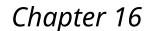

| Output Directories from the v++ Command          | 176                 |

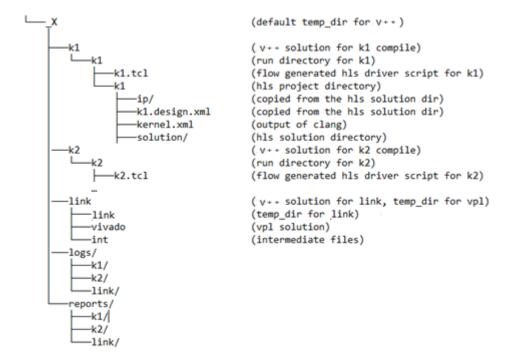

| Output Directories from the Vitis IDE            | 177                 |

| Chapter 17: Running an Application               | 179                 |

| Section IV: Profiling, Optimizing, and Debugging | the Application 182 |

| Chapter 18: Profiling the Application            | 183                 |

| Baselining Functionalities and Performance       | 184                 |

| Design Guidance                                  | 186                 |

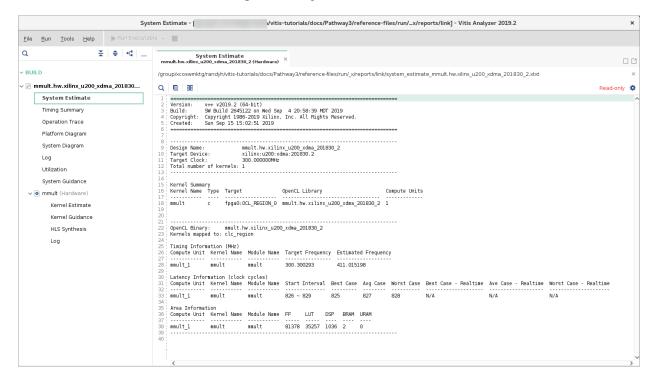

| System Estimate Report                           |                     |

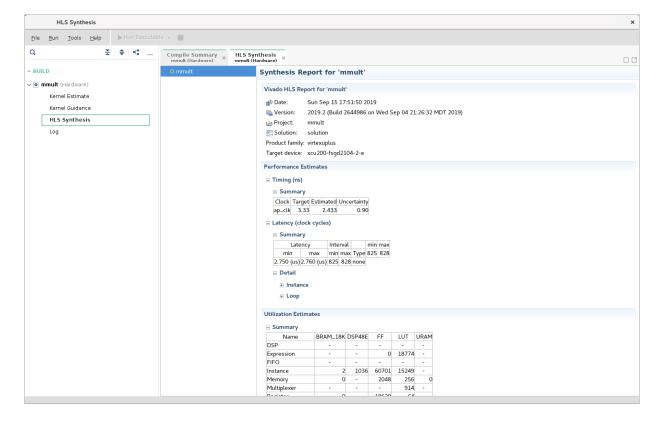

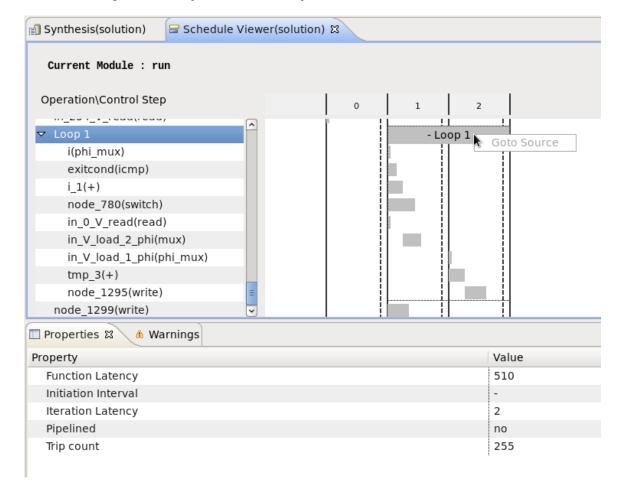

| HLS Report                                       |                     |

| Profile Summary Report                           |                     |

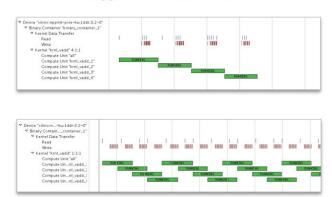

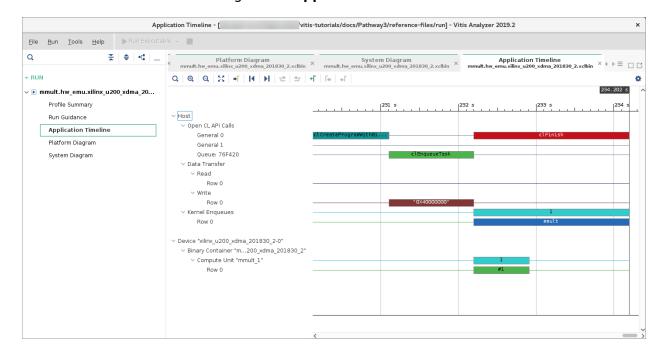

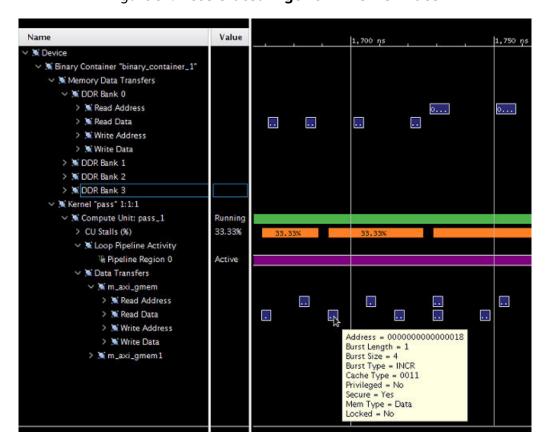

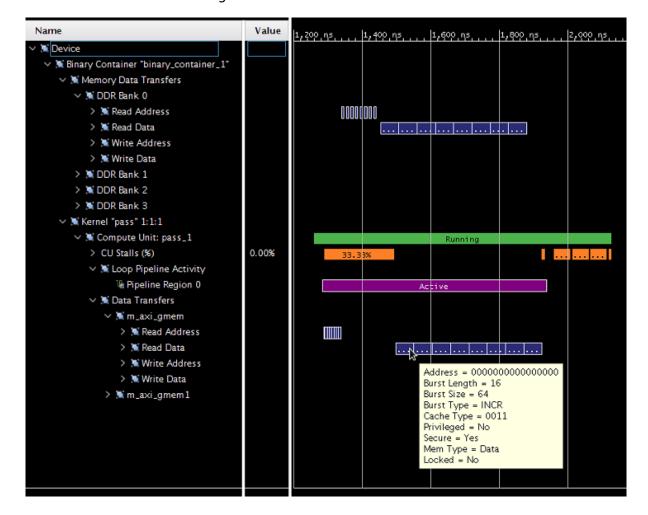

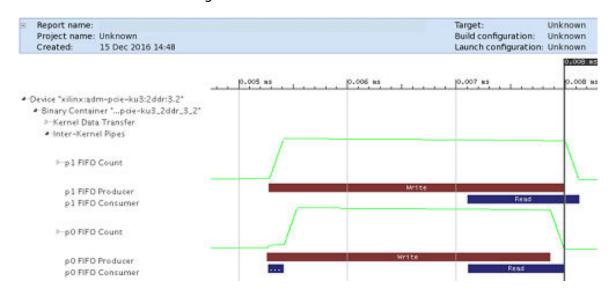

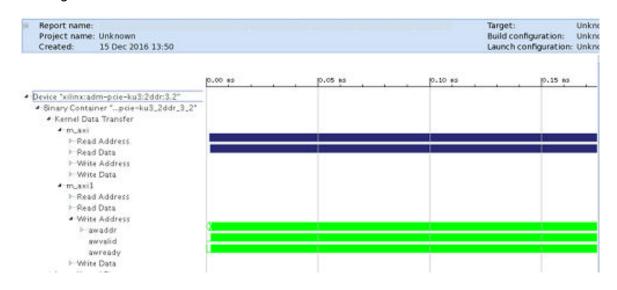

| Application Timeline                             |                     |

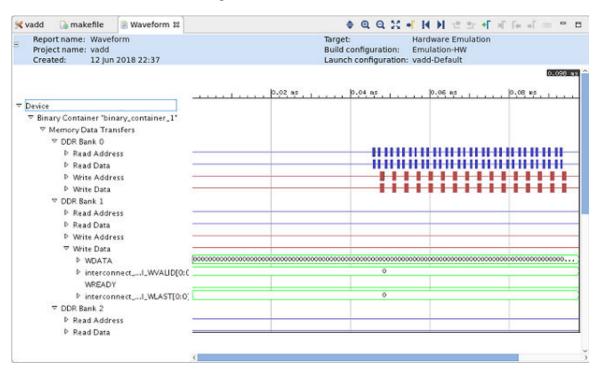

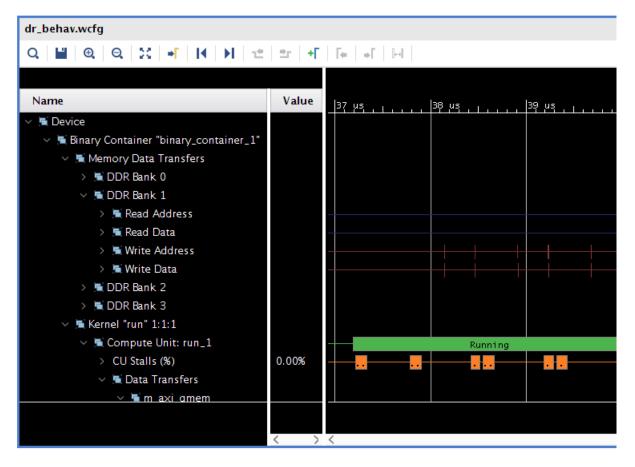

| Waveform View and Live Waveform Viewer           | 207                 |

| Chapter 19: Optimizing the Performance           | 213                 |

| Host Optimization                                | 213                 |

| Kernel Optimization                              | 222                 |

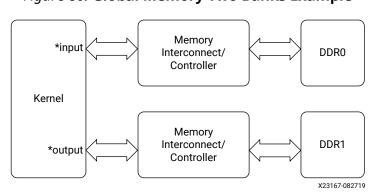

| Topological Optimization                         | 257                 |

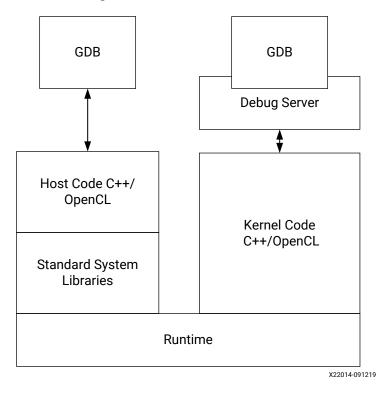

| Chapter 20: Debugging Applications and Kernel    | S262                |

| Debugging Flows                                  | 262                 |

| Debugging in Software Emulation                  | 263                 |

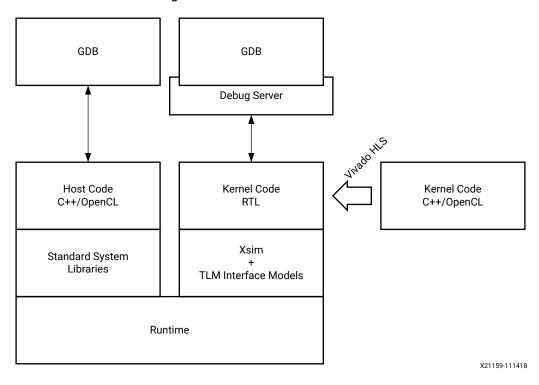

| Debugging in Hardware Emulation                  | 271                 |

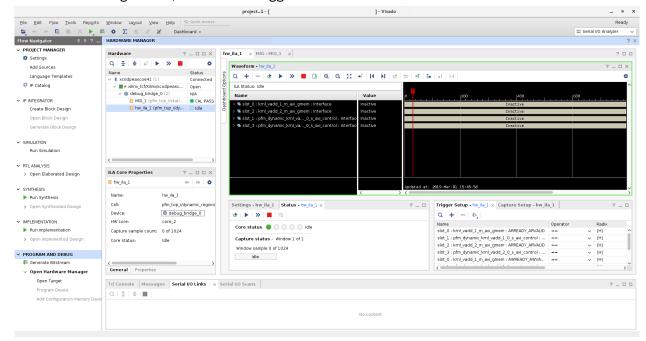

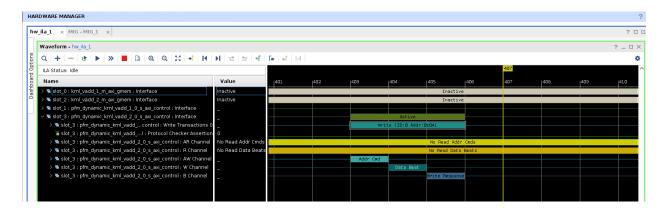

| Debugging During Hardware Execution              | 275                 |

| Example of Command Line Debugging                | 298 |

|--------------------------------------------------|-----|

| Section V: Vitis Environment Reference Materials | 301 |

| Chapter 21: Vitis Compiler Command               | 303 |

| Vitis Compiler General Options                   |     |

| advanced Options                                 |     |

| clock Options                                    | 321 |

| connectivity Options                             | 323 |

| hls Options                                      | 326 |

| vivado Options                                   | 329 |

| Vitis Compiler Configuration File                | 330 |

| Using the Message Rule File                      | 332 |

| Chapter 22: xrt.ini File                         | 334 |

| Chapter 23: platforminfo Utility                 | 338 |

| Basic Platform Information                       |     |

| Hardware Platform Information                    | 340 |

| Interface Information                            | 340 |

| Clock Information                                | 340 |

| Valid SLRs                                       | 341 |

| Resource Availability                            | 341 |

| Memory Information                               | 341 |

| Feature ROM Information                          | 343 |

| Software Platform Information                    | 343 |

| Chapter 24: kernelinfo Utility                   | 344 |

| Kernel Definition                                | 345 |

| Arguments                                        | 345 |

| Ports                                            | 346 |

| Chapter 25: emconfigutil Utility                 | 347 |

| Chapter 26: xclbinutil Utility                   | 349 |

| xclbin Information                               |     |

| Hardware Platform Information                    |     |

| Clocks                                           |     |

| Memory Configuration                             | 351 |

| Kernel Information              | 352 |

|---------------------------------|-----|

| Tool Generation Information     | 353 |

| Chapter 27: xbutil Utility      | 355 |

| clock                           |     |

| dmatest                         |     |

| dump                            |     |

| flash (xbutil)                  |     |

| flash scan                      |     |

| list                            |     |

| m2m                             | 365 |

| mem read                        | 365 |

| mem write                       | 366 |

| p2p                             | 366 |

| program                         | 367 |

| query                           | 367 |

| reset                           | 370 |

| scan                            | 370 |

| status                          | 371 |

| top                             | 373 |

| validate                        | 374 |

| Chapter 28: xbmgmt Utility      | 376 |

| flash (xbmgmt)                  | 376 |

| scan (xbmgmt)                   | 378 |

| version                         | 378 |

| Chapter 29: package_xo Command  | 379 |

| Chapter 30: HLS Pragmas         | 381 |

| pragma HLS allocation           |     |

| pragma HLS array_map            |     |

| pragma HLS array_partition      |     |

| pragma HLS array_reshape        |     |

| pragma HLS data_pack            |     |

| pragma HLS dataflow             | 394 |

| pragma HLS dependence           | 396 |

| pragma HLS expression_balance   | 399 |

| pragma HLS function_instantiate | 400 |

| pragma HLS inline                            | 401 |

|----------------------------------------------|-----|

| pragma HLS interface                         | 404 |

| pragma HLS latency                           | 410 |

| pragma HLS loop_flatten                      | 412 |

| pragma HLS loop_merge                        | 414 |

| pragma HLS loop_tripcount                    | 416 |

| pragma HLS occurrence                        | 417 |

| pragma HLS pipeline                          | 418 |

| pragma HLS reset                             | 420 |

| pragma HLS resource                          | 421 |

| pragma HLS stream                            | 423 |

| pragma HLS top                               | 425 |

| pragma HLS unroll                            | 426 |

| Chapter 31: OpenCL Attributes                | 429 |

| always_inline                                | 430 |

| opencl_unroll_hint                           | 431 |

| reqd_work_group_size                         | 432 |

| vec_type_hint                                | 434 |

| work_group_size_hint                         | 435 |

| xcl_array_partition                          | 436 |

| xcl_array_reshape                            | 439 |

| xcl_dataflow                                 | 442 |

| xcl_latency                                  | 443 |

| xcl_loop_tripcount                           | 444 |

| xcl_max_work_group_size                      | 446 |

| xcl_pipeline_loop                            | 447 |

| xcl_pipeline_workitems                       | 448 |

| xcl_reqd_pipe_depth                          | 449 |

| xcl_zero_global_work_offset                  | 451 |

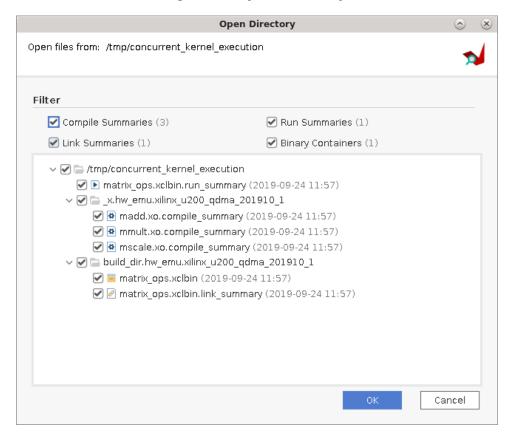

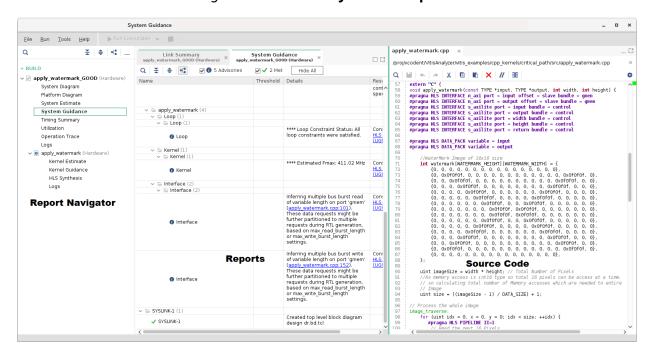

| Section VI: Using the Vitis Analyzer         | 453 |

| Chapter 32: Working with Reports             | 455 |

| Chapter 33: Understanding the Vitis Analyzer | 457 |

|                                              |     |

| Chapter 34: Creating a Run Configuration     | 459 |

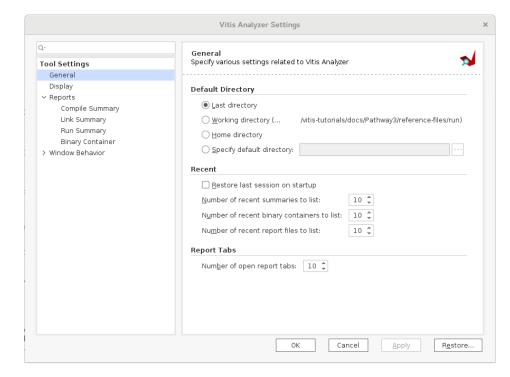

| Chapter 35: Configuring the Vitis Analyzer          | 461    |

|-----------------------------------------------------|--------|

| Section VII: Using the Vitis IDE                    | 463    |

| Chapter 36: Vitis Command Options                   | 464    |

| Chapter 37: Creating a Vitis IDE Project            | 465    |

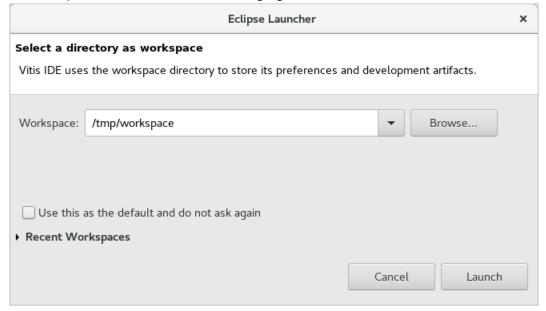

| Launch a Vitis IDE Workspace                        | 465    |

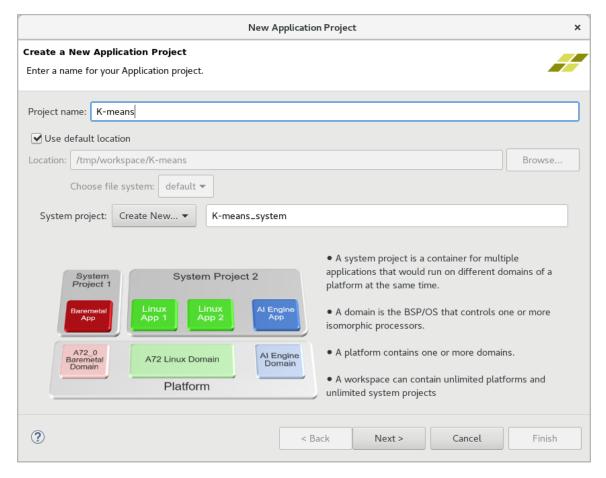

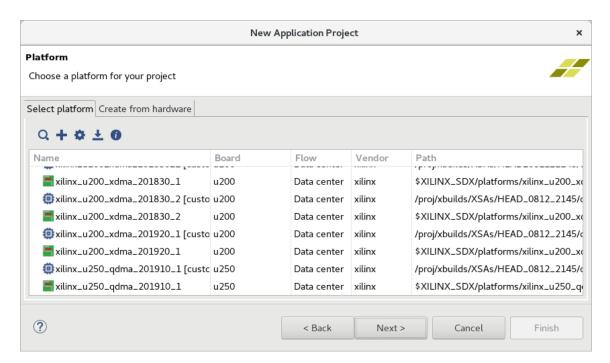

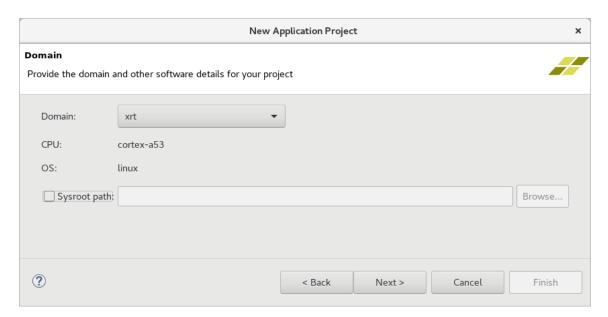

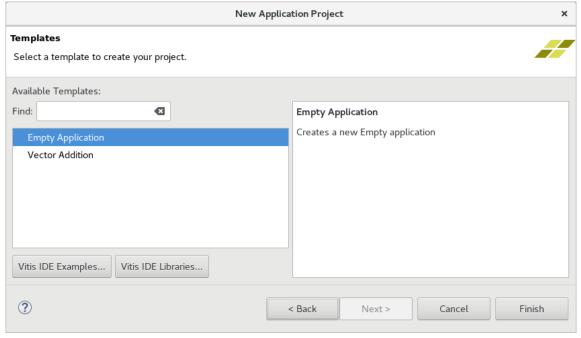

| Create an Application Project                       | 466    |

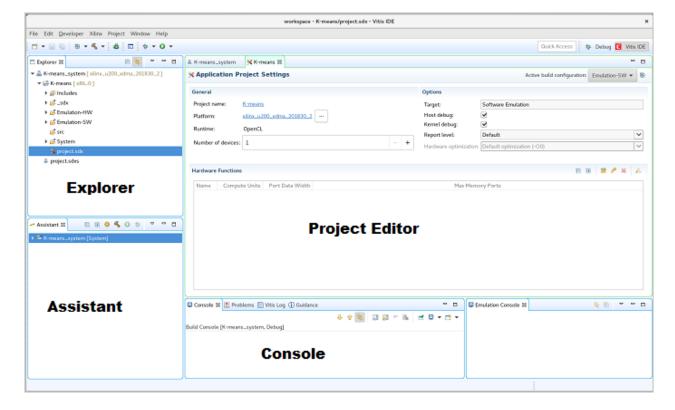

| Understanding the Vitis IDE                         | 470    |

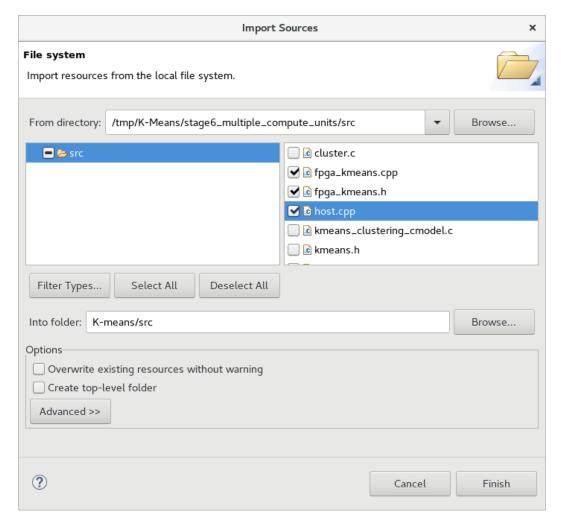

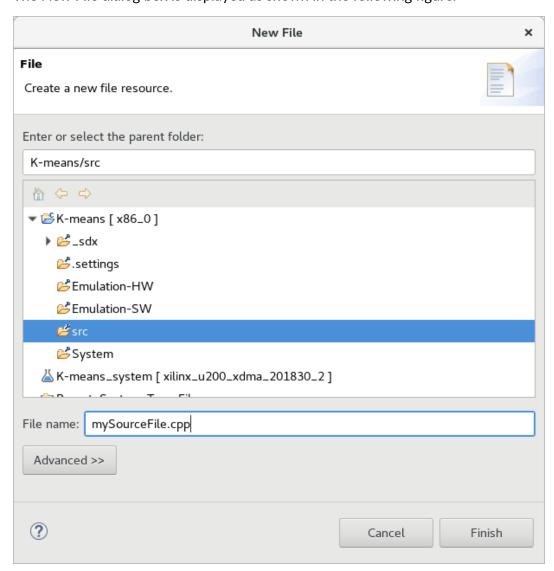

| Adding Sources                                      | 472    |

| Working in the Project Editor View                  |        |

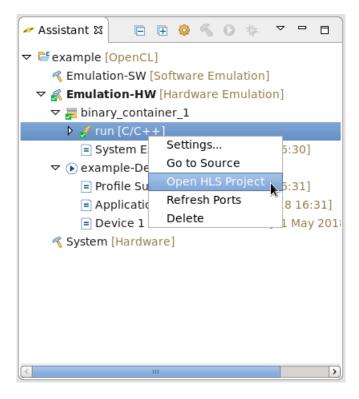

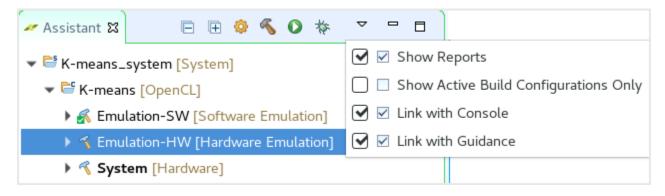

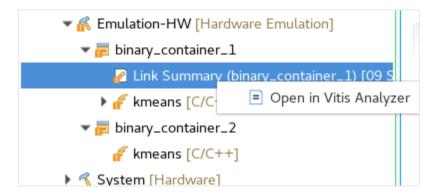

| Working in the Assistant View                       | 476    |

| Chapter 38: Building the System                     | 479    |

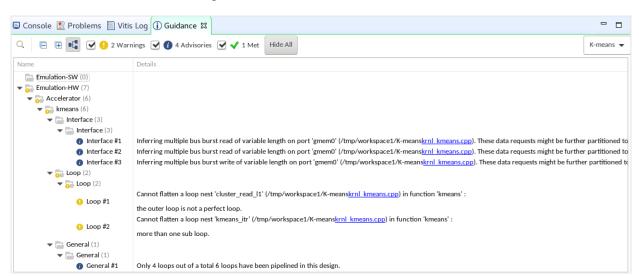

| Vitis IDE Guidance View                             | 480    |

| Working with Vivado Tools from the Vitis IDE        |        |

| Chapter 39: Vitis IDE Debug Flow                    | 483    |

| Chapter 40: Configuring the Vitis IDE               | 485    |

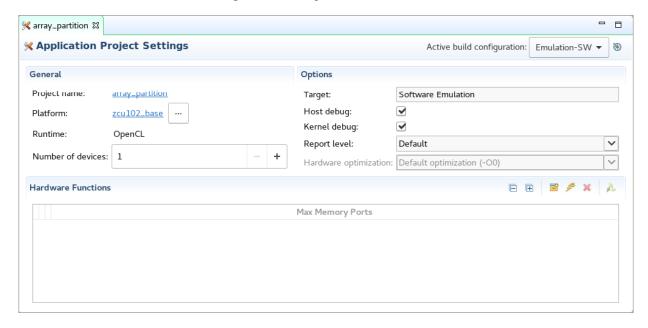

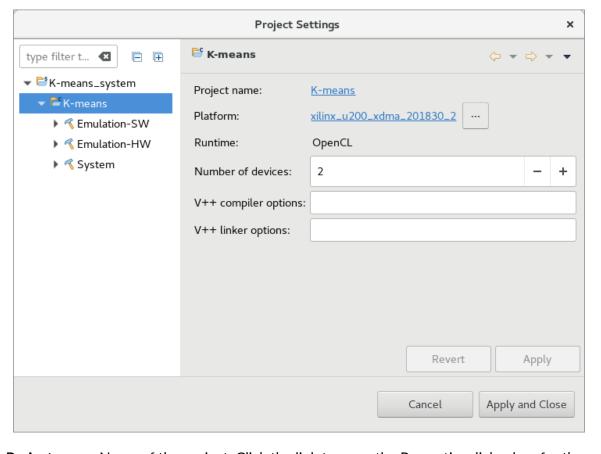

| Vitis Project Settings                              | 485    |

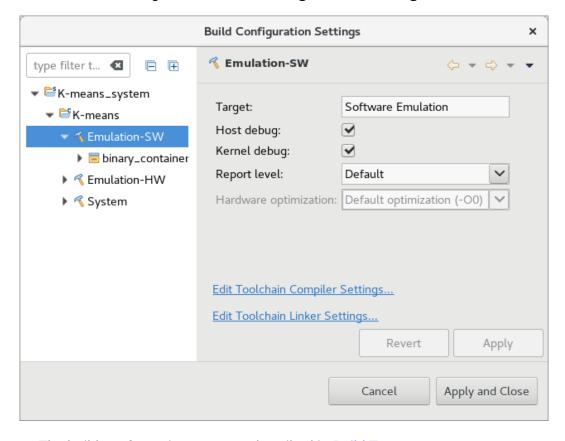

| Vitis Build Configuration Settings                  |        |

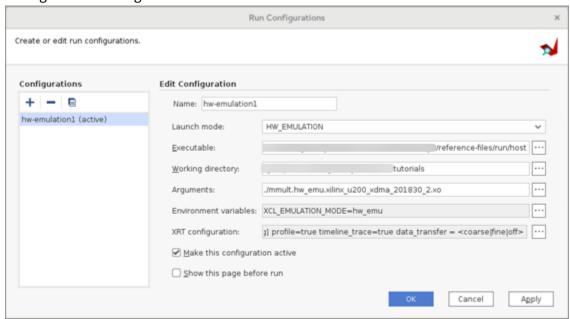

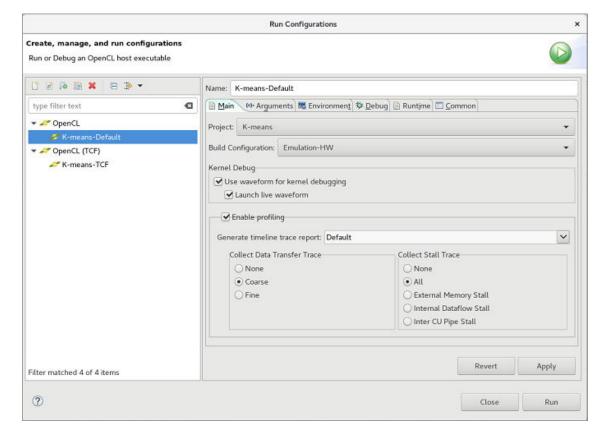

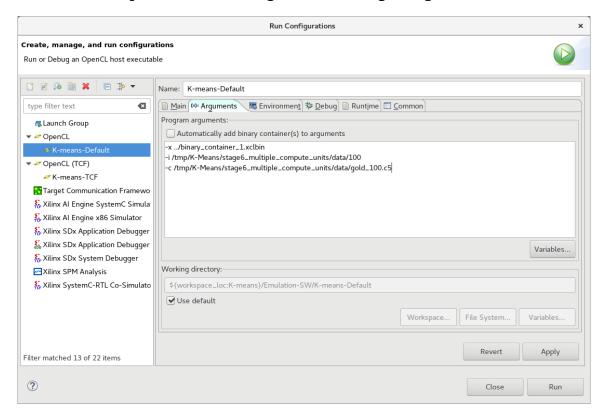

| Vitis Run Configuration Settings                    | 488    |

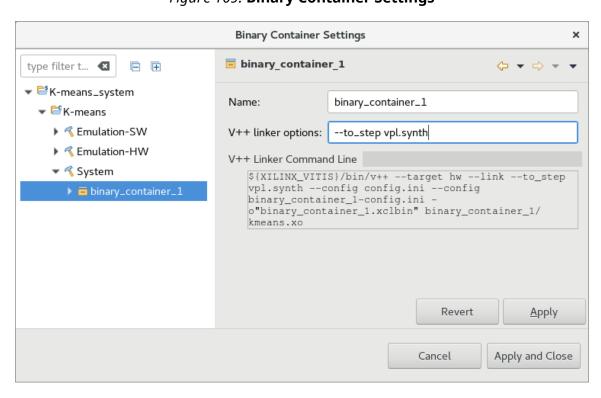

| Vitis Binary Container Settings                     | 491    |

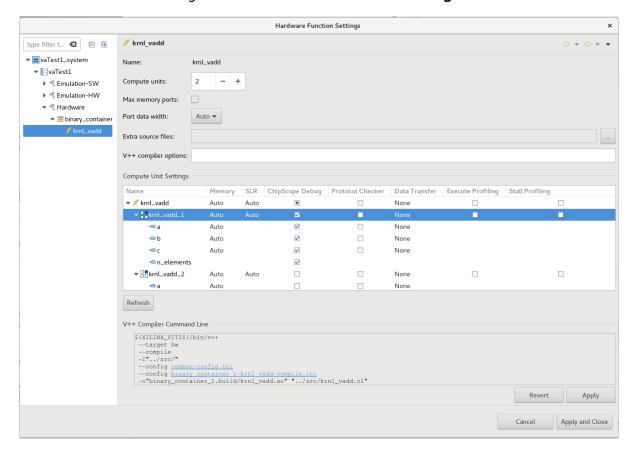

| Vitis Hardware Function Settings                    | 492    |

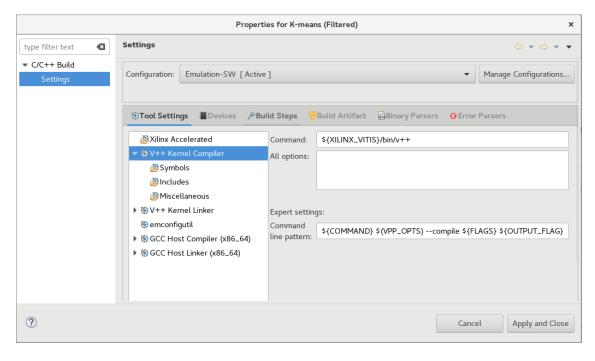

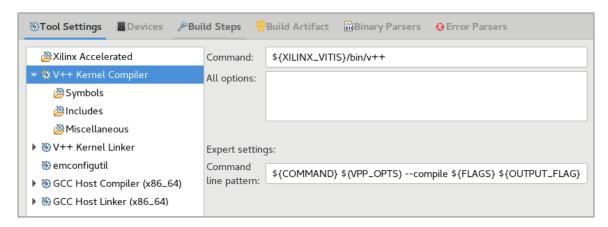

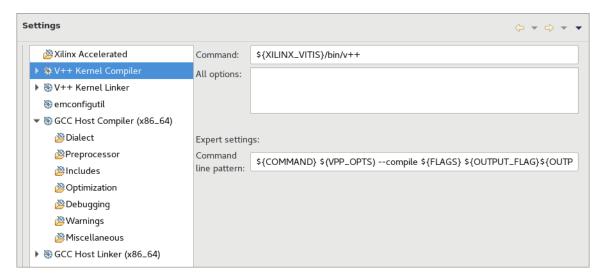

| Vitis Toolchain Settings                            | 493    |

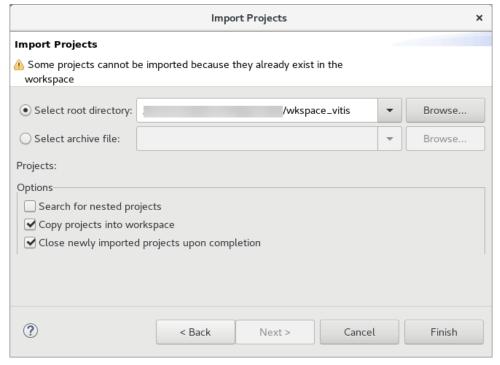

| Chapter 41: Project Export and Import               | 498    |

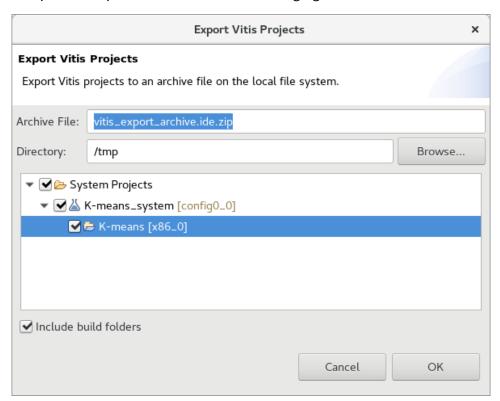

| Export a Vitis Project                              |        |

| Import a Vitis Project                              |        |

| Chapter 42: Getting Started with Examples           | 501    |

| Installing Examples                                 |        |

| Using Local Copies                                  |        |

| Section VIII: Embedded Processor Platform Developme | nt 504 |

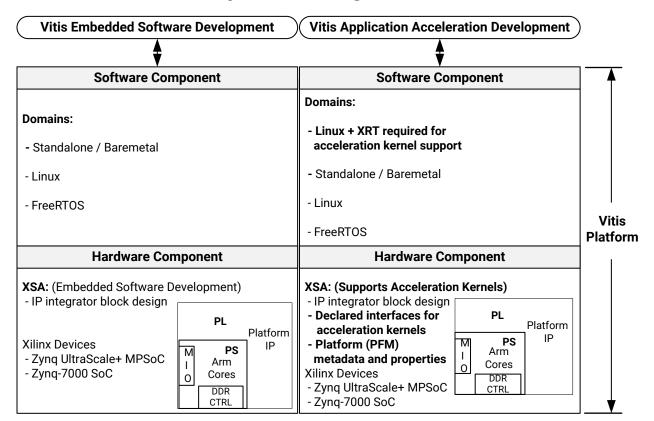

| Chapter 43: Vitis Embedded Platforms                | 505    |

| Chapter 44: Creating the Hardware Component                | 509 |

|------------------------------------------------------------|-----|

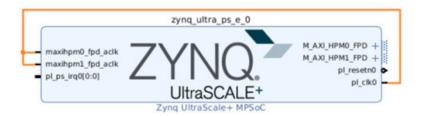

| XSA for Embedded Software Development                      | 511 |

| XSA for Application Acceleration Development Flow          | 513 |

| Chapter 45: Creating the Software Component                | 518 |

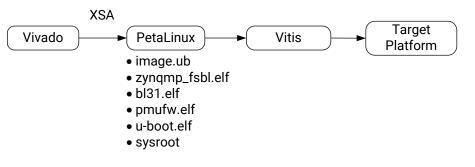

| Using PetaLinux for Generating Linux Output Products       | 518 |

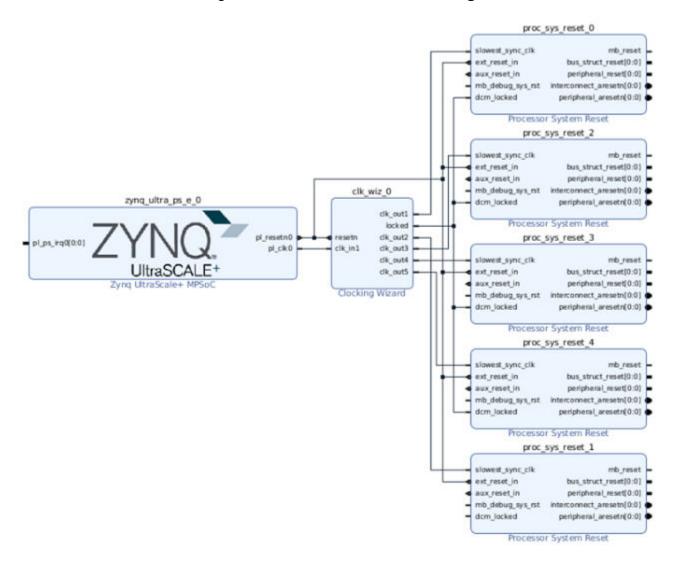

| Chapter 46: Creating the Platform                          | 522 |

| Creating Platforms with XRT and Kernel Support             | 523 |

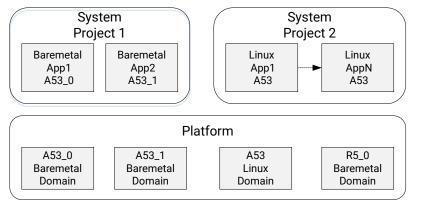

| Chapter 47: Configuring Platform Interface Properties      | 526 |

| Declaring Clocks                                           | 527 |

| Declaring AXI Ports                                        | 528 |

| Declaring AXI4-Stream Ports                                | 530 |

| Chapter 48: Hardware Component Requirements                | 531 |

| Chapter 49: Software Component Requirements                | 533 |

| Chapter 50: Platform Add-Ons                               | 534 |

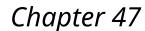

| Adding Kernel Interrupt Support                            | 534 |

| Section IX: Migrating Embedded Processor Applications from |     |

| SDSoC to Vitis                                             | 539 |

| Chapter 51: Overview                                       | 540 |

| Basic Migration Steps                                      | 540 |

| Chapter 52: Migrating the Host Application                 | 542 |

| Updating the Required #include Files                       | 543 |

| Loading the Main Function                                  | 544 |

| Using the OpenCL API                                       | 545 |

| Chapter 53: Migrating the Hardware Function                | 549 |

| Specifying the INTERFACE pragma                            | 549 |

| Chapter 54: Building the System                            | 551 |

| Chapter 55: Advanced Topics: Multiple Compute Uni  | ts and |

|----------------------------------------------------|--------|

| Kernel Streaming                                   | 552    |

| Multiple Compute Units                             | 552    |

| Kernel-to-Kernel Streaming                         |        |

| Section X: Migrating to a New Target Platform      | 556    |

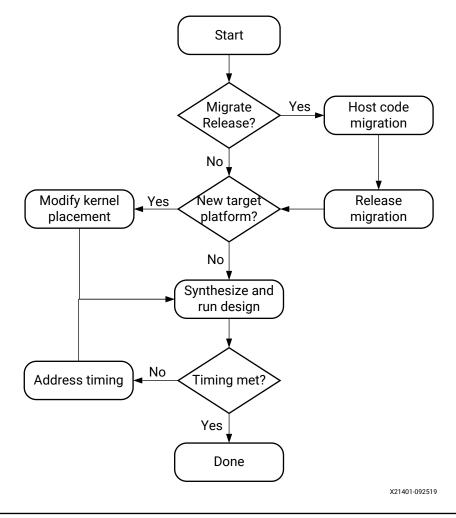

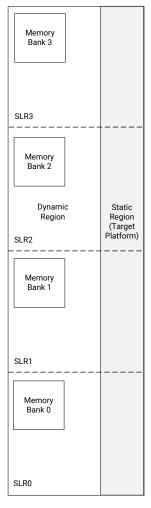

| Chapter 56: Design Migration                       | 557    |

| Understanding an FPGA Architecture                 |        |

| Understanding Target Platforms                     |        |

| Chapter 57: Migrating Releases                     | 563    |

| Host Code Migration                                |        |

| Release Migration                                  |        |

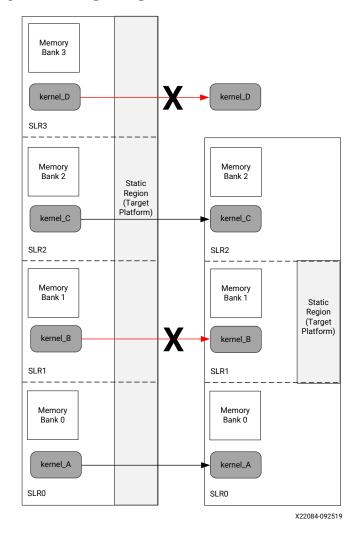

| Chapter 58: Modifying Kernel Placement             | 565    |

| Implications of a New Hardware Platform            |        |

| Determining Where to Place the Kernels             |        |

| Assigning Kernels to SLRs                          |        |

| Chapter 59: Address Timing                         | 572    |

| Custom Constraints                                 |        |

| Timing Closure Considerations                      |        |

| Section XI: Additional Resources and Legal Notices | 574    |

| Xilinx Resources                                   |        |

| Documentation Navigator and Design Hubs            |        |

| Please Read: Important Legal Notices               |        |

# Introduction to the Vitis Unified Software Platform

The Vitis<sup>™</sup> unified software platform is a new tool that combines all aspects of Xilinx<sup>®</sup> software development into one unified environment.

This section contains the following chapters:

- Vitis 2019.2 Software Platform Release Notes

- Installation

- Introduction to the Vitis Environment for Acceleration

- Methodology for Accelerating Applications with the Vitis Software Platform

# Vitis 2019.2 Software Platform Release Notes

This section contains information regarding the features and updates of the Vitis software platform in this release.

# What's in the Vitis Software Platform

#### **Hardware-Accelerated Application Development Flow**

For FPGA-based acceleration, the Vitis<sup>™</sup> core development kit lets you build a software application using an API, such as the OpenCL<sup>™</sup> API, to run hardware (HW) kernels on accelerator cards, like the Xilinx<sup>®</sup> Alveo<sup>™</sup> Data Center acceleration cards. The Vitis core development kit also supports running the software application on an embedded processor platform running Linux, such as on Zynq UltraScale+ MPSoC devices. For the embedded processor platform, the Vitis core development kit execution model also uses the OpenCL API and the Linux-based Xilinx Runtime (XRT) to schedule the HW kernels and control data movement.

The Vitis core development kit tools support the Alveo U50, U200, U250, and U280 Data Center accelerator cards, as well as the zcu102\_base, zcu104\_base, zc702\_base, and zc706\_base embedded processor platforms. In addition to these off-the-shelf platforms, custom platforms are also supported.

The Vitis software platform allows you to migrate data center applications to embedded platforms. The Vitis core development kit includes the v++ compiler for the hardware kernel on all platforms, the g++ compiler for compiling the application to run on an x86 host, and an Arm® compiler for cross-compiling the application to run on the embedded processor of a Xilinx device.

#### **Embedded Software Development Flow**

The Vitis IDE is designed to be used for the development of embedded software applications targeted towards Xilinx embedded processors. The Vitis IDE works with hardware designs created with Vivado Design Suite. Embedded platforms for the hardware acceleration flow can also be used in embedded software development.

# **Supported Platforms**

#### **Data Center Accelerator Cards**

Xilinx provides several accelerator cards available for data center use:

- Alveo U50 Data Center Accelerator card

- Alveo U200 Data Center Accelerator card

- Alveo U250 Data Center Accelerator card

- Alveo U280 Data Center Accelerator card

Refer to Alveo Data Center Accelerator Card Platforms User Guide (UG1120) for specifications of each accelerator card and available target platforms.

# **Changed Behavior**

The Vitis unified software platform inherits the features of SDAccel, SDSoC, and SDK, and integrates them into one unified software platform. This section provides an overview of migrating projects SDAccel, SDSoC, and SDK to the Vitis unified software platform.

#### Migrating from SDAccel

The following table specifies differences between the SDAccel development environment and the Vitis software platform.

**Table 1: Migration Summary**

| Area                                            | SDAccel Behavior                                                                                       | Vitis Behavior                                                                                                                                                                                                                  |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuring<br>the Alveo<br>accelerator<br>card | xbutil flash                                                                                           | xbmgmt flash  IMPORTANT! The xbutil utility previously performed the flash function, however, that sub-command has moved to the xbmgmt utility, which is intended for use by system administrators and requires sudo privilege. |

| Compilation and Linking                         | xocc                                                                                                   | v++                                                                                                                                                                                                                             |

| Design<br>Analysis                              | For the command line flow, you use the SDAccel IDE to view reports generated during the build process. | For the command line flow, you use the Vitis analyzer to view the reports generated during the build process.                                                                                                                   |

#### **Migrating from SDSoC**

For details about migrating your project from the SDSoC Development Environment to the Vitis unified software platform, refer to the Migrating Embedded Processor Applications from SDSoC to Vitis section in Vitis Unified Software Platform Documentation: Application Acceleration Development (UG1393).

# **Known Issues**

Known Issues for the Vitis software platform are available in AR#72773.

Known Issues for Xilinx Runtime are available in AR#71752.

# Installation

# **Installation Requirements**

The Vitis software platform consists of an integrated development environment (IDE) for interactive project development, and command-line tools for scripted or manual application development. The Vitis software platform also includes the Vivado® Design Suite for implementing the kernel on the target device, and for developing custom hardware platforms.

**Note:** Windows OS support is limited to the Vitis embedded software development flow. The acceleration features in the Vitis software platform are not supported.

Some requirements listed here are only required for software acceleration features, but not for embedded software development features. Xilinx recommends installing all the required packages to have the best experience with the Vitis software platform.

To install and run on a computer, your system must meet the following minimum requirements.

Table 2: Application Acceleration Development Flow Minimum System Requirements

| Component           | Requirement                                                       |

|---------------------|-------------------------------------------------------------------|

| Operating System    | Linux, 64-bit:                                                    |

|                     | • Ubuntu 16.04.5 LTS, 16.04.6 LTS, 18.04.1 LTS, 18.04.2 LTS       |

|                     | • CentOS 7.4, 7.5, 7.6                                            |

|                     | • RHEL 7.4, 7.5, 7.6                                              |

| System Memory       | For Alveo cards: 64 GB (80 GB is recommended) For embedded: 32 GB |

| Internet Connection | Required for downloading drivers and utilities.                   |

| Hard disk space     | 100 GB                                                            |

## Install Required CentOS/RHEL Packages

Before installing the Vitis software platform on CentOS or RedHat, you must install the Extra Packages for Enterprise Linux (EPEL), and ensure you have the proper kernel-headers and kernel-devel packages installed. The initial setup commands depend on your operating system. For more information, see <a href="https://fedoraproject.org/wiki/EPEL">https://fedoraproject.org/wiki/EPEL</a>.

**IMPORTANT!** For Linux, GLX version 1.3 or higher is required. For more information, see AR#73017.

Note: Ubuntu does not require additional packages.

1. Install EPEL.

On RedHat:

To enable an additional repository on your system and install the packages, open a terminal window, and enter the following command:

```

$ sudo yum-config-manager --enable rhel-7-server-optional-rpms

$ sudo yum install -y https://dl.fedoraproject.org/pub/epel/

epel-release-latest-7.noarch.rpm

```

On CentOS:

Open a terminal window, and enter the following command:

```

sudo yum install epel-release

```

2. To install kernel headers and kernel development packages, run the following commands:

```

$ sudo yum install kernel-headers-`uname -r`

$ sudo yum install kernel-devel-`uname -r`

```

**Note:** Ensure that uname is surrounded by backticks (`) and not single quotes (').

3. Cold reboot your system.

**TIP:** To verify that you have installed all required packages on your machine, use this script: https://github.com/ Xilinx/XRT/blob/master/src/runtime\_src/tools/scripts/xrtdeps.sh.

## **OpenCL Installable Client Driver Loader**

A system can have multiple OpenCL™ platforms, each with its own driver and OpenCL version. The Vitis™ environment supports the OpenCL Installable Client Driver (ICD) extension (cl\_khr\_icd). This extension allows multiple implementations of OpenCL to co-exist on the same system. The ICD Loader acts as a supervisor for all installed platforms, and provides a standard handler for all API calls.

Applications can choose an OpenCL platform from the list of installed platforms. Based on the platform ID specified by the application, the ICD dispatches the OpenCL host calls to the right runtime.

Xilinx does not provide the OpenCL ICD library, so the following should be used to install the library on your preferred system.

#### Ubuntu

On Ubuntu the ICD library is packaged with the distribution. Install the following packages:

- ocl-icd-libopencl1

- opencl-headers

- ocl-icd-opencl-dev

#### Linux

For RHEL/CentOS 7.X use EPEL 7, install the following packages:

- ocl-icd

- ocl-icd-devel

- opencl-headers

# Vitis Software Platform Installation

- 1. Install the Vitis Software Platform

- 2. Follow the instructions in Installing Xilinx Runtime.

- Install the data center platform, as described in Installing Data Center Platforms

- 4. Follow the instructions in Setting Up the Environment to Run the Vitis Software Platform.

**Note:** To install and use XRT on CentOS/RedHat, ensure that you have already installed all required packages and recommended libraries, as described in Install Required CentOS/RHEL Packages.

# **Install the Vitis Software Platform**

Ensure your system meets all requirements described in Installation Requirements.

TIP: To reduce installation time, disable anti-virus software and close all open programs that are not needed.

- 1. Go to the Xilinx Downloads Website.

- 2. Download the installer for your operating system.

- 3. Run the installer, which opens the Xilinx Unified 2019.2 Installer.

- 4. Click Next.

- 5. Enter your Xilinx user account credentials, and then select **Download and Install Now**.

- 6. Click Next.

- 7. Accept the terms and conditions by clicking each I Agree check box.

- 8. Click Next.

- 9. Select Vitis, and then click Next.

- 10. Optionally, customize your installation by selecting design tools and devices, and then click **Next**.

**IMPORTANT!** Do not deselect the following option. It is required for installation.

Devices → Install devices for Alveo and Xilinx Edge acceleration platforms

**Note:** Both the Vitis tools and Vivado Design Suite are installed. You do not need to separately install Vivado tools. You can also install System Generator and Model Composer if needed.

- 11. Select the installation directory, optional shortcut and file association options, and then click **Next**.

- 12. Review the installation summary, which shows the options and locations you have selected.

- 13. To proceed with the installation of the Vitis software platform, click **Install**.

After a successful installation, a confirmation message is displayed.

# **Installing Xilinx Runtime**

Xilinx Runtime (XRT) is implemented as a combination of user-space and kernel driver components. XRT supports Alveo PCIe-based cards, as well as Zynq UltraScale+ MPSoC-based embedded system platforms, and provides a software interface to Xilinx programmable logic devices.

You only need to install XRT once, regardless of how many platforms you may be installing.

**IMPORTANT!** XRT installation uses standard Linux RPM and Linux DEB distribution files, and root access is required for all software and firmware installations.

< rpm-dir> or < deb-dir> is the directory where you downloaded the packages to install.

To download and install the XRT package for your operating system, do the following.

#### CentOS/RedHat

- 1. To download the RPM file, click this link.

- 2. To install the package, enter the following command.

sudo yum install <rpm-dir>/<xrt\_filename>.rpm

#### Ubuntu

- 1. To download the DEB file, click one of the following:

- Ubuntu 16.04

- Ubuntu 18.04

- 2. To install the package, enter the following command.

```

sudo apt install <deb-dir>/<xrt_filename_OS>.deb

```

Note: <OS> represents the Ubuntu operating system version (16.04 or 18.04) you are using.

**IMPORTANT!** When installing XRT on Ubuntu, if the 2015 version of pyopencl is installed on your system, you must uninstall it. The XRT installation will install the 2019 version of pyopencl and will return an error if the 2015 version is installed. For more information, see AR#73055.

# **Installing Data Center Platforms**

For data center applications, you can configure your system for developing and debugging applications using the Vitis development environment, as well as running them on hardware. This does not require the actual accelerator card, but does require the installation of XRT, the deployment platform, and the development platform for each accelerator card you plan to develop applications for.

**TIP:** While the system does not require an accelerator card to develop applications, it is required to run and debug the application on hardware.

The platform includes information necessary for compiling and debugging new acceleration applications. It is a required part of the Vitis environment to support a specific accelerator card in the tool. Each accelerator card requires a platform that must be installed to support that platform in the Vitis environment.

Note: You must resolve any code host library dependencies.

#### Install Platforms on CentOS/RedHat

If you are installing these packages for use with the Vitis development environment and do not have an installed card, then you can ignore any message asking you to flash the accelerator card. However, if you are installing these packages for use with an installed accelerator card, you must follow the instructions in *Getting Started with Alveo Data Center Accelerator Cards* (UG1301).

**IMPORTANT!** Before installing platforms, you must have Xilinx Runtime installed, as described in Installing Xilinx Runtime.

- 1. Download the deployment and development target platform packages for the Alveo Data Center Accelerator card you are using:

- U50: Deployment Target Platform and Development Target Platform

- U200: Deployment Target Platform and Development Target Platform

- U250: Deployment Target Platform and Development Target Platform

- U280: Deployment Target Platform and Development Target Platform

- 2. To install the packages, enter the following command.

```

sudo yum install <rpm-dir>/<deployment_shell_filename>.rpm

sudo yum install <rpm-dir>/<development_shell_filename>.rpm

```

**Note:** < rpm-dir> is the directory where you downloaded the packages to install.

#### **Install Platforms on Ubuntu**

If you are installing these packages for use with the Vitis development environment and do not have an installed card, then you can ignore any message asking you to flash the accelerator card. However, if you are installing these packages for use with an installed accelerator card, you must follow the instructions in *Getting Started with Alveo Data Center Accelerator Cards* (UG1301).

**IMPORTANT!** Before installing platforms, you must have Xilinx Runtime installed, as described in Installing Xilinx Runtime.

- 1. Download the deployment and development target platform packages for the Alveo Data Center Accelerator card you are using:

- U50:

- Ubuntu 16.04: Deployment Target Platform and Development Target Platform

- Ubuntu 18.04: Deployment Target Platform and Development Target Platform

- U200:

- Ubuntu 16.04: Deployment Target Platform and Development Target Platform

- Ubuntu 18.04: Deployment Target Platform and Development Target Platform

- U250:

- Ubuntu 16.04: Deployment Target Platform and Development Target Platform

- **Ubuntu 18.04:** Deployment Target Platform and Development Target Platform

- U280:

- Ubuntu 16.04: Deployment Target Platform and Development Target Platform

- Ubuntu 18.04: Deployment Target Platform and Development Target Platform

- 2. To install the packages, enter the following command.

```

sudo apt install <deb-dir>/<deployment_shell_filename_OS>.deb

sudo apt install <deb-dir>/<development_shell_filename_OS>.deb

```

**Note:** <deb-dir> is the directory where you downloaded the packages to install. <OS> represents the Ubuntu operating system version (16.04 or 18.04) you are using.

# Setting Up the Environment to Run the Vitis Software Platform

To configure the environment to run the Vitis software platform, run the following scripts, which set up the environment to run in a specific command shell.

```

#setup XILINX_VITIS and XILINX_VIVADO variables

source <Vitis_install_path>/Vitis/2019.2/settings64.sh

#setup XILINX_XRT

source /opt/xilinx/xrt/setup.sh

```

**TIP:** . csh scripts are also provided.

To specify the location of any platforms you have installed as directed in Installing Data Center Platforms, or Installing Embedded Platforms, set the following environment variable:

export PLATFORM\_REPO\_PATHS=<path to platforms>

# Introduction to the Vitis Environment for Acceleration

# **Introduction and Overview**

The Vitis™ unified software platform is a new tool that combines all aspects of Xilinx® software development into one unified environment. The Vitis software platform supports both the Vitis embedded software development flow, for Xilinx Software Development Kit (SDK) users looking to move into the next generation technology, and the Vitis application acceleration development flow, for software developers looking to use the latest in Xilinx FPGA-based software acceleration. This content is primarily concerned with the application acceleration flow, and use of the Vitis core development kit and Xilinx Runtime (XRT).

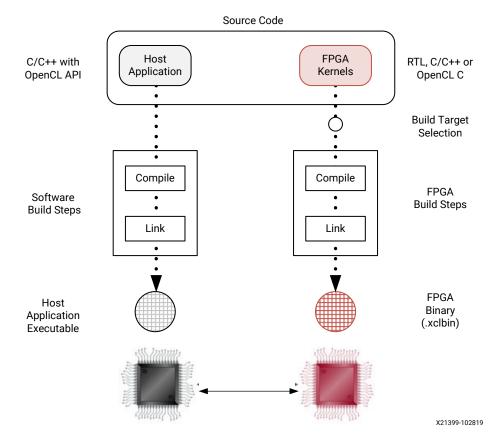

The Vitis application acceleration development flow provides a framework for developing and delivering FPGA accelerated applications using standard programming languages for both software and hardware components. The software component, or host program, is developed using C/C++ to run on x86 or embedded processors, with OpenCL™ API calls to manage runtime interactions with the accelerator. The hardware component, or kernel, can be developed using C/C++, OpenCL C, or RTL. The Vitis software platform accommodates various methodologies, letting you start by developing either the application or the kernel.

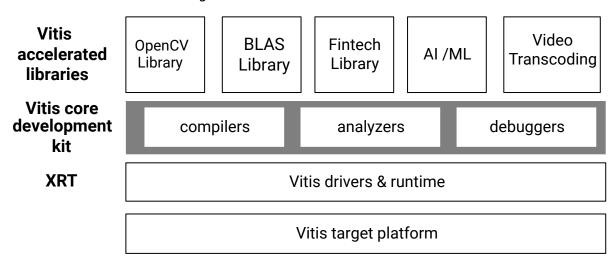

Figure 1: Vitis Unified Software Platform

X23292-092619

As shown in the figure above, the Vitis unified software platform consists of the following features and elements:

- Vitis technology targets acceleration hardware platforms, such as the Alveo<sup>™</sup> Data Center accelerator cards, or Zynq<sup>®</sup> UltraScale+<sup>™</sup> MPSoC and Zynq<sup>®</sup>-7000 SoC based embedded processor platforms.

- XRT provides an API and drivers for your host program to connect with the target platform, and handles transactions between your host program and accelerated kernels.

- Vitis core development kit provides the software development tool stack, such as compilers

and cross-compilers, to build your host program and kernel code, analyzers to let you profile

and analyze the performance of your application, and debuggers to help you locate and fix any

problems in your application.

- Vitis accelerated libraries provide performance-optimized FPGA acceleration with minimal

code changes, and without the need to reimplement your algorithms to harness the benefits

of Xilinx adaptive computing. Vitis accelerated libraries are available for common functions of

math, statistics, linear algebra and DSP, and also for domain specific applications, like vision

and image processing, quantitative finance, database, data analytics, and data compression.

For more information on Vitis accelerated libraries, refer to <a href="https://xilinx.github.io/">https://xilinx.github.io/</a>

Vitis\_Libraries/.

#### **FPGA Acceleration**

Xilinx FPGAs offer many advantages over traditional CPU/GPU acceleration, including a custom architecture capable of implementing any function that can run on a processor, resulting in better performance at lower power dissipation. When compared with processor architectures, the structures that comprise the programmable logic (PL) fabric in a Xilinx device enable a high degree of parallelism in application execution.

To realize the advantages of software acceleration on a Xilinx device, you should look to accelerate large compute-intensive portions of your application in hardware. Implementing these functions in custom hardware gives you an ideal balance between performance and power.

For more information on how to architect an application for optimal performance and other recommended design techniques, review the Methodology for Accelerating Applications with the Vitis Software Platform.

# **Execution Model**

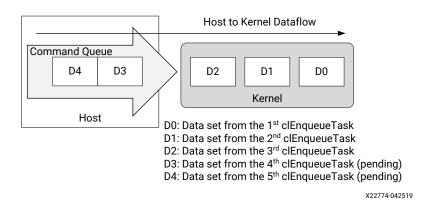

In the Vitis core development kit, an application program is split between a host application and hardware accelerated kernels with a communication channel between them. The host program, written in C/C++ and using API abstractions like OpenCL, runs on a host processor (such as an x86 server or an Arm processor for embedded platforms), while hardware accelerated kernels run within the programmable logic (PL) region of a Xilinx device.

The API calls, managed by XRT, are used to process transactions between the host program and the hardware accelerators. Communication between the host and the kernel, including control and data transfers, occurs across the PCle® bus or an AXI bus for embedded platforms. While control information is transferred between specific memory locations in the hardware, global memory is used to transfer data between the host program and the kernels. Global memory is accessible by both the host processor and hardware accelerators, while host memory is only accessible by the host application.

For instance, in a typical application, the host first transfers data to be operated on by the kernel from host memory into global memory. The kernel subsequently operates on the data, storing results back to the global memory. Upon kernel completion, the host transfers the results back into the host memory. Data transfers between the host and global memory introduce latency, which can be costly to the overall application. To achieve acceleration in a real system, the benefits achieved by the hardware acceleration kernels must outweigh the added latency of the data transfers.

Host Processor

Custom Application

XRT/OpenCL API

XRT

Drivers

Programmable Logic

Custom Kernels

AXI Interfaces

Global Memory

DMA

Figure 2: Architecture of a Vitis Core Development Kit Application

X21835-102219

The target platform contains the FPGA accelerated kernels, global memory, and the direct memory access (DMA) for memory transfers. Kernels can have one or more global memory interfaces and are programmable. The Vitis core development kit execution model can be broken down into the following steps:

- 1. The host program writes the data needed by a kernel into the global memory of the attached device through the PCle interface on an Alveo Data Center accelerator card, or through the AXI bus on an embedded platform.

- 2. The host program sets up the kernel with its input parameters.

- The host program triggers the execution of the kernel function on the FPGA.

- 4. The kernel performs the required computation while reading data from global memory, as necessary.

- 5. The kernel writes data back to global memory and notifies the host that it has completed its task.

- 6. The host program reads data back from global memory into the host memory and continues processing as needed.

The FPGA can accommodate multiple kernel instances on the accelerator, both different types of kernels, and multiple instances of the same kernel. XRT transparently orchestrates the interactions between the host program and kernels in the accelerator. XRT architecture documentation is available at <a href="https://xilinx.github.io/XRT/">https://xilinx.github.io/XRT/</a>.

# **Build Process**

**TIP:** For a brief tutorial on the actual build process, review the Essential Concepts for Building and Running an Accelerated Application tutorial on the Xilinx GitHub repository.

The Vitis core development kit offers all of the features of a standard software development environment:

- Compiler or cross-compiler for host applications running on x86 or Arm® processors.

- Cross-compilers for building the FPGA binary.

- Debugging environment to help identify and resolve issues in the code.

- Performance profilers to identify bottlenecks and help you optimize the application.

The build process follows a standard compilation and linking process for both the host program and the kernel code. As shown in the following figure, the host program is built using the GNU C ++ compiler (g++) or the GNU C++ Arm cross-compiler for MPSoC-based devices. The FPGA binary is built using the Vitis compiler.

Figure 3: Software/Hardware Build Process

## **Host Program Build Process**

The main application is compiled and linked with the g++ compiler, using the following two step process:

- 1. Compile any required code into object files (.o).

- 2. Link the object files (.o) with the XRT shared library to create the executable.

For details on this topic, refer to Building the Host Program.

## **FPGA Binary Build Process**

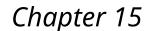

OpenCL C/C++ C/C++ RTL Vivado HLS V++ -C v++ -c package\_xo .xo .xo .xo .xo Target v++ -| Platform .xclbin

Figure 4: FPGA Build Process

X21155-091219

Kernels can be described in C/C++, or OpenCL C code, or can be created from packaged RTL designs. As shown in the figure above, each hardware kernel is independently compiled to a Xilinx object (.xo) file.

Xilinx object (.xo) files are linked with the hardware platform to create an FPGA binary file (.xclbin) that is loaded into the Xilinx device on the target platform.

The key to building the FPGA binary is to determine the build target you are producing. For more information, refer to Build Targets.

For a detailed explanation of the build process, refer to Building the FPGA Binary.

#### **Build Targets**

The Vitis compiler build process generates the host program executable and the FPGA binary (.xclbin). The nature of the FPGA binary is determined by the build target.

- When the build target is software or hardware emulation, the Vitis compiler generates simulation models of the kernels in the FPGA binary. These emulation targets let you build, run, and iterate the design over relatively quick cycles; debugging the application and evaluating performance.

- When the build target is the hardware system, Vitis compiler generates the .xclbin for the

hardware accelerator, using the Vivado Design Suite to run synthesis and implementation. It

uses these tools with predefined settings proven to provide good quality of results. Using the

Vitis core development kit does not require knowledge of these tools; however, hardwaresavvy developers can fully leverage these tools and use all the available features to implement

kernels.

The Vitis compiler provides three different build targets, two emulation targets used for debug and validation purposes, and the default hardware target used to generate the actual FPGA binary:

- Software Emulation (sw\_emu): Both the host application code and the kernel code are compiled to run on the host processor. This allows iterative algorithm refinement through fast build-and-run loops. This target is useful for identifying syntax errors, performing source-level debugging of the kernel code running together with application, and verifying the behavior of the system.

- Hardware Emulation (hw\_emu): The kernel code is compiled into a hardware model (RTL), which is run in a dedicated simulator. This build-and-run loop takes longer but provides a detailed, cycle-accurate view of kernel activity. This target is useful for testing the functionality of the logic that will go in the FPGA and getting initial performance estimates.

- **System (hw):** The kernel code is compiled into a hardware model (RTL) and then implemented on the FPGA, resulting in a binary that will run on the actual FPGA.

# **Tutorials and Examples**

To help you quickly get started with the Vitis core development kit, you can find tutorials, example applications, and hardware kernels in the following repositories on <a href="http://github.com/Xilinx">http://github.com/Xilinx</a>.

Vitis Application Acceleration Development Flow Tutorials: Provides a number of tutorials

that can be worked through to teach specific concepts regarding the tool flow and application

development.

The Getting Started pathway tutorials are an excellent place to start as a new user.

• Vitis Examples: Hosts many examples to demonstrate good design practices, coding guidelines, design pattern for common applications, and most importantly, optimization techniques to maximize application performance. The on-boarding examples are divided into several main categories. Each category has various key concepts illustrated by individual examples in both OpenCL™ C and C/C++ frameworks, when applicable. All examples include a Makefile to enable building for software emulation, hardware emulation, and running on hardware, and a README.md file with a detailed explanation of the example.

Now that you have an idea of the elements of the Vitis core development kit and how to write and build an application for acceleration, review the best approach for your design problem.

# Methodology for Accelerating Applications with the Vitis Software Platform

### Introduction

This content focuses on Data Center applications and PCIe®-based acceleration cards, but the concepts developed here are also generally applicable to embedded applications.

# **Document Audience and Scope**

The purpose of this guide is to familiarize system architects and software developers with the following:

- Methodology for architecting device-accelerated application

- Methodology for developing C/C++ kernels

Note: This guide covers processor logic (PL) acceleration.

## **Acceleration: An Industrial Analogy**

There are distinct differences between CPUs, GPUs, and programmable devices. Understanding these differences is key to efficiently developing applications for each kind of device and achieving optimal acceleration.

Both CPUs and GPUs have pre-defined architectures, with a fixed number of cores, a fixed-instruction set, and a rigid memory architecture. GPUs scale performance through the number of cores and by employing SIMD/SIMT parallelism. In contrast, programmable devices are fully customizable architectures. The developer creates compute units that are optimized for application needs. Performance is achieved by creating deeply pipelined datapaths, rather than multiplying the number of compute units.

Think of a CPU as a group of workshops, with each one employing a very skilled worker. These workers have access to general purpose tools that let them build almost anything. Each worker crafts one item at a time, successively using different tools to turn raw material into finished goods. This sequential transformation process can require many steps, depending on the nature of the task. The workshops are independent, and the workers can all be doing different tasks without distractions or coordination problems.

A GPU also has workshops and workers, but it has considerably more of them, and the workers are much more specialized. They have access to only specific tools and can do fewer things, but they do them very efficiently. GPU workers function best when they do the same few tasks repeatedly, and when all of them are doing the same thing at the same time. After all, with so many different workers, it is more efficient to give them all the same orders.

Programmable devices take this workshop analogy into the industrial age. If CPUs and GPUs are groups of individual workers taking sequential steps to transform inputs into outputs, programmable devices are factories with assembly lines and conveyer belts. Raw materials are progressively transformed into finished goods by groups of workers dispatched along assembly lines. Each worker performs the same task repeatedly and the partially finished product is transferred from worker to worker on the conveyer belt. This results in a much higher production throughput.

Another major difference with programmable devices is that the factories and assembly lines do not already exist, unlike the workshops and workers in CPUs and GPUs. To refine our analogy, a programmable device would be like a collection of empty lots waiting to be developed. This means that the device developer gets to build factories, assembly lines, and workstations, and then customizes them for the required task instead of using general purpose tools. And just like lot size, device real-estate is not infinite, which limits the number and size of the factories which can be built in the device. Properly architecting and configuring these factories is therefore a critical part of the device programming process.

Traditional software development is about programming functionality on a pre-defined architecture. Programmable device development is about programming an architecture to implement the desired functionality.

# **Methodology Overview**

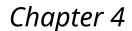

The methodology is comprised of two major phases:

- 1. Architecting the application

- 2. Developing the C/C++ kernels

In the first phase, the developer makes key decisions about the application architecture by determining which software functions should be mapped to device kernels, how much parallelism is needed, and how it should be delivered.

In the second phase, the developer implements the kernels. This primarily involves structuring source code and applying the desired compiler pragma to create the desired kernel architecture and meet the performance target.

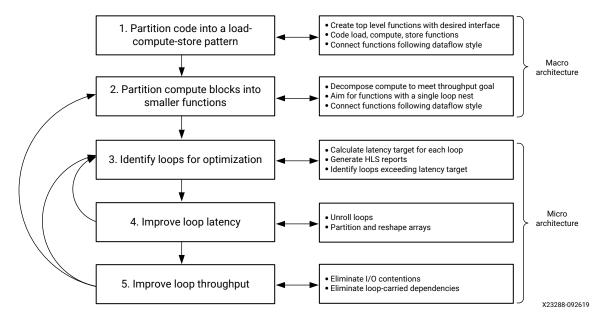

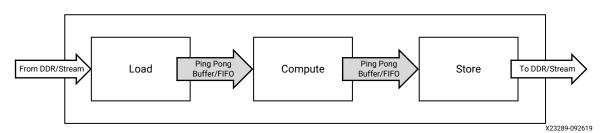

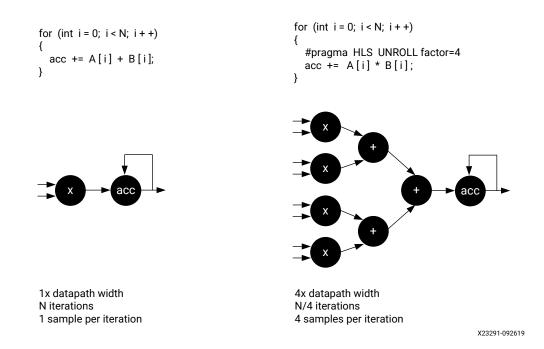

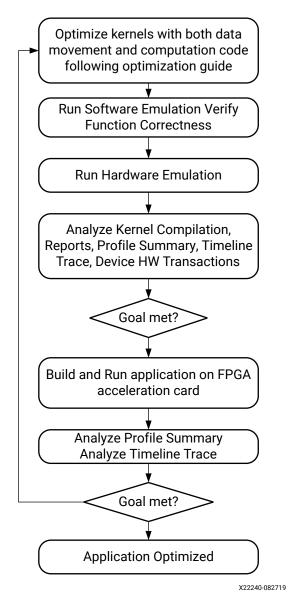

Figure 5: Methodology Overview

Performance optimization is an iterative process. The initial version of an accelerated application will likely not produce the best possible results. The methodology described in this guide is a process involving constant performance analysis and repeated changes to all aspects of the implementation.

#### **Recommendations**

A good understanding of the Vitis<sup>™</sup> unified software platform programming and execution model is critical to embarking on a project with this methodology. The following resources provide the necessary knowledge to be productive with the Vitis software platform:

- Section II: Developing Applications

- Vitis Application Acceleration Development Flow Tutorials on GitHub.

In addition to understanding the key aspects of the Vitis software platform, a good understanding of the following topics will help achieve optimal results with this methodology:

- Application domain

- Software acceleration principles

- Concepts, features and architecture of device

- Features of the targeted device accelerator card and corresponding target platform

- Parallelism in hardware implementations (http://kastner.ucsd.edu/hlsbook/)

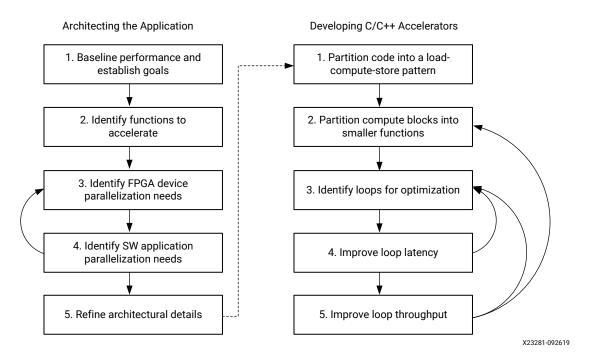

# Methodology for Architecting a Device Accelerated Application

Before beginning the development of an accelerated application, it is important to architect it properly. In this phase, the developer makes key decisions about the architecture of the application and determines factors such as what software functions should be mapped to device kernels, how much parallelism is needed, and how it should be delivered.

Figure 6: Methodology for Architecting the Application

This section walks through the various steps involved in this process. Taking an iterative approach through this process helps refine the analysis and leads to better design decisions.

# Step 1: Establish a Baseline Application Performance and Establish Goals

Start by measuring the runtime and throughput performance, to identify bottlenecks of the current application running on your existing platform. These performance numbers should be generated for the entire application (end-to-end) as well as for each major function in the application. The most effective way is to run the application with profiling tools, like <code>valgrind</code>, <code>callgrind</code>, and GNU <code>gprof</code>. The profiling data generated by these tools show the call graph with the number of calls to all functions and their execution time. These numbers provide the baseline for most of the subsequent analysis process. The functions that consume the most execution time are good candidates to be offloaded and accelerated onto FPGAs.

#### **Measure Running Time**

Measuring running time is a standard practice in software development. This can be done using common software profiling tools such as gprof, or by instrumenting the code with timers and performance counters.

The following figure shows an example profiling report generated with gprof. Such reports conveniently show the number of times a function is called, and the amount of time spent (runtime).

Figure 7: **Gprof Output Example**

| Each sample counts as 0.01 seconds. |            |         |       |         |         |                      |

|-------------------------------------|------------|---------|-------|---------|---------|----------------------|

| %                                   | cumulative | self    |       | self    | total   |                      |

| time                                | seconds    | seconds | calls | ms/call | ms/call | name                 |

| 70.45                               | 25.54      | 25.54   | 256   | 99.76   | 99.76   | F4(int*, int*, int*) |

| 12.44                               | 30.05      | 4.51    | 256   | 17.61   | 17.61   | F2(int*, int*)       |

| 9.91                                | 33.64      | 3.59    | 256   | 14.03   | 14.03   | F1(int*, int*, int*) |

| 7.83                                | 36.48      | 2.84    | 256   | 11.08   | 11.08   | F3(int*, int*)       |

| 0.00                                | 36.48      | 0.00    | 256   | 0.00    | 142.48  | F(int*, int*)        |

#### Measure Throughput

Throughput is the rate at which data is being processed. To compute the throughput of a given function, divide the volume of data the function processed by the running time of the function.

$$T_{SW} = max(V_{INPUT}, V_{OUTPUT}) / Running Time$$

Some functions process a pre-determined volume of data. In this case, simple code inspection can be used to determine this volume. In some other cases, the volume of data is variable. In this case, it is useful to instrument the application code with counters to dynamically measure the volume.

Measuring throughput is as important as measuring running time. While device kernels can improve overall running time, they have an even greater impact on application throughput. As such, it is important to look at throughput as the main optimization target.

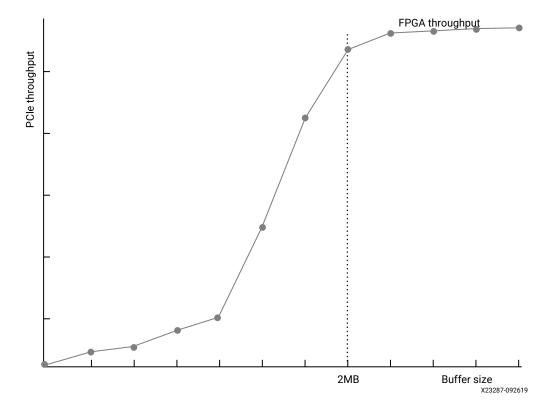

#### Determine the Maximum Achievable Throughput

In most device-accelerated systems, the maximum achievable throughput is limited by the PCIe<sup>®</sup> bus. PCIe performance is influenced by many different aspects, such as motherboard, drivers, target platform, and transfer sizes. Run DMA tests upfront to measure the effective throughput of PCIe transfers and thereby determine the upper bound of the acceleration potential, such as the xbutil dma test.

Figure 8: Sample Result of dmatest on an Alveo U200 Data Center Accelerator Card

```

$ xbutil dmatest

INFO: Found total 1 card(s), 1 are usable

Total DDR size: 65536 MB

Reporting from mem_topology:

Data Validity & DMA Test on bank0

Host -> PCIe -> FPGA write bandwidth = 11381.7 MB/s

Host <- PCIe <- FPGA read bandwidth = 8358.9 MB/s

Data Validity & DMA Test on bank1

Host -> PCIe -> FPGA write bandwidth = 11235.3 MB/s

Host <- PCIe <- FPGA read bandwidth = 7485.3 MB/s

INFO: xbutil dmatest succeeded.</pre>

```

An acceleration goal that exceeds this upper bound throughput cannot be met as the system will be I/O bound. Similarly, when defining kernel performance and I/O requirements, keep this upper bound in mind.

#### **Establish Overall Acceleration Goals**

Determining acceleration goals early in the development is necessary because the ratio between the acceleration goal and the baseline performance will drive the analysis and decision-making process.

Acceleration goals can be hard or soft. For example, a real-time video application could have the hard requirement to process 60 frames per second. A data science application could have the soft goal to run 10 times faster than an alternative implementation.

Either way, domain expertise is important for setting obtainable and meaningful acceleration goals.

### **Step 2: Identify Functions to Accelerate**

After establishing the performance baseline, the next step is to determine which functions should be accelerated in the device.

**TIP:** Minimize changes to the existing code at this point so you can quickly generate a working design on the FPGA and get the baselined performance and resource numbers.

When selecting functions to accelerate in hardware, there are two aspects to consider:

- Performance bottlenecks: Which functions are in application hot spots?

- Acceleration potential: Do these functions have the potential for acceleration?

#### **Identify Performance Bottlenecks**

In a purely sequential application, performance bottlenecks can be easily identified by looking at profiling reports. However, most real-life applications are multi-threaded and it is important to the take the effects of parallelism in consideration when looking for performance bottlenecks.

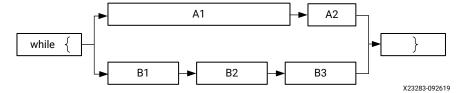

The following figure represents the performance profile of an application with two parallel paths. The width of each rectangle is proportional to the performance of each function.

Figure 9: Application with Two Parallel Paths

The above performance visualization in the context of parallelism shows that accelerating only one of the two paths will not improve the application's overall performance. Because paths A and B re-converge, they are dependent upon each other to finish. Likewise, accelerating A2, even by 100x, will not have a significant impact on the performance of the upper path. Therefore, the performance bottlenecks in this example are functions A1, B1, B2, and B3.

When looking for acceleration candidates, consider the performance of the entire application, not just of individual functions.

#### **Identify Acceleration Potential**

A function that is a bottleneck in the software application does not necessarily have the potential to run faster in a device. A detailed analysis is usually required to accurately determine the real acceleration potential of a given function. However, some simple guidelines can be used to assess if a function has potential for hardware acceleration:

• What is the computational complexity of the function?

Computational complexity is the number of basic computing operations required to execute the function. In programmable devices, acceleration is achieved by creating highly parallel and deeply pipelined data paths. These would be the assembly lines in the earlier analogy. The longer the assembly line and the more stations it has, the more efficient it will be compared to a worker taking sequential steps in his workshop.

Good candidates for acceleration are functions where a deep sequence of operations needs to be performed on each input sample to produce an output sample.

• What is the computational intensity of the function?

Computational intensity of a function is the ratio of the total number of operations to the total amount of input and output data. Functions with a high computational intensity are better candidates for acceleration since the overhead of moving data to the accelerator will be comparatively lower.

What is the data access locality profile of the function?

The concepts of data reuse, spatial locality and temporal locality are useful to assess how much overhead of moving data to the accelerator can be optimized. Spatial locality reflects the average distance between several consecutive memory access operations. Temporal locality reflects the average number of access operations for an address in memory during program execution. The lower these measures the better, since it makes data more easily cacheable in the accelerator, reducing the need to expensive and potentially redundant accesses to global memory.

How does the throughput of the function compare to the maximum achievable in a device?

Device-accelerated applications are distributed, multi-process systems. The throughput of the overall application will not exceed the throughput of its slowest function. The nature of this bottleneck is application specific and can come from any aspect of the system: I/O, computation or data movement. The developer can determine the maximum acceleration potential by dividing the throughput of the slowest function by the throughput of the selected function.

Maximum Acceleration Potential =  $T_{Min} / T_{SW}$

On Alveo Data Center accelerator cards, the PCIe bus imposes a throughput limit on data transfers. While it may not be the actual bottleneck of the application, it constitutes a possible upper bound and can therefore be used for early estimates. For example, considering a PCIe throughput of 10GB/sec and a software throughput of 50MB/sec, the maximum acceleration factor for this function is 200x.

These four criteria are not guarantees of acceleration, but they are reliable tools to identify the right functions to accelerate on a device.

### **Step 3: Identify Device Parallelization Needs**

After the functions to be accelerated have been identified and the overall acceleration goals have been established, the next step is to determine what level of parallelization is needed to meet the goals.

The factory analogy is again helpful to understand what parallelism is possible within kernels.

As described, the assembly line allows the progressive and simultaneous processing of inputs. In hardware, this kind of parallelism is called pipelining. The number of stations on the assembly line corresponds to the number of stages in the hardware pipeline.

Another dimension of parallelism within kernels is the ability to process multiple samples at the same time. This is like putting not just one, but multiple samples on the conveyer belt at the same time. To accommodate this, the assembly line stations are customized to process multiple samples in parallel. This is effectively defining the width of the datapath within the kernel.

Performance can be further scaled by increasing the number of assembly lines. This can be accomplished by putting multiple assembly lines in a factory, and also by building multiple identical factories with one or more assembly lines in each of them.

The developer will need to determine which combination of parallelization techniques will be most effective at meeting the acceleration goals.

#### Estimate Hardware Throughput without Parallelization

The throughput of the kernel without any parallelization can be approximated as:

$T_{HW}$  = Frequency / Computational Intensity = Frequency \* max( $V_{INPUT}$ ,  $V_{OUTPUT}$ ) /  $V_{OPS}$

Frequency is the clock frequency of the kernel. This value is determined by the targeted acceleration platform, or target platform. For instance, the maximum kernel clock on an Alveo U200 Data Center accelerator card is 300 MHz.

As previously mentioned, the Computational Intensity of a function is the ratio of the total number of operations to the total amount of input and output data. The formula above clearly shows that functions with a high volume of operations and a low volume of data are better candidates for acceleration.

#### Determine How Much Parallelism is Needed

After the equation above has been calculated, it is possible to estimate the initial HW/SW performance ratio:

Speed-up =  $T_{HW}/T_{SW}$  =  $F_{max}$  \* Running Time / $V_{ops}$

Without any parallelization, the initial speed-up will most likely be less than 1.

Next, calculate how much parallelism is needed to meet the performance goal:

Parallelism Needed =

$$T_{Goal} / T_{HW} = T_{Goal} * V_{ops} / (F_{max} * max(V_{INPUT}, V_{OUTPUT}))$$

This parallelism can be implemented in various ways: by widening the datapath, by using multiple engines, and by using multiple kernel instances. The developer should then determine the best combination given his needs and the characteristics of his application.

# Determine How Many Samples the Datapath Should be Processing in Parallel

One possibility is to accelerate the computation by creating a wider datapath and processing more samples in parallel. Some algorithms lend themselves well to this approach, whereas others do not. It is important to understand the nature of the algorithm to determine if this approach will work and if so, how many samples should be processed in parallel to meet the performance goal.

Processing more samples in parallel using a wider datapath improves performance by reducing the latency (running time) of the accelerated function.

# Determine How Many Kernels Can and Should be Instantiated in the Device

If the datapath cannot be parallelized (or not sufficiently), then look at adding more kernel instances, as described in Creating Multiple Instances of a Kernel. This is usually referred to as using multiple compute units (CUs).

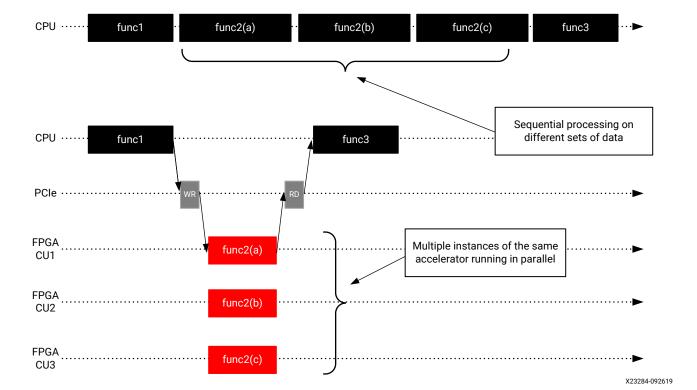

Adding more kernel instances improves the performance of the application by allowing the execution of more invocations of the targeted function in parallel, as shown below. Multiple data sets are processed concurrently by the different instances. Application performance scales linearly with the number of instances, provided that the host application can keep the kernels busy.

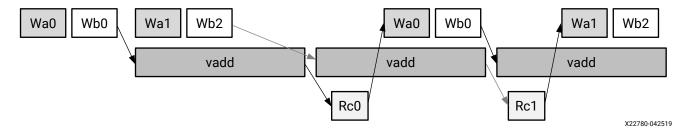

Figure 10: Improving Performance with Multiple Compute Units

As illustrated in the Using Multiple Compute Units tutorial, the Vitis technology makes it easy to scale performance by adding additional instances.

At this point, the developer should have a good understanding of the amount of parallelism necessary in the hardware to meet performance goals and, through a combination of datapath width and kernel instances, how that parallelism will be achieved

# Step 4: Identify Software Application Parallelization Needs

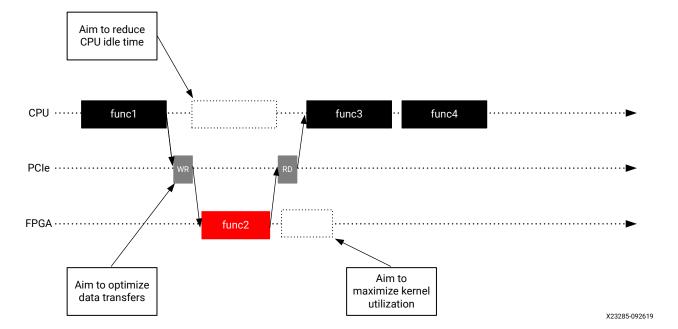

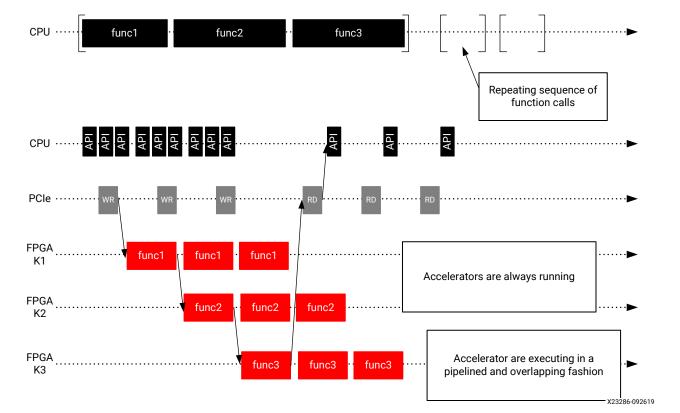

While the hardware device and its kernels are architected to offer potential parallelism, the software application must be engineered to take advantage of this potential parallelism.

Parallelism in the software application is the ability for the host application to:

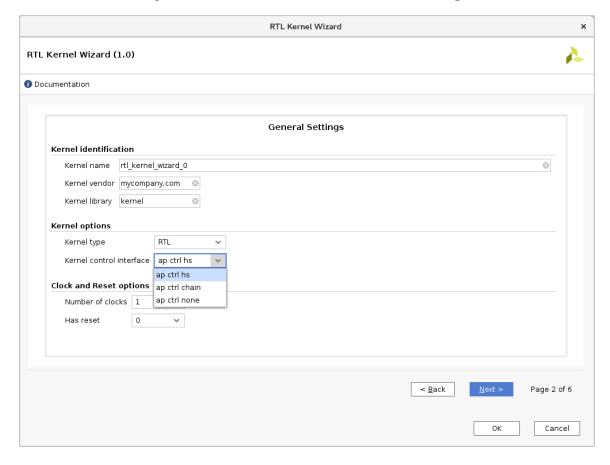

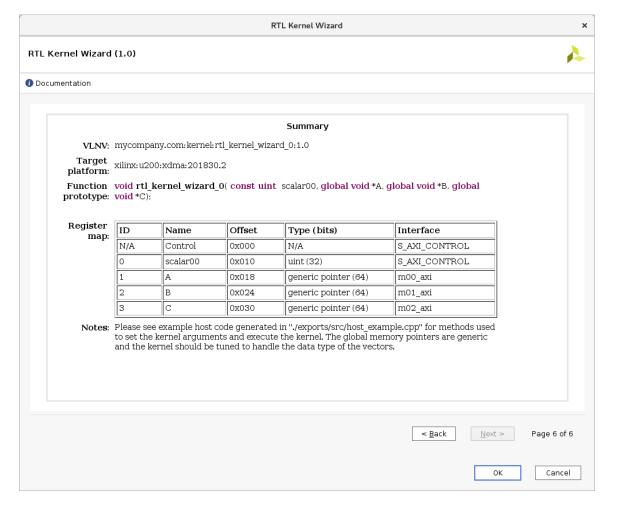

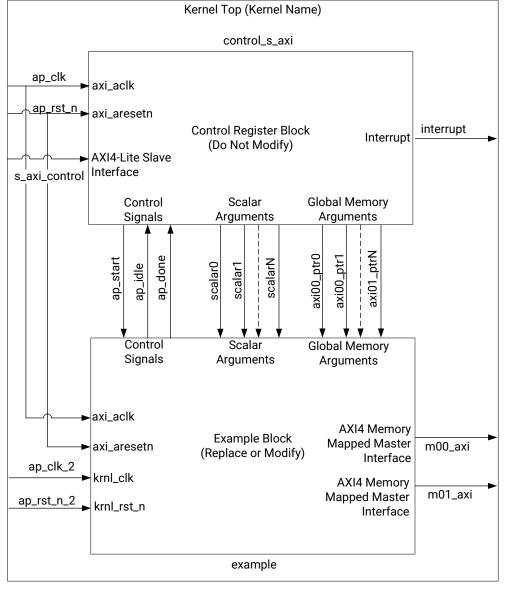

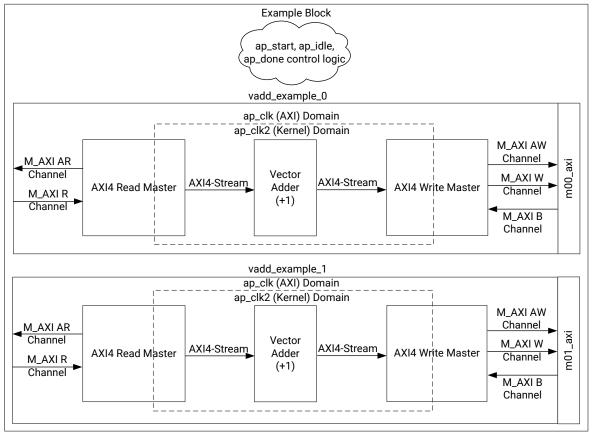

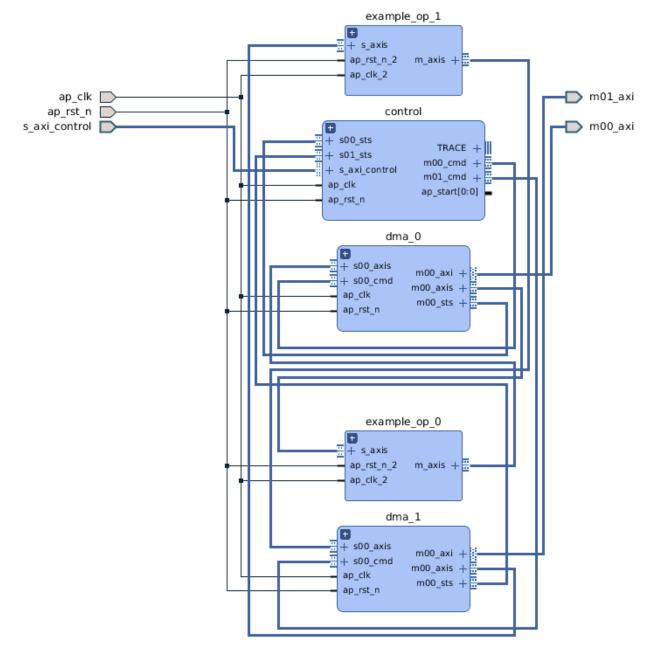

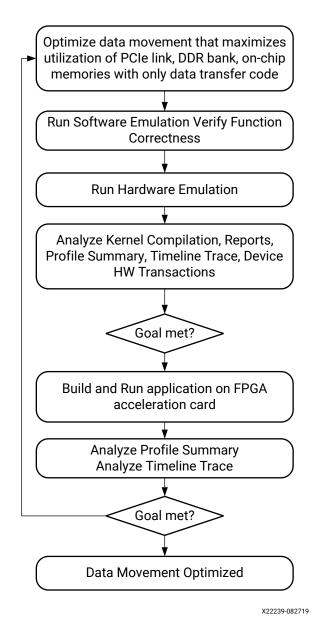

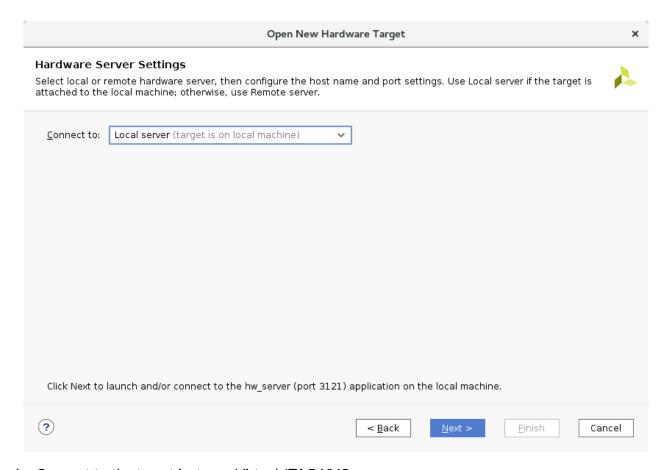

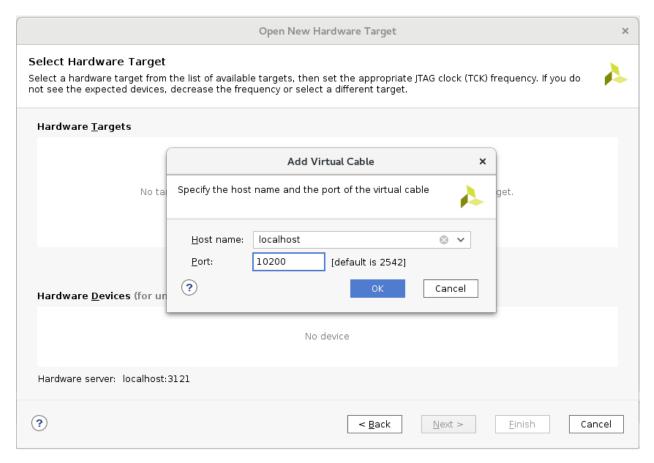

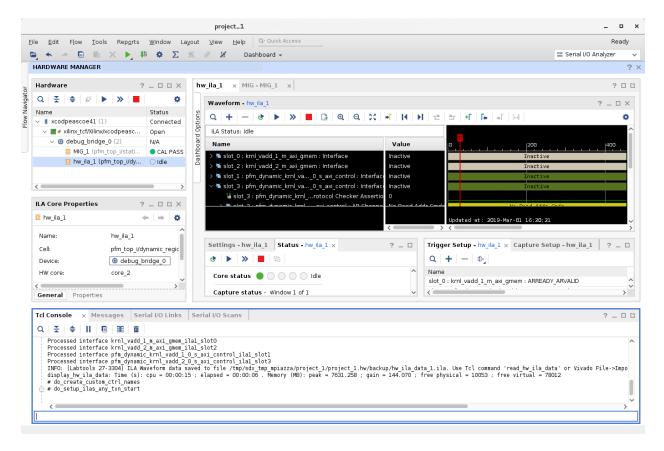

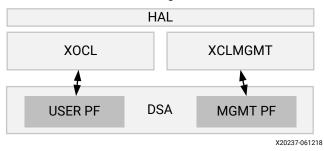

- Minimize idle time and do other tasks while the device kernels are running.