# **CEM 3310**

CURTIS ELECTROMUSIC SPECIALTIES

## **Voltage Controlled Envelope Generator**

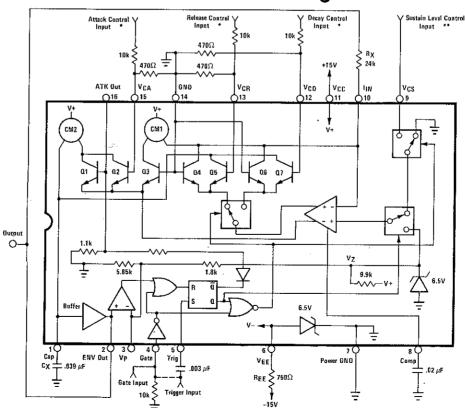

The CEM3310 is a self-contained. precision ADSR type of envelope generator intended for electronic music and other sound generation applications. Attack, decay and release times are exponentially voltage controllable over a wide range, and the sustain level is linearly voltage controllable from 0 to 100% of the peak voltage. A unique design approach allows for a 10,000 times improvement in control voltage rejection over conventional designs. In addition, much care has been given to the accuracy, repeatability and tracking of the parameters from unit to unit without external trimming. The times are to a first order determined only by the external resistor and capacitor and constant of physics, KT/q. Wide tolerance monolithic resistors are not used to set up the time constants or the control scale. Finally, all four control inputs are isolated from the rest of the circuitry so that the control pins of tracking units may be simply tied together. Although a low voltage process has been used to lower the cost and lower the leakage currents. an internal 6.5 volt Zener diode allows the chip to be powered by ± 15 volts supplies, as well as +15, -5 volt supplies.

- Zero to -5V Varies the Times from 2mS to 20S

- \*\* Zero to +5V Varies the Sustain Level from 0 to 100%

#### **Features**

- Low Cost

- Third Generation Design

- Large Time Control Range: 50,000 min

- Full ADSR Response

- True RC Envelope Shape

- Exceptionally Low Control Voltage Feedthrough: 90µV max

- Accurate Exponential Time Control Scales

- Isolated Control Inputs

- Good Repeatability and Tracking Between Units Without External Trim

- Independent Gate and Trigger

- ± 15 Volt Supplies

## **CEM 3310**

## **Electrical Characteristics**

| $V_{CC}$ = +15.0V $V_{EE}$ = -5.0 to -15.0V $R_X$ = 24K $T_A$ = 25°C                                                                                    |            |                   |              |            |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------|--------------|------------|--|

|                                                                                                                                                         | MIN        | TYP               | MAX          | Units      |  |

| Time Control Range                                                                                                                                      | 50,000:1   | 250,000:1         | <del>-</del> |            |  |

| Attack Asymtote Voltage (V <sub>Z</sub> )                                                                                                               | 6.1        | 6.5               | 6.9          | V          |  |

| Attack Peak Voltage (V <sub>p</sub> )                                                                                                                   | 4.7        | 5.0               | 5.3          | V          |  |

| Attack Peak to Asymptote Tracking                                                                                                                       | —          | 1.5               | 4            | %          |  |

| Control Scale Sensitivity                                                                                                                               | 58.5       | 60                | 61.5         | mV/Decade  |  |

| Temperature Coefficient of Control Scale                                                                                                                | +3,000     | +3,300            | +3,600       | ppm        |  |

| ATK, DCY, RLS Scale Tracking                                                                                                                            | -300       | 0                 | +300         | μV/Decade  |  |

| Exponential Full Scale Control Accuracy $50$ nA $<$ I $_{ m O}$ $<$ $50$ $\mu$ A $2$ nA $<$ I $_{ m O}$ $<$ $200$ $\mu$ A                               |            | 0.3<br>2          | 1.5<br>10    | %<br>%     |  |

| Attack C.V. Feedthrough <sup>2</sup><br>Decay C.V. Feedthrough <sup>2</sup><br>Release C.V. Feedthrough <sup>2</sup>                                    | _          | 6<br>NONE<br>NONE | 90           | μV         |  |

| Sustain Final Voltage Error (VO-VCS)                                                                                                                    | -3         | +10               | +23          | mV         |  |

| Release Final Voltage Error (VO)                                                                                                                        | -3         | +10               | +23          | mV         |  |

| RC Curve Asymptote Error <sup>3</sup> VCA,D,R = 0  VCA,D,R = -240mV                                                                                     |            | <del>-6</del>     | -60          | μV         |  |

|                                                                                                                                                         | -          | -125              | -1250        | mV         |  |

| Input Current (I <sub>IN</sub> ) to Output Current (I <sub>O</sub> ) Ratio, V <sub>CA,D,R</sub> = 0.5 Charge Current (ATK) Discharge Current (DCY, RLS) | .75<br>.83 | 1                 | 1.3<br>1.2   |            |  |

| Buffer Input Current (I <sub>B2</sub> )                                                                                                                 | _          | 0.5               | 5            | πA         |  |

| Op Amp Input Current (I <sub>B1</sub> )                                                                                                                 | 150        | 400               | 800          | nA         |  |

| Gate Threshold<br>Gate Input Current<br>Trigger Pulse Required to Trigger                                                                               | 2.0<br>5   | 2.3<br>25         | 2.6<br>100   | V<br>μA    |  |

| Envelope                                                                                                                                                | +1.1       | +1.3              | +1.5         | <b>Κ</b> Ω |  |

| Trigger Input Impedance                                                                                                                                 | 2.4        | 3                 | 4            |            |  |

| Time Control Input Current                                                                                                                              | 0.5        | 400               | 2500         | nA         |  |

| Sustain Control Input Current                                                                                                                           | 150        |                   | 800          | nĄ         |  |

| Attack Output Signal                                                                                                                                    | 4          | 8                 | <b>-1.2</b>  | V          |  |

| Output Current Sink Capability                                                                                                                          | 420        | 560               | 700          | μΑ         |  |

| Buffer Output Impedance                                                                                                                                 | 100        | 200               | 350          | Ω          |  |

| Positive Supply Voltage Range                                                                                                                           | +12.5      |                   | +18          | V          |  |

| Negative Supply Voltage Range <sup>4</sup>                                                                                                              | -4.5       |                   | -18          | V          |  |

| Supply Current                                                                                                                                          | 5.6        |                   | 9.4          | mA         |  |

- Note 1: Scale factor determined at mid-range. Spec represents total deviation from ideal at range extremities.

- Note 2: Output is at either sustain final voltage or release final voltage.  $V_{CA,D,R}$  varies 0 to -240mV.

- Note 3: Spec represents the difference between the actual final voltages (attack asymptote voltage, sustain final voltage, and release final voltage in the case of attack, decay, and release respectively) and the apparent voltage to which the output seems to be approaching asymptotically.

- Note 4: Current limiting resistor required when  $V_{\mbox{EE}} > -6.0$  volts.

- Note 5: Spec also represents time constant variation between units for  $V_{CA,D,R} = 0$ .

## **Application Hints**

### Supply

Since the device can withstand no more than 24 volts between its supply pins, an internal 6.5 volt ± 10% zener diode has been provided to allow the chip to run off virtually any negative supply voltage. If the negative supply is between -4.5 and -6.0 volts, it may be connected directly to the negative supply pin (pin 6). For voltages greater than -7.5 volts, a series current limiting resistor must be added between pin 6 and the supply. Its value is calculated as follows:

REE = (VEE - 7.2)/.010.

The circuit was designed for a positive supply of +15 volts.

Voltages other than +15 volts will cause the peak threshold voltage to be either at a minimum of .33VCC or at a maximum of 5.5 volts.

#### Gate and Trigger Inputs

The gate input is referenced to ground and therefore will accept any ground referenced TTL or CMOS logic level up to +18 volts. If the gate pin is left floating, it will be interpreted as a high level. The trigger input is referenced to the VEE pin (pin 6) and therefore, a ground referenced trigger pulse should be capacitively coupled to the trigger input pin (pin 5).

## Input Control Voltages

As the scale sensitivity on the three time control inputs is 60mV/decade, attenuation of the incoming control voltages will in most cases be required. Four decades of control requires only a 240mV voltage excursion. The more negative the voltages the longer the times. For best scale accuracy at the shortest times, the impedance at the time control pins should be kept low. At the shortest times (corresponding to  $200~\mu\text{A}$  of peak

## **Absolute Maximum Ratings**

current), every  $100\Omega$  will cause a 1% increase in control scale error. As the times are increased. this error will decrease in direct proportion.

The voltage applied to the sustain level control input will directly determine the sustain voltage of the output envelope (minus the sustain final voltage error). Voltages greater than the threshold voltage will cause the envelope to ramp up to this higher voltage when the peak threshold is reached. The rate at which this occurs will be equal to the fastest attack rate.

Since all four control inputs are connected only to the bases of NPN transistors, the control input pins of tracking units may be simply tied together. Therefore, in the case of the time control inputs, only one attenuator network is required to control the same parameter in a multiple chip system.

## Selection of Rx and Cx

As is shown in the envelope equations, the RC time constant of the attack, decay and release curves is given by RXCX times the exponential multiplier, exp(-VC/VT). Practical circuit limitations determine Rx and the multiplier, from which Cx can then be calculated. The peak capacitor charging and discharging currents is given by (V7/ RX)exp(VCA/VT), (VCS/RX) exp(VCD/VT), and (Vp/RX)exp (VCR/VT) for the attack, decay, and release phases respectively. For the best scale accuracy and tracking at the shortest times, these currents should be kept less than 100  $\mu$ A, and in all cases they should not be allowed to exceed 300  $\mu$ A. This sets the minimum value for Rx at 24K. Larger values of Rx will allow positive time control voltages to be used. However, as can also be

| Voltage Between V <sub>CC</sub> and V <sub>EE</sub> Pins    | 24V                                |  |

|-------------------------------------------------------------|------------------------------------|--|

| Voltage Between $V_{\hbox{\scriptsize CC}}$ and Ground Pins | +18V                               |  |

| Voltage Between VEE and Ground Pins                         | -6.0V                              |  |

| Current Into VEE Pin                                        | ±50mA                              |  |

| Voltage Between Control and Ground Pins                     | ±6.0V                              |  |

| Voltage to Gate and Trigger Input Pins                      | V <sub>EE</sub> to V <sub>CC</sub> |  |

| Storage Temperature Range                                   | –55°C to +150°C                    |  |

| Operating Temperature Range                                 | -25°C to +75°C                     |  |

seen from the envelope equations, the sustain/final voltage error, the asymptote error, and the control voltage feedthrough are all affected by Rx. A practical maximum of 240K is recommended for Rx when the internal buffer is used and 1M if an external FET buffer is used.

### Trimming the Envelope Times

The RC time constants of the output envelope will typically track to within ± 15% from unit to unit, even at the longest time settings. If better tracking is required, the best method for trimming the time constants is to simply adjust Rx with a trimming potentiometer.

#### Output Drive Capability

The buffer output can sink at least 400 µA and can source up to 10mA, but with considerable degradation in performance. An output load no less than 20K to ground is recommended.

The buffer has a somewhat high output impedance. As a result of this, small steps (50mV) appear in the output waveform at the phase transitions, due to the sudden change in drive the output must provide to Rx. The largest step is at the beginning of the envelope and is given by  $(R_O/R_X)V_Z$ . It may be decreased by increasing Rx, lowering RO, or using an external buffer with a low output impedance. Ro may be lowered by adding a resistor from the output pin to VEE. However, every 1mA of current drawn from the output pin may increase the buffer input current as much as 5-6 nA with consequent degradation in performance.

## **Envelope Equations**

#### Attack Curve

$$V_{OA} = V_Z \left(1 - \exp\left(-\frac{t}{R_X C_X} e^{V_{CA}/V_T}\right)\right)$$

### **Decay Curve**

$$V_{OD} = (V_P - V_{CS}) \exp(-\frac{t}{R_X C_X} e^{V_{CD}/V_T}) + V_{CS}$$

## Release Curve

$$V_{OR} = V_{CS} \exp(-\frac{t}{R_X C_X} e^{V_{CR}/V_T})$$

## Sustain/Release Final Voltage Error

$$\epsilon_F = V_{OS} + I_{B1}R_X - I_{B2}R_X/1 + e^{V_{CA}/V_T}$$

### Attack/Decay/Release Asymptote Error

$$\epsilon_{A}$$

= V<sub>OS</sub> + I<sub>B1</sub>R<sub>X</sub> - I<sub>B2</sub>R<sub>X</sub> e V<sub>CA,D,R</sub>/V<sub>T</sub>

V<sub>CA</sub> = Attack Control Voltage

V<sub>CD</sub> = Decay Control Voltage

VCB = Release Control Voltage

V<sub>CS</sub> = Sustain Control Voltage

Vos = Op Amp Offset

IB1 = Op Amp Input Current

IB2 = Buffer Input Current

V<sub>2</sub> = Attack Asymptote Voltage

V<sub>P</sub> = Envelope Peak Voltage

$V_T = kT/q$

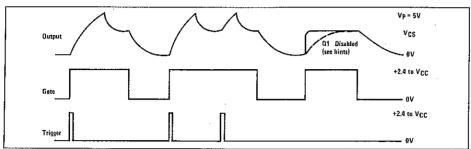

## **Input and Output Waveforms**

#### Use of External Buffer

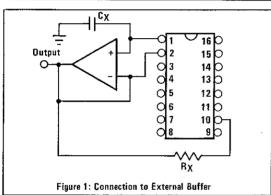

For various reasons, it may be desired to use an external buffer. One possible benefit might be a lower input bias current (1g2), with consequent improvement in the associated errors. The external buffer should be connected as shown in Figure 1. For proper operation, the buffer used should be capable of sourcing at least 700  $\mu$ A and should have a positive current flowing into the input pin, such as that resulting from NPN or P channel JFET inputs.

## Disabling the Control Voltage Rejection Circuit

The purpose of Q1 (see block diagram) is to greatly reduce the control voltage feedthrough. During the attack phase, the base of Q1 is brought negative effectively disabling it and allowing Q2 to control the charging current. During the decay and release phases, however, the base of Q1 is at ground, causing negative voltage excursions on the base of Q2 to vary the charging current only a maximum of 2:1 (as opposed to the normal 10,000:1 or greater). Under normal triggering conditions (applying a trigger and a gate), this has no consequence, except to reduce the attack control voltage feedthrough to a negligible amount. However, if only a gate is applied with no trigger, the output will ramp up to the sustain level, approaching it asymptotically with a RC time

constant of R<sub>X</sub>C<sub>X</sub>(exp(V<sub>CA</sub>/V<sub>T</sub>) + 1) (i.e. a rapid attack with only a 2:1 control range). To provide the normal full range of attack control under this mode of operation, Q1 should be disabled by connecting a resistor from pin 16 to V<sub>EE</sub> to generate at least -500mV at the base of Q2. This resistance may be calculated as follows:

#### $R = 1100(2V_{EE}-1)$

The result will be 5,000 times or more sustain and release final voltage shift with the attack control voltage. If external circuitry is added to apply the -500 mV only when the gate is high, then only the sustain final voltage will exhibit significant shift

## Use of the Attack and Threshold Voltage Output Pins

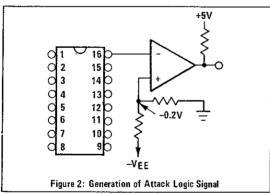

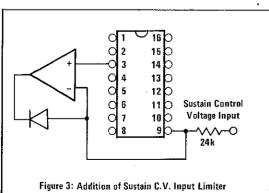

The attack output pin (pin 16) and the peak threshold voltage pin (pin 3) have been provided to allow additional flexibility. Since pin 16 outputs a -.4 to -1.2 volts only during the attack phase, it may be used to provide a logic signal which indicates the attack phase (see figure 2). This signal may be ANDed with the gate to provide a logic signal indicating the decay phase. As was mentioned above, a sustain control voltage greater than the threshold voltage will result in a "jump" to the sustain level. By using the threshold voltage pin as shown in figure 3, the sustain voltage can be prevented from rising above the envelope peak, thus eliminating this undesirable effect. (This effect can also be eliminated by disabling the control voltage rejection circuit as described above).