## **Digital Compensator**

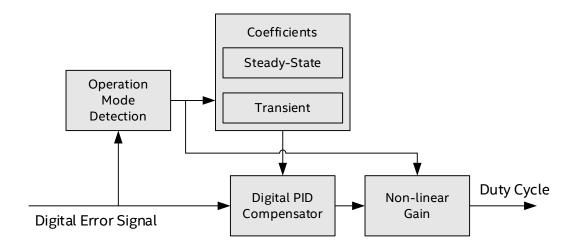

The sampled output voltage is processed by a digital control loop in order to modulate the DPWM output signals controlling the power stage. The advanced digital control loop works as a voltage-mode controller using a PID-type compensator. The basic structure of the controller is shown in Figure 5. The ED8401 controller features two parallel compensators for steady-state operation and fast transient operation. Fast, reliable switching between the different compensation modes ensures good transient performance and quiet steady state performance.

The ED8401 uses over-sampling techniques to acquire fast, accurate, and continuous information about the output voltage so that the device can react quickly to any changes in output voltage.

## Figure 5: Simplified Block Diagram Of The Digital Compensation

## Power Supply Circuitry, Reference Decoupling, and Grounding

The ED8401 incorporates several internal voltage regulators in order to derive all required supply and bias voltages from a single external supply voltage. This supply voltage can be either 5V or 3.3V depending on whether the internal 3.3V regulator is used. If the internal 3.3V regulator is not used, 3.3V must be supplied to VDD33 and VDD50 pins respectively. Decoupling capacitors are required at the VDD33, VDD18, and AVDD18 pins (1.0 $\mu$ F minimum; 4.7 $\mu$ F recommended). If the 5.0V supply voltage is used, i.e. the internal 3.3V regulator is used, a small load current can be drawn from the VDD33 pin. This can be used to supply pull-up resistors, for example. The specified minimum capacitance must take into account temperature and voltage therefore a high-quality dielectric like X7R is recommende.

| Table 5. Decoupting Capacitors |                     |               |          |

|--------------------------------|---------------------|---------------|----------|

| Pin #                          | Pin Name            | Value         | Note     |

| 2                              | VREFP               | 100nF         | Required |

| 36                             | VDD18               | 1μF (minimum) | Required |

| 37                             | VDD33               | 1μF (minimum) | Required |

| 38                             | VDD50               | 1µF(minimum)  | Required |

| 39                             | AVDD18              | 1μF (minimum) | Required |

| 40                             | ADCVREF             | 100nF         | Required |

| 2,40                           | VREFP to<br>ADCVREF | 51Ω           | Required |

## **Table 5: Decoupling Capacitors**