# AN4861 Application note

LCD-TFT display controller (LTDC) on STM32 MCUs

### Introduction

The evolution of the mobile, industrial and consumer applications leads to a stronger need of graphical user interfaces (GUIs) and to an increase in the required hardware resources. These applications require higher quality graphics, more hardware and software resources (like memory for graphical primitives or framebuffer) and higher processing performances.

To respond to this increasing demand, microprocessor units are often used, which leads to a higher costs and to more complex designs with longer time to market. To face these requirements, the STM32 MCUs offer a large graphical portfolio.

Thanks to their embedded LCD-TFT display controller (LTDC), the STM32 MCUs allow to directly drive high-resolution display panels without any CPU intervention. In addition, the LTDC can access autonomously to internal memories or external memories to fetch pixel data.

This application note describes the LCD-TFT display controller of the STM32 microcontrollers listed in *Table 1* and demonstrates how to use and configure the LTDC peripheral. It also highlights some hardware, software and architectural considerations to obtain the best graphical performances.

# **Related documents**

Available from STMicroelectronics web site www.st.com:

- STM32F75xxx and STM32F74xxx advanced ARM<sup>®</sup>-based 32-bit MCUs (RM0385)

- STM32F76xxx and STM32F77xxx advanced ARM<sup>®</sup>-based 32-bit MCUs (RM0410)

- STM32F469xx and STM32F479xx advanced ARM<sup>®</sup>-based 32-bit MCUs (RM0386)

- STM32F405/415, STM32F407/417, STM32F427/437 and STM32F429/439 advanced ARM<sup>®</sup>-based 32-bit MCUs (RM0090)

- STM32F429/439, STM32F469/479, STM32F7x6, STM32F7x7, STM32F7x8, STM32F7x9 datasheets

| Туре             | Product lines                                                               |

|------------------|-----------------------------------------------------------------------------|

| Mucrocontrollers | STM32F429/439, STM32F469/479,<br>STM32F7x6, STM32F7x7, STM32F7x8, STM32F7x9 |

#### Table 1. Applicable products

# Contents

| 1 | Display and graphics overview |           |                                                                               |    |

|---|-------------------------------|-----------|-------------------------------------------------------------------------------|----|

|   | 1.1                           | Basic gr  | raphics concepts                                                              | 8  |

|   | 1.2                           | Display   | interface standards                                                           | 11 |

|   | 1.3                           | Display   | interfaces supported by STM32 MCUs                                            | 13 |

| 2 | Overv                         | view of I | LTDC controller and STM32 MCUs graphical portfolio . 1                        | 5  |

|   | 2.1                           | LCD-TF    | T display controller on STM32 MCUs 1                                          | 15 |

|   | 2.2                           | LTDC a    | vailability and graphic portfolio across STM32 families                       | 15 |

|   | 2.3                           | LTDC in   | a smart architecture                                                          | 16 |

|   | 2.4                           | Advanta   | ages of using an STM32 LTDC controller                                        | 19 |

| 3 | LCD-                          | TFT (LTI  | DC) display controller description                                            | 20 |

|   | 3.1                           | Function  | nal description                                                               | 20 |

|   |                               | 3.1.1     | LTDC clock domains                                                            | 20 |

|   |                               | 3.1.2     | LTDC reset                                                                    | 20 |

|   | 3.2                           | Flexible  | timings and hardware interface 2                                              | 21 |

|   |                               | 3.2.1     | LCD-TFT pins and signal interface                                             | 21 |

|   |                               | 3.2.2     | Fully programmable timings for different display sizes                        | 22 |

|   | 3.3                           | Two pro   | grammable LTDC layers 2                                                       | 25 |

|   |                               | 3.3.1     | Flexible window position and size configuration                               | 26 |

|   |                               | 3.3.2     | Programmable layer: color framebuffer                                         | 27 |

|   | 3.4                           | Interrup  | ts                                                                            | 29 |

|   | 3.5                           | Low-pov   | wer modes                                                                     | 29 |

| 4 | Creat                         | ing a gr  | aphical application with LTDC                                                 | 31 |

|   | 4.1                           | Determi   | ning graphical application requirements                                       | 31 |

|   | 4.2                           |           | ig the display size and color depth compatibility hardware configuration      | 31 |

|   |                               | 4.2.1     | Framebuffer memory size requirements and location                             | 31 |

|   |                               | 4.2.2     | Checking display compatibility considering the memory bandwidth requirements  | 33 |

|   |                               | 4.2.3     | Check the compatibility of the display panel interface with the LTDC $\ldots$ | 39 |

|   | 4.3                           | STM32     | package selection guide                                                       | 40 |

|   | 4.4   | LTDC s  | ynchronization with DMA2D and CPU                                                 |

|---|-------|---------|-----------------------------------------------------------------------------------|

|   |       | 4.4.1   | DMA2D usage                                                                       |

|   |       | 4.4.2   | LTDC and DMA2D/CPU synchronization                                                |

|   | 4.5   | Graphic | performance optimization 42                                                       |

|   |       | 4.5.1   | Memory allocation                                                                 |

|   |       | 4.5.2   | Optimizing the LTDC framebuffer fetching from external memories (SDRAM or SRAM)43 |

|   |       | 4.5.3   | Optimizing the LTDC framebuffer fetching from SDRAM                               |

|   |       | 4.5.4   | Framebuffer content update during BLANKING period                                 |

|   | 4.6   | Special | recommendations for Cortex <sup>®</sup> -M7 (STM32F7 Series)                      |

|   |       | 4.6.1   | Disable FMC bank1 if not used                                                     |

|   |       | 4.6.2   | Configure the memory protection unit (MPU)                                        |

|   | 4.7   | LTDC p  | eripheral configuration                                                           |

|   |       | 4.7.1   | Display panel connection                                                          |

|   |       | 4.7.2   | LTDC clocks and timings configuration54                                           |

|   |       | 4.7.3   | LTDC layer(s) configuration                                                       |

|   |       | 4.7.4   | Display panel configuration57                                                     |

|   | 4.8   | Storing | graphic primitives                                                                |

|   |       | 4.8.1   | Converting images to C files                                                      |

|   | 4.9   | Hardwa  | re considerations                                                                 |

| 5 | Savin | g powe  | r consumption 60                                                                  |

| 6 |       | annlica | ation examples                                                                    |

| U |       | ••      | •                                                                                 |

|   | 6.1   | •       | entation examples and resources requirements                                      |

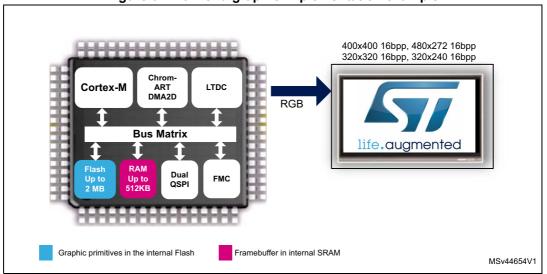

|   |       | 6.1.1   | Single chip MCU                                                                   |

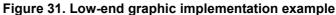

|   | 0.0   | 6.1.2   | MCU with external memory                                                          |

|   | 6.2   |         | e: creating a basic graphical application                                         |

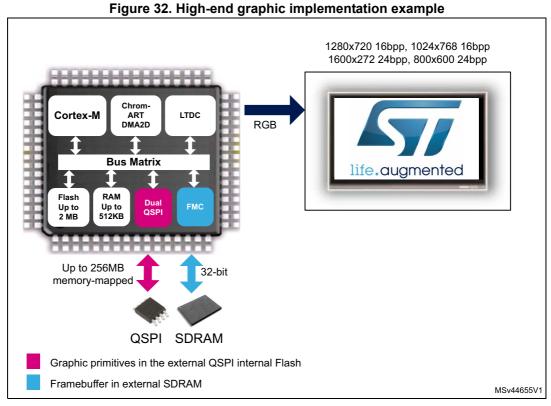

|   |       | 6.2.1   | Hardware description                                                              |

|   |       | 6.2.2   | How to check if a specific display size matches the hardware configuration        |

|   |       | 6.2.3   | LTDC GPIOs configuration                                                          |

|   |       | 6.2.4   | LTDC peripheral configuration                                                     |

|   |       | 6.2.5   | Displaying an image from the internal Flash                                       |

|   |       | 6.2.6   | FMC SDRAM configuration81                                                         |

|   |       |         |                                                                                   |

|   |       | 6.2.7   | MPU and cache configuration                                                       |

| 7  | Supported display panels   | 87 |

|----|----------------------------|----|

| 8  | Frequently asked questions | 88 |

| 9  | Conclusion                 | 89 |

| 10 | Revision history           | 90 |

# List of tables

| Table 1.  | Applicable products                                                                | 1    |

|-----------|------------------------------------------------------------------------------------|------|

| Table 2.  | Display interfaces supported by STM32 MCUs                                         | . 13 |

| Table 3.  | STM32 MCUs embedding an LTDC and their available graphic portfolio                 | . 15 |

| Table 4.  | Advantages of using STM32 MCUs LTDC controller                                     | . 19 |

| Table 5.  | LTDC interface output signals                                                      | . 21 |

| Table 6.  | LTDC timing registers                                                              | . 22 |

| Table 7.  | LTDC interrupts summary                                                            |      |

| Table 8.  | LTDC peripheral state versus STM32 low-power modes                                 |      |

| Table 9.  | Framebuffer size for different screen resolutions                                  | . 32 |

| Table 10. | STM32F4x9 with HCLK @ 180 MHz and SDRAM @ 90 MHz                                   |      |

|           | maximal supported pixel clock versus LTDC configuration and SDRAM bus width        | . 37 |

| Table 11. | STM32F7x6, STM32F7x7, STM32F7x8 and STM32F7x9 with HCLK @ 200 MHz and              |      |

|           | SDRAM@ 100 MHz maximal supported pixel clock versus                                |      |

|           | LTDC configuration and SDRAM bus width                                             |      |

| Table 12. | Example of supported display resolutions in specific STM32 hardware configurations | . 39 |

| Table 13. | STM32 packages with LTDC peripheral versus                                         |      |

|           | RGB interface availability                                                         |      |

| Table 14. | LCD-TFT timings extracted from ROCKTECH RK043FN48H datasheet                       |      |

| Table 15. | Programming LTDC timing registers.                                                 |      |

| Table 16. | Example of graphic implantations with STM32 in different hardware configurations   | . 63 |

| Table 17. | STM32 reference boards with embedding LTDC                                         |      |

|           | and featuring an on-board LCD-TFT panel.                                           | . 86 |

| Table 18. | Frequently asked questions                                                         |      |

| Table 19. | Document revision history                                                          | . 90 |

|           |                                                                                    |      |

# List of figures

| Figure 1.         | Basic embedded graphic system                                                          |      |

|-------------------|----------------------------------------------------------------------------------------|------|

| Figure 2.         | Display module with embedded controller and GRAM                                       | 9    |

| Figure 3.         | Display module without controller nor GRAM                                             |      |

| Figure 4.         | Display module without controller nor GRAM and with external framebuffer               | . 10 |

| Figure 5.         | MIPI-DBI type A or B interface                                                         | . 11 |

| Figure 6.         | MIPI-DBI type C interface                                                              | . 11 |

| Figure 7.         | MIPI-DPI interface                                                                     | . 12 |

| Figure 8.         | MIPI-DSI interface                                                                     | . 12 |

| Figure 9.         | LTDC AHB master in STM32F429/439 and STM32F469/479 lines smart architecture            | 17   |

| Figure 10.        | LTDC AHB master in STM32F7x6, STM32F7x7, STM32F7x8 and STM32F7x9                       | . 17 |

| rigule to.        | smart architecture                                                                     | 18   |

| Figure 11.        | LTDC Block digram.                                                                     |      |

| Figure 12.        | LTDC signal interface                                                                  |      |

| -                 | Typical LTDC display frame (active width = 480 pixels)                                 |      |

| Figure 13.        |                                                                                        |      |

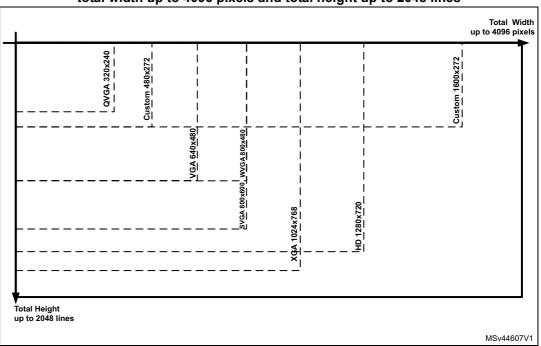

| Figure 14.        | Fully programmable timings and resolutions                                             | . 24 |

| Figure 15.        | LTDC fully programmable display resolution with                                        | 25   |

| <b>Eigener 10</b> | total width up to 4096 pixels and total height up to 2048 lines                        |      |

| Figure 16.        | Blending two layers with a background                                                  |      |

| Figure 17.        | Layer window programmable size and position                                            |      |

| Figure 18.        | Pixel data mapping versus color format                                                 |      |

| Figure 19.        | Programmable color layer in framebuffer                                                | . 28 |

| Figure 20.        | Pixel format conversion from RGB565 input pixel format to the internal ARGB8888 format |      |

| Figure 21.        | AHB masters concurrent access to SDRAM.                                                | . 34 |

| Figure 22.        | Typical graphic hardware configuration with external SDRAM                             | . 36 |

| Figure 23.        | Double buffering: synchronizing LTDC with DMA2D or CPU                                 | . 42 |

| Figure 24.        | Example of taking advantage from memory slaves split                                   |      |

|                   | on the STM32F4x9 line MCUs                                                             | . 43 |

| Figure 25.        | Burst access crossing the kilobyte boundary                                            | . 44 |

| Figure 26.        | Reducing layer window and framebuffer line widths                                      | . 45 |

| Figure 27.        | Adding dummy bytes to make the line width multiple of 64 bytes                         | . 47 |

| Figure 28.        | Placing the two buffers in independent SDRAM banks                                     |      |

| Figure 29.        | FMC SDRAM and NOR/PSRAM memory swap at default                                         |      |

| -                 | system memory map (MPU disabled).                                                      | . 51 |

| Figure 30.        | Connecting an RGB666 display panel                                                     | . 53 |

| Figure 31.        | Low-end graphic implementation example                                                 | . 62 |

| Figure 32.        | High-end graphic implementation example                                                |      |

| Figure 33.        | Graphic hardware configuration in the STM32F746G-DISCO                                 | . 64 |

| Figure 34.        | LCD-TFT connection in the STM32F746G-DISCO board                                       |      |

| Figure 35.        | Backlight controller module                                                            | . 66 |

| Figure 36.        | STM32CubeMX: LTDC GPIOs configuration                                                  | . 68 |

| Figure 37.        | STM32CubeMX: PJ7 pin configuration to LTDC_G0 alternate function                       | . 68 |

| Figure 38.        | STM32CubeMX: LTDC configuration                                                        | . 69 |

| Figure 39.        | STM32CubeMX: LTDC GPIOs output speed configuration                                     | . 69 |

| Figure 40.        | STM32CubeMX: display enable pin (LCD_DISP) configuration                               |      |

| Figure 41.        | STM32CubeMX: setting LCD_DISP pin output level to high                                 |      |

| Figure 42.        | STM32CubeMX: enabling LTDC global and error interrupts                                 |      |

| -                 |                                                                                        |      |

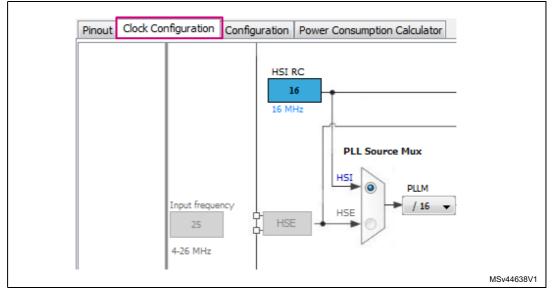

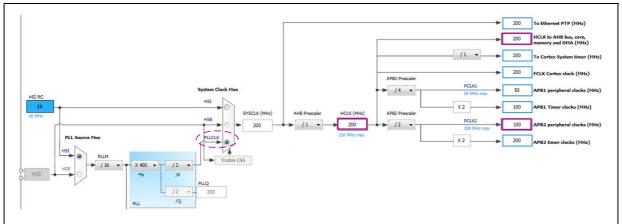

| Figure 43. | STM32CubeMX: clock configuration tab            | 72 |

|------------|-------------------------------------------------|----|

| Figure 44. | STM32CubeMX: System clock configuration         | 72 |

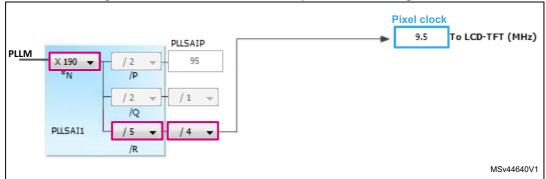

| Figure 45. | STM32CubeMX: LTDC pixel clock configuration     | 73 |

| Figure 46. | STM32CubeMX: LTDC timing configuration.         |    |

| Figure 47. | STM32CubeMX: LTDC Layer1 parameters setting     | 76 |

| Figure 48. | LCD Image Converter: home page                  | 77 |

| Figure 49. | LCD Image Converter: image project              | 78 |

| Figure 50. | LCD Image Converter: setting conversion options | 78 |

| Figure 51. | LCD Image Converter: generating the header file | 79 |

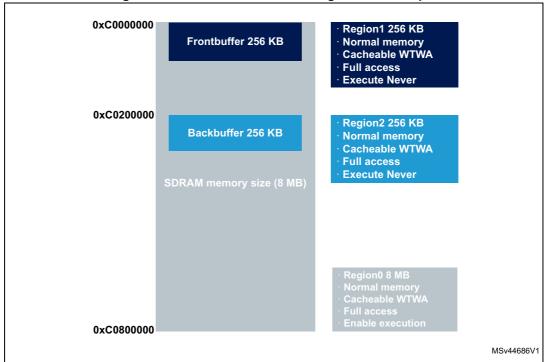

| Figure 52. | FMC SDRAM MPU configuration example             | 82 |

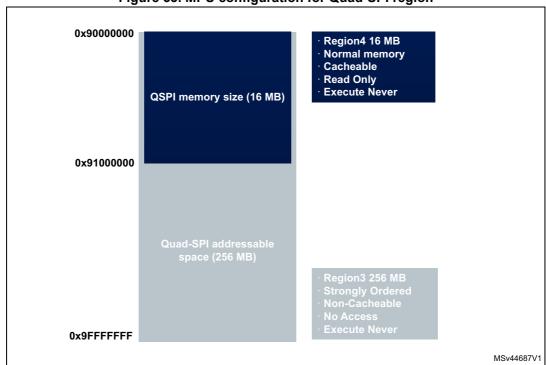

| Figure 53. | MPU configuration for Quad-SPI region           | 83 |

# 1 Display and graphics overview

This section describes the basic terms used on the displays and graphics context in order to provide an overview of the general display and graphics environment. This section also summarizes the display interfaces supported by the STM32 MCUs.

## 1.1 Basic graphics concepts

This section describes a basic embedded graphic system, the display module categories and the display technologies.

#### Basic embedded graphic system

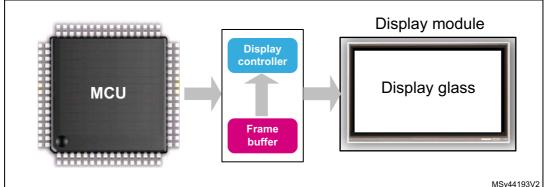

A basic embedded graphic system can be schematized as described in *Figure 1*.

A basic embedded graphic system is composed of a microcontroller, a framebuffer, a display controller and a display glass.

• The microcontroller computes the image to be displayed in the framebuffer, assembling graphical primitives such as icons or images. The CPU performs this operation by running a graphical library software. This process can be accelerated by a dedicated hardware like the DMA2D Chrom-Art Accelerator<sup>®</sup>, used by the graphical library. The more often the framebuffer is updated, the more fluent the animations are (animation fps).

- The framebuffer is a volatile memory used to store pixel data of the image to be displayed. This memory is usually called the graphic RAM (GRAM). The required size of the framebuffer depends on the resolution and color depth of the display. See *Section 4.2.1: Framebuffer memory size requirements and location* for more information on the required size of the framebuffer.

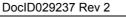

- Double buffering is a technique which uses double framebuffers to avoid displaying what is being written to the framebuffer.

- The display controller is continuously "refreshing" the display, transferring the framebuffer content to the display glass 60 times per second (60 Hz). The display controller can be embedded either in the display module or in the MCU.

- The display glass is driven by the display controller and is the responsible to display the image (which is composed of a matrix of pixels).

A display is characterized by:

- Display size (resolution): is defined by the number of pixels of the display which is represented by horizontal (pixels number) x vertical (lines number).

- Color depth: defines the number of colors in which a pixel can be drawn. It is represented in bits per pixel (bpp). For a color depth of 24 bpp (which can also be represented by RGB888) a pixel can be represented in 16777216 colors.

- Refresh rate (in Hz): is the number of times per second that the display panel is refreshed. A display shall be refreshed 60 times per seconds (60 Hz) since lower refresh rate creates bad visual effects.

#### **Display module categories**

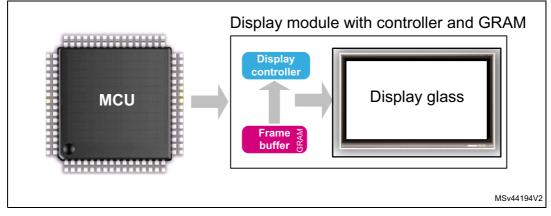

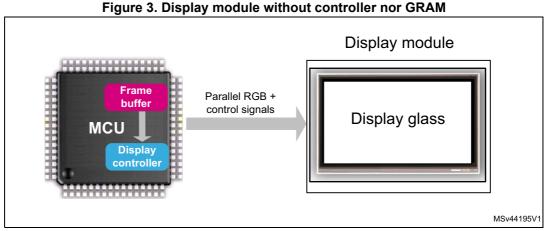

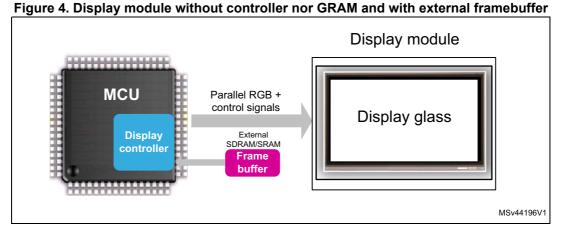

The display modules are classified in two main categories, depending on whether they embed or not an internal controller and a GRAM.

- The first category corresponds to the displays with an on-glass display controller and a GRAM (see *Figure 2*).

- The second category corresponds to the displays with an on-glass display with no main controller and that have only a low-level timing controller. To interface with displays without controller nor GRAM the used framebuffer may be located in the MCU's internal SRAM (see *Figure 3*) or located in an external memory (see *Figure 4*).

Figure 2. Display module with embedded controller and GRAM

#### **Display technologies**

There are many display technologies available on the market, the two main technologies used are described below:

- LCD-TFT displays (liquid crystal display thin film transistor): is a variant of LCD that uses the TFT technology to improve the control of each pixel. Thanks to the TFT technology, each pixel can be controlled by a transistor, allowing a fast response time and an accurate color control.

- OLED displays (organic LED): the pixels are made of organic LEDs emitting directly the light, offering a better contrast and an optimized consumption. The OLED technology enables the possibility to use flexible displays, as no glass nor backlight are required. The response time is very fast and the viewing angle is free as it does not depend on any light polarization.

The way of driving the display module is quite similar in TFT and OLED technologies, the main difference is in the backlight requirement, as the OLED is not requiring any.

## 1.2 Display interface standards

The MIPI (mobile industry processor interface) Alliance is a global, collaborative organization committed to define and promote interface specifications for mobile devices. The MIPI Alliance develops new standards but also standardizes the existing display interfaces:

#### MIPI display bus interface (MIPI-DBI)

The MIPI-DBI is one of the first display standards published by the MIPI Alliance to specify the display interfaces. The three types of interfaces defined inside the MIPI-DBI are:

- Type A: based on Motorola 6800 bus

- Type B: based on Intel<sup>®</sup> 8080 bus

- Type C: based on SPI protocol

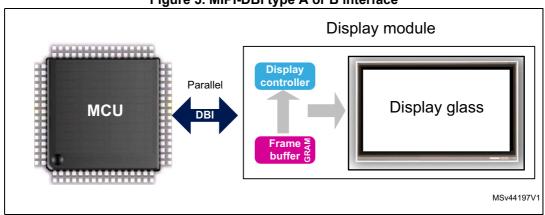

The MIPI-DBI is used to interface with a display with an integrated graphic RAM (GRAM). The pixel data is updated in the local GRAM of the display. *Figure 5* illustrates a MIPI-DBI type A or B display interfacing example.

Figure 5. MIPI-DBI type A or B interface

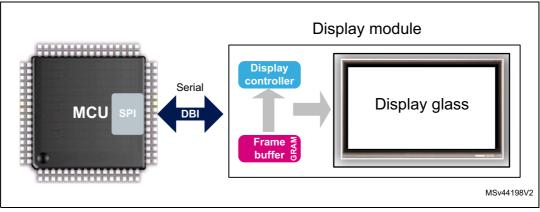

*Figure 6* illustrates a MPI-DBI type C display interfacing example.

#### Figure 6. MIPI-DBI type C interface

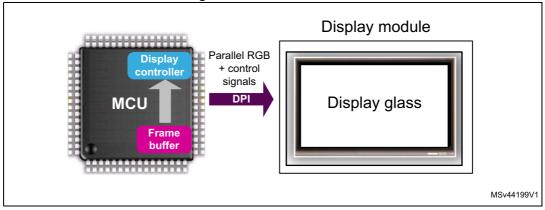

#### MIPI display parallel interface (MIPI-DPI)

The DPI standardizes the interface through a TFT controller. An example is when using a 16 to 24-bit RGB signaling in conjunction with synchronization signals (HSYNC, VSYNC, EN and LCD\_CLK).

The DPI is used to interface with a display without a framebuffer. The pixel data must be streamed real time to the display.

The real-time performance is excellent, but it requires a high bandwidth in the MCU to feed the display.

Figure 7. MIPI-DPI interface

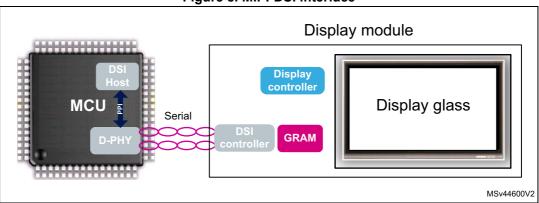

#### MIPI display serial interface (MIPI-DSI)

In order to decrease the number of lines to interface with a display, the MIPI Alliance has defined the DSI. The DSI is a high bandwidth multi-lane differential link; it uses standard MIPI D-PHY for the physical link.

The DSI encapsulates either DBI or DPI signals and transmits them to the D-PHY through the PPI protocol.

*Figure 8* illustrates a MPI-DSI display interfacing example.

#### Figure 8. MIPI-DSI interface

# 1.3 Display interfaces supported by STM32 MCUs

Here below a summary on the MIPI Alliance display interfaces supported by the STM32 MCUs:

- All STM32 MUCs support the MIPI-DBI type C (SPI) interface

- All STM32 MCUs with F(S)MC support the MIPI-DBI type A and B interfaces

- The STM32 MCUs with LTDC support the MIPI-DPI interface

- The STM32 MCUs embedding a DSI host support the MIPI-DSI interface

*Table 2* illustrates and summarizes the display interfaces supported by the STM32 microcontrollers.

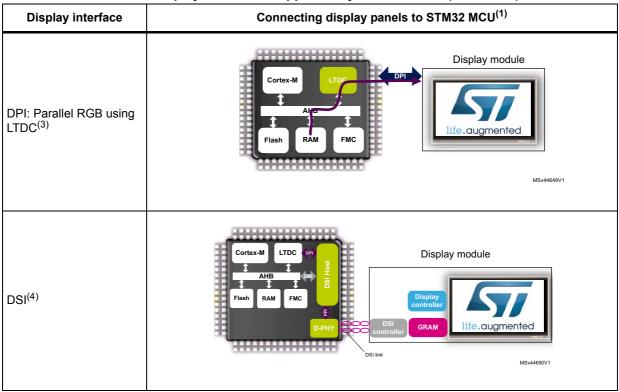

| Display                  | interface                                                 | Connecting display panels to STM32 MCU <sup>(1)</sup> |

|--------------------------|-----------------------------------------------------------|-------------------------------------------------------|

|                          | Motorola<br>6800<br>DBI Type A                            | Display module                                        |

| Intel 8080<br>DBI Type B | AHB<br>Flash RAM FMC DEL GRAM Life.cugmented<br>MS44647V1 |                                                       |

| DBI <sup>(2)</sup>       | SPI<br>DBI Type C                                         | Display module                                        |

#### Table 2. Display interfaces supported by STM32 MCUs

#### Table 2. Display interfaces supported by STM32 MCUs (continued)

1. Purple arrows show the pixel data path to the display.

2. For more information on how to support Motorola 6800 and Intel 8080 with STM32's F(S)MC, refer to the application note *TFT LCD interfacing with the high-density STM32F10xxx FSMC* (AN2790).

3. All other STM32 MCUs with no LTDC peripheral can directly drive LCD-TFT panels using FSMC and DMA. Refer to application note QVGA TFT-LCD direct drive using the STM32F10xx FSMC peripheral (AN3241).

4. Only the STM32 MCUs indicated in *Table 3* embedding a DSI Host can support the DSI interface. Refer to application note *DSI Host on STM32 microcontrollers* (AN4860) for more information.

# 2 Overview of LTDC controller and STM32 MCUs graphical portfolio

This section illustrates the LTDC controller benefits and summarizes the graphical portfolio of the STM32 microcontrollers.

### 2.1 LCD-TFT display controller on STM32 MCUs

The LTDC on the STM32 microcontrollers is an on-chip LCD display controller that provides up to 24-bit parallel digital RGB signals to interface with various display panels. The LTDC can also drive other display technologies with parallel RGB interface like the AMOLED displays. The LTDC allows interfacing with low-cost display panels which do not embed neither a controller nor a graphic RAM.

# 2.2 LTDC availability and graphic portfolio across STM32 families

*Table 3* summarizes the STM32 embedding an LTDC and details the corresponding available graphic portfolio.

| STM32 lines             | FLASH<br>(bytes) | On<br>chip<br>SRAM<br>(bytes) | Quad-<br>SPI <sup>(1)</sup> | Max AHB<br>frequency<br>(MHz) <sup>(2)</sup> | Max FMC<br>SRAM<br>and<br>SDRAM<br>frequency<br>(MHz) | Max<br>pixel<br>clock<br>(MHz)<br><sup>(3)</sup> | JPEG<br>codec | DMA2D<br>(4) | MIPI<br>-DSI<br>host<br>(5) | Graphic<br>libraries |

|-------------------------|------------------|-------------------------------|-----------------------------|----------------------------------------------|-------------------------------------------------------|--------------------------------------------------|---------------|--------------|-----------------------------|----------------------|

| STM32F429/<br>439       | Up to<br>2 M     | 256 k                         | No                          | 180                                          | 90                                                    | 83                                               | No            | Yes          | No                          |                      |

| STM32F469/<br>479       | Up to<br>2 M     | 384 k                         | Yes                         | 180                                          | 90                                                    | 83                                               | No            | Yes          | Yes                         | TouchGFX<br>Embedded |

| STM32F7x6               | Up to<br>1 M     | 320 k                         | Yes                         | 216                                          | 100                                                   | 83                                               | No            | Yes          | No                          | wizard<br>SEGGER     |

| STM32F7x7               | L In to          |                               | Yes                         | 216                                          | 100                                                   | 83                                               | Yes           | Yes          | No                          | STemWin              |

| STM32F7x8/<br>STM32F7x9 | Up to<br>2 M     | 512 k                         | Yes                         | 216                                          | 100                                                   | 83                                               | Yes           | Yes          | Yes                         |                      |

#### Table 3. STM32 MCUs embedding an LTDC and their available graphic portfolio

1. The Quad-SPI interface allows interfacing with external memories in order to extend the size of the application. For more details on STM32 MCUs QSPI interface refer to application note *Quad-SPI (QSPI) interface on STM32 microcontrollers* (AN476).

2. LTDC fetches graphical data at AHB speed.

Maximum pixel clock value at IO level, refer to Table 10 and Table 11 for maximum pixel clock at system level. Pixel clock (LCD\_CLK) form relevant STM32 datasheet.

4. Chrom-Art Accelerator®

5. The integrated MIPI-DSI controller allows easier PCB design with fewer pins, lower EMI (electromagnetic interference) and lower power consumption. For more details on STM32's MIPI-DSI host refer to application note AN4860.

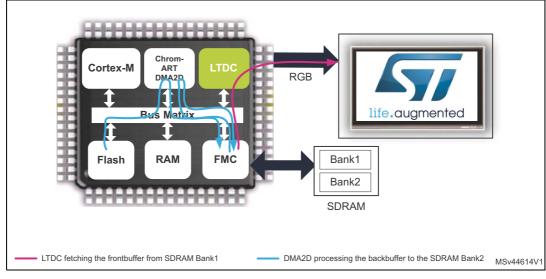

### 2.3 LTDC in a smart architecture

The LTDC is a master on the AHB architecture which performs read access on internal and external memories. The LTDC has two independent layers, each one with its own FIFO enabling more flexibility of the display.

The LTDC controller autonomously fetches graphical data at the speed of the AHB bus from the framebuffer. The graphical data is then stored in one of the FIFO internal layers then driven to the display.

The system architecture enables that graphics can be built and plotted to the screen without any CPU intervention. The LTDC retrieves the data belonging to an image from the framebuffer, while the Chrom-Art Accelerator<sup>®</sup> (DMA2D) is preparing the next images.

The LTDC interface is integrated in a smart architecture allowing:

- LTDC autonomously fetches the graphical data from the framebuffer (can be internal memories such as internal Flash, internal SRAM or external memories such as FMC\_SDRAM or Quad-SPI) and drives it to the display.

- DMA2D as an AHB master can be used to offload the CPU from graphics intensive tasks.

- LTDC is able to continue displaying graphics even in sleep mode when the CPU is not running.

- The multi-layer AHB bus architecture improves memories throughput and leads to higher performance.

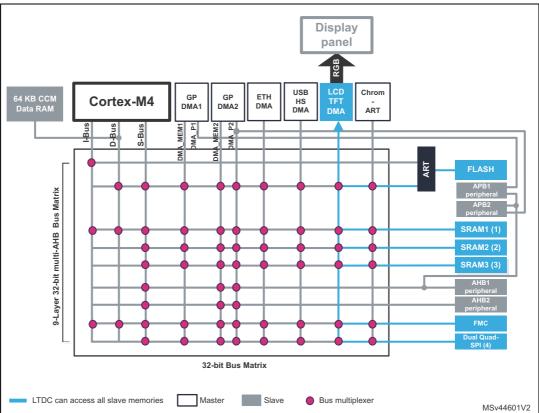

#### System architecture on STM32F429/439 and STM32F469/479 microcontrollers

The system architecture of the STM32F429/439 line and the STM32F469/479 line consists mainly of 32-bit multilayer AHB bus matrix that interconnects ten masters and nine slaves (eight slaves for the STM32F429/F439). The LTDC is one of the ten AHB masters on the AHB bus matrix.

The LTDC can autonomously access all the memory slaves on the AHB bus matrix, such as FLASH, SRAM1, SRAM2, SRAM3 FMC or Quad-SPI enabling an efficient data transfer which is ideal for graphical applications. *Figure 9* shows the LTDC interconnection in the STM32F429/439 and STM32F469/479 lines systems.

Figure 9. LTDC AHB master in STM32F429/439 and STM32F469/479 lines smart architecture

- 1. SRAM1 size = 112 Kbyte for STM32F429/439 and 160 Kbyte for STM32F469/479

- 2. SRAM2 size = 16 Kbyte for STM32F429/439 and 32 Kbyte for STM32F469/479

- 3. SRAM3 size = 64 Kbyte for STM32F429/439 and 128 Kbyte for STM32F469/479

- 4. Dual Quad-SPI interface is only available for STM32F469/479

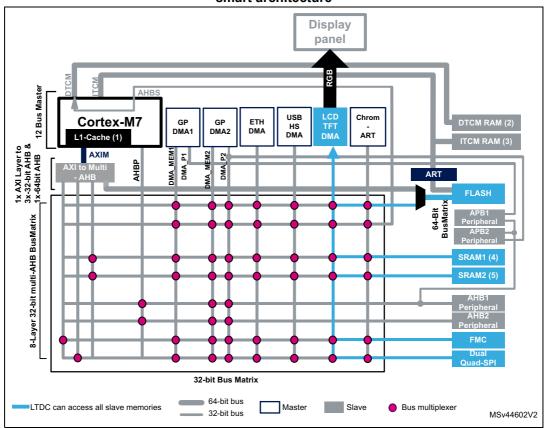

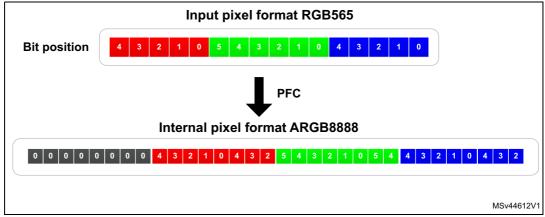

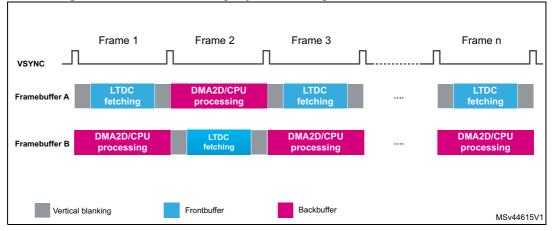

#### System architecture on STM32F7x6, STM32F7x7, STM32F7x8 and STM32F7x9

The system architecture of the STM32F7x6, STM32F7x7, STM32F7x8 and STM32F7x9 lines consists mainly of 32-bit multilayer AHB bus matrix that interconnects twelve masters and eight slaves. The LTDC is one of the twelve AHB masters on the AHB busmatrix.

The LTDC can autonomously access all the memory slaves on the AHB bus matrix, such as FLASH, SRAM1, SRAM2, FMC or Quad-SPI enabling an efficient data transfer which is ideal for graphical applications. *Figure 10* shows the LTDC interconnection in the STM32F7x6, STM32F7x7, STM32F7x8 and STM32F7x9 systems.

Figure 10. LTDC AHB master in STM32F7x6, STM32F7x7, STM32F7x8 and STM32F7x9 smart architecture

1.

I/D Cache size = 4 Kbyte for STM32F7x6 I/D Cache size = 16 Kbyte for STM32F7x7, STM32F7x8 and STM32F7x9 2.

DTCM RAM size = 64 Kbyte for STM32F7x6 DTCM RAM size = 128 Kbyte for STM32F7x7, STM32F7x8 and STM32F7x9

3. ITCM RAM size = 16 Kbyte for STM32F7x6, STM32F7x7, STM32F7x8 and STM32F7x9

- SRAM1 size = 240 Kbyte for STM32F7x6 SRAM1 size = 368 Kbyte for STM32F7x7, STM32F7x8 and STM32F7x9 4

- 5. SRAM2 size = 16 Kbyte for STM32F7x6, STM32F7x7, STM32F7x8 and STM32F7x9

# 2.4 Advantages of using an STM32 LTDC controller

*Table 4* summarizes the major advantages of using the STM32's embedded LTDC interface.

| Advantage                                                                   | Comments                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cost savings                                                                | Compared to other DBI interfaces (SPI, Motorola 6800 or<br>Intel 8080), the LTDC allows a connection to any low-cost<br>display module with no display controller nor GRAM.                                                                         |

| The CPU is offloaded                                                        | The LTDC is an AHB master with its own DMA, which fetches data autonomously from any AHB memory without any CPU intervention.                                                                                                                       |

| No need for extra applicative layer                                         | The LTDC hardware fully manages the data fetching, the RGB outputting and the signals control, so no need for extra applicative layer.                                                                                                              |

| Fully programmable resolution<br>supporting custom and standard<br>displays | Fully programmable resolution with total width of up to<br>4096 pixels and total height of up to 2048 lines and with<br>pixel clock of up to 83 MHz.<br>Support of custom and standard resolutions (QVGA, VGA,<br>SVGA, WVGA, XGA, HD, and others). |

| Flexible color format                                                       | Each LTDC layer can be configured to fetch the framebuffer in the desired pixel format (see Section 3.3.2: <i>Programmable layer: color framebuffer</i> ).                                                                                          |

| Flexible parallel RGB interface                                             | The flexible parallel RGB interface allows to drive 16-bit, 18-bit and 24-bit displays.                                                                                                                                                             |

| Ideal for low power and mobile applications such as smartwatches.           | The LTDC is able to continue graphic data fetching and display driving while the CPU is in SLEEP mode.                                                                                                                                              |

| Table 4. Advantages | of usina | STM32   | MCUs | LTDC | controller |

|---------------------|----------|---------|------|------|------------|

| Tuble H / Waranagee | or doing | 0.11102 |      |      |            |

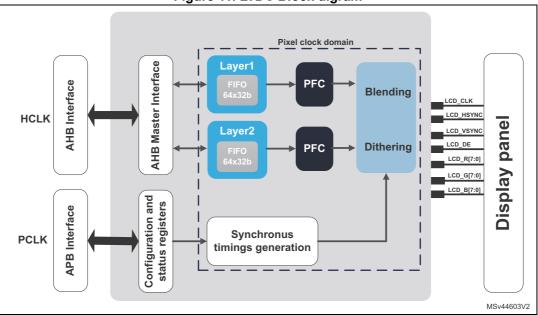

# 3 LCD-TFT (LTDC) display controller description

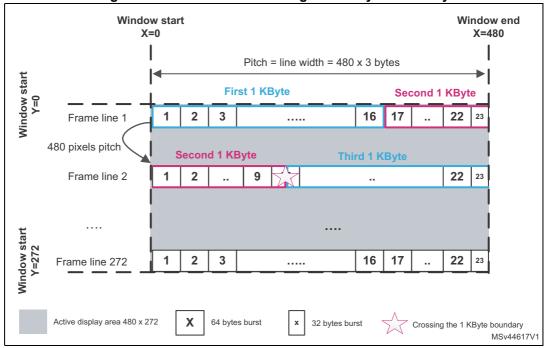

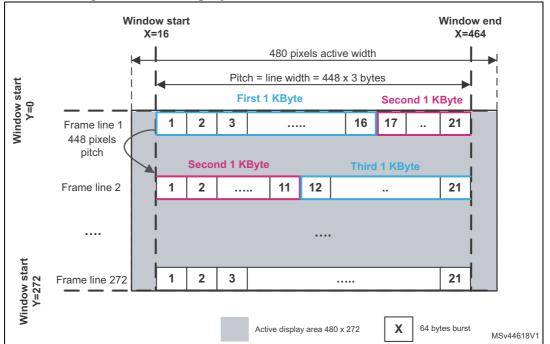

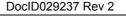

The LTDC is a controller that reads the data of images in a line per line fashion. Its memory access mode is 64 bytes length, but when the end of a line is reached and less than 64 bytes are left, the LTDC fetches the remaining data.

# 3.1 Functional description

On every pixel clock-raising edge or clock-falling edge and within the screen active area, the LTDC layer retrieves one pixel data from its FIFO, converts it to the internal ARGB8888 pixel format and blends it with the background and / or with the other layer pixel color. The resulting pixel, coded in the RGB888 format, goes through the dithering unit and is driven into the RGB interface. The pixel is then displayed on the screen.

Figure 11. LTDC Block digram

### 3.1.1 LTDC clock domains

The LCD-TFT controller peripheral uses three clock domains:

- AHB clock domain (HCLK): used to transfer data from the memories to the FIFO layer and the other way around.

- APB clock domain (PCLK): used to access the configuration and status registers.

- The pixel clock domain (LCD\_CLK): used to generate the LCD-TFT interface signals. The LCD\_CLK output should be configured following the panel requirements through the PLL.

### 3.1.2 LTDC reset

The LTDC is reset by setting the LTDCRST bit in the RCC\_APB2RSTR register.

DocID029237 Rev 2

## 3.2 Flexible timings and hardware interface

Thanks to its timings and hardware interface flexibility, the LCD-TFT controller is able to drive several monitors with different resolutions and signal polarities.

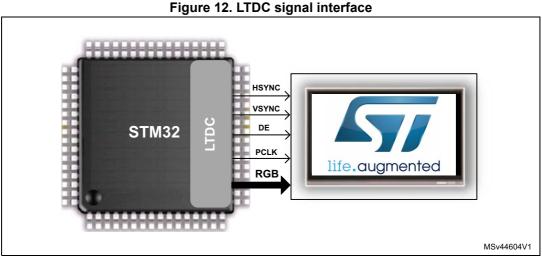

#### 3.2.1 LCD-TFT pins and signal interface

To drive LCD-TFT displays, the LTDC provides up to 28 signals using simple 3.3 V signaling including:

- Pixel clock LCD\_CLK.

- Data enable LCD\_DE.

- Synchronization signals (LCD\_HSYNC and LCD\_VSYNC).

- Pixel data RGB888.

Note:

The LTDC controller may support other display technologies if their interface is compatible.

The LTDC interface output signals are illustrated in *Table 6*.

| LCD-TFT signal | Description                                                                                                                                  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| LCD_CLK        | The LCD_CLK acts as the data valid signal for the LCD-TFT. The data is considered by the display only on the LCD_CLK rising or falling edge. |

| LCD_HSYNC      | The line synchronization signal (LCD_HSYNC) manages horizontal line scanning and acts as line display strobe.                                |

| LCD_VSYNC      | The frame synchronization signal (LCD_VSYNC) manages vertical scanning and acts as a frame update strobe.                                    |

| LCD_DE         | The DE signal, indicates to the LCD-TFT that the data in the RGB bus is valid and must be latched to be drawn.                               |

| Pixel RGB data | The LTDC interface can be configured to output more than one color depth. It can use up to 24 data lines (RGB888) as display interface bus.  |

#### Table 5. LTDC interface output signals .

#### Other signals

It is usual that display panel interfaces include other signals that are not part of the LTDC signals described in *Table 5*. These additional signals are required for a display module to be fully functional. The LTDC controller is able to drive only signals described in *Table 5*.

The signals that are not part of the LTDC may be managed using GPIOs and other peripherals and may need specific circuits.

The display panels usually embed a backlight unit which requires an additional backlight control circuit and a GPIO.

Some display panels need a reset signal and also a serial interface such as I2C or SPI. These interfaces are used in general for the display initialization commands or for the touch panel control.

*Figure 12* shows a display panel connected to an STM32 MCU using the LTDC interface signals illustrated in *Table 5*.

The LTDC can output data according to the following parallel formats: RGB565, RGB666 and RGB888. So a 16-bit RGB565, 18-bit RGB888 or a 24-bit RGB888 display can be connected.

#### LTDC signals programmable polarity

The LTDC control signals polarity is programmable allowing the STM32 microcontroller to drive any RGB parallel display. The control signals (Hsync, Vsync and data enable DE) as well as the pixel clock (LCD\_CLK) can be defined to be active high or active low through the LTDC\_GCR register.

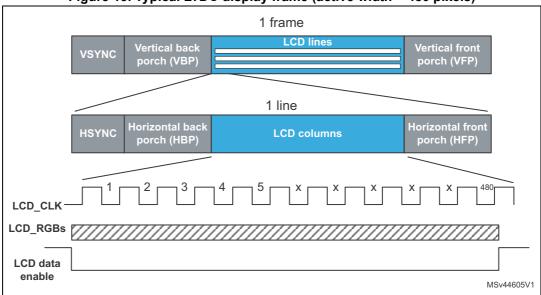

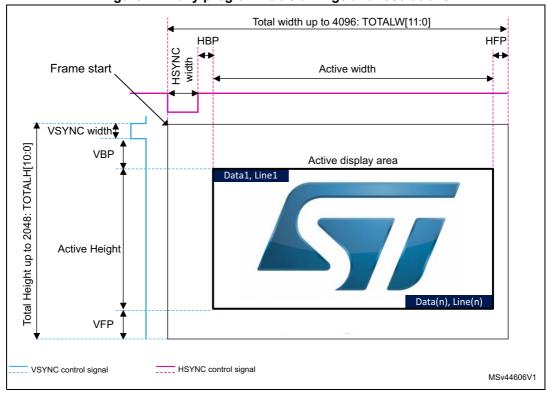

#### 3.2.2 Fully programmable timings for different display sizes

Thanks to its "timings flexibility", the LTDC peripheral can support any display size that respects the maximal programmable timing parameters in the registers and the maximal supported pixel clock described in *Table 3*, *Table 11* and *Table 13*.

The user should consider the timings registers described in *Table 6* when programming as the LTDC timings and synchronization signals should be programmed to match the display specification.

Table 6 summarizes the timings registers supported by the LTDC.

| Register                 |            | Timing parameter                        | Value to be programmed |  |

|--------------------------|------------|-----------------------------------------|------------------------|--|

| LTDC_SSCR <sup>(1)</sup> | HSW[11:0]  | HSYNC width - 1                         | From 1 to 4096 pixels  |  |

|                          | VSH[11:0]  | VSYNC height - 1                        | From 1 to 2048 lines   |  |

| LTDC_BPCR                | AHBP[11:0] | HSYNC width + HBP - 1                   | From 1 to 4096 pixels  |  |

|                          | AVBP[10:0] | VSYNC height + VBP - 1                  | From 1 to 2048 lines   |  |

| LTDC_AWCR                | AAW[11:0]  | HSYNC width + HBP + active width - 1    | From 1 to 4096 pixels  |  |

|                          | AAH[10:0]  | VSYNC height + BVBP + active height - 1 | From 1 to 2048 lines   |  |

#### Table 6. LTDC timing registers

| Register  |              | Timing parameter                              | Value to be programmed |  |

|-----------|--------------|-----------------------------------------------|------------------------|--|

| LTDC_TWCR | TOTALW[11:0] | HSYNC width + HBP + active width + HFP - 1    | From 1 to 4096 pixels  |  |

|           | TOTALH[10:0] | VSYNC height + BVBP + active height + VFP - 1 | From 1 to 2048 lines   |  |

#### Table 6. LTDC timing registers (continued)

1. Setting HSYNC to 0 in HSW[11:0] gives one pulse width of one LCD\_CLK. Setting VSYNC to 0 in VSW[11:0] gives one total line period

#### Example of a typical LTDC display frame

The *Figure 13* shows an example of a typical LTDC display frame showing the timing parameters described in *Table 6*.

#### Figure 13. Typical LTDC display frame (active width = 480 pixels)

#### LTDC flexible timings

The LTDC peripheral allows the user to interface with any display size with total width of up to 4096 pixels and total height of up to 2048 lines (refer to *Table 6*).

*Figure 14* illustrates fully programmable timings and resolutions.

#### Caution:

ion: Any display resolution belonging to the maximal total area in 4096 x 2048 as described in *Figure 15* is supported by the LTDC only if the following conditions are met:

- The display panel pixel clock must not exceed the maximal LTDC pixel clock in *Table 2*

- The display panel pixel clock must not exceed the maximal STM32 pixel clock respecting the framebuffer bandwidth (see Section 4.2: Checking the display size and color depth compatibility with the hardware configuration).

*Figure 15* shows some custom and standard resolutions belonging to the maximal 4096 x 2048 supported by the LTDC.

Figure 15. LTDC fully programmable display resolution with total width up to 4096 pixels and total height up to 2048 lines

1. Only the active display area is shown in this figure.

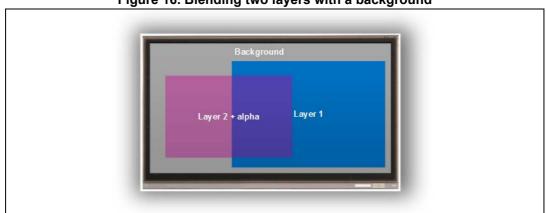

# 3.3 Two programmable LTDC layers

The LTDC features two layers, and each layer can be enabled, disabled and configured separately. The order of the layer display is fixed, so it is always bottom-up. If two layers are enabled, the Layer2 is the top displayed window.

The LTDC features configurable blending factors. Blending is always active using an alpha value. The blending order is fixed and it is always bottom-up. If two layers are enabled, first the Layer1 is blended with the background color, and then the Layer2 is blended with the result of the blended color of Layer1 and the background.

The background color is programmable through the LTDC\_BCCR register. A constant background color can be programmed in the RGB888 format where the BCRED[7:0] field is used for the red value, the BCGREEN[7:0] is used for the green value and the BCBLUE[7:0] is used for the blue value.

*Figure 16* illustrates the blending of two layers with a background.

Figure 16. Blending two layers with a background

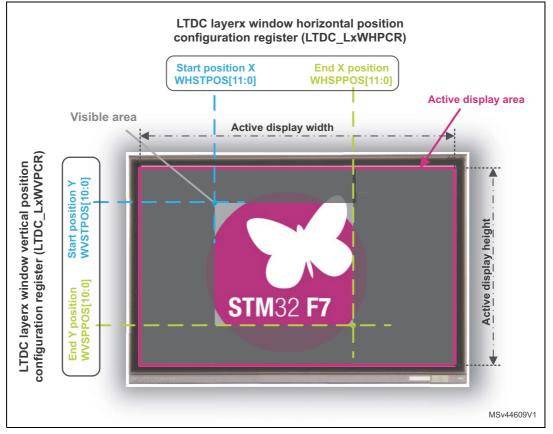

#### 3.3.1 Flexible window position and size configuration

Every layer can be positioned and resized at runtime and it must be inside the active display area. The programmable layer position and size define the first and last visible pixel of a line and the first and last visible line in the window. It allows to display either the full image (all the active display area) or only a part of the image frame. *Figure 17* shows a small window where only a portion of the image is displayed while the remaining area is not displayed.

1. LTDC\_LxWHPCR and LTDC\_LxWVPCR are respectively LTDC layer x window horizontal and vertical position configuration registers where "x" can refer to layer 1 or layer 2.

DocID029237 Rev 2

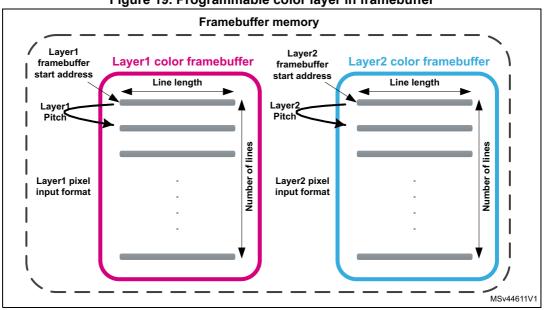

#### 3.3.2 Programmable layer: color framebuffer

Every layer has a dedicated configurable number of lines and line length for the color framebuffer and for the pitch.

#### Color framebuffer address

Every layer has a start address for the color framebuffer configured through the LTDC\_LxCFBAR register.

#### Color framebuffer length (size)

The line length and the number of lines parameters are used to stop the prefetching of data from the FIFO layer at the end of the framebuffer.

The line length (in bytes) is configurable in the LTDC\_LxCFBLR register.

The number of lines (in bytes) is configurable in the LTDC\_LxCFBLNR register.

#### Color framebuffer pitch

The pitch is the distance between the start of one line and the beginning of the next line in bytes. It is configured in the LTDC\_LxCFBLR register.

#### **Pixel input format**

The programmable pixel format is used in all the data stored in the framebuffer of each LTDC layer.

For each layer a specific pixel input format can be configured separately. The LTDC can be configured with up to eight programmable input color formats per layer.

Figure 18 illustrates the pixel data mapping versus the selected input color format.

#### @+3 @+2 @ @+4 ARGB8888 Ax[7:0] Rx[7:0] Gx[7:0] Bx[7:0] Direct color **RGB888** Bx+1[7:0] Bx[7:0] Rx[7:0] Gx[7:0] ARGB1555 Ax+1[0] Rx+1[4:0] Gx+1[4:3] Gx+1[2:0] Bx+1[4:0] Ax[0] Rx[4:0] Gx[4:3] Gx[2:0] Bx[4:0] ARGB4444 Rx+1[3:0] Ax+1[3:0] Gx+1[3:0] Bx+1[3:0] Ax[3:0] Bx[3:0] Rx[3:0] Gx[3:0] L8 Lx+3[7:0] Lx+2[7:0] Lx+1[7:0] Lx[7:0] Indirect color AL88 Ax+1[7:0] Lx+1[7:0] AL44 Ax+3[3:0] Lx+3[3:0] Ax+2[3:0] Lx+2[3:0] Ax+1[3:0] Lx+1[3:0] Ax[3:0] Lx[3:0] MSv44610V1

#### Figure 18. Pixel data mapping versus color format

*Figure 19* summarizes all layer color framebuffer configurable parameters.

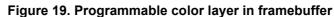

#### **Pixel format conversion (PFC)**

After being read from the framebuffer, the pixel data is transformed from the configured pixel input format to the internal ARGB8888 format.

The components that have a width of less than 8 bits get expanded to 8 bits by bit replication.

The 8 MSB bits are chosen. *Figure 20* shows a conversion from RGB565 input pixel format to the internal ARGB8888 format.

# Figure 20. Pixel format conversion from RGB565 input pixel format to the internal ARGB8888 format

Note: Using two layers creates bandwidth constraints on the system. It is preferable to use only one layer and to do the composition with the Chrom-Art Accelerator<sup>®</sup> during the framebuffer calculation (see Section 4.2.2: Checking display compatibility considering the memory bandwidth requirements).

DocID029237 Rev 2

#### AN4861

## 3.4 Interrupts

The LTDC peripheral supports two global interrupts:

- LTDC global interrupt.

- LTDC global error interrupt.

Each global interrupt is connected to two LTDC interrupts (logically disjointed) that can be masked separately through a specific register. *Table 7* summarizes all of the related interrupts and all the particular cases when each interrupt is generated.

| Related<br>NVIC<br>interrupt         | Interrupt<br>event              | Event flag bit<br>(LTDC_ISR<br>register) | Enable bit<br>(LTDC_IER<br>register) | Clear bit<br>(LTDC_ICR<br>register) | Description                                                          |

|--------------------------------------|---------------------------------|------------------------------------------|--------------------------------------|-------------------------------------|----------------------------------------------------------------------|

| LTDC<br>GLOBAL<br>INTERRUPT          | Line                            | LIF                                      | LIE                                  | CLIF                                | Generated when a defined line on the screen is reached               |

|                                      | Register<br>reload              | RRIF                                     | RRIE                                 | CRRIF                               | Generated when the shadow reload occurs                              |

| LTDC<br>GLOBAL<br>ERROR<br>INTERRUPT | FIFO<br>underrun <sup>(1)</sup> | FUIF                                     | FUIE                                 | CFUIF                               | Generated when a<br>pixel is requested<br>while the FIFO is<br>empty |

|                                      | Transfer<br>error               | TERRIF                                   | TERRIE                               | CTERRIF                             | Generated when bus<br>error occurs                                   |

Table 7. LTDC interrupts summary

1. FIFO underrun interrupt is useful for determining the display size compatibility (see Section 4.2.2: Checking display compatibility considering the memory bandwidth requirements).

# 3.5 Low-power modes

The STM32 power state has a direct effect on the LTDC peripheral. While in sleep mode, the LTDC is not affected and it keeps driving graphical data to the screen. While in the standby and the stop mode, the LTDC is disabled and no output is driven through its parallel interface. Exiting the standby mode should be followed with the LTDC reconfiguration.

It is possible to drive a display panel in sleep mode while the CPU is stopped thanks to the smart architecture embedded in the STM32 microcontrollers which allows all the peripherals to be enabled even in sleep mode. This feature fits wearable applications where the low-power consumption is a must.

The LTDC as an AHB master may continue fetching data from FMC\_SDRAM or Quad-SPI (when the memory-mapped mode is used) even after entering the MCU in SLEEP mode. A line event or register reload interrupt can be generated to wake up the STM32 when a defined line on the screen is reached or when the shadow reload occurs.

More information on reducing power consumption is available on Section 5.

Table 8 summarizes the LTDC's state versus the STM32's low-power modes.

| Mode    | Description                                                                   |  |  |

|---------|-------------------------------------------------------------------------------|--|--|

| Run     | Active                                                                        |  |  |

| Sleep   | Active. Peripheral interrupts cause the device to exit Sleep mode             |  |  |

| Stop    | Frozen. Peripheral registers content is kept                                  |  |  |

| Standby | Powered-down. The peripheral must be reinitialized after exiting Standby mode |  |  |

Table 8. LTDC peripheral state versus STM32 low-power modes

# 4 Creating a graphical application with LTDC

This section illustrates the different steps required before and during a graphical application development using LTDC. The user should at first determine the graphical application requirements, then check if the desired display size fits the hardware configuration. During the graphical application compatibility check phase, the user can use the existing STM32 reference boards described in *Table 17* to evaluate his hardware and software configuration.

# 4.1 Determining graphical application requirements

Determining the graphical application needs is a crucial step to start from. Some of the most important parameters to be defined before starting the creation of the graphical application are: display resolution, color depth, as well as the nature of the data to display (static images, text or animation).

Once the basic parameters mentioned above are defined, the user should determine the graphical hardware architecture of the application as well as the required hardware resources. The user should select the best-fitting STM32 package (see *Table 13*) according to the following parameters:

- If an external memory is needed for the framebuffer

- The external framebuffer memory bus width

- The LTDC interface: RGB565, RGB666 or RGB888 depending on the display module

- If an external memory is needed to store graphic primitives (QSPI or FMC\_NOR)

# 4.2 Checking the display size and color depth compatibility with the hardware configuration

When starting a graphic application development using a STM32 microcontroller, the user usually has a defined desired display size and color depth. A key question that the user must answer before continuing the development is *if such display size and color depth match a specific hardware configuration?*.

In order to answer this question, the user should follow below steps:

- 1. Determine the required framebuffer size and its location.

- 2. Check the compatibility of the display versus the framebuffer memory bandwidth requirements.

- 3. Check the compatibility of the display panel interface with the LTDC.

#### 4.2.1 Framebuffer memory size requirements and location

Determining the framebuffer memory size and its location is a key parameter for the display compatibility check.

The memory space required in the RAM to support the framebuffer should be contiguous and with a minimum size equal to:

Framebuffer size = number of pixels x bits per pixel

DocID029237 Rev 2

As shown in the formula above, the required framebuffer size depends on the display resolution and on its color depth.

It is not necessary that the framebuffer color depth (bpp) is the same than the display color depth. For instance, an RGB888 display can be driven using an RGB565 framebuffer.

Note: The required framebuffer size is doubled for double framebuffer configuration. It is common to use a double buffer configuration where one graphic buffer is used to store the current image while the second buffer used to prepare the next image.

*Table 9* shows the framebuffer size needed for standard screen resolutions with different pixel formats.

| Screen resolution                 | Number of | Framebuffer size (Kbyte) <sup>(1)</sup> |        |        |        |

|-----------------------------------|-----------|-----------------------------------------|--------|--------|--------|

| Screen resolution                 | pixels    | 8 bpp                                   | 16 bpp | 24 bpp | 32 bpp |

| QVGA (320 x 240)                  | 76800     | 75                                      | 150    | 225    | 300    |

| Custom (480 x 272) <sup>(2)</sup> | 130560    | 128                                     | 255    | 383    | 510    |

| HVGA(480 x 320)                   | 153600    | 150                                     | 300    | 450    | 600    |

| VGA (640 x 480)                   | 307200    | 300                                     | 600    | 900    | 1200   |

| WVGA(800 x 480)                   | 384000    | 375                                     | 750    | 1125   | 1500   |

| SVGA (800 x 600)                  | 480000    | 469                                     | 938    | 1407   | 1875   |

| XGA (1024 x 768)                  | 786432    | 768                                     | 1536   | 2304   | 3072   |

| HD (1280 x 720)                   | 921600    | 900                                     | 1800   | 2700   | 3600   |

Table 9. Framebuffer size for different screen resolutions

1. The required framebuffer size is doubled for double framebuffer configuration.

An example of a custom 480 x 272 display is the ROCKTECH embedded on the STM32F746 discovery kit (32F746GDISCOVERY).

#### **Framebuffer location**

Depending on the required framebuffer size, it can be located either in an internal SRAM or in an external SRAM/SDRAM.

If the internal RAM is not enough for the framebuffer, the user must use an external SDRAM/SRAM connected to the FMC.

Consequently, the required framebuffer size will determine if the use of an external memory is needed or not. The required framebuffer size depends on the display size and color depth.

#### Locating the framebuffer in the Internal SRAM

Depending on the framebuffer size, it can be placed either in the internal SRAM or the external SRAM or SDRAM.

Using an internal SRAM as a framebuffer allows the maximum performances and avoids any bandwidth limitation issues for the LTDC.

Using the internal SRAM instead of an external SRAM or SDRAM has many advantages:

- Provides a higher throughput (0 wait state access).

- Reduces the number of required pins and the PCB design complexity.

- Reduces the BOM, hence the cost, since no external memory is needed.

The only limitation when using the internal SRAM is its limited size (hundreds of Kilobytes). When the framebuffer size exceeds the available memory, the external SDRAM or SRAM (driven by the FMC interface) should be used. However, when dealing with external memories, the user must be careful to avoid bandwidth limitation. For more detailed information refer to *Section 4.5: Graphic performance optimization*.

Note: The color look-up table CLUT can be used to decrease the required framebuffer size. (For more details refer to the relevant STM32 MCU reference manual).

#### 4.2.2 Checking display compatibility considering the memory bandwidth requirements

The scope of this section is to explain how to check a display compatibility considering the framebuffer memory bandwidth. For that, this section describes some important bandwidth aspects and explains how to determine the required bandwidth for the pixel clock and the LTDC. Finally, this section shows a simple method that allows to conclude whether a desired display size is compatible with a specific hardware configuration.

#### Framebuffer memory bandwidth aspects

Once that the framebuffer location is fixed (either in internal or external memory), the user should check if its bandwidth can sustain the hardware configuration.

In order to check if the memory bandwidth can sustain the LTDC required bandwidth, the user must consider any other concurrent accesses to the memory.

In general, a small size framebuffer located in the internal RAM does not require a high bandwidth. This is because a small size framebuffer means low pixel clock, hence low LTDC required bandwidth.

A more complex use case to analyze is when the framebuffer is located in an external memory (SDRAM or SRAM).

#### Framebuffer memory bus concurrency

• LTDC, DMA2D and CPU masters

In a typical graphic application where an external SDRAM or SRAM memory is used as framebuffer, two or three main AHB masters concurrently use the same memory.

The DMA2D (or the CPU) updates the next image to be displayed while the LTDC fetches and displays the actual image. The memory bus load depends mainly on the LTDC required bandwidth.

Other AHB masters

It is common that an external SDRAM or SRAM memory is shared by other masters and not only by those used for graphics. This concurrency leads to heavy bus load and may impact the graphic performances.

Figure 21 shows all the AHB masters with concurrent access to the SDRAM.

Figure 21. AHB masters concurrent access to SDRAM

#### External SDRAM/SRAM memory bus width

When locating the framebuffer in an external SDRAM/SRAM, the user should consider that the external memory running frequency is around half or third of the system frequency. That is the reason why the memory bandwidth should be considered as the bottleneck of the whole graphic system.

One of the needed parameters for checking the display compatibility is the memory bus width. For SDRAM, the user can use a 8-bit, 16-bit or 32-bit configuration.

As previously stated, the most complex to analyze is the use case when the framebuffer is placed in an external memory:

The masters concurrent access on the same external memory leads to more latency and impacts its throughput.

#### Determining pixel clock and LTDC required bandwidth

#### Pixel clock computation

The pixel clock is a key parameter for checking display size compatibility with a specific hardware configuration.

In order to get the typical pixel clock of display, refer to the display's datasheet. The computed pixel clock should respect the display's specifications.

The pixel clock for a specific refresh rate calculated with the following formula:

LCD\_CLK (MHz) = total screen size x refresh rate

Where total screen size = total width x total height.

#### LTDC required bandwidth

The LTDC required bandwidth depends mainly on three factors:

- The number of used LTDC layers

- The LTDC layer color depth

- The pixel clock (depends on the resolution of the display panel and on the refresh rate)

The maximum required bandwidth can be calculated as described below:

- If only one LTDC layer is used

- LTDC required bandwidth = LCD\_CLK x BppL1

- If two LTDC layers are used

- LTDC required bandwidth = LCD\_CLK x (BppL1 + BppL2)

Where BppL1 and BppL2 are respectively the color depth for LTDC Layer1 and Layer2.

The LTDC required bandwidth should not exceed the memory's available bandwidth, otherwise, display problems will occur and the FIFO underrun flag will be set (if the FIFO underrun interrupt was enabled).

*Note:* If the memory used to store the framebuffer is also used for other application purposes, it may impact the graphical performances of the system.

#### Check if the used display resolution fits the hardware configuration

The general method for checking whether a display size with a particular color depth is compatible with memory bandwidth is:

- 1. Compute the pixel clock according to the display size or extract it from the display's datasheet.

- 2. Check if the display's pixel clock does not exceed the maximum system's supported pixel clock described in *Table 10* or *Table 11*. The user should use the following parameters to extract from *Table 10* or *Table 11* the maximum supported pixel clock corresponding to the used hardware configuration:

- a) Number of used LTDC layers.

- b) The used system's clock speed HCLK and framebuffer memory speed.

- c) External framebuffer memory bus width.

- d) Number of AHB masters accessing concurrently to external framebuffer memory.

- 3. The user should perform some tests to confirm the hardware compatibility with the desired display size and color depth. In order to do it, the user should monitor the LTDC FIFO underrun interrupt flag in the LTDC\_ISR register. If the FIFO underrun interrupt flag is always reset then the user confirms that the

If the FIFO underrun interrupt flag is always reset then the user confirms that the desired display size is compatible with the hardware configuration. If the FIFO underrun flag is set, the user should check the following points:

a) Verify if he extracted, from *Table 10* or *Table 11*, the correct maximum pixel clock corresponding to the right hardware (for example the user is working with a 16-bit

SDRAM but he extracted a pixel clock corresponding to a 32-bit SDRAM, which would be a mistake).

- b) The color framebuffer line width is not 64 bytes aligned (see Section 4.5.2: Optimizing the LTDC framebuffer fetching from external memories (SDRAM or SRAM).

- c) For the STM32F7 Series, the MPU is not correctly configured to avoid Cortex<sup>®</sup>-M7 speculative read accesses to the SDRAM (see *Section 4.6: Special recommendations for Cortex*®-M7 (*STM32F7 Series*)).

- d) If the FIFO underrun is still set because there are more than two AHB masters concurrent access to the external memory, the user should relax the memory bandwidth using the below recommendations:

- use only one LTDC Layer

- use the largest possible memory bus width (use 32-bit instead of 16-bit or 8-bit SDRAM/SRAM)

- update the framebuffer content during the blanking period when the LTDC is not fetching

- use the highest possible system clock HCLK and the highest memory speed (FMC\_SDRAM/FMC\_SRAM)

- decrease the images color depth (BPP)

- For more details on memory bandwidth optimization see Section 4.5: Graphic performance optimization.

- Note: To evaluate the STM32's graphical capability in a specific hardware configuration, the user can use the STM32 boards described in Table 17: STM32 reference boards with embedding LTDC and featuring an on-board LCD-TFT panel.

*Figure 22* shows a typical graphic hardware configuration where an external SDRAM is connected to the FMC which is used for framebuffer. The SDRAM memory bandwidth depends on the bus width and in the operating clock.

The SDRAM bus width can be 32-bit, 16-bit or 8-bit, while the operating clock depends on the system clock HCLK and the configured prescaler (HCLK/2 or HCLK/3).

Figure 22. Typical graphic hardware configuration with external SDRAM

*Table 10* lists the maximal supported pixel clock at system level for the STM32F4x9 line and *Table 11* lists the maximal supported pixel clock at system level for the STM32F7x6, STM32F7x7, STM32F7x8 and STM32F7x9 lines in the following conditions:

- For the STM32F4x9 line the system clock HCLK is running @ 180 MHz and the SDRAM is @ 90 MHz.

- For the STM32F7x6, STM32F7x7, STM32F7x8 and STM32F7x9 lines the system clock HCLK is running @ 200 MHz and the SDRAM is @ 100 MHz.

- One or two AHB masters concurrent access to SDRAM (LTDC or LTDC+DMA2D).

- The SDRAM bus width is 16-bit or 32-bit.

- Either only one LTDC layer or two layers are used.

- The LTDC layer color depth is 8 bpp, 16 bpp, 24 bpp or 32 bpp.

|                  | pported pixel        | Maximum pixel clock (MHz) |              |              |              |  |  |  |

|------------------|----------------------|---------------------------|--------------|--------------|--------------|--|--|--|

| Used LTDC layers | Color depth<br>(bpp) | LT                        | DC           | LTDC +       | DMA2D        |  |  |  |

|                  | ,                    | SDRAM 16-bit              | SDRAM 32-bit | SDRAM 16-bit | SDRAM 32-bit |  |  |  |

|                  | 32                   | 38                        | 67           | 22           | 35           |  |  |  |

| 1 lover          | 24                   | 51                        | 83           | 30           | 47           |  |  |  |

| 1 layer          | 16                   | 76                        | 83           | 45           | 70           |  |  |  |

|                  | 8                    | 83                        | 83           | 83           | 83           |  |  |  |

|                  | 32/32                | 19                        | 33           | NA           | 18           |  |  |  |

|                  | 32/24                | 22                        | 38           | 13           | 21           |  |  |  |

|                  | 32/16                | 25                        | 44           | 15           | 25           |  |  |  |

|                  | 32/8                 | 30                        | 53           | 19           | 30           |  |  |  |

|                  | 24/24                | 26                        | 44           | 15           | 24           |  |  |  |

| 2 layers         | 24/16                | 31                        | 53           | 18           | 30           |  |  |  |

|                  | 24/8                 | 38                        | 67           | 23           | 38           |  |  |  |

|                  | 16/16                | 39                        | 67           | 22           | 37           |  |  |  |

|                  | 16/8                 | 51                        | 83           | 31           | 50           |  |  |  |

|                  | 8/8                  | 78                        | 83           | 46           | 74           |  |  |  |

## Table 10. STM32F4x9 with HCLK @ 180 MHz and SDRAM @ 90 MHz maximal supported pixel clock versus LTDC configuration and SDRAM bus width

|                                   |                      | <u> </u>     | Maximum pix  | el clock (MHz) |              |

|-----------------------------------|----------------------|--------------|--------------|----------------|--------------|

| Used LTDC layers                  | Color depth<br>(bpp) | LT           | DC           | LTDC +         | DMA2D        |

|                                   |                      | SDRAM 16-bit | SDRAM 32-bit | SDRAM 16-bit   | SDRAM 32-bit |

|                                   | 32                   | 42           | 74           | 25             | 39           |

| 1 10 10 1                         | 24                   | 56           | 83           | 34             | 52           |

| 1 layer 16<br>8<br>32/32<br>32/24 | 83                   | 83 83 5      |              | 78             |              |

|                                   | 8                    | 83           | 83           | 83             | 83           |

|                                   | 32/32                | 21           | 37           | 12             | 20           |

|                                   | 32/24                | 24           | 42           | 14             | 23           |

|                                   | 32/16                | 28           | 49           | 17             | 28           |

|                                   | 32/8                 | 34           | 59           | 21             | 34           |

|                                   | 24/24                | 29           | 49           | 17             | 27           |

| 2 layers                          | 24/16                | 34           | 59           | 20             | 33           |

|                                   | 24/8                 | 42           | 74           | 26             | 42           |

|                                   | 16/16                | 43           | 74           | 25             | 41           |

|                                   | 16/8                 | 57           | 83           | 34             | 56           |

|                                   | 8/8                  | 83           | 83           | 51             | 82           |

#### Table 11. STM32F7x6, STM32F7x7, STM32F7x8 and STM32F7x9 with HCLK @ 200 MHz and SDRAM@ 100 MHz maximal supported pixel clock versus LTDC configuration and SDRAM bus width

*Note:* Decreasing the system clock (HCLK then LTDC) leads to a degradation of graphic performances.

#### Example of supported display resolutions for STM32F4x9 line and STM32F7 Series

*Table 12* lists an example of some standard and custom display sizes supported by the STM32F4x9 line and the STM32F7 Series in the following conditions:

- For the STM32F4x9 line the system clock HCLK is running @ 180 MHz and the SDRAM is @ 90 MHz.

- For the STM32F7x6, STM32F7x7, STM32F7x8 and STM32F7x9 lines the system clock HCLK is running @ 200 MHz and the SDRAM is @ 100 MHz.

- Only one LTDC layer used.

- Two AHB masters concurrent access to the SDRAM (LTDC + DMA2D).

|                     | Display cha  | racteristics |                           | STM32's LTDC | configuration               |

|---------------------|--------------|--------------|---------------------------|--------------|-----------------------------|

| Resolution          | Refresh rate | Pixel clock  | Display                   | Color        | depth                       |

| Resolution          | (Hz)         | (MHz)        | standard                  | SDRAM 16-bit | SDRAM 32-bit                |

| 320 x 240<br>(QVGA) |              | 5.6          | Custom                    | Up to :      | 32 bpp                      |

| 480 x 272           |              | 9.5          |                           |              |                             |

| 640 x 480<br>(VGA)  |              | 25.175       | Industry<br>standard      | Up to 24 bpp | Up to 32 bpp                |

| 800 x 600<br>(SVGA) | 60           | 40.000       | VESA                      | Up to 16 bpp | Up to 24 bpp                |

| 1024 x 768<br>(XGA) |              | 65           | guidelines <sup>(1)</sup> |              | Up to 16 bpp                |

| 1280 x 768          |              | 68.250       | CVT R.B <sup>(2)</sup>    | 9 hnn        |                             |

| 1280 x 720<br>(HD)  |              | 74.25        | CEA <sup>(3)</sup>        | 8 bpp        | Up to 16 bpp <sup>(4)</sup> |

| 1920 x1080          | 30           | 74.25        | CEA <sup>(3)</sup>        | ]            |                             |

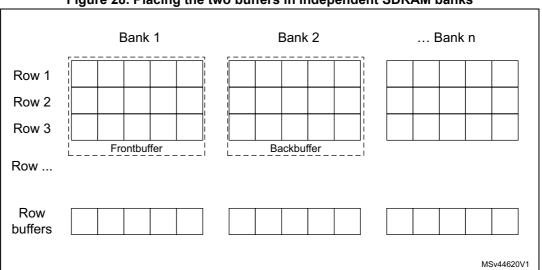

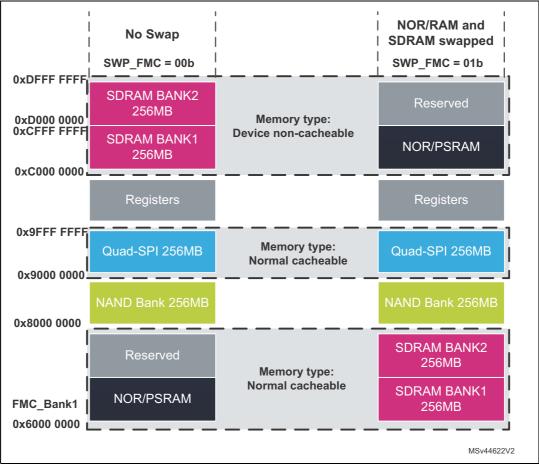

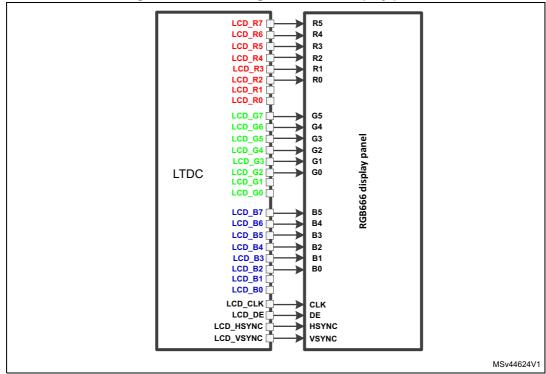

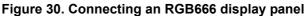

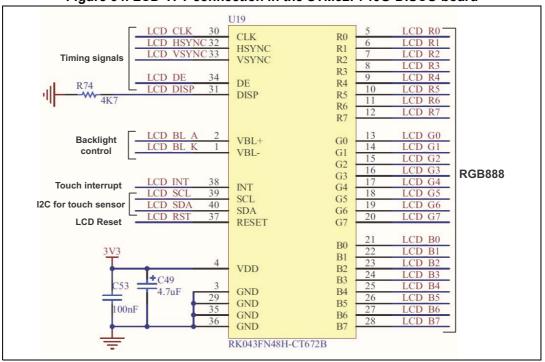

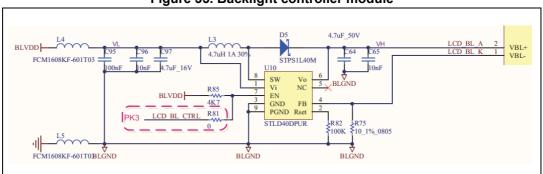

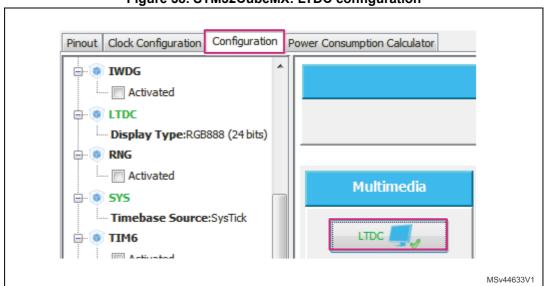

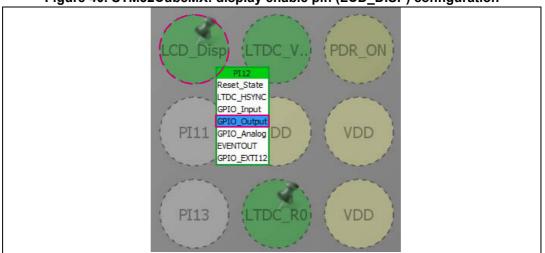

Table 12. Example of supported display resolutions in specific STM32 hardware configurations