# $\mu$ PD720201/ $\mu$ PD720202

User's Manual: Hardware

# **USB3.0 HOST CONTROLLER**

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

### **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.5.0-1 October 2020)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <a href="https://www.renesas.com/contact/">www.renesas.com/contact/</a>

#### NOTES FOR CMOS DEVICES

- (1) VOLTAGE APPLICATION WAVEFORM AT INPUT PIN: Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between VIL (MAX) and VIH (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between VIL (MAX) and VIH (MIN).

- (2) HANDLING OF UNUSED INPUT PINS: Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

- (3) PRECAUTION AGAINST ESD: A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

- (4) STATUS BEFORE INITIALIZATION: Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

- (5) POWER ON/OFF SEQUENCE: In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current. The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

- (6) INPUT OF SIGNAL DURING POWER OFF STATE: Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

### **PREFACE**

**Readers** This manual is intended for engineers who need to be familiar with the capability

of the  $\mu$ PD720201/ $\mu$ PD720202 in order to develop application systems based on

it.

Purpose The purpose of this manual is to help users understand the hardware capabilities

(listed below) of the  $\mu$ PD720201/ $\mu$ PD720202.

**Configuration** This manual consists of the following chapters:

Overview

- Pin function

- Register information

- Power management

- · How to connect to external elements

- · How to access external ROM

- FW download interface

- · Battery charging function

**Guidance** Readers of this manual should already have a general knowledge of electronics,

logic circuits, and microcomputers.

**Notation** This manual uses the following conventions:

Data bit significance: High-order bits on the left side;

low-order bits on the right side

Active low: XXXXB (Pin and signal names are suffixed with B.)

**Note**: Explanation of an indicated part of text

**Caution**: Information requiring the user's special attention

**Remark**: Supplementary information Numerical value: Binary ... xxxx or xxxxb

Decimal ... xxxx

Hexadecimal ... xxxxh

**Related Document**Use this manual in combination with the following document.

The related documents indicated in this publication may include preliminary

versions. However, preliminary versions are not marked as such.

μPD720201/μPD720202 Data Sheet: R19DS0047E

### CONTENTS

| 1. Overv  | /iew         |              |                                                     | 1  |

|-----------|--------------|--------------|-----------------------------------------------------|----|

| 1.1       | Feature      | s            |                                                     | 1  |

| 1.2       | Applications |              |                                                     |    |

| 1.3       | Orderin      | g Informatio | on                                                  | 2  |

| 1.4       |              | •            |                                                     |    |

| 1.5       | Pin Con      | figuration ( | TOP VIEW)                                           | 5  |

| 2 Din E   | ınation      |              |                                                     | 7  |

| 2. FIII F |              |              |                                                     |    |

| 2.1       |              |              |                                                     |    |

|           | _            | _            |                                                     |    |

| 2.5       | 2.3.1        |              | face signal                                         |    |

|           | 2.3.1        | •            | Interface                                           |    |

|           | 2.3.2        | •            | ce                                                  |    |

|           | 2.3.4        |              | 3                                                   |    |

|           | 2.3.4        | SFIIIIeiiace | <del></del>                                         | 11 |

| 3. Regis  | ter Infori   | mation       |                                                     | 12 |

| 3.1       | Registe      | r Attributes |                                                     | 12 |

| 3.2       | PCI Cor      | figuration S | Space                                               | 13 |

|           | 3.2.1        | PCI Type 0   | Configuration Space Header                          | 13 |

|           |              | 3.2.1.1      | Vendor ID Register                                  | 15 |

|           |              | 3.2.1.2      | Device ID Register                                  | 15 |

|           |              | 3.2.1.3      | Command Register                                    | 15 |

|           |              | 3.2.1.4      | Status Register                                     | 16 |

|           |              | 3.2.1.5      | Revision ID Register                                | 17 |

|           |              | 3.2.1.6      | Class Code Register                                 | 17 |

|           |              | 3.2.1.7      | Cache Line Size Register                            | 17 |

|           |              | 3.2.1.8      | Latency Timer Register                              | 18 |

|           |              | 3.2.1.9      | Header Type Register                                | 18 |

|           |              | 3.2.1.10     | BIST Register                                       | 18 |

|           |              | 3.2.1.11     | Base Address Register #0                            | 18 |

|           |              | 3.2.1.12     | Base Address Register #1                            | 19 |

|           |              | 3.2.1.13     | Subsystem Vendor ID Register                        | 19 |

|           |              | 3.2.1.14     | Subsystem ID Register                               | 19 |

|           |              | 3.2.1.15     | Capabilities Pointer Register                       | 19 |

|           |              | 3.2.1.16     | Interrupt Line Register                             | 20 |

|           |              | 3.2.1.17     | Interrupt Pin Register                              | 20 |

|           |              | 3.2.1.18     | Min_Gnt Register                                    | 20 |

|           |              | 3.2.1.19     | Max_LAT Register                                    | 20 |

|           |              | 3.2.1.20     | Serial Bus Release Number Register (SBRN)           | 20 |

|           |              | 3.2.1.21     | Frame Length Adjustment Register (FLADJ)            | 21 |

|           | 3.2.2        | PCI Power N  | Management Capabilities                             | 22 |

|           |              | 3.2.2.1      | Capabilities List Register                          | 22 |

|           |              | 3.2.2.2      | Power Management Capabilities Register (PMC)        | 22 |

|           |              | 3.2.2.3      | Power Management Status / Control Register (PMSC) . | 23 |

|           | 3.2.3        | MSI Capabil  | ities                                               | 25 |

|           |              | 3.2.3.1      | Capabilities List Register for MSI                  | 25 |

|           |              | 3.2.3.2      | Message Control for MSI                             | 25 |

|       | 3.2.3.3      | Message Address for MSI                                      | 25 |

|-------|--------------|--------------------------------------------------------------|----|

|       | 3.2.3.4      | Message Upper Address for MSI                                | 25 |

|       | 3.2.3.5      | Message Data for MSI                                         | 26 |

|       | 3.2.3.6      | Mask Bits for MSI                                            | 26 |

|       | 3.2.3.7      | Pending Bits for MSI                                         | 26 |

| 3.2.4 | MSI-X Capa   | bilities                                                     | 27 |

|       | 3.2.4.1      | Capabilities List Register for MSI-X                         | 27 |

|       | 3.2.4.2      | Message Control for MSI-X                                    | 27 |

|       | 3.2.4.3      | Table Offset / Table BIR for MSI-X                           | 27 |

|       | 3.2.4.4      | PBA Offset for MSI-X                                         | 28 |

| 3.2.5 | PCI Express  | Extended Capabilities                                        | 29 |

|       | 3.2.5.1      | PCI Express Capabilities List Register                       | 29 |

|       | 3.2.5.2      | PCI Express Capabilities Register                            | 29 |

|       | 3.2.5.3      | Device Capabilities Register                                 | 29 |

|       | 3.2.5.4      | Device Control Register                                      | 30 |

|       | 3.2.5.5      | Device Status Register                                       | 31 |

|       | 3.2.5.6      | Link Capabilities Register                                   | 32 |

|       | 3.2.5.7      | Link Control Register                                        | 32 |

|       | 3.2.5.8      | Link Status Register                                         | 34 |

|       | 3.2.5.9      | Device Capabilities 2 Register                               | 34 |

|       | 3.2.5.10     | Device Control 2 Register                                    | 34 |

|       | 3.2.5.11     | Device Status 2 Register                                     | 35 |

|       | 3.2.5.12     | Link Capabilities 2 Register                                 | 35 |

|       | 3.2.5.13     | Link Control 2 Register                                      | 35 |

|       | 3.2.5.14     | Link Status 2 Register                                       | 36 |

| 3.2.6 | RENESAS S    | Specific Registers                                           | 37 |

|       | 3.2.6.1      | FW Version Register                                          | 37 |

|       | 3.2.6.2      | PHY Control 0 Register                                       | 37 |

|       | 3.2.6.3      | PHY Control 1 Register                                       | 37 |

|       | 3.2.6.4      | PHY Control 2 Register                                       | 38 |

|       | 3.2.6.5      | Host Controller Configuration (HCConfiguration) Register     | 40 |

|       | 3.2.6.6      | External ROM Information Register                            | 42 |

|       | 3.2.6.7      | External ROM Configuration Register                          | 42 |

|       | 3.2.6.8      | FW Download Control and Status Register                      | 42 |

|       | 3.2.6.9      | External ROM Access Control and Status Register              | 43 |

|       | 3.2.6.10     | DATA0 Register                                               | 44 |

|       | 3.2.6.11     | DATA1 Register                                               | 45 |

| 3.2.7 | Advanced E   | rror Reporting Capabilities                                  | 46 |

|       | 3.2.7.1      | Advanced Error Reporting Enhanced Capability Header Register | 46 |

|       | 3.2.7.2      | Uncorrectable Error Status Register                          | 46 |

|       | 3.2.7.3      | Uncorrectable Error Mask Register                            | 47 |

|       | 3.2.7.4      | Uncorrectable Error Severity Register                        | 47 |

|       | 3.2.7.5      | Correctable Error Status Register                            | 48 |

|       | 3.2.7.6      | Correctable Error Mask Register                              | 48 |

|       | 3.2.7.7      | Advanced Error Capabilities and Control Register             | 49 |

|       | 3.2.7.8      | Header Log Register                                          | 49 |

| 3.2.8 | Device Seria | al Number Enhanced Capability                                | 50 |

|       | 3.2.8.1      | Device Serial Number Enhanced Capability Header Register     | 50 |

|       | 3.2.8.2      | Serial Number Register                                       | 50 |

| 3.2.9 | Latency Tole | erance Reporting (LTR) Capability                            | 51 |

|       | 3.2.9.1      | LTR Extended Capability Header Register                      | 51 |

|     |         | 3.2.9.2       | Max Snoop Latency Register                                      | 51 |

|-----|---------|---------------|-----------------------------------------------------------------|----|

|     |         | 3.2.9.3       | Max No-Snoop Latency Register                                   | 51 |

| 3.3 | Host Co | ntroller Ca   | pability Register                                               | 52 |

|     | 3.3.1   | Capability R  | Registers Length (CAPLENGTH)                                    | 52 |

|     | 3.3.2   | Host Contro   | oller Interface Version Number (HCIVERSION)                     | 52 |

|     | 3.3.3   | Structural P  | arameters 1 (HCSPARAMS1)                                        | 53 |

|     | 3.3.4   | Structural P  | arameters 2 (HCSPARAMS2)                                        | 53 |

|     | 3.3.5   | Structural P  | arameters 3 (HCSPARAMS3)                                        | 54 |

|     | 3.3.6   | Capability F  | Parameters (HCCPARAMS)                                          | 54 |

|     | 3.3.7   | Doorbell Of   | fset (DBOFF)                                                    | 56 |

|     | 3.3.8   | Runtime Re    | gister Space Offset (RTSOFF)                                    | 56 |

| 3.4 | Host Co | ntroller Op   | erational Registers                                             | 57 |

|     | 3.4.1   | USB Comm      | and Register (USBCMD)                                           | 58 |

|     | 3.4.2   | USB Status    | Register (USBSTS)                                               | 60 |

|     | 3.4.3   | Page Size F   | Register (PAGESIZE)                                             | 61 |

|     | 3.4.4   | Device Noti   | fication Control Register (DNCTRL)                              | 62 |

|     | 3.4.5   | Command F     | Ring Control Register (CRCR)                                    | 63 |

|     | 3.4.6   |               | text Base Address Array Pointer Register (DCBAAP)               |    |

|     | 3.4.7   | Configure R   | Register (CONFIG)                                               | 65 |

|     | 3.4.8   | Host Contro   | oller Port Register Set                                         | 66 |

|     |         | 3.4.8.1       | Port Status and Control Register (PORTSC)                       | 67 |

|     |         | 3.4.8.2       | Port PM Status and Control Register (PORTPMSC)                  | 72 |

|     |         | 3.4.8.3       | USB3 Protocol PORTPMSC definition                               | 73 |

|     |         | 3.4.8.4       | USB2 Protocol PORTPMSC definition                               |    |

|     |         | 3.4.8.5       | Port Link Info Register (PORTLI)                                |    |

| 3.5 | Host Co |               | ntime Registers                                                 |    |

|     | 3.5.1   |               | Index Register (MFINDEX)                                        |    |

|     | 3.5.2   | Interrupter F | Register Set                                                    |    |

|     |         | 3.5.2.1       | Interrupter Management Register (IMAN)                          |    |

|     |         | 3.5.2.2       | Interrupter Moderation Register (IMOD)                          |    |

|     |         | 3.5.2.3       | Event Ring Segment Table Size Register (ERSTSZ)                 |    |

|     |         | 3.5.2.4       | Event Ring Segment Table Base Address Register (ERSTBA)         |    |

|     |         | 3.5.2.5       | Event Ring Dequeue Pointer Register (ERDP)                      |    |

| 3.6 |         | _             |                                                                 |    |

| 3.7 | xHCI Ex | -             | pabilities                                                      |    |

|     | 3.7.1   | •             | y Support Capability                                            |    |

|     |         | 3.7.1.1       | USB Legacy Support Capability (USBLEGSUP)                       |    |

|     |         | 3.7.1.2       | USB Legacy Support Control / Status (USBLEGCTLSTS)              |    |

|     | 3.7.2   |               | orted Protocol Capability                                       |    |

|     |         | 3.7.2.1       | USB 3.0 Supported Protocol Capability                           |    |

|     |         | 3.7.2.2       | USB 2.0 Supported Protocol Capability                           |    |

|     | 3.7.3   | • •           | ability                                                         |    |

|     |         | 3.7.3.1       | Debug Capability ID Register                                    |    |

|     |         | 3.7.3.2       | Debug Capability Doorbell Register                              |    |

|     |         | 3.7.3.3       | Debug Capability Event Ring Segment Table Size Register         |    |

|     |         | 3.7.3.4       | Debug Capability Event Ring Segment Table Base Address Register |    |

|     |         | 3.7.3.5       | Debug Capability Event Ring Dequeue Pointer Register            |    |

|     |         | 3.7.3.6       | Debug Capability Event Ring Dequeue Pointer Register            |    |

|     |         | 3.7.3.7       | Debug Capability Status Register                                |    |

|     |         | 3.7.3.8       | Debug Capability Port Status and Control Register               |    |

|     |         | 3.7.3.9       | Debug Capability Context Pointer Register                       | 96 |

|         |           | 3.7.3.10 Debug Capability Device Descriptor Info Register 1           | 96  |

|---------|-----------|-----------------------------------------------------------------------|-----|

|         |           | 3.7.3.11 Debug Capability Device Descriptor Info Register 2           | 96  |

| 3.8     | MSI-X/    | PBA Table                                                             | 98  |

|         | 3.8.1     | Message Address for MSI-X Table                                       |     |

|         | 3.8.2     | Message Upper Address for MSI-X Table                                 |     |

|         | 3.8.3     | Message Data for MSI-X                                                |     |

|         | 3.8.4     | Vector Control for MSI-X                                              |     |

|         | 3.8.5     | Pending Bits for MSI-X PBA Entries                                    | 99  |

| 4. Powe | er Manage | ement                                                                 | 100 |

| 4.1     | Power N   | Management States                                                     | 100 |

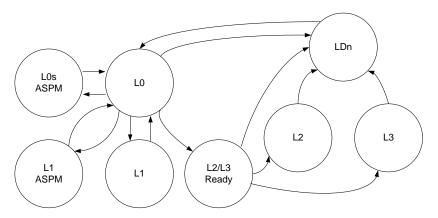

|         | 4.1.1     | PCI Express Link State Power Management (L-States)                    | 100 |

|         | 4.1.2     | PCI Express Device Power Management States (D-States)                 | 101 |

|         | 4.1.3     | CLKREQ# Signal                                                        | 101 |

|         | 4.1.4     | Summary of PCI Express Power Management States                        | 102 |

| 4.2     | Power N   | Management Event (PME) Mechanism                                      | 103 |

|         | 4.2.1     | PME support                                                           |     |

|         | 4.2.2     | Pin configuration for supporting PME generation from D3cold           | 103 |

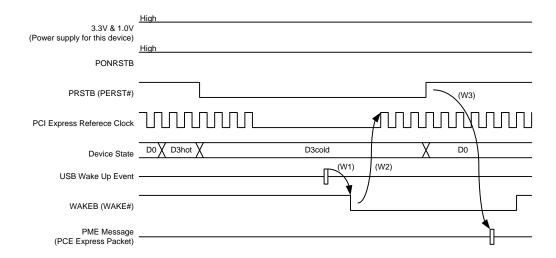

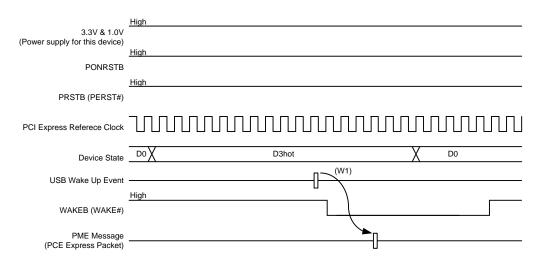

|         | 4.2.3     | Timing Diagram for PME                                                | 104 |

|         | 4.2.4     | Wakeup Events                                                         |     |

| 4.3     | Control   | for System Clock Operation                                            |     |

|         | 4.3.1     | Clock system                                                          |     |

| 4.4     | Latency   | Tolerance Reporting (LTR) mechanism                                   | 108 |

|         | 4.4.1     | Timing of sending LTR message                                         | 108 |

| 5. How  | to Conne  | ct to External Elements                                               | 109 |

| 5.1     | Handlin   | g Unused Pins                                                         | 109 |

| 5.2     | USB Po    | rt Connection                                                         | 110 |

| 5.3     | Analog    | Circuit Connection                                                    | 114 |

| 5.4     | Crystal   | Connection                                                            | 115 |

| 5.5     | Externa   | Serial ROM Connection                                                 | 116 |

| 5.6     | PCI Exp   | ress Interface Connection                                             | 119 |

| 5.7     | SMIB/SI   | MI Interface Connection                                               | 120 |

| 6. How  | to Access | s External ROM                                                        | 121 |

| 6.1     | Access    | External ROM Registers                                                | 121 |

| 6.2     | Access    | External ROM                                                          | 123 |

|         | 6.2.1     | How to write FW to External ROM                                       | 123 |

|         |           | 6.2.1.1 Outline                                                       | 123 |

|         |           | 6.2.1.2 Sequence to write the FW (External ROM data) of µPD720201 and |     |

|         |           | μPD720202                                                             | 123 |

|         | 6.2.2     | How to read ROM Data from External ROM                                | 124 |

|         |           | 6.2.2.1 Outline                                                       | 124 |

|         |           | 6.2.2.2 Sequence to read External ROM data from External ROM          | 124 |

|         | 6.2.3     | How to erase the data of the whole chip to be "1b" (Chip Erase)       |     |

|         |           | 6.2.3.1 Outline                                                       | 124 |

|         |           | 6.2.3.2 Sequence for Chip Erase                                       | 124 |

| 6.3     | Data Fo   | rmat                                                                  |     |

|         | 6.3.1     | Firmware                                                              | 125 |

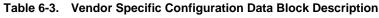

|         | 6.3.2     | Vendor Specific Configuration Data Block                              | 126 |

|         |           | 6.3.2.1 Data Format                                                   | 126 |

|          |           | 6.3.2.2      | Address map for Vendor Specific Configuration Block  | 126 |

|----------|-----------|--------------|------------------------------------------------------|-----|

|          |           | 6.3.2.3      | External ROM Data                                    | 128 |

|          | 6.3.3     | CRC16 cald   | culation                                             | 129 |

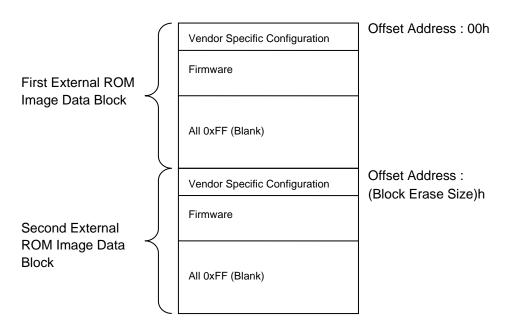

|          | 6.3.4     | External RC  | DM Data format                                       | 130 |

|          |           | 6.3.4.1      | First External ROM Image Data Block of Figure 6-4    | 130 |

|          |           | 6.3.4.2      | Second External ROM Image Data Block of Figure 6-4   | 130 |

|          |           | 6.3.4.3      | Loading the FW from the External ROM                 | 130 |

| 7. FW D  | ownload   | Interface    |                                                      | 132 |

| 7.1      |           |              | a Firmware into <i>µ</i> PD720201/ <i>µ</i> PD720202 |     |

|          | 7.1.1     | FW downloa   | ad registers                                         | 132 |

|          | 7.1.2     | Outline of F | W download sequences                                 | 132 |

|          | 7.1.3     | FW downloa   | ad sequences                                         | 132 |

| 8. Batte | ry Chargi | ing Functio  | on                                                   | 134 |

| 8.1      | , ,       | •            |                                                      |     |

| 8.2      |           |              | Mode                                                 |     |

| 8.3      |           |              |                                                      |     |

|          | 8.3.1     |              | ration requirement                                   |     |

|          |           | •            |                                                      |     |

### LIST OF FIGURES

| Figure No.  | Title                                                              | Page |

|-------------|--------------------------------------------------------------------|------|

| Figure 1-1. | μPD720201 Block Diagram                                            | 3    |

| Figure 1-2. | μPD720202 Block Diagram                                            | 3    |

| Figure 1-3. | Pin Configuration of µPD720201                                     | 5    |

| Figure 1-4. | Pin Configuration of µPD720202                                     | 6    |

|             | Link Power Management State Flow Diagram                           |      |

|             | Wake Up State Transition from D3cold (AUXDET bit = '1')            |      |

| •           | Wake Up State Transition only from D3hot                           |      |

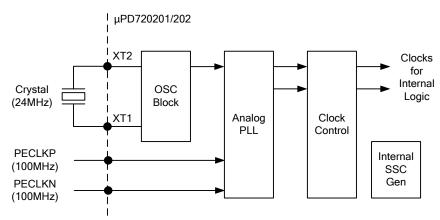

| Figure 4-4. | μPD720201/202's Clock System                                       | 107  |

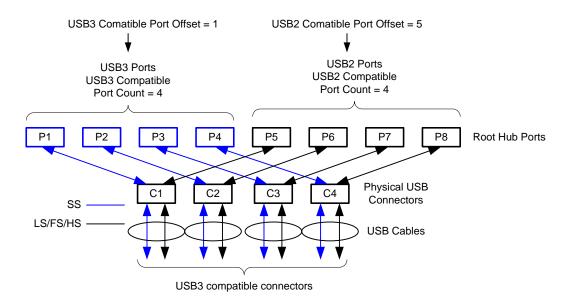

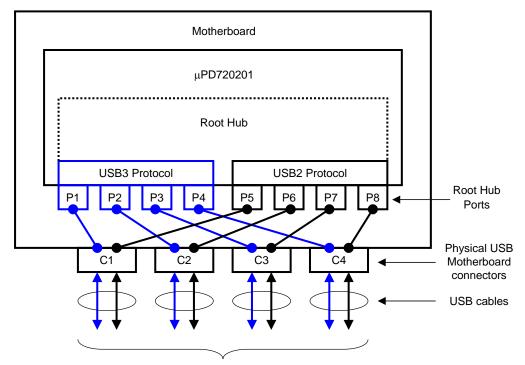

|             | Root Hub Port to USB Connector Mapping of µPD720201                |      |

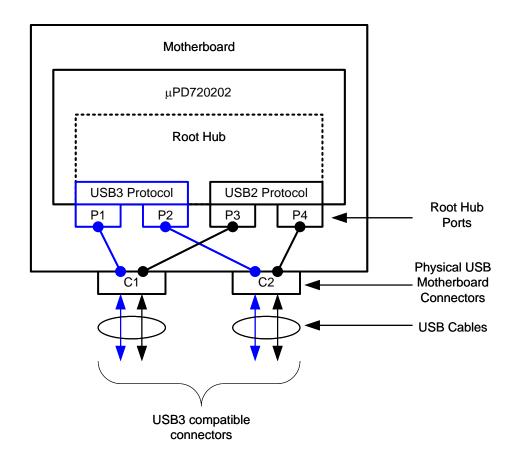

| Figure 5-2. | Root Hub Port to USB Connector Mapping of µPD720202                | 111  |

| •           | USB Downstream Port Connection                                     |      |

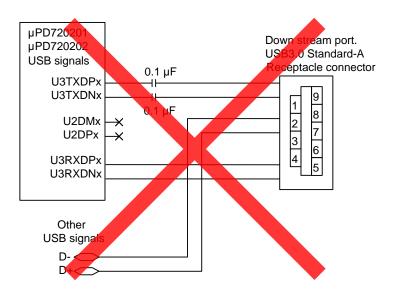

|             | Prohibited USB Downstream Port Connection                          |      |

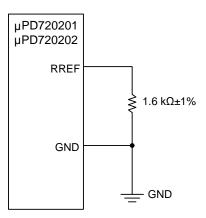

| -           | RREF Connection                                                    |      |

| Ū           | Crystal Connection                                                 |      |

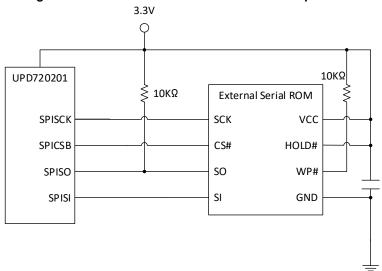

|             | External Serial ROM Connection for µPD720201                       |      |

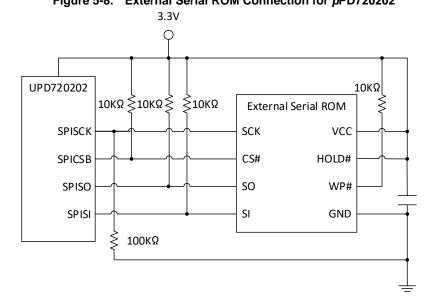

| _           | External Serial ROM Connection for µPD720202                       |      |

| _           | Unused Pins Connection When the External Serial ROM Is Not Mounted |      |

| _           | ). PCI Express Interface Connection                                |      |

| Figure 5-1  | SMIB Interface Connection                                          | 120  |

| Figure 6-1. | Firmware                                                           | 125  |

| Figure 6-2. | Vendor Specific Configuration Data Block                           | 126  |

| Figure 6-3. | External ROM Data                                                  | 128  |

| -           | External ROM Data Format                                           |      |

| Figure 6-5. | Loading FW from External ROM                                       | 131  |

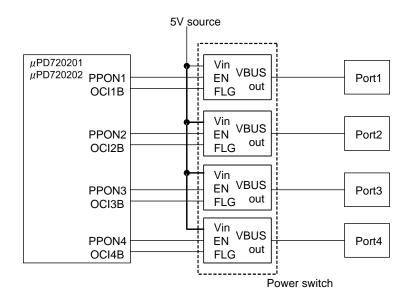

| Figure 8-1. | VBUS Control Configuration with Battery Charging Function          | 135  |

# LIST OF TABLES (1/4)

| Table No.  | Title                                                              | Page |

|------------|--------------------------------------------------------------------|------|

| Table 2-1. | Power Supply                                                       | 7    |

| Table 2-2. | Analog Signal                                                      | 7    |

| Table 2-3. | System Clock                                                       | 7    |

| Table 2-4. | System Interface Signal                                            | 8    |

| Table 2-5. | PCI Express Interface                                              | 8    |

| Table 2-6. | USB Interface                                                      | 9    |

| Table 2-7. | SPI Interface                                                      | 11   |

|            | Register and Register Bit-Field Types                              |      |

|            | PCI Type 0 Configuration Space Header                              |      |

|            | Vendor ID Register (Offset Address: 00h)                           |      |

|            | Device ID Register (Offset Address: 02h)                           |      |

| Table 3-5. | Command Register (Offset Address: 04h)                             | 15   |

|            | Status Register (Offset Address: 06h)                              |      |

| Table 3-7. | Revision ID Register (Offset Address: 08h)                         | 17   |

|            | Class Code Register (Offset Address: 09h)                          |      |

| Table 3-9. | Cache Line Size Register (Offset Address: 0Ch)                     | 17   |

| Table 3-10 | . Latency Timer Register (Offset Address: 0Dh)                     | 18   |

| Table 3-11 | . Header Type Register (Offset Address: 0Eh)                       | 18   |

| Table 3-12 | . BIST Register (Offset Address: 0Fh)                              | 18   |

| Table 3-13 | . Base Address Register #0 (Offset Address: 10h)                   | 18   |

| Table 3-14 | . Base Address Register #1 (Offset Address: 14h)                   | 19   |

| Table 3-15 | . Subsystem Vendor ID Register (Offset Address: 2Ch)               | 19   |

| Table 3-16 | . Subsystem ID Register (Offset Address: 2Eh)                      | 19   |

| Table 3-17 | . Capabilities Pointer Register (Offset Address: 34h)              | 19   |

| Table 3-18 | . Interrupt Line Register (Offset Address: 3Ch)                    | 20   |

| Table 3-19 | . Interrupt Pin Register (Offset Address: 3Dh)                     | 20   |

| Table 3-20 | . Min_Gnt Register (Offset Address: 3Eh)                           | 20   |

| Table 3-21 | . Max_Lat Register (Offset Address: 3Fh)                           | 20   |

| Table 3-22 | . SBRN Register (Offset Address: 60h)                              | 20   |

| Table 3-23 | . FLADJ Register (Offset Address: 61h)                             | 21   |

| Table 3-24 | Capabilities List Register (Offset Address: 50h)                   | 22   |

| Table 3-25 | PMC Register (Offset Address: 52h)                                 | 22   |

|            | PMSC Register (Offset Address: 54h)                                |      |

|            | Capabilities List Register (Offset Address: 70h)                   |      |

|            | Message Control Register (Offset Address: 72h)                     |      |

|            | Message Address Register (Offset Address: 74h)                     |      |

|            | Message Upper Address Register (Offset Address: 78h)               |      |

|            | . Message Data Register (Offset Address: 7Ch)                      |      |

|            | Mask Bits Register (Offset Address: 80h)                           |      |

|            | Pending Bits Register (Offset Address: 84h)                        |      |

|            | Capabilities List Register (Offset Address: 90h)                   |      |

|            | . Message Control Register (Offset Address: 92h)                   |      |

|            | . Table Offset / Table BIR Register (Offset Address: 94h)          |      |

|            | . Message Upper Address Register (Offset Address: 98h)             |      |

|            | PCI Express Capabilities List Register (Offset Address: A0h)       |      |

|            | PCI Express Capabilities Capability Register (Offset Address: A2h) |      |

# LIST OF TABLES (2/4)

| Table No.   | Title                                                                               | Page |

|-------------|-------------------------------------------------------------------------------------|------|

| Table 3-40. | Device Capabilities Register (Offset Address: A4h)                                  | 29   |

| Table 3-41. | Device Control Register (Offset Address: A8h)                                       | 30   |

| Table 3-42. | Device Status Register (Offset Address: AAh)                                        | 31   |

| Table 3-43. | Link Capabilities Register (Offset Address: ACh)                                    | 32   |

|             | Link Control Register (Offset Address: B0h)                                         |      |

| Table 3-45. | Link Status Register (Offset Address: B2h)                                          | 34   |

| Table 3-46. | Device Capabilities 2 Register (Offset Address: C4h)                                | 34   |

| Table 3-47. | Device Control 2 Register (Offset Address: C8h)                                     | 34   |

| Table 3-48. | Device Status 2 Register (Offset Address: CAh)                                      | 35   |

| Table 3-49. | Link Capabilities 2 Register (Offset Address: CCh)                                  | 35   |

| Table 3-50. | Link Control 2 Register (Offset Address: D0h)                                       | 35   |

| Table 3-51. | Link Status 2 Register (Offset Address: D2h)                                        | 36   |

| Table 3-52. | FW Register (Offset Address: 6Ch)                                                   | 37   |

| Table 3-53. | PHY Control 0 Register (Offset Address: DCh)                                        | 37   |

| Table 3-54. | PHY Control 1 Register (Offset Address: E0h)                                        | 37   |

| Table 3-55. | PHY Control 2 Register (Offset Address: E4h)                                        | 38   |

| Table 3-56. | HCConfiguration Register (Offset Address: E8h)                                      | 40   |

| Table 3-57. | External ROM Information Register (Offset Address: ECh)                             | 42   |

| Table 3-58. | External ROM Configuration Register (Offset Address: F0h)                           | 42   |

| Table 3-59. | FW Download Control and Status Register (Offset Address: F4h)                       | 42   |

| Table 3-60. | FW Control and Status Register (Offset Address: F6h)                                | 43   |

| Table 3-61. | DATA0 Register (Offset Address: F8h)                                                | 44   |

| Table 3-62. | DATA1 Register (Offset Address: FCh)                                                | 45   |

| Table 3-63. | Advanced Error Reporting Enhanced Capability Header Register (Offset Address: 100h) | 46   |

| Table 3-64. | Uncorrectable Error Status Register (Offset Address: 104h)                          | 46   |

| Table 3-65. | Uncorrectable Error Status Register (Offset Address: 108h)                          | 47   |

| Table 3-66. | Uncorrectable Error Severity Register (Offset Address: 10Ch)                        | 47   |

| Table 3-67. | Correctable Error Status Register (Offset Address: 110h)                            | 48   |

| Table 3-68. | Correctable Error Mask Register (Offset Address: 114h)                              | 48   |

| Table 3-69. | Advanced Error Capabilities and Control Register (Offset Address: 118h)             | 49   |

| Table 3-70. | Header Log Register (Offset Address: 11Ch)                                          | 49   |

| Table 3-71. | Device Serial Number Enhanced Capability Header Register (Offset Address: 140h)     | 50   |

| Table 3-72. | Serial Number Register (Offset Address: 144h)                                       | 50   |

| Table 3-73. | LTR Extended Capability Header Register (Offset Address: 150h)                      | 51   |

| Table 3-74. | Max Snoop Latency Register (Offset Address: 154h)                                   | 51   |

| Table 3-75. | Max No-Snoop Latency Register (Offset Address: 156h)                                | 51   |

| Table 3-76. | eXtensible Host Controller Capability                                               | 52   |

| Table 3-77. | CAPLENGTH (Offset Address: Base + 00h)                                              | 52   |

| Table 3-78. | HCIVERSION (Offset Address: Base + 02h)                                             | 52   |

| Table 3-79. | HCSPARAMS1 (Offset Address: Base + 04h)                                             | 53   |

| Table 3-80. | HCSPARAMS2 (Offset Address: Base + 08h)                                             | 53   |

| Table 3-81. | HCSPARAMS3 (Offset Address: Base + 0Ch)                                             | 54   |

| Table 3-82. | HCCPARAMS (Offset Address: Base + 10h)                                              | 54   |

| Table 3-83. | DBOFF (Offset Address: Base + 14h)                                                  | 56   |

| Table 3-84. | RTSOFF Offset (Offset Address: Base + 18h)                                          | 56   |

| Table 3-85. | Host Controller Operational Registers                                               | 57   |

| Table 3-86. | USBCMD Register (Offset Address: Operational Base (20h) + 00h)                      | 58   |

# LIST OF TABLES (3/4)

| Table No.   | Title                                                                                                          | Page |

|-------------|----------------------------------------------------------------------------------------------------------------|------|

| Table 3-87. | USBSTS Register (Offset Address: Operational Base (20h) + 04h)                                                 | 60   |

| Table 3-88. | PAGESIZE Register (Offset Address: Operational Base (20h) + 08h)                                               | 61   |

|             | DNCTRL Register (Offset Address: Operational Base (20h) + 14h)                                                 |      |

| Table 3-90. | CRCR Register (Offset Address: Operational Base (20h) + 18h)                                                   | 63   |

|             | DCBAAP Register (Offset Address: Operational Base (20h) + 30h)                                                 |      |

|             | CONFIG Register (Offset Address: Operational Base (20h) + 38h)                                                 |      |

|             | Host Controller Port Register Set (Offset shows from Base)                                                     |      |

|             | PORTSC Register (Offset Address: Operational Base (20h) + (400h + (10h *(n-1)))                                |      |

|             | PLS Write Value                                                                                                |      |

| Table 3-96. | PLS Read Value                                                                                                 | 72   |

| Table 3-97. | PLS transitions                                                                                                | 72   |

| Table 3-98. | USB3 PORTPMSC Register (Offset Address: Operational Base (20h) + (404h + (10h*(n-1)))                          | 73   |

|             | USB2 PORTPMSC Register (Offset Address: Operational Base (20h) +(404h + (10h*(n-1)))                           |      |

|             | USB3 PORTLI Register (Offset Address: Operational Base (20h) + (408h + (10h * (n-1)))                          |      |

|             | . Host Controller Runtime Registers                                                                            |      |

|             | MFINDEX Register (Offset Address: Runtime Base (600h) + 00h)                                                   |      |

|             | Interrupter Register Set                                                                                       |      |

|             | . IMAN Register (Offset Address: Runtime Base (600h) + 020h + (20h*Interrupter))                               |      |

|             | . IMOD Register (Offset Address: Runtime Base (600h) + 024h + (20h*Interrupter))                               |      |

|             | ERSTSZ Register (Offset Address: Runtime Base (600h) + 028h + (20h*Interrupter))                               |      |

|             | . ERSTBA Register (Offset Address: Runtime Base (600h) + 30h + (20h*Interrupter))                              |      |

|             | ERDP Register (Offset Address: Runtime Base (600h) + 038h + (20h*Interrupter))                                 |      |

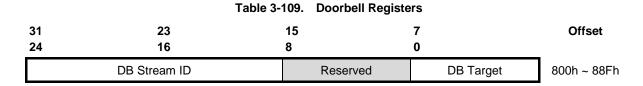

|             | Doorbell Registers                                                                                             |      |

|             | Doorbell Register                                                                                              |      |

| Table 3-111 | . HC Extended Capability Registers                                                                             | 83   |

|             | USBLEGSUP (Offset Address: xECP (500h) + 00h)                                                                  |      |

|             | USBLEGCTLSTS (Offset Address: xECP (500h) + 04h)                                                               |      |

|             | xHCI Supported Protocol Capability Register                                                                    |      |

|             | <ul> <li>Offset 00h - xHCl Supported Protocol Capability Field (Offset Address: xECP + 10h (510h)).</li> </ul> |      |

|             | 5. Offset 04h - xHCl Supported Protocol Capability Field (Offset Address: xECP + 14h (514h)).                  |      |

| Table 3-117 | . Offset 08h - xHCl Supported Protocol Capability Field (Offset Address: xECP + 18h (518h)).                   | 86   |

|             | s. Offset 0Ch - xHCl Supported Protocol Capability Field (Offset Address: xECP + 1Ch (51Ch))                   |      |

| Table 3-119 | . Offset 00h - xHCl Supported Protocol Capability Field (Offset Address: xECP + 24h (524h)).                   | 87   |

|             | . Offset 04h - xHCl Supported Protocol Capability Field (Offset Address: xECP + 28h (528h)).                   |      |

|             | . Offset 08h - xHCl Supported Protocol Capability Field (Offset Address: xECP + 2Ch (52Ch))                    |      |

|             | . Offset 0Ch - xHCl Supported Protocol Capability Field (Offset Address: xECP + 30h (530h)).                   |      |

|             | B. Debug Capability Register Layout                                                                            |      |

|             | Offset 00h – Debug Capability Field (Offset Address: xECP + 50h (550h))                                        |      |

|             | 5. Offset 04h – Debug Capability Field (Offset Address: xECP + 54h (554h))                                     |      |

|             | 5. Offset 08h – Debug Capability Field (Offset Address: xECP + 58h (558h))                                     |      |

|             | . Offset 0Ch – Debug Capability Field (Offset Address: xECP + 60h (560h))                                      |      |

|             | s. Offset 18h – Debug Capability Field (Offset Address: xECP + 68h (568h))                                     |      |

|             | Offset 20h – Debug Capability Field (Offset Address: xECP + 70h (570h))                                        |      |

|             | Offset 24h – Debug Capability Field (Offset Address: xECP + 74h (574h))                                        |      |

|             | Offset 28h – Debug Capability Field (Offset Address: xECP + 78h (578h))                                        |      |

|             | 2. Offset 30h – Debug Capability Field (Offset Address: xECP + 80h (580h))                                     |      |

|             | 3. Offset 38h – Debug Capability Field (Offset Address: xECP + 88h (588h))                                     |      |

# LIST OF TABLES (4/4)

| Table No.  | Title                                                                        | Page |

|------------|------------------------------------------------------------------------------|------|

| Table 3-13 | 34. Offset 3Ch – Debug Capability Field (Offset Address: xECP + 8Ch (58Ch))  | 96   |

| Table 3-13 | 35. MSI-X Table Registers                                                    | 98   |

| Table 3-13 | 36. PBA Table Registers                                                      | 98   |

| Table 3-13 | 37. Message Address (Offset Address: Base + 1000h + (10h*Interrupter))       | 98   |

| Table 3-13 | 88. Message Upper Address (Offset Address: Base + 1004h + (10h*Interrupter)) | 98   |

| Table 3-13 | 39. Message Data (Offset Address: Base + 1008h + (10h*Interrupter))          | 98   |

| Table 3-14 | 40. Message Data (Offset Address: Base + 100Ch + (10h*Interrupter))          | 99   |

| Table 3-14 | 11. Message Data (Offset Address: Base + 1080h)                              | 99   |

| Table 4-1. | PCI Express Link States                                                      | 100  |

| Table 4-2. | PCI Express Device Power Management States                                   | 101  |

| Table 4-3. | Operation of CLKREQ# Signal                                                  | 101  |

| Table 4-4. | Summary of PCI Express Power Management States                               | 102  |

| Table 4-5. | Wakeup Events                                                                | 106  |

| Table 5-1. | Unused Pin Connection                                                        | 109  |

| Table 5-2. | Port configuration for µPD720201                                             | 109  |

| Table 5-3. | Port configuration for µPD720202                                             | 109  |

| Table 5-4. | Supported External Serial ROM List (A)                                       | 118  |

| Table 5-5. | Supported External Serial ROM List (B)                                       | 118  |

| Table 6-1. | External ROM Information & Parameter                                         | 122  |

| Table 6-2. | Firmware Block Description                                                   | 125  |

| Table 6-3. | Vendor Specific Configuration Data Block Description                         | 126  |

| Table 6-4. | Address Map for Vendor Specific Configuration Block                          | 126  |

| Table 8-1. | Battery Charging Mode                                                        | 134  |

### μPD720201/μPD720202 ASSP (USB3.0 HOST CONTROLLER)

R19UH0078EJ0710 Rev. 7.10 Sep 25, 2023

### 1. Overview

The  $\mu$ PD720201 and  $\mu$ PD720202 are Renesas' third generation Universal Serial Bus 3.0 host controllers, which comply with Universal Serial Bus 3.0 Specification, and Intel's eXtensible Host Controller Interface (xHCI). These devices reduce power consumption and offer a smaller package footprint making them ideal for designers who wish to add the USB3.0 interface to mobile computing devices such as laptops and notebook computers.

The  $\mu$ PD720201 supports up to four USB3.0 SuperSpeed ports and the  $\mu$ PD720202 supports up to two USB3.0 SuperSpeed ports. The  $\mu$ PD720201 and  $\mu$ PD720202 use a PCI Express® Gen 2 system interface bus allowing system designers to easily add up to four ( $\mu$ PD720201) or two ( $\mu$ PD720202) USB3.0 SuperSpeed ports to systems containing the PCI Express bus interface. When connected to USB 3.0-compliant peripherals, the  $\mu$ PD720201 and  $\mu$ PD720202 can transfer information at clock speeds of up to 5 Gbps. The  $\mu$ PD720201 and  $\mu$ PD720202 and USB 3.0 standard are fully compliant and backward compatible with the previous USB2.0 standard. The new USB 3.0 standard supports data transfer speeds of up to ten times faster than those of the previous-generation USB2.0 standard, enabling quick and efficient transfers of large amounts of information.

### 1.1 Features

- Compliant with Universal Serial Bus 3.0 Specification Revision 1.0, which is released by USB Implementers Forum, Inc

- Supports the following speed data rates: Low-Speed (1.5 Mbps) / Full-Speed (12 Mbps) / Hi-Speed (480 Mbps) / SuperSpeed (5 Gbps)

- μPD720201 supports up to 4 downstream ports for all speeds

- µPD720202 supports up to 2 downstream ports for all speeds

- Supports all USB compliant data transfer types as follows; Control / Bulk / Interrupt / Isochronous transfer

- Compliant with Intel's eXtensible Host Controller Interface (xHCI) Specification Revision 1.0

- Supports USB debugging capability on all SuperSpeed ports.

- Supports USB legacy function

- Compliant with PCI Express Base Specification Revision 2.0

- Supports Latency Tolerance Reporting ECN of PCI Express Specification

- Supports ExpressCard<sup>™</sup> Standard Release1.0

- Supports PCI Express Card Electromechanical Specification Revision 2.0

- Supports PCI Bus Power Management Interface Specification Revision 1.2

- Supports USB Battery Charging Specification Revision 1.2 and other portable devices

- DCP mode of BC 1.2

- CDP mode of BC 1.2

- China Mobile Phone Chargers

- EU Mobile Phone Chargers

- Apple iOS products

- Operational registers are direct-mapped to PCI memory space

- Supports Serial Peripheral Interface (SPI) type ROM for Firmware

- Supports Firmware Download Interface from system BIOS or system software

- System clock: 24 MHz crystal

• Small and low count pin package with improved signal pin assignment for efficient PCB layout

- μPD720201 adopts 68pin QFN (8 x 8)

- μPD720202 adopts 48pin QFN (7 x 7)

- 3.3 V and 1.05 V power supply

### 1.2 Applications

Desktop and Laptop computers, Tablet, Server, PCI Express Card / Express Card, Digital TV, Set-Top-Box, BD Player/Recorder, Media Player, Digital Audio systems, Projector, Multi Function Printer, Storage, Router, NAS, etc

### 1.3 Ordering Information

| Part Number              | Package            | Packing form                                                        | Operating temperature | Remark            |

|--------------------------|--------------------|---------------------------------------------------------------------|-----------------------|-------------------|

| μPD720201K8-701-BAC-A    | 68-pin QFN (8 × 8) | Fraction (any vacancy in the                                        |                       |                   |

| μPD720202K8-701-BAA-A    |                    | tray and any free space in the carton)                              | 0 to 85 °C            | Lead-free product |

| μPD720202K8-701-BAA-M1-A | 48-pin QFN (7 x 7) | Full Carton<br>(tray and Carton is<br>packed with every<br>product) |                       |                   |

| μPD720201K8-711-BAC-A    | 60 pip OFN (0 9)   | Fraction                                                            |                       |                   |

| μPD720201K8-711-BAC-M1-A | 68-pin QFN (8 × 8) | Full Carton                                                         | 40.45.05.00           |                   |

| μPD720202K8-711-BAA-A    | 40 min OFN (7 v 7) | Fraction                                                            | −40 to 85 °C          | Lead-free product |

| μPD720202K8-711-BAA-M1-A | 48-pin QFN (7 x 7) | Full Carton                                                         |                       |                   |

**Note:**  $\mu$ PD720201K8-711-BAC-A &  $\mu$ PD720201K8-711-BAC-M1-A &  $\mu$ PD720202K8-711-BAA-A &  $\mu$ PD720202K8-711-BAA-A should should use the FW Download function.

$\mu$ PD720201K8-711-BAC-A &  $\mu$ PD720201K8-711-BAC-M1-A &  $\mu$ PD720202K8-711-BAA-A &  $\mu$ PD720202K8-711-BAA-M1-A should do not support the External ROM (Serial Peripheral Interface (SPI) type ROM).  $\mu$ PD720201 &  $\mu$ PD720202 should download the firmware from the External ROM (-701 versions only) or by FW download function after Power on Reset.

Regarding External ROM & FW Download function, refer to "6.How to Access External ROM" & "7. FW Download Interface".

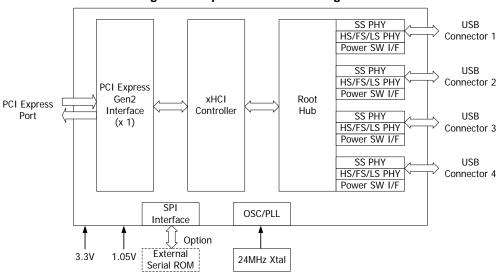

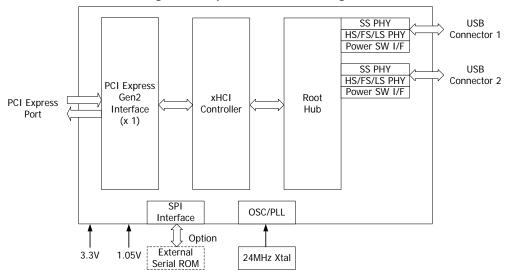

### 1.4 Block Diagram

Figure 1-1. µPD720201 Block Diagram

Figure 1-2. µPD720202 Block Diagram

| PCI Express<br>Gen2 Interface | Complies with PCI Express Gen2 interface, with 1 lane. This block includes both the link and PHY layers.                                          |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| xHCI Controller               | Handles all support required for USB 3.0, SuperSpeed and Hi-/Full-/Low-Speed. This block includes the register interface from the system.         |

| Root hub                      | Hub function in host controller.                                                                                                                  |

| SS PHY                        | For SuperSpeed Tx/Rx                                                                                                                              |

| HS/FS/LS PHY                  | For Hi-/Full-/Low-Speed Tx/Rx                                                                                                                     |

| Power SW I/F                  | Connected to external power switch for port power control and over current detection.                                                             |

| SPI Interface                 | Connected to external serial ROM. When system BIOS or system software does not support FW download function, the external serial ROM is required. |

| OSC                           | Internal oscillator block.                                                                                                                        |

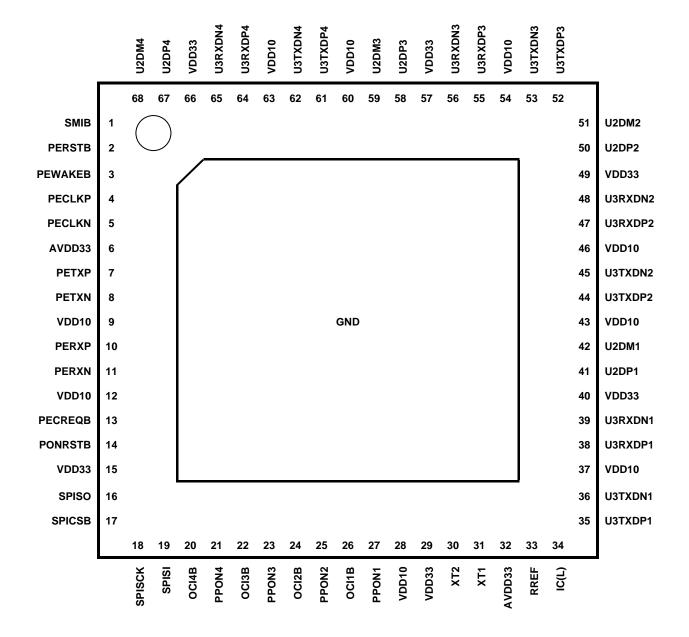

### 1.5 Pin Configuration (TOP VIEW)

68-pin QFN (8 × 8)

μPD720201K8-701-BAC-A

μPD720201K8-711-BAC-A

μPD720201K8-711-BAC-M1-A

Figure 1-3. Pin Configuration of  $\mu$ PD720201

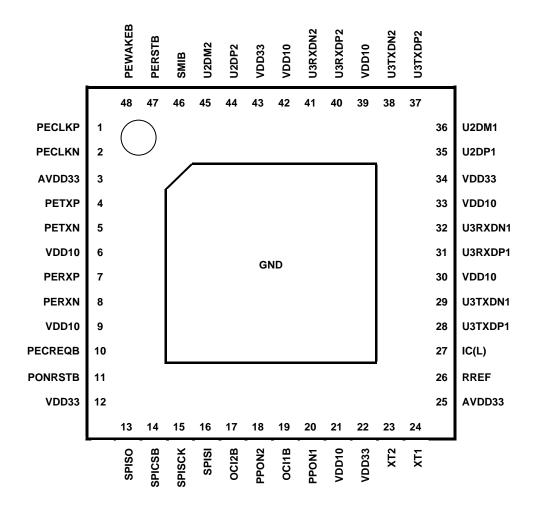

### • 48-pin QFN (7 x 7)

μPD720202K8-701-BAA-A

μPD720202K8-701-BAA-M1-A

μPD720202K8-711-BAA-A

μPD720202K8-711-BAA-M1-A

Figure 1-4. Pin Configuration of  $\mu$ PD720202

# 2. Pin Function

This section describes each pin functions.

# 2.1 Power supply

Table 2-1. Power Supply

| Pin<br>Name | 720201<br>Pin No.                       | 720202<br>Pin No.           | I/O<br>Type | Function                                |

|-------------|-----------------------------------------|-----------------------------|-------------|-----------------------------------------|

| VDD33       | 15, 29, 40, 49,<br>57, 66               | 12, 22, 34, 43              | Power       | +3.3 V power supply                     |

| VDD10       | 9, 12, 28, 37,<br>43, 46, 54, 60,<br>63 | 6, 9, 21, 30, 33,<br>39, 42 | Power       | +1.05 V power supply.                   |

| AVDD33      | 6, 32                                   | 3, 25                       | Power       | +3.3 V power supply for analog circuit. |

| GND         | GND PAD                                 | GND PAD                     | Power       | Connect to ground.                      |

| IC(L)       | 34                                      | 27                          | I           | Test pin. Connect to ground.            |

# 2.2 Analog Signal

Table 2-2. Analog Signal

| Pin  | 720201  | 720202  | I/O  | Active | Function                       |

|------|---------|---------|------|--------|--------------------------------|

| Name | Pin No. | Pin No. | Type | Level  |                                |

| RREF | 33      | 26      | USB2 | -      | Reference resistor connection. |

# 2.3 System clock

Table 2-3. System Clock

| Pin<br>Name | 720201<br>Pin No. | 720202<br>Pin No. | Туре       | Active<br>Level | Function                                    |

|-------------|-------------------|-------------------|------------|-----------------|---------------------------------------------|

| XT1         | 31                | 24                | (OSC)      | _               | Oscillator in Connect to 24 MHz crystal. *  |

| XT2         | 30                | 23                | O<br>(OSC) | _               | Oscillator out Connect to 24 MHz crystal. * |

**Note 1:** An external modular oscillator cannot be used instead of a crystal, due to aggressive clock management in reduced power states.

$\mu$ PD720201/ $\mu$ PD720202 2. Pin Function

### 2.3.1 System Interface signal

Table 2-4. System Interface Signal

| Pin Name | 720201<br>Pin No. | 720202<br>Pin No. | I/O<br>Type                      | Active<br>Level | Function                                                                                                                         |

|----------|-------------------|-------------------|----------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------|

| PONRSTB  | 14                | 11                | I<br>(3.3 V<br>Schmitt<br>Input) | Low             | Power on reset signal. When supporting wakeup from D3cold, this signal should be pulled high with system auxiliary power supply. |

| SMIB     | 1                 | 46                | O<br>(3.3 V<br>Output)           | Low             | System management Interrupt signal. This is controlled with the USB Legacy Support Control/Status register.                      |

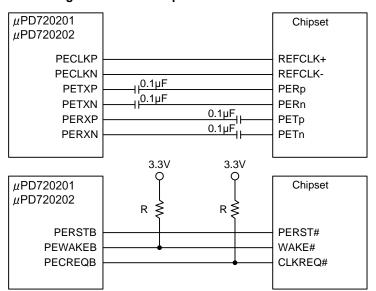

### 2.3.2 PCI Express Interface

Table 2-5. PCI Express Interface

| Pin Name | 720201<br>Pin No. | 720202<br>Pin No. | I/O<br>Type           | Active<br>Level | Function                                                                                                                                   |

|----------|-------------------|-------------------|-----------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| PECLKP   | 4                 | 1                 | I<br>(PCIE)           | _               | PCI Express 100 MHz Reference Clock.                                                                                                       |

| PECLKN   | 5                 | 2                 | I<br>(PCIE)           | _               | PCI Express 100 MHz Reference Clock.                                                                                                       |

| PETXP    | 7                 | 4                 | O<br>(PCIE)           | _               | PCI Express Transmit Data+.                                                                                                                |

| PETXN    | 8                 | 5                 | O<br>(PCIE)           | _               | PCI Express Transmit Data                                                                                                                  |

| PERXP    | 10                | 7                 | I<br>(PCIE)           | _               | PCI Express Receive Data+.                                                                                                                 |

| PERXN    | 11                | 8                 | I<br>(PCIE)           | _               | PCI Express Receive Data                                                                                                                   |

| PERSTB   | 2                 | 47                | I<br>(3.3 V<br>Input) | Low             | PCI Express "PERST#" signal.                                                                                                               |

| PEWAKEB  | 3                 | 48                | O<br>(Open<br>Drain)  | Low             | PCI Express "WAKE#" signal. This signal is used for remote wakeup mechanism, and requests the recovery of power and reference clock input. |

| PECREQB  | 13                | 10                | O<br>(Open<br>Drain)  | Low             | PCI Express "CLKREQ#" signal. This signal is used to request run/stop of reference clock.                                                  |

### 2.3.3 USB Interface

Table 2-6. USB Interface

| Pin Name | 720201<br>Pin No. | 720202<br>Pin No. | I/O<br>Type       | Active<br>Level | Function                                      |

|----------|-------------------|-------------------|-------------------|-----------------|-----------------------------------------------|

| U3TXDP1  | 35                | 28                | O<br>(USB3)       | Ι               | USB3.0 Transmit data D+ signal for SuperSpeed |

| U3TXDN1  | 36                | 29                | O<br>(USB3)       | ı               | USB3.0 Transmit data D- signal for SuperSpeed |

| U3RXDP1  | 38                | 31                | l<br>(USB3)       | ı               | USB3.0 Receive data D+ signal for SuperSpeed  |

| U3RXDN1  | 39                | 32                | l<br>(USB3)       | ı               | USB3.0 Receive data D- signal for SuperSpeed  |

| U2DP1    | 41                | 35                | I/O<br>(USB2)     | 1               | USB2.0 D+ signal for Hi-/Full-/Low-Speed      |

| U2DM1    | 42                | 36                | I/O<br>(USB2)     | -               | USB2.0 D- signal for Hi-/Full-/Low-Speed      |

| OCI1B    | 26                | 19                | 1 (2.2.)/         | Low             | Over-current status input signal.             |

|          |                   |                   | (3.3 V<br>Input)  |                 | 0: Over-current condition is detected         |

|          |                   |                   |                   |                 | 1: No over-current condition is detected      |

| PPON1    | 27                | 20                | O<br>(3.3 V       | High            | USB port power supply control signal.         |

|          |                   |                   | Output)           |                 | 0: Power supply OFF                           |

|          |                   |                   | _                 |                 | 1: Power supply ON                            |

| U3TXDP2  | 44                | 37                | O<br>(USB3)       | _               | USB3.0 Transmit data D+ signal for SuperSpeed |

| U3TXDN2  | 45                | 38                | O<br>(USB3)       | I               | USB3.0 Transmit data D- signal for SuperSpeed |

| U3RXDP2  | 47                | 40                | (USB3)            | ı               | USB3.0 Receive data D+ signal for SuperSpeed  |

| U3RXDN2  | 48                | 41                | I<br>(USB3)       | _               | USB3.0 Receive data D- signal for SuperSpeed  |

| U2DP2    | 50                | 44                | I/O<br>(USB2)     | _               | USB2.0 D+ signal for Hi-/Full-/Low-Speed      |

| U2DM2    | 51                | 45                | I/O<br>(USB2)     | _               | USB2.0 D- signal for Hi-/Full-/Low-Speed      |

| OCI2B    | 24                | 17                | I                 | Low             | Over-current status input signal.             |

|          |                   |                   | (3.3 V<br>Input)  |                 | 0: Over-current condition is detected         |

|          |                   |                   | πιραι)            |                 | 1: No over-current condition is detected      |

| PPON2    | 25                | 18                | 0                 | High            | USB port power supply control signal.         |

|          |                   |                   | (3.3 V<br>Output) |                 | 0: Power supply OFF                           |

|          |                   |                   | Catput            |                 | 1: Power supply ON                            |

| Pin Name | 720201<br>Pin No. | 720202<br>Pin No. | I/O<br>Type       | Active<br>Level | Function                                      |

|----------|-------------------|-------------------|-------------------|-----------------|-----------------------------------------------|

| U3TXDP3  | 52                | _                 | O<br>(USB3)       | -               | USB3.0 Transmit data D+ signal for SuperSpeed |

| U3TXDN3  | 53                | _                 | O<br>(USB3)       | -               | USB3.0 Transmit data D- signal for SuperSpeed |

| U3RXDP3  | 55                | -                 | (USB3)            | -               | USB3.0 Receive data D+ signal for SuperSpeed  |

| U3RXDN3  | 56                | _                 | l<br>(USB3)       | ı               | USB3.0 Receive data D- signal for SuperSpeed  |

| U2DP3    | 58                | _                 | I/O<br>(USB2)     | ı               | USB2.0 D+ signal for Hi-/Full-/Low-Speed      |