# **CMOS ternary logic circuits**

X.W. Wu Prof. F.P. Prosser. **PhD**

Indexing terms: Logic, Digital arithmetic, Metal-oxide-semiconductor structures

Abstract: We review the main difficulties and advantages in developing CMOS ternary circuits. In addition to employing multiple power sources and multiple thresholds, we describe a new theory of transmission functions for designing CMOS ternary logic circuits. It can explain the main CMOS ternary circuits proposed previously. Computer simulations show that the circuits based on the transmission-function theory have more desirable transfer characteristics than ones with resistors.

#### 1 Introduction

The practical goal of multivalued logic (MVL) research is to direct the design and fabrication of multivalued circuits. In theory, multivalued circuits should enjoy the following advantages over their binary counterparts:

- (a) since each wire can transmit more MVL information than binary, the number of connections inside the chip can be reduced

- (b) since each MVL element can process more information than a binary element, the complexity of circuits may be decreased

- (c) the connections on- and off-chip can be reduced to help alleviate the pin-out difficulties that arise with increasingly larger chips

- (d) the speed of serial information transmission will be. faster since the transmitted information p.u. time is increased.

However, theory also predicts several disadvantages of MVL circuits

- (i) for fixed values of the highest and lowest voltages, the tolerances of circuits with more logic levels will be more critical than with binary circuits

- (ii) to realise low-output impedance, additional sources of power are needed to produce the intermediate voltage outputs

- (iii) the complexity of fabricating an MVL circuit may be increased since the elements in a circuit must deal with multivalued signals.

Why have we focussed on ternary CMOS circuits? Ternary and quaternary circuits have been studied increasingly in recent years. Quaternary circuits have the practical advantage that a four-valued signal can easily be transformed into a two-valued signal. However, based

Paper 6934G (E10), first received 19th April 1988 and in revised form 12th July 1989

Mr. Wu is with the Department of Physics, Hangzhou University, Hangzhou, People's Republic of China

Prof. Prosser is with the Department of Computer Science, Indiana University, Bloomington, IN 47405, USA

on the following considerations, we feel that ternary circuits may be of more theoretical significance than quaternary:

- (a) since 3 is the smallest radix higher than binary, ternary functions and circuits have the simpler **form** and construction. They can be studied and discussed easily, yet they still display the characteristics of multivalued elements

- (b) As a measure of the cost or complexity of multivalued circuits, the product of the radix and the number of signals has been proposed. Since 3 is the digit nearest to e = 2.718, ternary circuits will be more economical according to this measure [1]

- (c) if balanced ternary logic (1, 0, -1) is used, the same hardware may be used for addition and for subtraction

- (d) since 3 is not an integral power of 2, research on ternary logic may disclose design techniques that are overlooked in the study of binary or quaternary logic.

CMOS integrated-circuit technology is the choice for **rea**lising ternary logic for the following reasons:

- (i) CMOS multivalued circuits are expected to share three principal advantages of CMOS binary circuits: zero static power dissipation in either stable state, low-output impedance in either state and elimination of passive elements (resistors)

- (ii) any multivalued signal can be transmitted through a CMOS transmission gate

- (iii) in contrast with the pn-junction threshold of a bipolar transistor, the MOS transistor's threshold may easily be changed during fabrication, simplifying the task of responding to a multilevel input signal

- (iv) since the first CMOS ternary circuits were proposed by Mouftah and Jordan in 1974 [2], they have received more attention than other multivalued circuits.

The standards for evaluating proposed circuit designs and the tactics used in the research should be set out in advance. The goal of research in multivalued circuits is to overcome difficulties of binary VLSI with too high density and too many connections. Therefore, we may establish the following criteria for evaluating proposed circuit designs:

- (a) is the circuit suitable for VLSI implementation?

- (b) are the circuit's electrical parameters competitive with its binary counterpart?

- (c) can the circuit be functionally and electrically compatible with a binary circuit in a mixed-radix system?

The research tactics are

- (i) to derive experience and understanding from the theory and circuit design of CMOS binary circuits

- (ii) to use a suitable algebraic system as a guide for describing the function and realisation of a circuit

- (iii) to evaluate a proposed circuit design using the criteria given above, and then to analyse and improve the design

### 2 Logic levels and traditional algebra

In a ternary system there are three logic levels (2, 1, 0) corresponding, for instance, to high, middle and low voltages (2E, E, Ground). To detect three different signal voltages, there must be two detection threshold voltages, for instance 0.5E and 1.5E, which are associated with logic levels 0.5 and 1.5, respectively.

A ternary function is ddfined by its truth table. Tables 1 and 2 show truth tables of some functions of one or two variables.

Table 1: Truth table of one-variable functions

| x | x | °x° | <sup>1</sup> x <sup>1</sup> | 2 <sub>X</sub> 2 | <sup>2</sup> χ <sup>2</sup> |

|---|---|-----|-----------------------------|------------------|-----------------------------|

| 0 | 2 | 2   | 0                           | 0                | 2                           |

| 1 | 1 | 0   | 2                           | 0                | 2                           |

| 2 | 0 | 0   | 0                           | 2                | 0                           |

Table 2: Truth table of two-variable functions

| x | y | f(x, y)     | $x \wedge y$ | $x \wedge y$ | $x \vee y$ | $x \vee y$ |

|---|---|-------------|--------------|--------------|------------|------------|

| 0 | 0 | Co          | 0            | 2            | 0          | 2          |

| 0 | 1 | C,          | 0            | 2            | 1          | 1          |

| 0 | 2 | С,          | 0            | 2            | 2          | 0          |

| 1 | 0 | $C_3$       | 0            | 2            | 1          | 1          |

| 1 | 1 | $C_{\perp}$ | 1            | 1            | 1          | 1          |

| 1 | 2 | C           | 1            | 1            | 2          | 0          |

| 2 | 0 | C.          | 0            | 2            | 2          | 0          |

| 2 | 1 | C,          | 1            | 1            | 2          | 0          |

| 2 | 2 | C's         | 2            | 0            | 2          | 0          |

In Table 1,  ${}^{0}x^{0}$ ,  ${}^{1}x^{1}$  and  ${}^{2}x^{2}$  are the binary-valued literals of variable x,  $\overline{x}$  is the inverse of x and  ${}^{0}x^{0}$  and  ${}^{2}\overline{x^{2}}$  are called the negative and positive inverses of x, respectively. In Table 2,  $x \wedge y$  and  $x \wedge \overline{y}$  are the ternary AND operation (minimum) and the ternary NAND operation, and  $x \vee y$  and  $\overline{x \vee y}$  are the ternary OR operation. In Table 2, f(x, y) expresses a general form of a two-variable function, where the function value  $C_{i} \in (0, 1, 2)$ .

In a Post algebra, the literal, the AND and the OR form a complete set of operations, and f(x, y) in Table 2 can be expressed in the following algebraic form:

$$f(x, y) = (C_0 A^0 x^0 A^0 y^0) V(C, A^0 x^0 A^1 y^1)$$

$$V(C_2 \wedge^0 x^0 \wedge^2 y^2) V(C_3 \wedge^1 x^1 \wedge^0 y^0)$$

$$V(C_4 \wedge^1 x^1 \wedge^1 y^1) V(C_5 \wedge^1 x^1 \wedge^2 y^2)$$

$$V(C, A^2 x^2 A^0 y^0) V(C_7 A^2 x^2 A^1 y^1)$$

$$V(C, A^2 x^2 A^2 y^2)$$

(1)

If the values defining 'xi (from Table 1) are changed from (2,0) to (1,0) and the operations A and V are replaced by modulo-3 multiplication  $(\otimes)$  and modulo-3 addition  $(\oplus)$ , eqn. 1 will be transformed into a form based on a modulus algebra. Substituting other operations in eqn. 1 yields similar expansions. As long as these operations reflect the way elements act in circuits, the corresponding functional form can be fabricated into a circuit and therefore is potentially useful.

By factoring common values of  $C_i$  in eqn. 1, f(x, y) can be written in the following form:

$$f(x, y) = (0 \wedge {}^{0}f^{0}) \vee (1 \wedge {}^{1}f^{1}) \vee (2 \wedge {}^{2}f^{2})$$

(2)

In eqn. 2,  ${}^0f^0$ ,  ${}^1f^1$  and  ${}^2f^2$  are functions with binary output (2, 0) that are mutually complementary and exclusive

$${}^{0}f^{0} \vee {}^{1}f^{1} \vee {}^{2}f^{2} = 2$$

$${}^{0}f^{0} \wedge {}^{1}f^{1} = {}^{0}f^{0} \wedge {}^{2}f^{2} = {}^{1}f^{1} \wedge {}^{2}f^{2} = 0$$

(3)

A detailed discussion of this algebra system can be found in many references [1].

#### 3 CMOS ternary circuits with resistors

At least two elements with different detection thresholds, for instance 1.5 and 0.5, are needed to recognise three logic levels (2, 1, 0) of an input signal. The pair of complementary enhancement-mode MOS transistors in traditional CMOS binary circuits can handle this requirement. If the detection thresholds of the PMOS and NMOS transistors are placed at 1.5 and 0.5, respectively, both transistors will turn on for an input 1. If these detection thresholds are interchanged, both transistors will turn off for an input 1 [3].

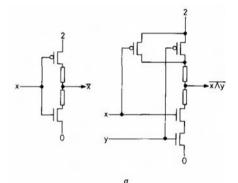

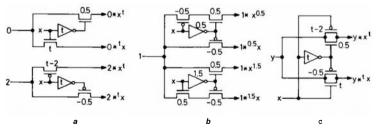

Suppose that the threshold voltage  $V_{TP}$  of a PMOS transistor is  $-0.5\mathrm{E}$  or  $-1.5\mathrm{E}$ . We may represent the threshold voltage as -0.5 or -1.5. Which we may call the threshold of the PMOS transistor. The threshold voltage  $V_{TN}$  of an NMOS transistor may be  $0.5\mathrm{E}$  or  $1.5\mathrm{E}$ , represented by threshold 0.5 or 1.5. As shown in Fig. 1, two kinds of ternary CMOS inverter and NAND gate may be designed [2, 4]. In Fig. 1a, all the PMOS and NMOS transistors have thresholds of -0.5 and 0.5, respectively, so that they can respond to an input signal with detection thresholds 1.5 and 0.5. In Fig. 1b, the PMOS and NMOS transistors have thresholds of -1.5 and 1.5, permitting them to respond to an input signal with detection thresholds 0.5 and 0.5. These circuits are

Fig. 1 CMOS ternary circuits with resistors a  $T_p = -0.5$

$T_N = 0.5$ b  $T_p = -1.5$  $T_n = 1.5$

similar to the traditional CMOS binary inverter and NAND gate. They are ingenious and attractive

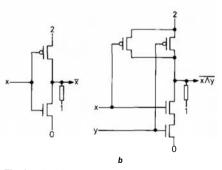

In ternary algebra, the literal and the NAND operation form a complete set. This follows because the AND/OR form of a ternary equation such as eqn. 1 can be expressed in NAND/NAND form by the use of **DeMorgan's** Law:  $\overline{\mathbf{x} \ \mathbf{v} \ \mathbf{y}} = \overline{x} \ \mathbf{A} \ \overline{y}$ . Consider a circuit realising a simple two-variable function defined by the ternary K-map shown in Fig. 2a. We may express the simplified

$$f(x, y) = (2 \wedge \overline{y^2}) \vee (1 \wedge \overline{x^0} \wedge \overline{y^2}) \vee (0 \wedge \overline{x^0} \wedge \overline{y^2})$$

This equation has an AND/OR form, but variables x and y appear only as literals. This means that the input variables may be decoded first into binary literals, and then these binary signals may be processed using ternary gates. We had an idea to use binary circuits, about which we know a great deal, to process these binary signals to get f' in eqn. 2, and then use the newer and relatively untested ternary circuits to synthesise the ternary output.

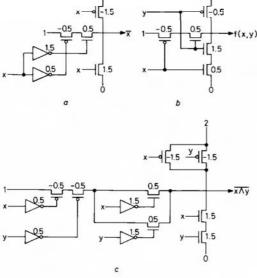

Birk and Farmer [5] proposed such a procedure: form  $(2A^2f^2)$  and  $(IA^1f^1)$  by weighting the power source of the last gates that realise  $^2f^2$  and  $^1f^1$ , and then obtain the ternary output by using a ternary OR gate. The circuit realisation of function f in Fig. 2a is shown in Fig. 2b. Etiemble and Israel [6] proposed a general circuit construction method, illustrated in Fig. 2c. In this construction, a decoder transforms each ternary input into two binary signals that are then processed by a pure binary circuit, and a final encoder transforms the output of the binary circuit into the desired ternary output. For such realisation, we only need a few ternary decoders and encoders. Decoders that correspond to the two choices of threshold in Fig. 1 are shown in Figs. 2d and e, where the decimal numbers by the MOS transistors represent their thresholds. Figs. 2f and g show two forms of encoder.

The CMOS ternary circuits in Figs. 1 and 2 contain passive devices (resistors), which take up too much chip area and increase the power dissipation, output impedance and delay of the circuit. Furthermore, resistors are difficult to fabricate in a CMOS VLSI circuit, and ternary circuits containing resistors will probably poorly when compared with their binary equivalent.

# CMOS ternary encoder and decoder

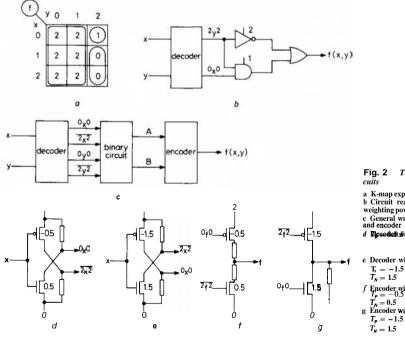

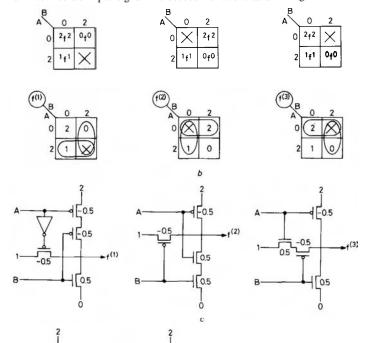

We can use a pair of binary signals, A and B, to convey ternary information to the inputs of a ternary encoder. From A and B we can construct  ${}^0\!f^0$ ,  ${}^1\!f^1$  and  ${}^2\!f^2$  in three ways, as shown in the K-maps in Fig. 3a. In each of these three encoding schemes the 'don't care' term x is placed three encoding schemes the doint care term A is practically diagonal to a different  ${}^{i}f^{i}$ , and we have the three sets of relationships  $A = {}^{1}f^{1}$ ,  $B = 0 f^{0}$ ;  $A = {}^{2}f^{2}$ ,  $B = {}^{1}f^{1}$ ;  $A = {}^{2}f^{2}$ ,  $B = {}^{0}f^{0}$ . The required outputs may also be expressed with K-maps, as shown in Fig. 3b. The encoders in Figs. 2f and g conform to the third encoding scheme. However, the existence of resistors in these encoders will increase the output impedance and delay, and will decrease the load-driving capability of the

To eliminate the resistors and obtain better performance characteristics for these ternary circuits, three power sources (2, 1, 0) are needed instead of only two (2, 1, 0)0). This leads to a consideration of multiple-powered circuits [7, 8]. McCluskey proposed all three forms of the ternary encoder, without resistors, by using an additional intermediate power source [9]. Fig. 3c shows these cir-

Now let us eliminate resistors in the ternary decoders. Mouftah and Garba pointed out that altering the lengthto-width ratio of the PMOS and NMOS channels can change the resistance of the channels [10]. Their circuits are shown in Fig. 4a. When an intermediate input signal is presented, the asymmetric resistances of the two MOS transistors will make the output either high or low, depending on the choice of circuit. This form of decoder

Traditional construction of ternary cir-

- a K-map expression of a two-variable ternary function b Circuit realisation by decoding input signals and weighting power sources

- c General wnstruction of ternary circuits with decoder and encoder

- d DecodeD with resistors

Decoder with resistors

Encoder with resistors  $T_{\rm e} = -0.5$

Encoder with resistors

IEE PROCEEDINGS, Vol. 137, Pt. G, No. I, FEBRUARY 1990

merges the resistors into the transistor channels. Under an intermediate input signal this decoder functions as a voltage divider rather than relying on the natural switching states of the transistors.

L/W=25/9

L/W=5/5

Fig. 3 CMOS ternary encoders a Three encoding schemes b K-maps of required output c Circuit realisations of a w d e r

Huertas and Carmona proposed a decoder without resistors, as shown in Fig. 4b, in which two-pad MOS transistors are used to shift their detection thresholds up or down [8]. Taking the left circuit in Fig. 4b as an example, the input signal x must be twice the threshold of the NMOS transistor in order for these two NMOS transistors to turn on. Therefore, if these two NMOS transistors are considered to be one input element, then the threshold of this element is raised. This decoder circuit has problems: in addition to the increase in the number of active elements in the circuit, the low-level output voltage is raised, placing it near the NMOS threshold. Nevertheless, changing the threshold of a transistor is a good idea because it does provide a way for the circuit to recognise the three different input levels.

Fabricators may change the threshold voltage of a MOS transistor by implanting ions of a dopant atom into the substrate of the transistor channel. For example, for n-channel devices, p-type ions (boron) raise the threshold and n-type ions (phosphorus) lower the threshold [11]. Table 3 shows how four kinds of NMOS transistor with different thresholds can be fabricated by combining high-dose and low-dose boron implants into an n-channel. These four transistors can be used as multiple state cells in the storage matrix of a ROM, in which case a four-state ROM is formed [12].

For ternary circuits we can use multiple ion implantation techniques to make NMOS transistors with thresh-

Fig. 4 CMOS ternary decoders

L/W=25/5

a

- a Decoder with MOS transistors altering length-to-width ratio b Decoder with pad MOS transistors c Decoder with multithreshold MOS transistors

Table 3: NMOS transistors with different thresholds

| High dose | Low dose | Threshold voltage |  |  |

|-----------|----------|-------------------|--|--|

| No        | No       | 0.7 V             |  |  |

| No        | Yes      | 2.2 V             |  |  |

| Yes       | No       | 3.2 V             |  |  |

| Yes       | Yes      | 4.1 V             |  |  |

olds 1.5 and 0.5, and to make PMOS transistors with thresholds -1.5 and -0.5. Then a new decoder is possible, as shown in Fig. 4c. This decoder has ideal operational characteristics, at the expense of additional masks and implantation steps during fabrication.

Ternary encoders and decoders designed according to the above techniques meet the requirements for useful ternary circuits, at the expense of additional power sources and additional fabrication steps. However, the sandwich-like structure of the ternary circuits of Fig. 2c is not satisfying, since we have only surrounded the original binary circuit by new ternary crusts. Moreover, the centre binary circuit is inefficient, since its two outputs are wholly devoted to representing one ternary signal. Furthermore, the ternary crusts surrounding the binary circuit increase the number of stages in the circuit and increase the circuit's transmission delay. Such a circuit is unlikely to be viewed as superior to a pure binary circuit that **realises** the same function.

These undesirable properties are a result of the sandwich-like construction of the ternary circuits, but the sandwich mode seems inherent in the fabrication of the reported multivalued circuits [13] and it is difficult to avoid its effects even in the design of storage devices [14]. If we trace the cause of the sandwich-like implementations, we find that the functional form of eqn. I is responsible. In this form the ternary function has been expressed in terms of literals with binary outputs, which then are used in subsequent steps in the processing. The sandwich form of the resulting circuits cannot be changed as long as eqn. I forms the basis of expressing functions defined by truth tables.

# 5 Transmission functions and CMOS transmission networks

As an alternative to eqn. 1, the function f(x, y) of Table 2 may be expressed as follows, by making use of the transmission-threshold properties of MOS switching transistors [15]:

$$\begin{split} f(x,y) &= C_0 \stackrel{\star}{=} (x^{0.5} \,\blacksquare\,\, y^{0.5}) \,\#\,\, C_1 \stackrel{\star}{=} (x^{0.5} \,\blacksquare\,\, 0.5 \,y \bullet y^{1.5}) \\ &\#\,\, C_2 \stackrel{\star}{=} (x^{0.5} \,\blacksquare\,\, 1.5 \,y) \,\#\,\, C_3 \stackrel{\star}{=} (^{0.5} x \bullet x^{1.5} \,\blacksquare\,\, y^{0.5}) \\ &\#\,\, C_4 \stackrel{\star}{=} (^{0.5} x \bullet x^{1.5} \,\blacksquare\,\, 0.5 \,y \bullet y^{1.5}) \\ &\#\,\, C_5 \stackrel{\star}{=} (^{0.5} x \bullet x^{1.5} \,\blacksquare\,\, 1.5 \,y) \\ &\#\,\, C_6 \stackrel{\star}{=} (^{1.5} x \bullet y^{0.5}) \,\#\,\, C_7 \stackrel{\star}{=} (^{1.5} x \bullet ^{0.5} y \bullet y^{1.5}) \\ &\#\,\, C_8 \stackrel{\star}{=} (^{1.5} x \bullet ^{1.5} y) \end{split}$$

Three new types of operations appear in eqn. 4. These are defined below.

5.1 Threshold-comparison operations  $x^{t} \triangleq \begin{cases} T & \text{if } x < t \\ F & \text{if } x > t \end{cases} \text{ and } {}^{t}x \triangleq \begin{cases} T & \text{if } x > t \\ F & \text{if } x < t \end{cases}$

In these definitions, the input variable  $x \in (0, 1, 2)$  and the detection threshold  $t \in (0.5, 1.5)$ . The result  $x^t$  or 'x is a Boolean switching value T or F rather than a ternary signal value 2 or 0 as arose in  $x^t$  in eqn. 1. The AND operator • and the OR operator + (which does not appear in eqn. 4) are the conventional Boolean algebraic operators. They represent switches connected in series and in parallel, respectively.

# 5.2 Transmission operation

$$C_i * B \triangleq \begin{cases} C_i & \text{if } B = T \\ \emptyset & \text{if } B = F \end{cases}$$

Here  $C_i \in (0, 1, 2)$  is called the transmission source. When the switching variable B is true, the source  $C_i$  will be transmitted to the output. When B is false, the output is empty  $(\emptyset)$ .

# 5.3 Union operation

$$C_i * B_i \# C_j * B_j \triangleq \begin{cases} C_i * B_j & \text{if } B_j = F \\ C_j * B_j & \text{if } B_i = F \end{cases}$$

If  $C_i \neq C_j$  and  $B_i = B_j = T$ , then a voltage conflict arises between sources  $C_i$  and  $C_j$ ; this condition is disallowed.

In MOS circuits, the threshold-comparison operation and the transmission operation describe physical actions of MOS transistors. The union operation represents the wiring together of the outputs of corresponding transmission branches in CMOS circuits.

Since  $C_i \in (0, 1, 2)$ , eqn. 4 can be factored into the form

$$f(x, y) = 0 * B_0 # 1 * B_1 # 2 * B_2$$

(5)

where the three switching functions  $B_i$  are mutually complementary and exclusive, as in eqn. 2

$$B_0 + B_1 + B_2 = T$$

$B_0 \bullet B_1 = B_0 \bullet B_2 = B_1 \bullet B_2 = F$  (6)

With these definitions, let us consider how to use MOS transistors to realise the transmission functions C \* x' and  $C * {}^t x$ , where C,  $x \in (0, 1, 2)$  and  $t \in (0.5, 1.5)$ . NMOS transistors conduct where the difference between the gate voltage  $V_G$  and the source voltage  $V_S$  is greater than the threshold voltage  $V_{T_N}: (V_G - V_S) - V_{T_N} > 0$ . PMOS transistors conduct when the difference between the gate and source voltages is less than the threshold voltage  $V_{T_P}: (V_G - V_S) - V_{T_P} < 0$ . Accordingly, Fig. 5 shows circuit realisations of various transmission functions. In Fig. 5a the inverter symbols labeled t represent the threshold t inverter, which detects a ternary input x with

Fig. 5 CMOS circuit realisations of transmission functions

a Transmission functions with sources 0 and 2 b Transmission functions with source 1

c Transmission functions with variable source

detection threshold t and produces a binary output  $\overline{x(t)}$ . Of particular interest are the cases for thresholds 0.5 and 1.5:  $\overline{x(0.5)} = {}^0x^0$  and  $\overline{x(1.5)} = {}^2x^2$ . Fig. 5b shows two schemes to realise transmission functions  $1*x^{0.5}$  and 1\*1.5x. Fig. 5c shows how to propagate a variable source  $y \in (0, 1, 2)$  using complementary MOS transmission

Using the transmission-function algebra, we can express several functions introduced earlier in this paper;  $\bar{x}$ ,  ${}^0x^0$ , and  ${}^{2}x^2$  from Table 1, the three encoder functions f from Fig. 3b, function f defined in Fig. 2a and  $\bar{x}\wedge\bar{y}$  from Table 2

In the expressions for  $f^{(t)}$ , the detection thresholds may be selected arbitrarily as 1.5 or 0.5, since A and B are binary signals with values (2, 0).

Using the circuits in Fig. 5 to realise the transmission functions, we can establish that the circuits for  $\overline{x(t)}$  and  $f^{(t)}$  are the same as in Figs. 4c and 3c, respectively. Fig. 6 shows circuits that realise  $\overline{x}$ , f and  $\overline{x} \wedge \overline{y}$ . Fig. 6b is a fully ternary circuit, containing no binary signals since the threshold-comparison operation represents a binary switching state rather than a binary signal transfer. Examples of the design of other basic CMOS ternary circuits.

Fig. 6 CMOS circuit realisations

b f(x, y) in Fig. 2a c  $x \wedge y$  cuits and storage devices can be found in Reference 16; further work is in progress.

Transmission-function theory can also explain CMOS ternary circuits that contain resistors. In eqn. 5, one of the three transmission functions Bi may be realised by a resistor R, giving a circuit with two low-impedance paths and one high-impedance path. Since the three transmission functions are mutually complementary and exclusive, the MOS transmission network will work in the following way: when one of the two nonresistive sources is transmitted to the output (with a low impedance), the source passing through the high-impedance R has no effect on the output, but when neither low-impedance source is transmitted, the source passing through R will be transmitted to the output.

If a resistor R takes the place of the more complicated branch to which source 1 is attached in Figs. **6a** and **c**, these circuits will be the same as that in Fig. **1b**. Similarly, we can derive Fig. **2g** from the third circuit in Fig. **3c**. These three transmission functions can be rewritten as follows:

$$\overline{x} = 2 * x^{0.5} \# 0 * {}^{1.5}x \# 1_R$$

$$\overline{x \wedge y} = 2 * (x^{0.5} + y^{0.5}) \# 0 * ({}^{1.5}x \bullet {}^{1.5}y) \# 1_R$$

$$f^{(3)} = 2 * A^t \# 0 * {}^tB \# 1_R \quad t \in \{0.5, 1.5\}$$

The technique of replacing a branch of a circuit with a resistor can also be applied to a two-source MOS transmission network. If R substitutes for an NMOS transistor, a PMOS circuit family is formed, and if R substitutes for a PMOS transistor, an NMOS circuit family is formed. For example, the circuits in Figs. 2d and e can be derived from the circuits in Figs. 4c.

In the above discussion, if the circuits are not in a state that is transmitting source 2 or source 0, then the circuits are transmitting source 1. There is another approach which eliminates voltage source 1: to create an output at the medial voltage of source 1, we may simultaneously transmit both source 2 and source 0 instead of source 1 to the output through two balanced voltage-division resistors. Again using the functions x,  $\overline{x \wedge y}$  and  $f^{(3)}$  as examples, we may write transmission-function expressions that do not require source 1

$$\overline{x} = 2_R * x^{1.5} # 0_R * {}^{0.5}x$$

$$\overline{x \wedge y} = 2_R * (x^{1.5} + y^{1.5}) # 0_R * ({}^{0.5}x \bullet {}^{0.5}y)$$

$$f^{(3)} = 2_R * B^t # 0_R * {}^t A \quad t \in \{0.5, 1.5\}$$

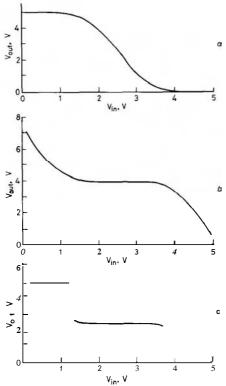

The circuits corresponding to these expressions are the same ones shown in Figs. In and 2f. The preceding discussion shows that the proposed transmission-function theory can explain previous CMOS ternary circuits that contain resistors. Although the circuits with resistors look simpler, their electrical parameters and characteristics are not desirable. SPICE2G5 has been used to simulate CMOS ternary circuits. Taking 5 V and 2.5 V as the high- and middle-voltage sources in the ternary circuits, a part of model parameters of NMOS and PMOS transistors used in SPICE simulations are listed in Table 4, where  $T_N$  and  $T_P$  represent thresholds of NMOS and PMOS transistors, respectively [15].

DC transfer characteristics of two kinds of ternary inverter with resistors and the inverter in Fig. 6a are shown in Fig. 7. Obviously, Fig. 7a and b are not desirable because of the existence of resistors. In Fig. 7c, the voltages corresponding to detection thresholds 0.5 and 1.5 are 1.25 V and 3.75 V, respectively. In comparison

Table 4: SPICE2G5 parameters

|     | N                | MOS                        |                 |                | PMOS             |                                |          |  |  |

|-----|------------------|----------------------------|-----------------|----------------|------------------|--------------------------------|----------|--|--|

| T   | <b>VTO,</b><br>У | μ <sub>01</sub><br>cm²/V/s | <i>W,</i><br>µm | T <sub>p</sub> | <b>VТО,</b><br>V | $\mu_0$ , cm <sup>2</sup> /V/s | W,<br>µm |  |  |

| 0.5 | 0.8              | 560                        | 25              | -0.5           | -3.3             |                                | 55       |  |  |

| 1.5 | 3.3              | 330                        | 35              | -1.5           | -0.8             | 130                            | 85       |  |  |

Channel length  $L = 10 \, \mu m$ Oxide thickness  $TOX = 0.07 \mu m$

Fig. 7 DC transfer characteristics of the ternary inverters

- Temperature =  $27^{\circ}$ C

- a Inverter in Fig. 1o b Inverter in Fig. 1b With two resistors With one resistor

- c Inverter in Fig. 6a

with the conventional binary inverter, the DC transfer curve has two different outputs and shows only a single detection threshold. It means that ternary gates have greater capability for processing signals than binary ones.

### Conclusions

Based on briefly reviewing the research progress of CMOS ternary circuits, the transmission-function theory is introduced in this paper. After proposing three operations (threshold-comparison operation, transmission operation and union operation), the expression of transmission function and the corresponding CMOS circuit realisation are discussed. The result of the thresholdcomparison operation is Boolean switching value T or F rather than the highest and lowest ternary signal value 2 or 0, as in other references that conform to the switching function of MOS transistors, and it avoids a sandwichlike structure of the ternary circuits. This paper shows that the new circuit design can explain the main CMOS ternary circuits proposed previously. We think that the transmission-function theory proposed in this paper, used in an environment with multiple power sources and multiple threshold, provides another step toward making practical CMOS multivalued circuits. The major advantage of using multiple ion implant technique is that the size of a ternary MOS transistor is same as a binary one F121. Therefore, the silicon areas necessary for ternary MOS devices are not larger than conventional binary ones using the same fabrication geometries. This means that a reduction in silicon area is possible for ternary circuits when processing given information.

The procedure for designing CMOS ternary combinational circuits can be used to construct CMOS ternary sequential circuit [16]. Besides, the discussion in this paper can be extended to a higher radix, and can be used to design the traditional CMOS binary circuits as well.

#### 7 Acknowledgment

This work is part of a project supported by NSFC.

#### References

- 1 HURST, S.L.: 'Multiple-valued logic Its status and its future',

- 1 HURST, S.L.: Multiple-valued logic Its status and its future', IEEE Trans., 1984, C-33, (10), pp. 1160-1179

2 MOUFTAH, H.T., and JORDAN, I.B.: 'Integrated circuits for ternary logic'. IEEE Proceedings of ISMVL, 1974, pp. 285-302

3 WU, X.W., and PROSSER, F.P. 'Binary-ternary mixed-valued counter'. IEEE Proceedings of ISMVL, 1987, pp. 53-60

4 MOUFTAH, H.T., and SMITH, K.C.: 'Injected voltage low-power CMOS. for three valued logic IEEE Proc. (102) 420, (40) exp.

- CMOS for three-valued logic', IEE Proc. G, 1982, 129, (6), pp.

- 5 BIRK, J.E., and FARMER, D.E.: 'An algebraic method for designing multivalued logic circuits using principally binary components', IEEE Trans., 1975, **C-24**, (11), pp. 1101–1104

6 ETIEMBLE, D., and ISRAEL, M.: 'Implementation of ternary cir-

- cuits with binary integrated circuits', IEEE Trans., 1977, C-26, (12), pp. 1222–1232

- 7 KOANATAKOOL, H.T.: 'Implementation of ternary indentity cell using CMOS integrated circuits', Electron. Lett., 1978, 14, (15), pp. 462-464

- 8 HUERTAS, J.L., and CARMONA, J.M.: 'Low-power ternary

- 8 HUERTAS, J.L., and CARMONA, J.M.: 'Low-power ternary CMOS circuits'. IEEE Proceedings of ISMVL, 1979, pp. 170-174

9 McCLUSKEY, E.J.: 'A discussion of multiple-valued loxic circuits'. IEEE Proceedings of ISMVL, 1982, pp. 200-205

10 MOUFTAH, H.T., and GARBA, A.L.: 'VLSI implementation of a five-trit full adder', IEE Proc. G, 1984, 131, (5), pp. 214-220

11 HODGES, D., and JACKSON, H.: 'Analysis and design of digital integrated climitics' (MCGent Pill) New York, 1982, 1982.

- integrated circuits' (McGraw-Hill, New York, 1983)

12 RICH, D.A.: 'A survey of multivalued memories', IEEE Trans.,

- 12 RICH, D.A.: A survey of multivalued memories, IEEE Trans., 1986, C-35, (2), pp. 99–106

13 ETIEMBLE, D.: Multivalued MOS integrated circuits and VLSI implementation', Bull. MVL Tech. Comm., 1986.7, (3), pp. 17–18

14 WU, X.W., and CHEN, X.X.: Ternary flip-flops with triple-rail

- output and their application in ternary sequential circuits', Sci. Sin. A (China), 1985.28, (11), pp. 1208–1221

- 15 ZUKERAN, C., AFUSO, C., KAMEYAMA, M., and HIGUCHI, T.: 'Design of new low-power quaternary CMOS logic circuits based on multiple ion implants'. IEEE Proceedings of ISMVL, 1985,

- pp. 84–90

16 WU, XW., and PROSSER, F.P.: 'CMOS ternary sequential circuits'. IEEE Proceedings of ISMVL, 1988, pp. 307–313