# Extending C++ for Explicit Data-Parallel Programming via SIMD Vector Types

Dissertation

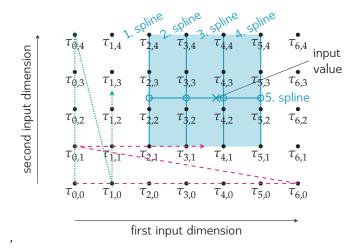

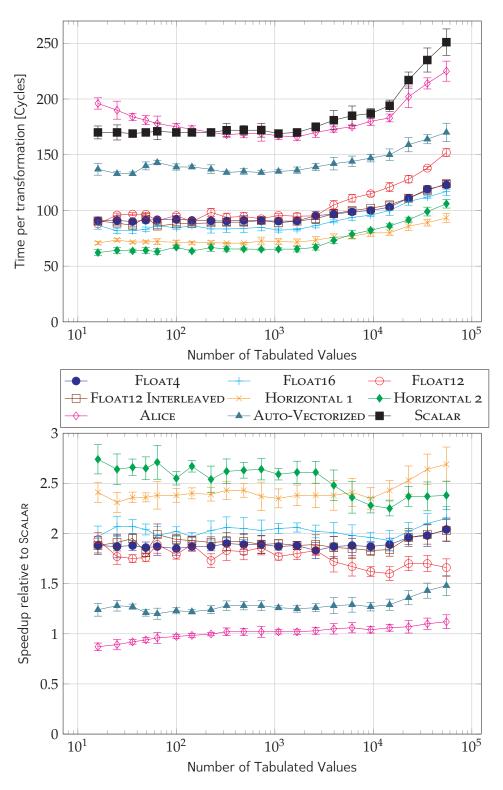

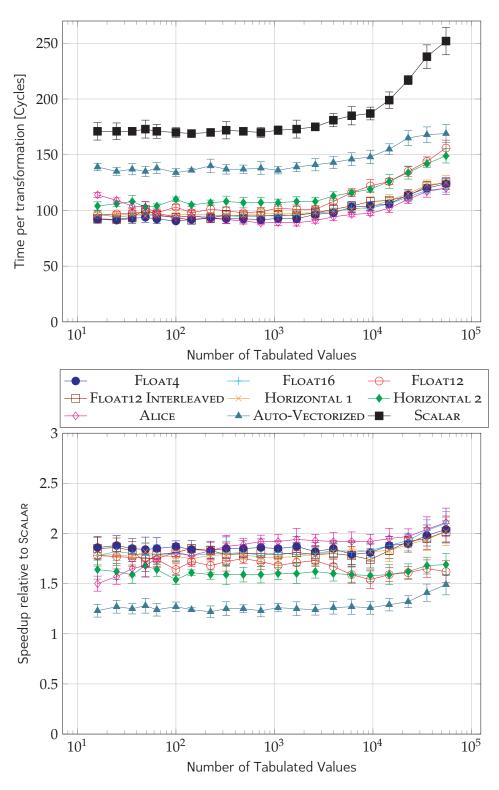

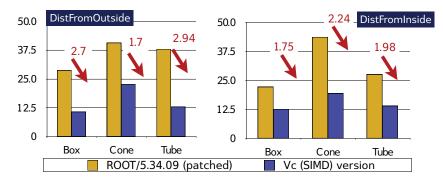

zur Erlangung des Doktorgrades

der Naturwissenschaften

vorgelegt beim Fachbereich 12 der Johann Wolfgang Goethe-Universität in Frankfurt am Main

von

Matthias Kretz aus Dieburg

Frankfurt (2015) (D 30)

| vom Fachbereich 12 der                                          |                                                                                   |  |  |  |  |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------|--|--|--|--|

| Johann Wolfgang Goethe-Universität als Dissertation angenommen. |                                                                                   |  |  |  |  |

|                                                                 |                                                                                   |  |  |  |  |

| Dekan:                                                          | Prof. Dr. Uwe Brinkschulte                                                        |  |  |  |  |

| Gutachter:                                                      | Prof. Dr. Volker Lindenstruth Prof. Dr. Ulrich Meyer Prof. DrIng. André Brinkmann |  |  |  |  |

|                                                                 | Tron Dr. mg. Andre Dillikmann                                                     |  |  |  |  |

Datum der Disputation: 16. Oktober 2015

# **CONTENTS**

| ΑE | STRA | CT                                          | vii      |

|----|------|---------------------------------------------|----------|

| PU | BLIC | ATIONS                                      | ix       |

| AC | KNO  | WLEDGMENTS                                  | xi       |

| ΙI | NTRC | DDUCTION                                    |          |

| 1  | SIMI |                                             | 3        |

|    | 1.1  | The SIMD Idea                               | 3        |

|    | 1.2  | SIMD Computers                              | 5        |

|    | 1.3  | SIMD Operations                             | 6        |

|    | 1.4  | Current SIMD Instruction Sets               | 8        |

|    | 1.5  | The future of SIMD                          | 10       |

|    | 1.6  | Interaction With Other Forms of Parallelism | 11       |

|    | 1.7  | Common Optimization Challenges              | 12       |

|    | 1.8  | Conclusion                                  | 14       |

| 2  | LOO  | P-VECTORIZATION                             | 15       |

|    | 2.1  | Definitions                                 | 15       |

|    | 2.2  | Auto-Vectorization                          | 18       |

|    | 2.3  | Explicit Loop-Vectorization                 | 21       |

| 3  |      | RODUCTION TO SIMD TYPES                     | 23       |

| J  | 3.1  | The SIMD Vector Type Idea                   | -3<br>23 |

|    | 3.2  | SIMD Intrinsics                             | -5<br>24 |

|    | 3.3  | Benefits of a SIMD Vector Type              | 25       |

|    | 3·4  | Previous Work on SIMD Types                 | 26       |

|    | 3.5  | Other Work on SIMD Types                    | 27       |

| тт |      | •                                           | •        |

| 11 |      | A C++ Library for Explicit Vectorization    |          |

| 4  |      | ATA-PARALLEL TYPE                           | 31       |

|    | 4.1  | The Vector <t> Class Template</t>           | 32       |

|    | 4.2  | SIMD Vector Initialization                  | 35       |

|    | 4.3  | Loads and Stores                            | 40       |

|    | 4.4  | Unary Operators                             | 44       |

|    | 4.5  | Binary Operators                            | 45       |

|    | 4.6  | Compound Assignment Operators               | 50       |

|    | 4.7  | Subscript Operators                         | 51       |

|    | 4.8  | Gather & Scatter                            | 52       |

|    | 4.9  | Selecting the Default SIMD Vector Type     |

|----|------|--------------------------------------------|

|    | 4.10 | Interface to Internal Data                 |

|    | 4.11 | Conclusion                                 |

| 5  | DAT  | A-PARALLEL CONDITIONALS 73                 |

|    | 5.1  | Conditionals in SIMD Context               |

|    | 5.2  | The Mask <t> Class Template</t>            |

|    | 5.3  | Write-Masking                              |

|    | 5.4  | Masked Gather & Scatter                    |

|    | 5.5  | Conclusion                                 |

| 6  | VECT | OR CLASS DESIGN ALTERNATIVES 89            |

|    | 6.1  | Discussion                                 |

|    | 6.2  | Conclusion                                 |

| 7  | SIME | OARRAY: VALARRAY AS IT SHOULD HAVE BEEN 93 |

|    | 7.1  | std::valarray <t></t>                      |

|    | 7.2  | Vc::SimdArray <t, n=""></t,>               |

|    | 7.3  | Uses for SimdArray                         |

|    | 7.4  | Implementation Considerations              |

|    | 7.5  | Mask Types                                 |

|    | 7.6  | Conclusion                                 |

| 8  | ABI  | CONSIDERATIONS 99                          |

|    | 8.1  | ABI Introduction                           |

|    | 8.2  | ABI Relevant Decisions in Vc               |

|    | 8.3  | Problem                                    |

|    | 8.4  | Solution Space                             |

|    | 8.5  | Future Research & Development              |

| 9  | LOA  | D/STORE ABSTRACTIONS 109                   |

|    | 9.1  | Vectorized STL Algorithms 109              |

|    | 9.2  | Vectorizing Container                      |

|    | 9.3  | Conclusion                                 |

| 10 | AUT  | OMATIC TYPE VECTORIZATION 113              |

|    |      | Template Argument Transformation           |

|    |      | Adapter Type                               |

|    |      | Scalar Insertion and Extraction            |

|    | 10.4 | Complete Specification                     |

|    |      | Current Limitations                        |

|    | 10.6 | Conclusion                                 |

| Ш  | VECT | TORIZATION OF APPLICATIONS                 |

|    |      | REST NEIGHBOR SEARCHING 129                |

| 11 |      | ,                                          |

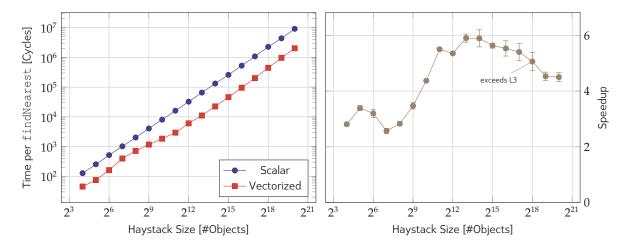

|    | 11.1 | Vectorizing Searching                      |

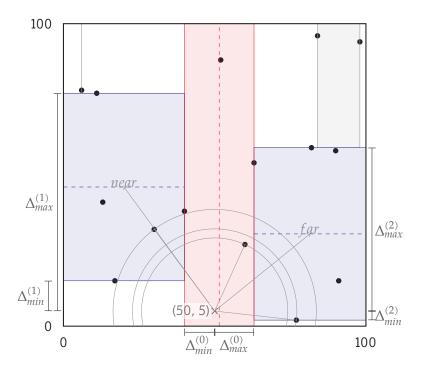

|     | 11.2 Vectorizing Nearest Neighbor Search       | 134 |

|-----|------------------------------------------------|-----|

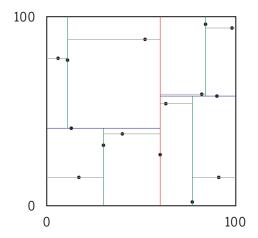

|     | 11.3 k-d Tree                                  | 139 |

|     | 11.4 Conclusion                                | 152 |

| 12  | VC IN HIGH ENERGY PHYSICS                      | 155 |

|     | 12.1 ALICE                                     | 155 |

|     | 12.2 Kalman-filter                             | 166 |

|     | 12.3 Geant-V                                   | -   |

|     | 12.4 ROOT                                      | 170 |

|     | 12.5 Conclusion                                | 171 |

| IV  | Conclusion                                     |     |

| 13  | CONCLUSION                                     | 175 |

| V.  | Appendix                                       |     |

| A   | WORKING-SET BENCHMARK                          | 179 |

| В   | LINEAR SEARCH BENCHMARK                        | 183 |

| C   | NEAREST NEIGHBOR BENCHMARK                     | 187 |

| D   | BENCHMARKING                                   | 193 |

| E   | C++ implementations of the k-d tree algorithms | 195 |

|     | E.1 INSERT Algorithm                           | 195 |

|     | E.2 FINDNEAREST Algorithm                      | 197 |

| F   | ALICE SPLINE SOURCES                           | 203 |

|     | F.1 Spline Implementations                     | 203 |

|     | F.2 Benchmark Implementation                   | 209 |

| G   | THE SUBSCRIPT OPERATOR TYPE TRAIT              | 213 |

| Н   | THE ADAPTSUBSCRIPTOPERATOR CLASS               | 215 |

| I   | SUPPORTING CUSTOM DIAGNOSTICS AND SFINAE       | 217 |

|     | I.1 Problem                                    | 217 |

|     | I.2 Possible Solutions                         | 219 |

|     | I.3 Evaluation                                 | 220 |

| AC  | CRONYMS                                        | 221 |

| BIE | BLIOGRAPHY                                     | 223 |

| INI | DEX                                            | 231 |

| GE  | ERMAN SUMMARY                                  | 235 |

## **ABSTRACT**

Data-parallel programming is more important than ever since serial performance is stagnating. All mainstream computing architectures have been and are still enhancing their support for general purpose computing with explicitly data-parallel execution. For CPUs, data-parallel execution is implemented via SIMD instructions and registers. GPU hardware works very similar allowing very efficient parallel processing of wide data streams with a common instruction stream.

These advances in parallel hardware have not been accompanied by the necessary advances in established programming languages. Developers have thus not been enabled to explicitly state the data-parallelism inherent in their algorithms. Some approaches of GPU and CPU vendors have introduced new programming languages, language extensions, or dialects enabling explicit data-parallel programming. However, it is arguable whether the programming models introduced by these approaches deliver the best solution. In addition, some of these approaches have shortcomings from a hardware-specific focus of the language design. There are several programming problems for which the aforementioned language approaches are not expressive and flexible enough.

This thesis presents a solution tailored to the C++ programming language. The concepts and interfaces are presented specifically for C++ but as abstract as possible facilitating adoption by other programming languages as well. The approach builds upon the observation that C++ is very expressive in terms of types. Types communicate intention and semantics to developers as well as compilers. It allows developers to clearly state their intentions and allows compilers to optimize via explicitly defined semantics of the type system.

Since data-parallelism affects data structures and algorithms, it is not sufficient to enhance the language's expressivity in only one area. The definition of types whose operators express data-parallel execution automatically enhances the possibilities for building data structures. This thesis therefore defines low-level, but fully portable, arithmetic and mask types required to build a flexible and portable abstraction for data-parallel programming. On top of these, it presents higher-level abstractions such as fixed-width vectors and masks, abstractions for interfacing with containers of scalar types, and an approach for automated vectorization of structured types.

The Vc library is an implementation of these types. I developed the Vc library for researching data-parallel types and as a solution for explicitly data-parallel programming. This thesis discusses a few example applications using the Vc library showing the real-world relevance of the library. The Vc types enable parallelization of search algorithms and data structures in a way unique to this solution. It shows the importance of using the type system for expressing data-parallelism. Vc has also become an important building block in the high energy physics community. Their reliance on Vc shows that the library and its interfaces were developed to production quality.

## **PUBLICATIONS**

The initial ideas for this work were developed in my *Diplom* thesis in 2009:

[55] Matthias Kretz. "Efficient Use of Multi- and Many-Core Systems with Vectorization and Multithreading." Diplomarbeit. University of Heidelberg, Dec. 2009

The Vc library idea has previously been published:

[59] Matthias Kretz et al. "Vc: A C++ library for explicit vectorization." In: *Software: Practice and Experience* (2011). ISSN: 1097-024X. DOI: 10.1002/spe. 1149

An excerpt of Section 12.2 has previously been published in the pre-Chicago mailing of the C++ standards committee:

[58] Matthias Kretz. SIMD Vector Types. ISO/IEC C++ Standards Committee Paper. N3759. 2013. url: http://www.open-std.org/jtc1/sc22/wg21/docs/papers/2013/n3759.html

Chapters 4 & 5 and Appendix I have previously been published in the pre-Urbana mailing of the C++ standards committee:

- [57] Matthias Kretz. SIMD Types: The Vector Type & Operations. ISO/IEC C++ Standards Committee Paper. N4184. 2014. url: http://www.open-std.org/jtc1/sc22/wg21/docs/papers/2014/n4184.pdf

- [56] Matthias Kretz. SIMD Types: The Mask Type & Write-Masking. ISO/IEC C++ Standards Committee Paper. N4185. 2014. url: http://www.open-std.org/jtc1/sc22/wg21/docs/papers/2014/n4185.pdf

- [60] Matthias Kretz et al. Supporting Custom Diagnostics and SFINAE. ISO/IEC C++ Standards Committee Paper. N4186. 2014. url: http://www.open-std.org/jtc1/sc22/wg21/docs/papers/2014/n4186.pdf

# ACKNOWLEDGMENTS

For Appendix I, I received a lot of useful feedback from Jens Maurer, which prompted me to rewrite the initial draft completely. Jens suggested to focus on deleted functions and contributed Section I.3.

# Part I Introduction

## **SIMD**

Computer science research is different from these more traditional disciplines. Philosophically it differs from the physical sciences because it seeks not to discover, explain, or exploit the natural world, but instead to study the properties of machines of human creation.

— Dennis M. Ritchie (1984)

This thesis discusses a programming language extension for portable expression of data-parallelism, which has evolved from the need to program modern SIMD<sup>1</sup> hardware. Therefore, this first chapter covers the details of what SIMD is, where it originated, what it can do, and some important details of current hardware.

## 1.1 THE SIMD IDEA

The idea of SIMD stems from the observation that there is data-parallelism in almost every compute intensive algorithm. Data-parallelism occurs whenever one or more operations are applied repeatedly to several values. Typically, programming languages only allow iterating over the data, which leads to strictly serial semantics. Alternatively (e.g. with C++), it may also be expressed in terms of a standard algorithm applied to one or more container objects.<sup>2</sup>

Hardware manufacturers have implemented support for data-parallel execution via special instructions executing the same operation on multiple values (Listing 1.1). Thus, a single instruction stream is executed but multiple (often 4, 8, or 16) data sets are processed in parallel. This leads to an improved transistors per FLOPs<sup>3</sup> ratio<sup>4</sup> and hence less power usage and overall more capable CPUs.

<sup>1</sup> Single Instruction, Multiple Data

<sup>2</sup> Such an algorithm can relax the iteration ordering and thus place additional restrictions on the semantics—in terms of concurrency—of the executed code. (cf. [36])

<sup>3</sup> floating-point operations

<sup>4</sup> The number of transistors required for instruction decoding and scheduling is large relative to the transistors needed for the arithmetic and logic unit. However, mainly the latter must be increased if

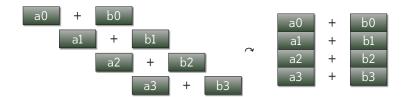

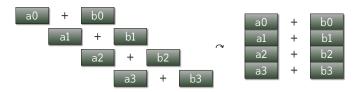

Figure 1.1: Transformation of four scalar operations into one SIMD operation.

```

; scalar multiply-add: 1 FLOP per instruction

mulss %xmm1,%xmm0

addss %xmm2,%xmm0

; SSE multiply-add: 4 FLOP per instruction

mulps %xmm1,%xmm0

addps %xmm2,%xmm0

; AVX multiply-add: 8 FLOP per instruction

vmulps %ymm1,%ymm0,%ymm0

vaddps %ymm2,%ymm0,%ymm0

; AVX with FMA multiply-add: 16 FLOP per instruction

vfmadd213ps %ymm1,%ymm0,%ymm2

```

Listing 1.1: Example of SIMD instructions in x86-64 assembly.

Figure 1.1 visualizes the conceptual idea of SIMD execution. Code that needs to execute four add operations on four different value pairs needs four instructions to execute the addition operations. Alternatively, the same result can be achieved with a single SIMD instruction that executes four addition operations on two vectors with four values each. In terms of operations per instruction, the SIMD variant is a factor four better. Since on most modern CPUs the scalar and the vector instruction execute equally fast this translates directly to a factor four higher operations per cycle throughput.

In the following,  $\mathcal{W}_{\mathbb{T}}$  denotes the number of scalar values in a SIMD vector register of type  $\mathbb{T}$  (the width of the vector). Thus, with SSE<sup>6</sup> or AltiVec  $\mathcal{W}_{\texttt{float}} = 4$  and with AVX<sup>7</sup> it is 8 (see Section 1.4). In addition,  $\mathcal{S}_{\mathbb{T}}$  denotes  $\texttt{sizeof}(\mathbb{T})$ . It follows that  $\mathcal{S}_{\mathbb{T}} \cdot \mathcal{W}_{\mathbb{T}}$  is the size of a SIMD vector of type  $\mathbb{T}$  in Bytes.

a  $CPU^5$  adds SIMD instructions or grows the SIMD width. Therefore, the total number of transistors grows by a fraction whereas the peak performance (in terms of operations per cycle) doubles.

<sup>6</sup> Streaming SIMD Extensions

<sup>7</sup> Advanced Vector Extensions

In the original Von Neumann architecture [66] from 1945 the processing unit of a computer consists of a "central arithmetical part", a "central control part", various forms of memory, and I/O. In all of the first computer designs registers and operations were meant to store and process only single (scalar) values. Thus, the ALUs<sup>8</sup> only processed one value (normally two inputs and one output) with a given instruction. This model later became known as SISD (according to Flynn [24]), because a *Single Instruction* processes a *Single Data* element.

In 1972, the ILLIAC IV [38] was the first array machine to introduce SIMD computing [78]. Array machines employ multiple processing units (PEs<sup>9</sup>) in parallel, which are controlled from the same instruction stream. They may support conditional execution via flags that enable/disable a selected PE. The PEs have some form of local memory and a local index to identify their position in the whole machine. Tanenbaum [78] describes the history and architecture of these machines in more detail. These machines became known as SIMD machines because a *Single Instruction* processes *Multiple Data* elements.

The modern implementation of SIMD machines are called vector machines. The name *vector* stems from the use of wide registers able to store multiple values. Associated *vector instructions* process all entries in such *vector registers* in parallel. For some time, vector instructions were only targeted at specific problems, such as multimedia processing. However, over the years many more instructions have been introduced, making the vector units more suited for general purpose computing.

Whereas array machines have a greater separation between the different PEs, vector machines use the same memory for the whole vector register. Additionally, there is no natural identification in vector machines that would resemble the local index of array machines. Vector instructions, in most hardware, calculate the result for all vector lanes<sup>10</sup> and have no means to selectively write to the destination register. Subsequent blend instructions (or a combination of and, andnot, or) can be used to achieve conditional assignment. Newer vector instructions (the Intel Xeon Phi and AVX-512) now support generic write-masking encoded into every instruction.

The rest of the document will focus on vector machines. Most considerations can be directly translated to a classical SIMD machine, though.

<sup>8</sup> Arithmetic Logic Units

<sup>9</sup> Processing Elements

<sup>10</sup> A vector lane (or SIMD lane) identifies a scalar entry in a vector register. Most SIMD instructions execute the same operation per lane and do not read/write any data from/to lanes at a different offset in the register. In that sense they are comparable to the PEs of array machines.

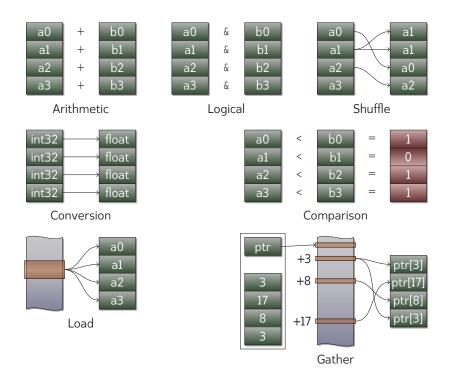

Figure 1.2: Overview over common SIMD vector operations. Shuffle operations are special because they execute cross-lane data movement and are important to build reduction functions, for example. Load and gather operations copy  $\mathcal{W}_{\mathbb{T}}$  values from consecutive or indexed—respectively—memory locations. The reverse operations, store and scatter, also exist. The remaining depicted operations show the concurrent execution of  $\mathcal{W}_{\mathbb{T}}$  operations on  $\mathcal{W}_{\mathbb{T}}$  different operands.

# 1.3 SIMD OPERATIONS

The set of possible SIMD operations closely mirrors the available scalar instructions. Accordingly, there are instructions for arithmetic, compare, and logical operations. Figure 1.2 gives an overview for  $\mathcal{W}_{\mathbb{T}}=4$ . However, SIMD instruction sets typically are not complete. For instance, the SSE 32-bit integer multiply instruction did not exist until the introduction of SSE4. Also division (especially for integers) is a likely candidate for omission in SIMD instruction sets (cf. [41, 70]). This difference in available operations is one reason why it is not easy to predict the speedup from vectorization of a given algorithm.

1.3.1 ALIGNMENT

SIMD programming requires special attention to alignment, otherwise the program may perform worse or even crash. The C++ standard defines alignment in [48, §3.11]:

Object types have alignment requirements which place restrictions on the addresses at which an object of that type may be allocated. An alignment is an implementation-defined integer value representing the number of bytes between successive addresses at which a given object can be allocated.

For fundamental types the alignment requirement normally equals the size of the type.

A vector register requires  $\mathcal{W}_{\mathbb{T}} \cdot \mathcal{S}_{\mathbb{T}}$  Bytes when stored in memory. SIMD architectures typically require the natural alignment of vectors in memory to be equal to their sizes. Thus, the alignment requirement is  $\mathcal{W}_{\mathbb{T}}$  times higher than for type  $\mathbb{T}$  (alignof (VT) =  $\mathcal{W}_{\mathbb{T}} \cdot alignof$  (T), where VT is the type for a vector of T). Only every  $\mathcal{W}_{\mathbb{T}}$  address in an array of T is a valid aligned address for vector register load and store operations. One may therefore consider the memory to be an interleaving of memory that is local to each SIMD lane. Consequently, memory is partitioned into  $\mathcal{W}_{\mathbb{T}}$  parts for a given type T.

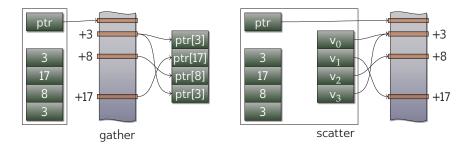

Nevertheless, there are several mechanisms to break this natural partitioning of the memory and assign data to different SIMD lanes. The most obvious of them are unaligned loads and stores. These are usable with an arbitrary offset into an array. It is also possible to execute two aligned loads and stores together with one or more vector shuffle instructions. Additionally, for greatest flexibility, a SIMD instruction set might support gather and scatter instructions. These take a base address and a vector of offsets to load or store the entries of a vector from/to arbitrary memory locations.

1.3.2 COMPARISONS

Another important set of instructions are comparisons. In contrast to compare operations of fundamental types, there cannot be a single true or false answer for a SIMD comparison. Instead there must be  $\mathcal{W}_{\mathbb{T}}$  boolean values in the result. This implies that such an instruction cannot sensibly set any of the flags that most architectures use for branching instructions.

A vector of  $\mathcal{W}_{\mathbb{T}}$  boolean values is called a *mask*. There exist different implementations for such masks. They can either use the same registers as the data vectors or they are stored in specialized mask registers. Special mask registers can thus be optimized to store only  $\max\{\mathcal{W}_{\mathbb{T}} \forall \mathbb{T}\}$  Bits. If the mask is stored in a vector register,

it is useful to have an instruction converting the mask to an integer where every bit corresponds to one boolean value of the mask.

# 1.4 CURRENT SIMD INSTRUCTION SETS

There have been many different SIMD computers, but the most relevant SIMD instruction sets at the time of writing are the ones based on x86, ARM, and PowerPC architectures.

1.4.1 POWERPC

The PowerPC architecture is most relevant for its use in the Xbox 360 and PlayStation 3 game consoles and the Blue Gene supercomputers. These CPUs provide SIMD instructions known as AltiVec, VMX, VMX128, or Velocity Engine. *PowerPC Microprocessor Family: Vector / SIMD Multimedia Extension Technology Programming Environments Manual* [70] documents the details: The vector registers are 128 bits wide and can store sixteen 8-bit, eight 16-bit, or four 32-bit integers or four 32-bit single-precision floats. Thus, 64-bit data types, especially double-precision floats, are not supported in AltiVec vector registers. In addition to typical arithmetic operations the instruction set contains FMA<sup>11</sup> operations. Also, AltiVec contains a generic permute instruction for very flexible data reorganization from two source registers.

1.4.2 ARM

The ARM architecture is becoming more and more relevant, not only because of its use in mobile products, but moreover because of its potential as energy-efficient general-purpose computing platform. Most current ARM designs include a SIMD instruction set called NEON, which was introduced with the ARM Cortex<sup>™</sup>-A8 processor (ARMv7 architecture). *Introducing NEON* [47] provides an introduction. The vector registers can be accessed as sixteen 128-bit or thirty-two 64-bit registers. There is no need to explicitly switch between 128-bit and 64-bit vector registers as the instruction used determines the view on the register bank. If the VFPv3 instructions are implemented, the vector registers additionally alias the floating-point registers. The registers can pack 8-bit, 16-bit, 32-bit, or 64-bit integers or 32-bit single-precision floats. Optionally, NEON supports fast conversion between single-precision floats and fixed-point, 32-bit integer, or half-precision floats.

Even without the NEON extension, ARM CPUs (since ARMv6) support a small set of SIMD instructions on integer values packed into standard 32-bit registers.

<sup>11</sup> Fused Multiply-Add

1.4.3 x86

Intel introduced the first SIMD extension to the x86 family in 1997 with the "Pentium processor with MMX Technology" [69]. This extension is still supported but for all practical purposes superseded by the SSE and SSE2 extensions that followed in 1999 and 2001. SSE provides eight (sixteen in 64-bit mode) vector registers which are 128 bits wide. It supports 8-bit, 16-bit, 32-bit, and 64-bit integers in addition to 32-bit single-precision and 64-bit double-precision floats. The available instructions for the different integer types differ slightly and some useful integer instructions were only added with later SSE revisions. For all recent microarchitectures the usage of SIMD instructions improves computational throughput by a of factor  $\mathcal{W}_{\scriptscriptstyle \rm T}$ .  $^{12}$  With the Intel SandyBridge and AMD Bulldozer microarchitectures (both released in 2011) AVX was introduced, doubling the SIMD register width on x86. However, AVX only shipped full-width arithmetic instructions for single-precision and double-precision floats. Thus,  $\mathcal{W}_{\scriptscriptstyle T}$  effectively only doubled for float and double. With the Intel Haswell microarchitecture (released in 2013) AVX2 was introduced. AVX2 includes the missing integer arithmetic instructions. Additionally, AVX2 includes gather instructions able to optimize indirect array reads. AMD introduced FMA instructions with the Bulldozer microarchitecture in 2011. The use of FMA instructions is required on Bulldozer for full performance. Intel introduced FMA with Haswell and thus doubled SIMD performance relative to the previous microarchitecture, as well.

1.4.4 INTEL XEON PHI

The Intel Xeon Phi is a highly parallel, high performance computing accelerator to compete with GPUs<sup>13</sup> for general-purpose computing. It is built from many small, relatively slow, but 16-way vectorized CPU cores. The Xeon Phi provides 32 vector registers of 512 bits width. It supports sixteen 32-bit integers, sixteen 32-bit single-precision floats, or eight 64-bit double-precision floats. There is limited support for 64-bit integers. Other data types are supported via cheap conversions at load or store.

On the Xeon Phi, one vector register is exactly as large as one cache line. Consequently, any unaligned vector load or store is certain to be more expensive than an aligned access. This is clearly visible in the Xeon Phi's instruction set where unaligned loads and stores each require two instructions: one instruction per cache line. Furthermore, the large register size has implications on locality considera-

<sup>12</sup> This is not entirely true for the AMD Bulldozer microarchitecture. The effective SIMD width is that of SSE. AVX support is implemented as execution of two 128-bit operations.

<sup>13</sup> Graphics Processing Units

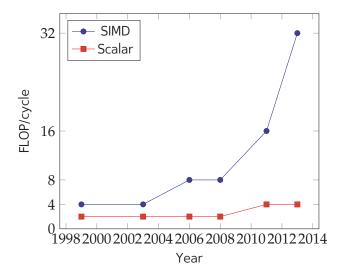

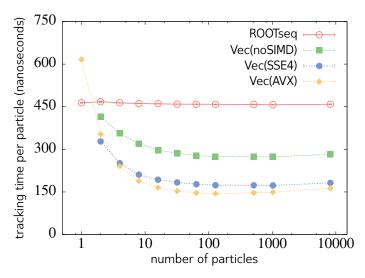

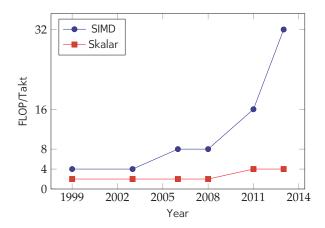

Figure 1.3: The maximum single-precision FLOP/cycle when using SIMD/scalar instructions on a single thread on x86(-64) (maximum of AMD and Intel CPUs) plotted against year of releases of new microarchitectures. [74, 26, 41]

tions since loading one full vector does not fetch any other related or unrelated data.

# 1.5 THE FUTURE OF SIMD

In the last years we have seen a steady rise in importance and performance relative to scalar instructions for SIMD (see Figure 1.3). This development is unlikely to reverse. It is consequential to expect that vector registers are going to become wider and/or that more efficient SIMD instructions will be released. The AVX instruction coding (VEX prefix) has a 2-bit field encoding the width of the register. Values 0 and 1 are used for 128-bit and 256-bit width, respectively. Values 2 and 3 are likely to be used for 512-bit and 1024-bit wide vectors.

GPUs have shown the great potential of SIMD in general purpose computing. The important GPU architectures are internally similar to SIMD architectures, even though they are typically able to make independent progress on all the "quasi-threads", requiring an explicit barrier for inter-lane communication. Their programming models are becoming more flexible with every release and will likely converge more and more to general purpose programming models (such as full C++ support).

## 1.6 INTERACTION WITH OTHER FORMS OF PARALLELISM

Hardware designers have implemented several dimensions of parallel execution in current CPU architectures to achieve high performance. It is therefore certainly possible that, if use of the SIMD dimension is increased, a different dimension has less opportunity to parallelize the execution. This section will discuss the issue.

## 1.6.1 INSTRUCTION LEVEL PARALLELISM

CPUs use pipelining to start execution of subsequent instructions in the instruction stream while previous ones have not been retired yet. However, in general an instruction cannot start before all its input registers are ready, implying that all instructions writing to those registers need to have retired. Therefore, a stream of instructions where each one depends on the output of the previous one cannot benefit from pipelining. It is often possible to execute several serial instruction streams on independent data streams in the same time required to process a single data stream. Consequently, compilers (and sometimes also developers) apply loop unrolling to create this data-parallel stream of independent calculations.

Some transformations from a scalar implementation to a SIMD implementation may reduce the opportunity for pipelined execution. This is especially the case with "vertical vectorization" (cf. [59]), where several independent, serially executed instructions are transformed into a single SIMD-parallel instruction. In such a case the execution units are stalling for longer durations in the SIMD implementation. It is one of the reasons why vectorization sometimes does not yield the expected speedup. Especially, because current compilers are sometimes not as smart about loop unrolling SIMD code as they are for scalar code. Manual loop unrolling of SIMD code often improves the vectorization results.

Superscalar execution is another dimension of parallelism present in current CPUs [40]. The CPU schedules instructions to different execution units, which work independently. Typically, the execution units are specialized for a specific set of instructions. For example, the Intel SandyBridge CPU can schedule execution of up to 6 micro-ops every cycle. Mapped to actual instructions this could be one floating-point add/sub, one floating-point mul, and two 128-bit load instructions [41]. Superscalar execution therefore does not compete with SIMD parallelization. It equally accelerates SIMD and scalar instructions.

Speculative execution is an optimization tied to branch prediction. The CPU predicts which path the code will take at a given branch instruction. It will then continue to execute the predicted code path (only operations that can be rolled back) as if the branch was taken. On a mis-prediction this work will be rolled back and the other branch will be executed. SIMD code often has fewer branches because branch

<sup>14</sup> This is not a fundamental problem, but just missing optimizations in the compiler.

conditions are tied to scalar values and not the whole vector. Consequently, SIMD code has to execute all branches and use conditional assignment to merge the results. SIMD code therefore does not benefit as much from speculative execution and might not yield a good speedup for algorithms with many conditionals.

1.6.2 MULTIPLE CORES

Common frameworks for thread-parallelization, such as OpenMP [68] and TBB<sup>15</sup> [45] provide easy to use multi-threaded execution of data-parallel algorithms (and more) via fork-join execution. The common parallel-for construct splits the work of a given loop into several chunks that are executed on separate worker threads. This parallelization strategy is very efficient because it makes the code scale from low to high CPU core counts rather easily. However, SIMD relies on data-parallelism as well. Therefore, on the one hand, vectorization and multi-threading may compete for the same inherent parallelism. On the other hand, the combination of multi-threading and vectorization may also complement each other, because in contrast to SIMD execution threads allow concurrent execution of different/diverging tasks.

# 1.7 COMMON OPTIMIZATION CHALLENGES

If a given scalar code is transformed into SIMD code the throughput of arithmetic (and logic and compare) operations can increase as much as by a factor of  $\mathcal{W}_{\mathbb{T}}$ . For almost every algorithm this requires an equal increase in load/store throughput. Thus, the size of the working set increases and the cache may be under considerably higher pressure.

The load/store unit may also be a bottleneck. For example, the Intel SandyBridge and AMD Bulldozer microarchitectures both can execute up to two 128-bit loads and one 128-bit store per cycle [74, 41]. Thus, only one AVX vector can be read from L1 cache per cycle, and only one AVX vector can be stored to L1 cache every second cycle. This is a considerable limitation, given that these CPUs can execute two AVX floating-point instructions or even three AVX logical operations per cycle. Intel therefore improved the Haswell microarchitecture to allow two 256-bit loads and one 256-bit store per cycle [40].

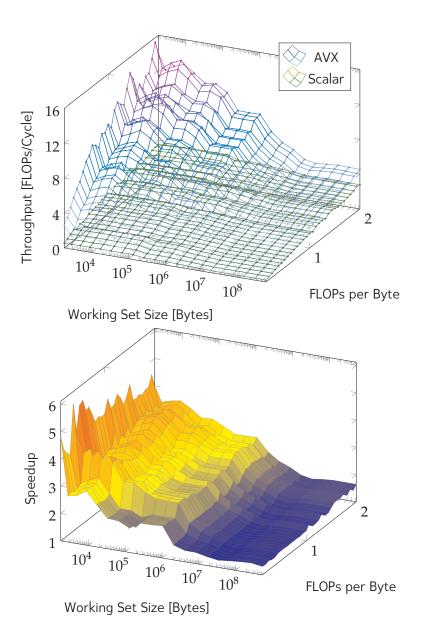

Figure 1.4 shows the result of a benchmark (cf. Appendix A) testing the floating-point operations throughput for different scenarios. It turns out that SIMD improves the throughput for every tested case. Even if very few operations are executed over a very large working set, the result is slightly improved by using SIMD. This is visible in the lower plot showing the speedup factor  $\frac{\text{AVX}}{\text{Scalar}}$ .

Figure 1.4: The plot shows the measured (single-precision) FLOPs per clock cycle depending on the working set size and the amount of calculation per data access (loads and stores combined). The benchmark was compiled and executed once with AVX instructions and once without SIMD instructions for an AMD Bulldozer CPU. It uses FMA instructions in both cases. However, the number of values that are processed in parallel depend on  $\mathcal{W}_{\text{float}}$ . The speedup plot shows the quotient of the AVX throughput relative to the scalar throughput ( $\frac{\text{AVX}}{\text{Scalar}}$ ). (Note that for AVX, with  $\mathcal{W}_{\text{float}}=8$ , the best theoretical speedup is 800%. See Appendix A for the benchmark code.)

1.8

Software developers and designers have to consider SIMD. Developers need to understand what SIMD can do and how it can be used. Only then a developer can design data structures and algorithms which fully utilize modern CPUs. Especially compute intensive programs need to use the SIMD capabilities, otherwise CPU utilization will only be at 6–25% of theoretical peak performance. However, programs that are bound by memory accesses can also benefit from vectorization since SIMD can make many memory operations more efficient (cf. Figure 1.4). Only tasks such as user interaction logic (and other inherently sequential codes) often have no use for SIMD.

From the discussion of different forms of parallelism we can conclude that it is helpful for developers to understand how SIMD and other forms of parallelism work. Blindly vectorizing a given code might not yield the expected performance improvement. Therefore, the interface for data-parallel programming should provide as much guidance as possible. Such an interface needs to be designed from use-cases of important parallelization patterns, and not only from existing hardware capabilities. This design process will additionally lead to an abstraction that can hide the substantial differences in hardware.

## LOOP-VECTORIZATION

It is a common pattern of software development to execute a sequence of operations on different input values. Programming languages support this pattern with loop statements. In particular, the for-loop is designed for iteration over an index or iterator range. In many cases the individual iterations of the loop are independent from one another (or could be expressed in such a way) and could therefore be executed in any order and even in parallel. This observation has led to many parallelization interfaces that build upon parallelization of loop iterations.

Loop-vectorization, including auto-vectorization, is likely the most prevalent method of vectorization. Since this work presents a solution for SIMD programming in C++ this chapter will present the main alternatives and discuss their limitations and issues. The following chapters on Vc (Part II) will show that these issues are solved / do not occur with SIMD types.

#### 2.1 DEFINITIONS

COUNTABLE LOOPS A common requirement of tool-based vectorizers is that the number of iterations a loop will execute can be determined before the loop is entered. Loops where this condition holds are called *countable*.

VECTORIZATION The process of transforming a serial/scalar code into vector/SIMD code is called *vectorization*. This transformation is relatively simple to apply for (inner) loops. As a simple example consider Listing 2.1. (The iteration-count can be determined before the loop is entered, making the loop *countable*.) The iterations are all independent, because &d[i]  $!= \&d[j] \forall i \neq j$ . Thus, the loop may be transformed into N/ $\mathcal{W}_{float}$  iterations where each remaining iteration executes

```

void func(float *d) {

for (int i = 0; i < N; ++i) {

d[i] += 1.f;

}

}</pre>

```

Listing 2.1: A simple countable loop of independent calculations.

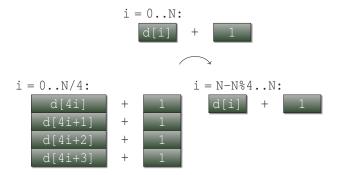

Figure 2.1: Illustration of the loop transformation which the vectorizer applies: A loop over N additions is transformed into a vectorized loop and possibly a scalar prologue and/or epilogue loops. This transformation is the basic strategy for (automatic or manual) vectorization of most data-parallel problems.

$\mathcal{W}_{\text{float}}$  additions with one instruction (Figure 2.1). Plus a remainder loop in case N is not a multiple of  $\mathcal{W}_{\text{float}}$ .

AUTO-VECTORIZATION Auto-vectorization describes the process of automatically locating vectorizable code and applying the necessary code transformations. In most cases this is done in an optimization step of the compiler. Alternatively, there are tools (i.e. meta-compilers) translating scalar code to (compiler-specific) SIMD code. The auto-vectorizer identifies vectorizable loops or possibly vectorizable sequences of scalar operations on adjacent values in an array.

EXPLICIT LOOP-VECTORIZATION For a given loop, the developer can annotate the loop as SIMD loop. There are two basic approaches to these loop annotations:

- 1. The loop annotation tells the compiler that the developer expects the loop to be vectorizable under the transformation rules of the auto-vectorizer. Therefore, the developer can reason about his/her code with serial semantics<sup>1</sup>. On the other hand, if auto-vectorization fails it is now possible for the compiler to generate more diagnostic information.<sup>2</sup> In addition to stating the intent, the annotation typically supports additional clauses able to guide the vectorizer to better optimizations.

- The loop annotation alters the semantics of the loop body. Serial semantics do not apply anymore. Instead vector semantics are used and the compiler does not have to prove that serial semantics and vector semantics produce

<sup>1 &</sup>quot;Serial semantics" characterizes the normal C++ sequenced before rule [48, §1.9 p13].

<sup>2</sup> At least with GCC<sup>3</sup> 4.9.1 no useful diagnostics were printed when the loop failed to be vectorized (even with the -Wopenmp-simd flag).

the same result. Thus, cross-iteration data-dependencies (e.g. **for** (**int** i = 0; i < N - 1; ++i) a[i] += a[i + 1];) will not inhibit vectorization, enabling a new class of algorithms to be vectorizable via loops. However, it can lead to subtle bugs where the developer (erroneously) reasons about the code with serial semantics.

The following discussion will only refer to the second variant of explicit loop-vectorization, because it is the more general and powerful solution. The first variant only slightly improves over the auto-vectorization status-quo.

VECTOR SEMANTICS A thorough definition of vector semantics is an important prerequisite for an implementation of explicit loop-vectorization in a programming language. The Parallelism TS [49] states the following on the semantics of code executed with a vector-parallel execution policy:

The invocations of element access functions [...] are permitted to execute in an unordered fashion [...] and unsequenced with respect to one another within each thread.

For a loop, this means that individual iterations can make independent progress, progress in lock-step, or in any conceivable interleaving. Riegel [71] defines a possible forward progress guarantee for "weakly parallel execution":

The implementation does not need to ensure that a weakly parallel EA<sup>4</sup> is allowed to execute steps independently of which steps other EAs might or might not execute.

Geva et al. [30] state a formal definition of the wavefront execution model (cf. [35]), which is a stricter progress guarantee for vector semantics:

A SIMD loop has logical iterations numbered 0, 1, ..., N-1 where N is the number of loop iterations, and the logical numbering denotes the sequence in which the iterations would execute in the serialization of the SIMD loop. The order of evaluation of the expressions in a SIMD loop is a partial order, and a relaxation of the order specified for sequential loops. Let  $X_i$  denote evaluation of an expression X in the i<sup>th</sup> logical iteration of the loop. The partial order is:

For all expressions X and Y evaluated as part of a SIMD loop, if X is sequenced before Y in a single iteration of the serialization of the loop and  $i \le j$ , then  $X_i$  is sequenced before  $Y_j$  in the SIMD loop.

[ *Note:* In each iteration of a SIMD loop, the "sequenced before" relationships are exactly as in the corresponding serial loop. — *end note* ]

<sup>4</sup> EA (Execution Agent) is defined by  $ISO/IEC\ 14882:2011\ [48, \S 30.2.5.1]$  as: "An execution agent is an entity such as a thread that may perform work in parallel with other execution agents."

This overview shows that there is no consensus—at this time—for the specifics of vector semantics. Any further discussion in this document involving vector semantics applies to all variants of vector semantics, though.

#### AUTO-VECTORIZATION

#### 2.2.1

2.2

#### USES FOR AUTO-VECTORIZATION

It is the job of a compiler to create the best machine code from a given source. The executable code should make use of the target's features (in terms of instruction set and micro-architecture) as much as is allowed under the "as-if" rule of C++ [48, §1.9 p1]. Therefore, auto-vectorization is an important optimization step. Many codes can benefit without any/much extra effort from the developer's side. This is important for low-budget development or developers without experience in parallel programming. It can also be used for highly optimized codes. Though, in this case explicit loop-vectorization should be preferred, as the implicit expression of parallelism is fragile in terms of maintainability.

#### 2.2.2

#### INHIBITORS TO AUTO-VECTORIZATION

Intel documented the capabilities and limitations of the ICC<sup>5</sup> auto-vectorizer in detail [4]. They point out several obstacles and inhibitors to vectorization:

Non-contiguous memory accesses: Non-contiguous memory accesses lead to inefficient vector loads/stores. Thus the compiler has to decide whether the computational speedup outweighs the inefficient loads/stores.

Data dependencies: Data dependencies between the iteration steps make it hard or impossible for the compiler to execute loop steps in parallel.

Countable: If the loop is not countable the compiler will not vectorize.

Limited branching: Branching inside a loop leads to masked assignment. Instead of actual branches in the machine code, the auto-vectorizer has to emit code that executes all branches and blend their results according to the condition on each SIMD lane. If the compiler determines that the amount of branching negates the improvement of vectorization it will skip the loop.

Outer loops: Outer loops (loops containing other loops) are only vectorized after certain code transformations were successful.

Function calls: Function calls inhibit vectorization. However, functions that can be inlined and intrinsic math functions are exceptions to this rule.

<sup>5</sup> Intel C++ Compiler

THREAD INTERACTION: Any calls to mutexes, or atomics inhibit auto-vectorization.

Auto-vectorization in GCC [5] additionally documents that for some SIMD transformations the order of arithmetic operations must be modified. Since this kind of optimization can change the result when applied to floating-point variables it would deviate from the C++ standard. The standard specifies that operators of equal precedence are evaluated from left to right. Consequently, Auto-vectorization in GCC [5] recommends the -ffast-math or -fassociative-math flags for best auto-vectorization results.

#### 2.2.3

#### LIMITATIONS OF AUTO-VECTORIZATION

In most cases, auto-vectorization cannot instantly yield the best vectorization of a given algorithm (if at all). This is in part due to the limited freedom the compiler has in transforming the code, such as aliasing issues, fixed data structures, pointer alignment, function signatures, and conditional statements. Another important part is that the user did not express the inherent data-parallelism explicitly. The compiler has to infer information about the problem that got lost in translation to source code. Finally, the user has to limit himself to a subset of the language as listed in Section 2.2.2.

If a user wants to vectorize his/her code via auto-vectorization, it is necessary to let the compiler report on its auto-vectorization progress and use this information to adjust the code for the needs of the vectorizer. Sometimes this can require larger structural changes to the code, especially because data storage must be transformed from arrays of structures to structures of arrays. Additionally, users should add annotations about the alignment of pointers to improve vectorization results.

2.2.3.1 ALIASING

Auto-vectorization relies on iterations over arrays to express the per-iteration input and output data. Since structures of arrays work best for the vectorizer, the loop body typically dereferences several pointers to the same fundamental data type. The compiler must account for the possibility that these pointers are equal or point to overlapping arrays. Then, any assignment to such an array potentially alters input values and might create cross-iteration dependencies.

```

float add_one(float in) {

return in + 1.f;

}

```

Listing 2.2: A simple function.

```

float *data = ...

for (int i = 0; i < N; ++i) {

data[i] = add_one(data[i]);

}</pre>

```

Listing 2.3: A function call in a loop.

## 2.2.3.2

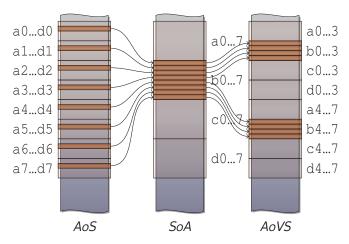

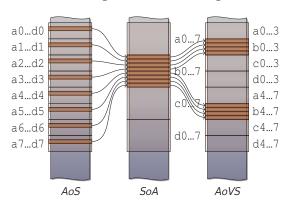

FIXED DATA STRUCTURES

A major factor for the efficiency of a vectorized algorithm is how the conversion from  $\mathcal{W}_{\mathbb{T}}$  scalar objects in memory to a single vector register and back is done. The compiler has no freedom to improve the data layout, which is fully defined by the types used by the algorithm. At the same time, the scalar expression of the algorithm conceals the problem from the developer who often is oblivious to the limitations of the vector load and store operations of the hardware.

2.2.3.3 POINTER ALIGNMENT

In most cases the compiler cannot deduce whether a given pointer uses the necessary over-alignment for more efficient vector load and store instructions. Without extra effort, and an understanding of hardware details, the user will therefore create a more complex vectorization of the algorithm than necessary.

## 2.2.3.4 FUNCTION SIGNATURES

Consider a simple function like Listing 2.2. A function defines an interface for data in- and/or output. There are fixed rules how to translate such code to a given  $ABI^6$ . For example the in parameter has to be stored in the bits 0–31 of register xmm0 on x86\_64 Linux. Unless the compiler is allowed/able to inline the function, the function itself cannot be vectorized. Neither can a calling loop, such as Listing 2.3, be vectorized in this case.

In theory, the above limitation can be solved with LTO<sup>7</sup>. With LTO the compiler has more opportunity to inline functions since it still has access to the abstract syntax tree of the callee when the optimizer vectorizes the caller loop.

<sup>6</sup> Application Binary Interface

<sup>7</sup> Link Time Optimization

## 2.2.3.5

#### CONDITIONAL STATEMENTS

Many algorithms require conditional execution which depends on the actual values of the input data. Since the algorithm is expressed with scalar types, the user has to use if-statements (or while, for, or switch). These cannot be vectorized as actual branches. Instead, the vectorized code has to execute all cases and implicitly mask off assignments according to the conditions in the different vector lanes. This leads to more code that needs to be executed and the user may be completely unaware of the cost of conditionals (and possible alternatives), unless (s)he has learned how the vectorizer and the target hardware works.

# 2.3 EXPLICIT LOOP-VECTORIZATION

ICC has integrated explicit loop-vectorization (SIMD-loops) in their compiler via the #pragma simd extension [42]. Intel considers this extension important enough that they are pursuing inclusion of this feature in the C++ standard (cf. [30, 35]). The extension is a significant improvement over auto-vectorization, where the developer has no mechanism to ensure SIMD parallel execution of a given loop.

All the limitations described in Section 2.2.3 still apply to explicit loop-vectorization. In contrast to auto-vectorization, the user explicitly expresses that the algorithm is data-parallel, which improves diagnostics and maintainability. In addition, optional clauses to the SIMD-loop syntax allow the user to guide the compiler to a more efficient vectorization.

Vector semantics (as defined in Section 2.1) imply the following restrictions, which are correct and well-defined scenarios with serial semantics:

- The behavior is undefined for loops with cross-iteration dependencies, unless correctly annotated with a clause such as safelen. It would be desirable to require compilers to make SIMD-loops with such dependencies ill-formed. This is impossible, though, because the dependencies might be hidden behind pointer aliasing. The issue is thus only detectable at run time.

- Thread synchronizing operations, such as mutexes, may deadlock. Current implementations of explicit loop-vectorization either have to declare synchronizing operations either as undefined behavior or ill-formed.

- If an exception is thrown in a vector loop, the behavior is undefined or may result in a call to std::terminate.<sup>8</sup>

If such a case occurs in a (non-inline) function called from the SIMD-loop, the compiler cannot recognize the condition, in which case auto-vectorization would be inhibited. With vector semantics it is well-defined behavior to call the function

<sup>8</sup> std::terminate is the consequence of throwing a second exception during stack unwinding [48].

for each entry in the SIMD vector in sequence, though. This can lead to deadlock, surprising side-effects (e.g. global variables), or inconsistent exceptions with a possible call to std::terminate.

The user must therefore be aware of the different semantics and the functions (s)he calls. Especially calls into library functions may be fragile as a new release of the library might become unsafe to use in a SIMD-loop.

## INTRODUCTION TO SIMD TYPES

Perhaps the greatest strength of an object-oriented approach to development is that it offers a mechanism that captures a model of the real world.

- Grady Booch (1986)

# 3.1 THE SIMD VECTOR TYPE IDEA

Most of the current commodity hardware supports SIMD registers and instructions. However, C++ projects that target these systems have no standardized way to explicitly use this part of the hardware. The solutions that currently serve as best practice are auto-vectorization (i. e. pure scalar code / cf. Section 2.2), OpenMP 4 [68] and Cilk Plus [44] SIMD loops (cf. Section 2.3), vendor-specific SIMD intrinsics (cf. Section 3.2), and (inline) assembly. C++ itself only provides types and operators for scalar integer and floating-point registers and instructions. The standard leaves most of the mapping of type names to exact register widths implementation-defined. SIMD registers and operations are simply ignored in the standard and left to "as-if" transformations of the optimizer (auto-vectorization).

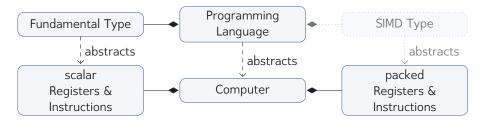

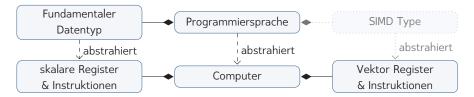

If C++ were to provide types that map to implementation-defined SIMD registers and instructions then SIMD instructions would be just as accessible as scalar instructions (see Figure 3.1). Such a SIMD type should, in most respects, behave analogous to the scalar type, in order to make SIMD programming intuitively usable for any C++ developer. The obvious difference to scalar types is that instead of storing and manipulating a single value, it can hold and manipulate  $\mathcal{W}_{\mathbb{T}}$  values in parallel.

Since the differences between different target microarchitectures are a lot more significant in SIMD instructions than in scalar instructions, the portability concerns with these types are a lot more apparent than with scalar types. Therefore, while the type needs to be target-dependent, the interface must be target-agnostic. The type thus needs to express data-parallel execution in an abstract form. It should not be designed specifically for SIMD execution, which is just one form of efficient

Figure 3.1: Programming languages abstract how computers work. The central processing units of the computer is controlled via registers and instructions. Most languages, notably C++, use types and their associated operators to abstract registers and instructions. Though, since the advent of SIMD registers and instructions there exists a gap in the abstraction.

data-parallel execution. Such a strong design focus on SIMD could make the type less portable, thus less general, and therefore less useful.

On the other hand, a type that cannot translate to the most efficient SIMD instructions (in all but maybe a few corner cases) would not be useful either. Users that want to explicitly optimize for a given target architecture should be able to do so with the SIMD type. The design goal is therefore to make the vector types (together with a properly optimizing compiler) as efficient as hand-written assembler SIMD code.

# 3.2 SIMD INTRINSICS

All major C++ implementations provide SIMD intrinsics as an extension to the standard. These extensions provide types and functions that map directly to the available SIMD registers and instructions. One of the most widespread extensions are x86 SIMD intrinsics for MMX<sup>1</sup>, SSE, AVX.

Another important extension are builtin vector types, which provide more contextual information to the middle-end and back-end of the compiler. The GCC and clang implementations of vector builtins support operators for the vector types and retain more information for the optimizer about the per-entry operations that are executed. This allows the compiler to be smarter about optimizing sequences of SIMD operations.

<sup>1</sup> Multimedia Extensions

A SIMD vector type constitutes the low-level interface to SIMD programming.<sup>2</sup> It is possible to build higher levels of abstraction using standard C++ facilities on top of these types. If this lowest level of SIMD programming is not provided then users of C++ will be constrained to work within the limits of the provided higher level abstraction. Even if such an abstraction were very efficient for most problems, it could lead to a situation where an additional and unrelated means of SIMD programming (outside of standard C++) were still required.

In some cases the compiler might generate better code if only the intent is stated instead of an exact sequence of operations. Therefore, higher-level abstractions might seem preferable to low-level SIMD types. In my experience this is not the case because programming with SIMD types makes intent very clear and compilers can optimize sequences of SIMD operations. This is effectively identical to optimizations on scalar operations.

SIMD types themselves do not lead to an easy and obvious answer to efficient and easily usable data structures. However, SIMD types reveal inefficient data structures, as they become hard or awkward to use. This can guide developers to create more efficient data structures for vectorization. Chapter 10 shows a high-level interface to data structure vectorization, which can make creation of proper vectorizable data structures easier or even completely transparent for a user of a given interface (such as shown in Chapter 11). On the other hand, a SIMD programming abstraction that completely hides vectorized memory accesses behind scalar memory accesses requires compiler diagnostics to guide the developer to more efficient data structures.

One major benefit from SIMD types is that the programmer can gain an intuition for SIMD. This subsequently influences further design of data structures and algorithms to better suit SIMD architectures.

Additionally, there are already many users of SIMD intrinsics (and thus a primitive and non-portable form of SIMD types). Providing a cleaner and portable SIMD API<sup>3</sup> would provide many of them with a better alternative. Thus, SIMD types in C++ would capture existing practice.

<sup>2</sup> One could argue that target-specific intrinsics or builtins should be considered as the low-level interface. I believe this is the wrong approach, since the programming language should only provide abstractions for all the machines it may be compiled for and not concrete, target-specific interfaces.

<sup>3</sup> Application Programming Interface

3.4

### PREVIOUS WORK ON SIMD TYPES

## 3.4.1 INTEL C++ CLASS INTERFACE TO SSE

Intel has provided simple C++ wrapper classes with the Intel C++ Compiler. These classes use operator overloading to make intrinsics more convenient to use from C++. However, these classes have stopped short from becoming a more generic solution for data-parallel programming. The types are directly tied to a specific SIMD register width. Therefore, these types can only be used for compatible targets. Code written with these types does not scale to newer hardware, even if it is a compatible target. Access to scalar entries in a SIMD vector is provided, but breaks aliasing requirements, leading to subtle bugs.<sup>4</sup>

3.4.2 E.V.E.

The E.V.E. [21] library wraps the AltiVec instruction set of PowerPC CPUs. As the paper notes, it would be feasible to implement different target architectures, such as MMX/SSE2 and thus provide a portable API. The main emphasis was put on vectorization of calculations on larger data structures with more or less homogeneous treatment. The E.V.E. library built a basis for the NT<sup>2</sup> project [20], which now contains a more modern and more flexible SIMD abstraction called Boost.SIMD (Section 3.5.1).

3.4.3 MACSTL

Another library wrapping AltiVec exists, where MMX and SSE up to SSE3 were added later on, called macstl [62]. This library focuses on a main class for processing which is an improved STL<sup>5</sup> **valarray** implementation with vectorized operations on it. However, the flexibility for heterogeneous processing, required for the track finder, was missing. The library is not licensed as Free Software, and was thus unsuitable for the tracker.

### 3.4.4 KISEL/GORBUNOV'S HEADERS

The Kalman filter, the most compute-intensive part of the track finder, has previously been vectorized, which was presented in [33]. For this work, a small abstraction around SSE was developed. This work was evaluated and incorporated into the library presented here. In the mean time, this Kalman filter benchmark has been modified to use Vc, showing a slight improvement in performance [53].

<sup>4</sup> This is normally not a problem for projects compiled with ICC, since the compiler per default does not enforce strict-aliasing rules.

<sup>5</sup> Standard Template Library

Since its first public release of the Vc library in 2009 there have been several new projects to abstract SIMD types very similar to the basic idea discussed here. The main difference in the interface abstraction of Vc to the other libraries is that Vc abstracts data-parallel programming as independent from  $\mathcal{W}_{\mathbb{T}}$  as possible. The other libraries encode  $\mathcal{W}_{\mathbb{T}}$  in the type name or encode the target SIMD instruction set in the type name.

3.5.1 BOOST.SIMD

The Boost.SIMD library abstracts SIMD objects via the pack<T, N> class template [18, 17]. N may be omitted to compile for the native  $\mathcal{W}_{\mathbb{T}}$  of the target. This makes pack<T> almost equal to Vc::Vector<T> except for the ABI incompatibility issue of pack<T> discussed in Chapter 6. The Vc mask type is available in Boost.SIMD as pack<logical<T>, N>, thus tying the mask API to the value vector API, which I specifically chose differently for the design of Vc (Section 5.2). Compare operators of pack<T> return bool, instead of the mask type for Boost.SIMD, requiring predicate functions to do vectorized compares instead. The implementation of write-masking is not as generic as in the Vc API: Boost.SIMD provides the if\_else function that implements a vector blend and special functions like selinc and seldec to execute write-masked increment and decrement. The Vc API builds these expressions with standard C++ operators instead (Section 5.3).

In contrast to the Vc operators, Boost.SIMD uses expression templates with the operators for pack. This enables the library to do code transformations on longer expressions, such as fusing multiplications and additions/subtractions or reorder elementwise operations. Vc instead relies on the compiler optimizer to do these kind of optimizations, because expression templates can increase compile times significantly and make diagnostic output from ill-formed programs unreadable. Also from experience with Vc, a good optimizing compiler nowadays generates optimal machine code in almost all uses. The few remaining issues are solvable "missed-optimization" issues in the compiler. The important benefit of the Vc approach is that the vectorization quality does not depend on how many temporary values are captured in variables, which is a major "gotcha" with expression-template solutions.

<sup>6</sup> Vc also encodes the SIMD instruction set in the type name, but it is an internal type name. The user-visible types are target-agnostic.

<sup>7</sup> Boost.SIMD is not in boost yet. This is the intention of the developers, though.

3.5.2 OTHER LIBRARIES

The VCL Library [25] and the Generic SIMD Library [83] are two more implementations of C++ wrapper libraries around SIMD intrinsics. They are competing implementations for the ideas presented here and in earlier publications such as Kretz [55] and Kretz et al. [59].

# Part II

Vc: A C++ Library for Explicit Vectorization

### A DATA-PARALLEL TYPE

Programs must be written for people to read, and only incidentally for machines to execute.

— Harold Abelson et al. (1996)

The SIMD vector class shall be an abstraction for the expression of data-parallel operations (cf. Section 3.1). If the target architecture of a compilation unit does not support SIMD instructions, but similar data-parallel execution, the expressed data-parallelism shall be translated accordingly. The following list states the desired properties for such a type:

- The value of an object of Vector<T> consists of  $W_T$  scalar values of type T.

- The size of and align of Vector <T > objects is target-dependent.

- Scalar entries of a SIMD vector can be accessed via lvalue reference.

- The number of scalar entries  $(W_T)$  is accessible as a constant expression.

- Operators that can be applied to T can be applied to Vector<T> with the same semantics per entry of the vector. (With exceptions, if type conversions are involved. See below.)

- The result of each scalar value of an operation on Vector<T> does not depend on  $\mathcal{W}_{\mathbb{T}}$ .

- The syntax and semantics of the fundamental arithmetic types translate directly to the Vector<T> types. There is an additional constraint for implicit type conversions, though: Vector<T> does not implicitly convert to Vector<U> if W<sub>T</sub> ≠ W<sub>U</sub> for any conceivable target system.

<sup>1</sup> Obviously the number of scalar operations executed depends on  $\mathcal{W}_{\mathbb{T}}$ . However, the resulting value of each scalar operation that is part of the operation on Vector<T> is independent.

```

namespace Vc {

namespace target_dependent {

2

template <typename T> class Vector {

implementation_defined data;

4

public:

6

typedef implementation_defined VectorType;

typedef T EntryType;

8

typedef implementation_defined EntryReference;

typedef Mask<T> MaskType;

10

11

static constexpr size_t MemoryAlignment = implementation_defined;

12

13

static constexpr size_t size() { return implementation_defined; }

14

static Vector IndexesFromZero();

15

// ... (see the following Listings)

};

17

template <typename T> constexpr size_t Vector<T>::MemoryAlignment;

19

typedef Vector<

float > float_v;

typedef Vector< float> float_v;

typedef Vector< double> double_v;

typedef Vector< signed int> int_v;

typedef Vector<unsigned int> uint_v;

21

2.3

typedef Vector< signed short> short_v;

typedef Vector<unsigned short> ushort_v;

2.5

} // namespace target_dependent

} // namespace Vc

```

Listing 4.1: Template class definition for <code>Vector<T></code>. A concrete implementation for SSE2 could call the inner namespace <code>SSE</code>, use the intrinsic types <code>\_\_m128</code>, <code>\_\_m128d</code>, and <code>\_\_m128i</code> for <code>VectorType</code>, a union for the data member, <code>T</code> & for <code>EntryReference</code>,  $\frac{\mathcal{S}_{\text{VectorType}}}{\mathcal{S}_{\text{T}}}$  for <code>size()</code>, and  $\mathcal{S}_{\text{VectorType}}$  for <code>MemoryAlignment</code>.

• The compiler is able to identify optimization opportunities and may apply constant propagation, dead code elimination, common subexpression elimination, and all other optimization passes that equally apply to scalar operations.<sup>2</sup>

### 4.1 THE VECTOR<T> CLASS TEMPLATE

The boilerplate of the SIMD vector class interface is shown in Listing 4.1. There are several places in this listing where the declaration says "target-dependent" or "implementation-defined". All of the following listings, which declare functions of the Vector<T> class (to insert on line 16), do not require any further implementation-specific differences. All these differences in Vector<T> are fully captured by the code shown in Listing 4.1.

<sup>2</sup> In practice, there are still a few opportunities for compilers to improve optimization of SIMD operations.

The only data member of the vector class is of an implementation-defined type (line 4). This member therefore determines the size and alignment of Vector<T>. Therefore, the SIMD classes may not contain virtual functions. Otherwise, a virtual table were required and thus objects of this type would be considerably larger (larger by the minimum of the pointer size and the alignment of VectorType).

4.1.1 MEMBER TYPES

The member types of Vector<T> abstract possible differences between implementations and ease generic code for the SIMD vector types.

### VectorType

(line 7) is the internal type for implementing the vector class. This type could be an intrinsic or builtin type. The exact type that will be used here depends on the compiler and compiler flags, which determine the target instruction set. Additionally, if an intrinsic type is used it might not be used directly (on line 4) but indirectly via a wrapper class that implements compiler-specific methods to access scalar entries of the vector.

The **VectorType** type allows users to build target- and implementation-specific extensions on top of the predefined functionality. This requires a function that returns an Ivalue reference to the internal data (line 4). See Section 4.10 for such functions.

### EntryType

(line 8) is always an alias for the template parameter **T**. It is the logical type of the scalar entries in the SIMD vector. The actual bit-representation in the SIMD vector register may be different to **EntryType**, as long as the observable behavior of the scalar entries in the object follows the same semantics.

#### EntryReference

(line 9) is the type returned from the non-const subscript operator. This type should be an Ivalue reference to one scalar entry of the SIMD vector. It is not required for EntryReference to be the same as EntryType &. Consider an implementation that uses 32-bit integer SIMD registers for Vector<short>, even though a short uses only 16 bits on the same target. Then EntryReference has to be an Ivalue reference to int. If EntryReference were declared as short & then sign extension to the upper 16 bits would not work correctly on assignment.

#### MaskType

(line 10) is the mask type that is analogous to bool for scalar types. The type is

used in functions that have masked overloads and as the return type of compare operators. A detailed discussion of the class for this type is presented in Chapter 5.

4.1.2 CONSTANTS

SIZE() The vector class provides a static member function (SiZe()) which identifies the number of scalar entries in the SIMD vector (line 13). This value is determined by the target architecture and therefore known at compile time. By declaring the SiZe() variable constexpr, the value is usable in contexts where constant expressions are required. This enables template specialization on the number of SIMD vector entries in user code. Also it enables the compiler to optimize generic code that depends on the SIMD vector size more effectively. The siZe() function additionally makes Vector<T> implement the standard container interface, and thus increases the reusability in generic code.<sup>3</sup>

MemoryAlignment The MemoryAlignment static data member defines the alignment requirement for a pointer passed to an aligned load or store function call of Vector<T>. The need for a MemoryAlignment static data member might be surprising at first. In most cases the alignment of Vector<T> will be equal to MemoryAlignment. However, as discussed in Section 4.1.1, implementations are free to use a SIMD register with different representation of the scalar entries than EntryType. In such a case, the alignment requirements for Vector<T> will be higher than  $W_T \times S_T$  for an aligned load or store. Note that the load and store functions allow converting loads (Section 4.3.1). These functions need a pointer to memory of a type different than EntryType. Subsequently the alignment requirements for these pointers can be different. Starting with C++14 it may therefore be a good idea to declare MemoryAlignment as:

```

template <typename U>

static constexpr size_t MemoryAlignment = implementation_defined;

```

INDEXESFROMZERO() The IndexesFromZero() function (line 14) returns a Vector<T> object where the entries are initialized to the successive values {0, 1, 2, 3, 4, ...}. This constant is useful in many situations where the different SIMD lanes need to access different offsets in memory or to generate an arbitrary uniform offset vector with just a single multiplication.

<sup>3</sup> It would suffice to define only the <code>size()</code> function and drop <code>size()</code>. Personally, I prefer to not use function calls in constant expressions. Additionally, a 50% difference in the number of characters makes <code>size()</code> preferable because it is such a basic part of using SIMD types.

4.1.3 NAMESPACE

Line 2 defines a namespace that is not part of the standard interface. A user should be able to access the natural SIMD registers and operations via the Vector<T> type and its typedefs float\_v, double\_v, .... However, consider the case of compiling two translation units with different target compiler flags. In that case Vector<T> could map to different SIMD widths even though they had the same type. Thus, the code would compile, link, and possibly even run—but not correctly—. The namespace turns the Vector<T> types into different symbols and thus ensures correct linkage of different translation units. An implementation may choose to document the target-dependent namespaces, as discussed in Section 4.9.2.

4.1.4 SIMD TYPE ALIASES

The code on lines 20–25 declares handy aliases for the Vector<T> class template. The intent of these aliases is to make SIMD vector code more concise and recognizable.

There is a design decision here: whether to use the types char, short, int, long, and long long or the int8\_t, int16\_t, int32\_t, and int64\_t typedefs. The problem with the latter list is that these types are optional. Thus, the definition of int32\_v (= Vector<int32\_t>) is optional, too. Since the intN\_t typedefs must map to one of the fundamental types in the first list of types, definition of the SIMD Types with the fundamental types of the first list is more general.

It is a sensible choice to additionally declare typedefs for  $intN_v$  in the presence of  $intN_t$  typedefs.

## 4.2 SIMD VECTOR INITIALIZATION

The interface for initialization (excluding loads (covered in Section 4.3) and gathers (covered in Section 4.8)) is shown in Listing 4.2. The Vc vector types are not POD<sup>4</sup> types because the class interface needs full control over the implicit and explicit initialization methods (and because there is no guarantee about the POD-ness of VectorType). The decision for what constructors to implement follows from syntactical and semantical compatibility with the builtin arithmetic type EntryType. Thus, the expressions in Listing 4.3 must compile and behave analogous to the corresponding fundamental types.

<sup>4</sup> Plain Old Data

```

// init to zero

1

Vector();

2

// broadcast with implicit conversions

4

Vector(EntryType);

// disambiguate broadcast of 0 and load constructor

Vector(int); // must match exactly

8

// implicit conversion from compatible Vector<T>

10

template <typename U>

11

requires ImplicitConversionAllowed<U, EntryType>()

12

Vector(Vector<U>);

13

14