-

-

Notifications

You must be signed in to change notification settings - Fork 41

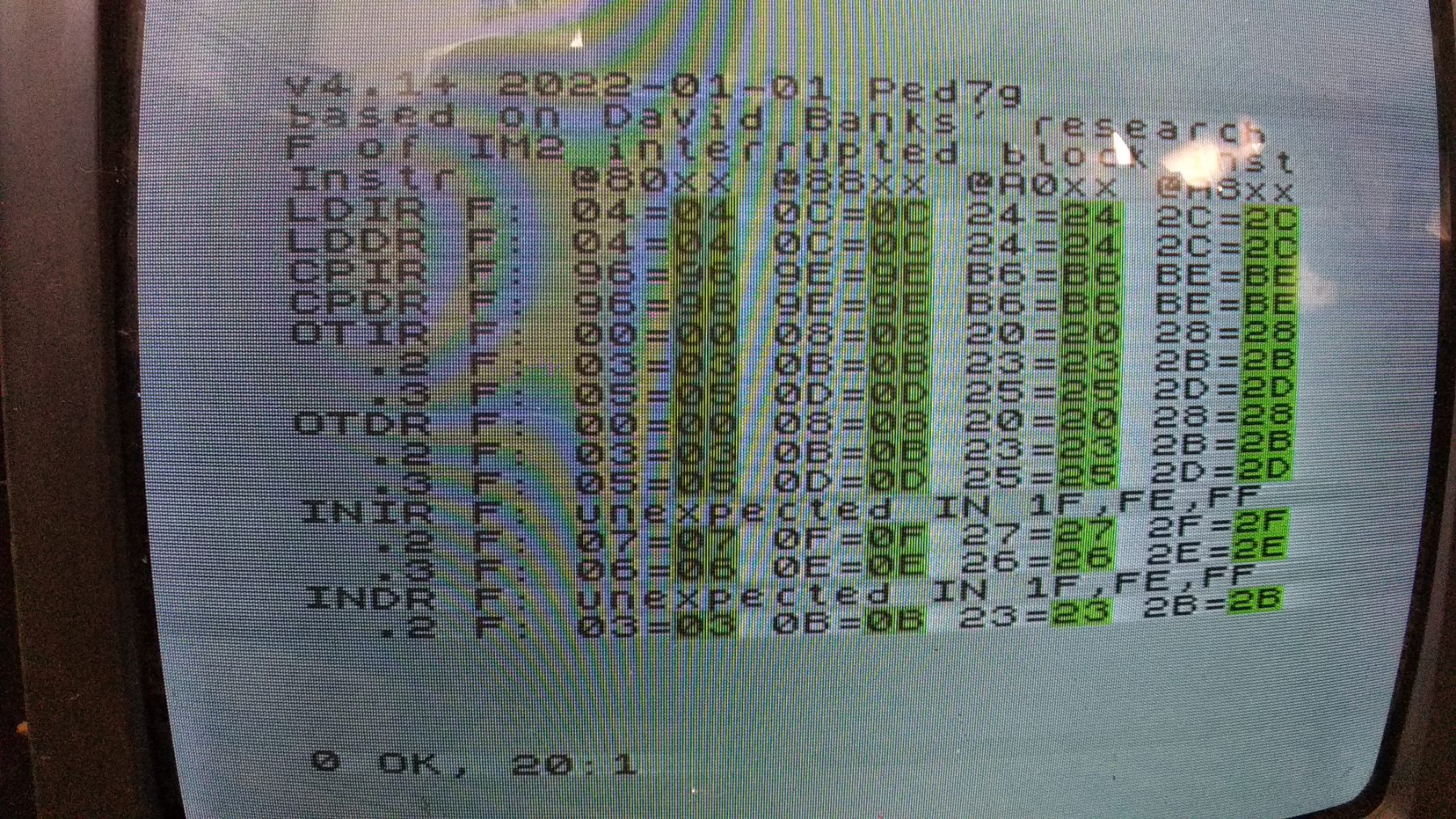

Z80 Block Flags Test

Platform: ZX Spectrum

Author: Helcmanovsky, Peter

License: MIT

Links: GitHub

| Version | Release date | Links | Download |

|---|---|---|---|

| v5.0 | 2022-02-17 | GitHub commit | tar.xz (hosted) - zip (GitHub) |

| v5.0 | 2022-01-11 | GitHub commit | tar.xz (hosted) - zip (GitHub) |

| v5.0-beta | 2022-01-11 | Discord post | tap (hosted) - tap (Discord post) |

| v4.1+2 | 2022-01-09 | Discord post | tap (hosted) - tap (Discord post) |

| v4.1+1 | 2022-01-06 | GitHub commit | tar.xz (hosted) - zip (GitHub) |

| v4.1+ | 2022-01-06 | GitHub commit | tar.xz (hosted) - zip (GitHub) |

| v4.1 | 2022-01-03 | GitHub commit | tar.xz (hosted) - zip (GitHub) |

| v4.0 | 2022-01-01 | Discord post | tap, asm (hosted) - tap, asm (Discord post) |

| v3.0+ | 2022-01-01 | Discord post | tap (hosted) - tap (Discord post) |

| v3.0 | 2021-12-31 | Discord post 1, Discord post 2 | tap, sna, asm (hosted) - tap, sna, asm (Discord post) |

| v2.0+2 | 2021-12-31 | Discord post | tap (hosted) - tap (Discord post) |

| v2.0+1 | 2021-12-31 | Discord post | tap (hosted) - tap (Discord post) |

| v2.0+ | 2021-12-31 | Discord post | tap (hosted) - tap (Discord post) |

| v2.0 | 2021-12-30 | Discord post | tap, asm (hosted) - tap, asm (Discord post) |

| v2.0-beta.1 | 2021-12-30 | Discord post | tap (hosted) - tap (Discord post) |

| v2.0-beta | 2021-12-30 | Discord post | tap (hosted) - tap (Discord post) |

| v1.0 | 2021-12-27 | Discord post | tap, asm (hosted) - tap, asm (Discord post) |

| alpha | 2021-12-27 | Discord post | tap, asm (hosted) - tap, asm (Discord post) |

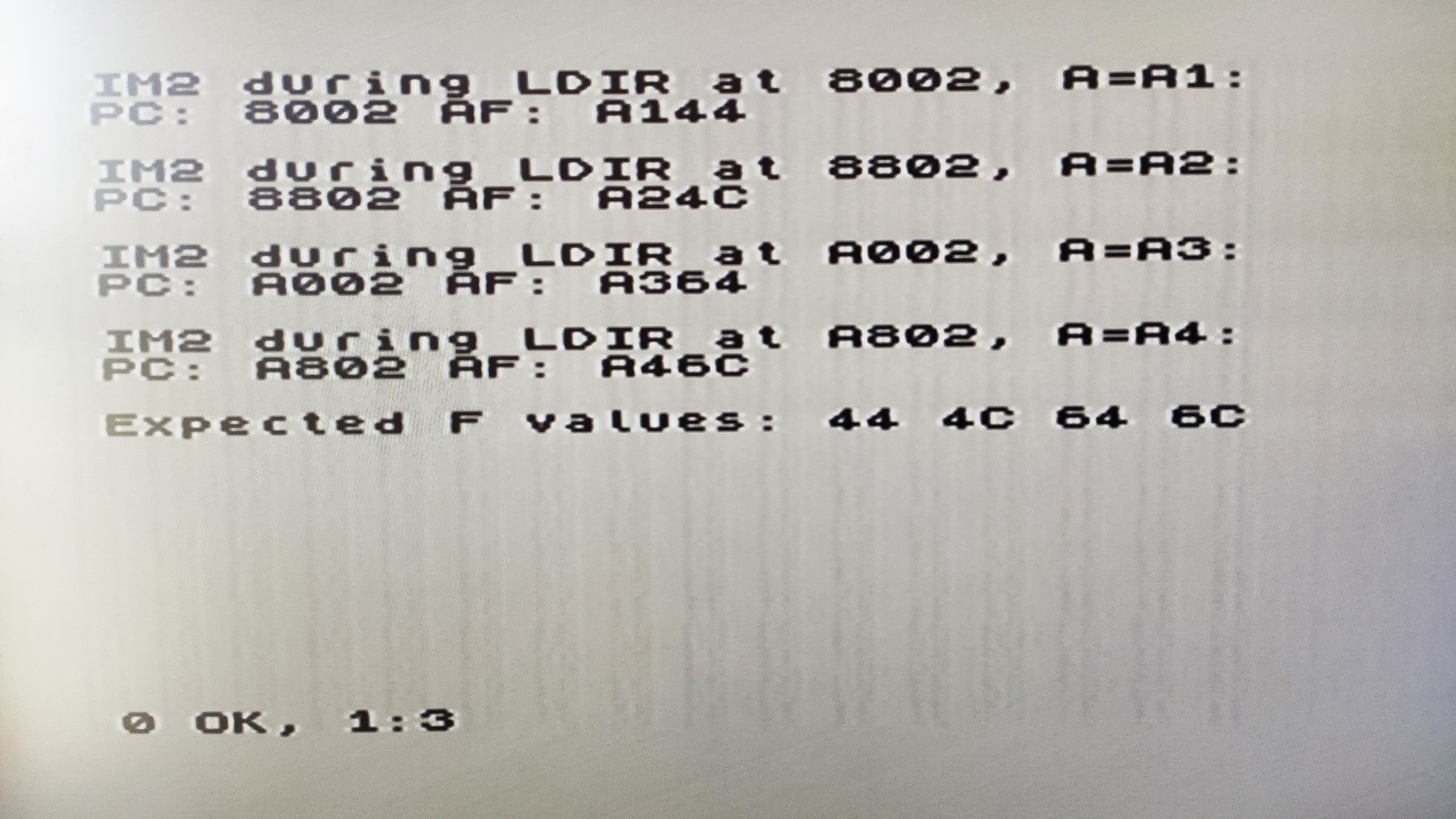

This test checks the flags after executing block instructions, when those instructions are repeated and interrupted before counter will reach zero.

The test is using IM2 interrupt to check the state of F register during the block instruction loop, and it is using commonly available ZX I/O ports for keyboard (FEh) (expecting values with b7=1), Kempston joystick (1Fh) (expecting values with b7=0) and "floating bus" (FFh) (expecting value FFh around interrupt processing).

Expected behaviour: These rules apply only in case the block instruction was already executed at least once, the counter is non-zero (the CPU plans to execute the same instruction again) and instead the interrupt is serviced, so PC points back at the EDh byte of the block instruction and flags are set by the extra machine cycle servicing the repeating of instruction and reverting PC back. After return from interrupt handler the block instruction will resume and continue until counter is zero.

In such case, ldXr and cpXr instruction have flags set as ldX/cpX, but bit 5 (YF) is equal to PC.13 and bit 3 (XF) is equal to PC.11.

inXr/otXr do also modify YF/XF with PC.13/PC.11, but also further modify PF and HF (on top of the flag modifications caused already by the inX/outX sub-instruction-part already executed), see source code with larger comment describing calculation of PF/HF in such case.

It's possible the behaviour will be different for different Z80 clones or technology used, like CMOS Z80.

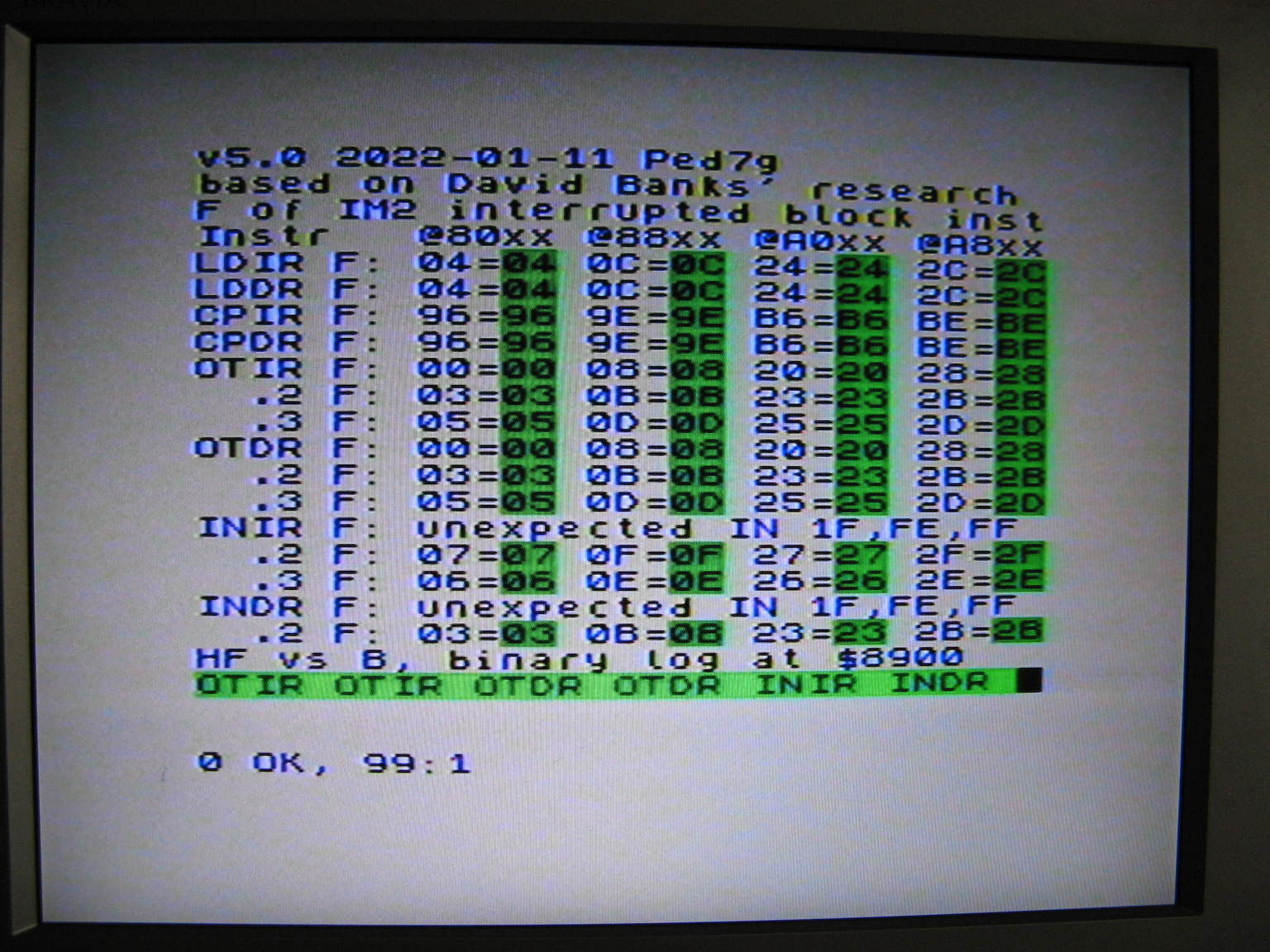

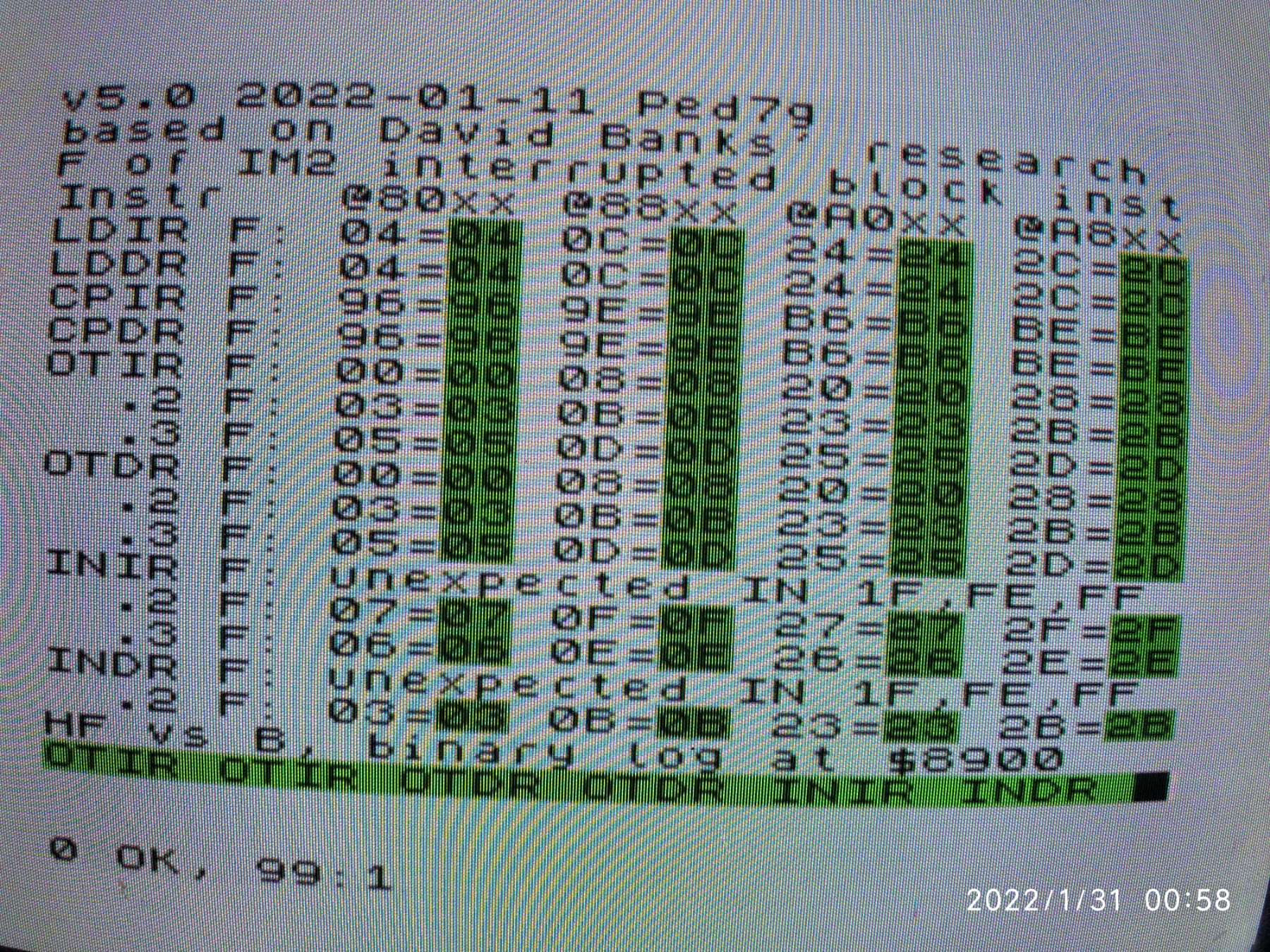

| v5.0 | v5.0-beta |

|

|

| v4.1+2 | v4.1+1 |

|

|

| v4.1+ | v4.1 |

|

|

| v4.0 | v3.0+ |

|

|

| v3.0 | v2.0+2 |

|

|

| v2.0+1 | v2.0+ |

|

|

| v2.0 | v2.0-beta.1 |

|

|

| v2.0-beta | v1.0 |

|

|

| alpha | |

|

Tested by Ricardo Martínez Cantero

Tested by Ricardo Martínez Cantero

The erroneous values are possibly due to the CPU being in turbo mode.

With Kempston Joistick Interface attached:

Without Kempston Joistick Interface attached:

Copyright © Manuel Sainz de Baranda y Goñi, Tony Brewer and Peter Helcmanovsky

Published under the terms of the GNU Free Documentation License v1.3