MIL-STD-1862B 3 January 1983 SUPERSEDING MIL-STD-1862A 2 November 1981

# **MILITARY STANDARD**

# Nebula Instruction Set Architecture

**FSC IPSC**

# **Table of Contents**

| 1. SCOPE AND PURPOSE 1.1. Scope                                          |   | 1 1.     |

|--------------------------------------------------------------------------|---|----------|

| 1.2. Purpose                                                             |   | 1        |

| 2. REFERENCED DOCUMENTS                                                  |   | 2        |

| 2.1. Issue of document                                                   |   | 2        |

| 3. DEFINITIONS 3.1. Assembler Notation Conventions                       |   | 3<br>4   |

| 4. OVERVIEW                                                              |   | 5        |

| 4.1. Memory Organization                                                 |   | 5        |

| 4.2. Instruction Format                                                  |   | 5        |

| 4.3. Control Structure                                                   |   | 5        |

| 4.4. Addressing                                                          |   | 6        |

| 4.5. Data Types                                                          | • | 6        |

| 5. OPERAND ADDRESSING MODES                                              |   | 7        |

| 5.1. Maximum Accessible Register                                         |   | 7        |

| 5.2. Compound Modes                                                      |   | 7<br>8   |

| 5.3. Address Operands                                                    |   | 9        |

| 5.4. Register Mode                                                       |   | 9        |

| 5.5. Short Literal Mode                                                  |   | 10       |

| <ul><li>5.6. Literal Mode</li><li>5.7. Memory Addressing Modes</li></ul> |   | 10       |

| 5.7.1. Indirect Register Mode                                            |   | 11       |

| 5.7.2. Register Indexed Modes                                            |   | 12       |

| 5.7.3. Absolute Mode                                                     |   | 13       |

| 5.8. Parameter Addressing Modes                                          |   | 14       |

| 5.8.1. Short Parameter Mode                                              |   | 14       |

| 5.8.2. Extended Parameter Mode                                           |   | 14       |

| 5.8.3. General Parameter Mode                                            |   | 15       |

| 5.9. Unscaled Index Mode                                                 |   | 16       |

| 5.10. Scaled Index Mode                                                  |   | 17       |

| 5.11. Reserved Specifiers ·                                              |   | 18<br>18 |

| 5.12. Undefined Operand Sizes                                            |   |          |

| 6. PROCESSOR STATUS WORD                                                 |   | 19       |

| 6.1. Kernel/Task Mode                                                    |   | 19       |

| 6.2. Last Mode                                                           |   | 19       |

| 6.3. Reserved Bits                                                       |   | 19       |

| 6.4. Priority                                                            |   | 19       |

| 6.5. Carry Condition Code                                                |   | 19<br>19 |

| C C I HUMANIA CANCIDAN COCA                                              |   |          |

| 6.7. Negative Condition Code                     |   | 20   |

|--------------------------------------------------|---|------|

| 6.8. Zero Condition Code                         |   | 20   |

| 6.9. Debugging Control                           |   | 20   |

| 6.10. Privilege                                  |   | .20  |

| 6.11. Base of Context                            |   | 20   |

| 6.12. Supervisor Mode                            |   | 20   |

| 6.13. Up/Down Level Exception Propagation (UDLE) | • | 20   |

| 6.14. Enable Arithmetic Error                    |   | 20   |

| 6.15. Maxreg Field                               |   | 20   |

| 6.16. Number of Parameters                       |   | 20   |

| 7. AUXILIARY STATUS REGISTER                     |   | 21   |

| 7.1. Soft Memory Error Enable                    |   | 21   |

| 7.2. Reserved Bits                               |   | 21   |

| 7.3. Floating Point Mode Control                 | • | 21   |

| 7.3.1. Infinity Control                          |   | 21   |

| 7.3.2. Exception Event and Mask Bits             |   | 21   |

| 7.3.3. Rounding Control                          |   | 21   |

| 8. PROCEDURE INTERFACE                           |   | 22   |

| 8.1. The Context Stacks                          |   | 22   |

| 8.1.1. Context Pointers                          |   | 22   |

| 8.1.2. Structure of Context Stacks               |   | 23   |

| 8.1.3. Cacheing of the Context Stack             |   | 24   |

| 8.1.4. Changing of Context Stack Pointers        |   | 24   |

| 8.1.5. Alignment of Context Pointers             |   | 24   |

| 8.2. Procedure Descriptor                        |   | 24   |

| 8.2.1. Fixed/Variable Number of Parameters       |   | 25   |

| 8.2.2. Reserved Bit                              | • | 25   |

| 8.2.3. Exception Propagation Control             |   | 25   |

| 8.2.4. Arithmetic Error Control                  |   | 25   |

| 8.2.5. Available Registers                       |   | 25   |

| 8.3. Procedure Invocation                        |   | 25   |

| 8.3.1. Determination of a New PSW                |   | 25   |

| 8.3.2. Register Set Allocation .                 |   | 26   |

| 8.3.3. Initialization of Exception Handler       |   | 26   |

| 8.3.4. Initialization of Parameter List          |   | 26   |

| 8.4. Parameter Lists                             |   | 26   |

| 8.4.1. Parameter Specification                   |   | 27   |

| 8.4.2. Parameter Access                          |   | 27   |

| 8.4.3. Example of Parameter Linkage              |   | 27   |

| 8.4.4. Mechanism of Parameter Addressing         |   | 29   |

| 8.5. Vectored Calls: SVC and OPEX                |   | 31   |

| 8.6. Vector Format                               |   | . 33 |

| 8.7. Return from Procedures                      |   | 33   |

| 9. EXCEPTIONS                                    |   | 34   |

| 9.1. Procedure Exception Handler                 |   | 34   |

| 9.2. Desinition of an Exception Handler          |   | 34   |

| 9.3. Raising an Exception                        |   | 34   |

| 9.4. Exception Handling 9.5. Supervisor Exception Handler |   | 35<br>37  |

|-----------------------------------------------------------|---|-----------|

| 10. DEBUGGING FACILITIES 10.1. Program Tracing            |   | 38<br>38  |

| 11. INTERRUPTS AND TRAPS                                  | • | . 39      |

| 11.1. Interrupt Priority                                  |   | 39        |

| 11.2. I/O Interrupts                                      |   | 39        |

| 11.3. Software Interrupt Requests                         |   | 39        |

| 11.4. Power Failure Interrupt                             |   | 39        |

| 11.5. Power Restore Interrupt                             |   | 40        |

| 11.6. Memory System Error Traps                           |   | 40        |

| 11.6.1. Hard Memory Errors                                |   | 40        |

| 11.6.2. Soft Memory Errors                                |   | 41        |

| 11.7. Privileged Instruction Trap                         | · | 41        |

| 11.8. Memory Management Traps                             |   | 41        |

| 11.8.1. Instruction Execution                             |   | 41        |

| †1.8.2. Task Context Stack                                |   | 41        |

| 11.8.3. Kernel Context Stack                              |   | 41        |

| 11.9. Reset and IPL                                       |   | 42        |

| 11.10. Built In Test Traps                                |   | 42        |

| 11.11. Simultaneous Events                                | • | 42        |

| 12. MEMORY MANAGEMENT SYSTEM                              |   | 43        |

| 12.1. Virtual Address Space                               |   | 43        |

| 12.2. Mapping of Virtual Addresses                        |   | 44        |

| 12.2.1. Map Pointer Registers                             |   | 44        |

| 12.2.2. Memory Map Structure                              |   | 44        |

| 12.2.3. Segment Association                               |   | 45        |

| 12.2.4. Relocation of Virtual Addresses                   |   | 46        |

| 12.2.5. Access Protection                                 |   | 47        |

| 12.2.5.1. Self-Modifying Code                             |   | 47        |

| 12.2.6. Crossing Segment Boundaries                       |   | 47        |

| 12.2.7. Protection of the Supervisor                      |   | 47        |

| 12.3. Implementation Considerations                       |   | 48        |

| 12.3.1. Cacheing of Memory Maps                           |   | 48        |

| 12.3.2. Aliasing of Physical Addresses                    |   | 48        |

| 12.4. Memory Management Traps                             |   | 48        |

| 12.5. I/O Space Selection                                 |   | 49        |

| 12.6. Subseting of Memory Management                      |   | 49        |

| 40 L/O CONTROLLEDO                                        |   | <b>FA</b> |

| 13. I/O CONTROLLERS                                       |   | 50<br>50  |

| 13.1. Channel Configuration Registers                     |   | 50        |

| 13.2. IOC Programs                                        |   | 50        |

| 13.2.1. Program Counter                                   |   | 51<br>51  |

| 13.2.2. Message Pointer Register 13.2.3. Accumulator      |   | 51<br>51  |

| ,                                                         |   | 51<br>51  |

| 10.2.4. Onaline Olatos                                    |   | 51<br>50  |

| 13.2.5. Channel Program Status                            |   | 52        |

| 13.3. Virtual Addressing                               |                                       | 52   |

|--------------------------------------------------------|---------------------------------------|------|

| 13.3.1. Segment Specifiers                             |                                       | 54   |

| 13.4. Physical Addressing                              |                                       | 54   |

| 13.5. Instruction Execution                            |                                       | 54   |

| 13.6. Operand Accessing                                | •                                     | 54   |

| 13.7. IOC Interrupts                                   | •                                     | - 54 |

| 13.7.1. IOC Error Interrupts                           | ·                                     | 55   |

| 13.8. IOC Instructions                                 |                                       | 55   |

| 13.8.1. IOC Instruction Descriptions                   |                                       | 55   |

| 13.8.2. Transfer Instructions                          |                                       | 55   |

| 13.8.3. Control Instructions                           |                                       | 59   |

| 13.8.4. Channel Specific Instructions                  | •                                     | 62   |

| 13.8.4.1. Parallel Point to Point Interface            | •                                     | 62   |

| 13.8.4.2. Serial Point to Point Interface              |                                       | 64   |

| 13.8.4.3. MIL-STD-1553 Serial Interface                |                                       | 64   |

| 13.8.4.3.1. MIL-STD-1553 RT Mode Specific Instructions | •                                     | 64   |

| 13.8.4.3.2. MIL-STD-1553 BC Mode Specific Instructions |                                       | 64   |

| 13.9. MIL-STD-1553B Remote Terminal Mode Operation     |                                       | 66   |

| 13.9.1. Message Pointer Register                       | •                                     | 66   |

| 13.9.2. Status Word                                    |                                       | 66   |

| 13.9.3. Vector Word                                    |                                       | 67   |

| 13.9.4. Transfer Commands                              |                                       | 67   |

| 13.9.5. Mode Commands                                  | •                                     | 67   |

| 13.9.6. RT Mode Interrupts                             |                                       | 68   |

| 13.10. Interrupt Vector Assignments                    | • • • • • • • • • • • • • • • • • • • | 68   |

| 13.11. IOC Control Register Assignments                |                                       | 69   |

| 4.4 TIMED OUDDODT                                      |                                       |      |

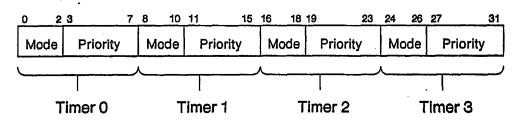

| 14. TIMER SUPPORT                                      |                                       | 70   |

| 14.1. Time of Day                                      |                                       | 70   |

| 14.2. Interval Timers                                  |                                       | 70   |

| 15. ASSIGNED PHYSICAL ADDRESSES                        |                                       | 71   |

| 15.1. Memory Space Assignments                         | •                                     | 71   |

| 15.2. I/O Space Assignments                            | ·                                     | 72   |

|                                                        |                                       | 12   |

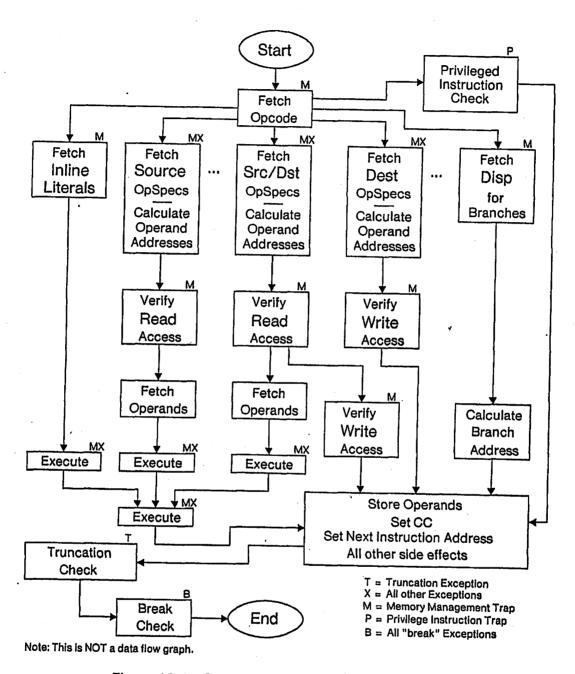

| 16. CONCEPTUAL MODEL OF INSTRUCTION EXECUTION          |                                       | 73   |

| 16.1. The Serial Model                                 |                                       | 73   |

| 16.2. Effects of Parallelism                           |                                       | 73   |

| 16.3. Instruction Fetch                                | •                                     | 75   |

| 16.4. Operand Address Calculation                      |                                       | 76   |

| 16.5. Operand Fetch                                    |                                       | 76   |

| 16.6. Instruction Execution                            |                                       | 76   |

| 16.7. Operand Storage                                  |                                       | 76   |

| 16.8. Memory Accesses                                  |                                       | 76   |

| 16.9. Interruptible Instructions                       |                                       | 77   |

| 16.10. Serialization                                   |                                       | 77   |

| 16.11. IOC Serialization                               |                                       | 77   |

| IZ INCTRUCTION DECORPTIONS                             |                                       |      |

| 17. INSTRUCTION DESCRIPTIONS                           |                                       | 78   |

| 17.1. General Information                              |                                       | 78   |

| <b>v</b>                                                   |   |                  |

|------------------------------------------------------------|---|------------------|

| 17.2. Operands                                             |   | 78               |

| 17.2.1. Signed Integers                                    |   | 78               |

| 17.2.2. Unsigned Integers                                  |   | 79<br>           |

| 17.2.3. Logicals 17.2.4. Floating Point                    |   | 79<br>79         |

| 17.2.5. Address Operands                                   |   | 79<br>79         |

| 17.3. Symbols and Functions                                |   | 79               |

| 18. INTEGER ARITHMETIC                                     |   | 80               |

| 18.1. Integer Data Types                                   |   | 80               |

| 18.2. Integer Arithmetic Instructions                      | • | 81               |

| 19. LOGICAL INSTRUCTIONS                                   |   | 95               |

| 20. SHIFT AND ROTATE INSTRUCTIONS                          | • | 98               |

| 21. MOVE AND CLEAR INSTRUCTIONS                            |   | 101              |

| 22. COMPARE AND TEST INSTRUCTIONS                          |   | 105              |

| 23. CONTROL INSTRUCTIONS                                   |   | 109              |

| 24. PROCEDURE CALL AND RETURN INSTRUCTIONS                 |   | 121              |

| 25. TASK CONTROL INSTRUCTIONS                              |   | 126              |

| 26. EXCEPTION HANDLING INSTRUCTIONS                        |   | 131              |

| 27. STRING INSTRUCTIONS                                    |   | 135              |

| 28. BIT FIELD INSTRUCTIONS                                 |   | 140              |

| 29. MISCELLANEOUS INSTRUCTIONS                             |   | 145              |

| 30. FLOATING-POINT ARITHMETIC                              |   | 155              |

| 30.1. Floating-Point Data Classes                          |   | 155              |

| 30.2. Floating-Point Formats 30.3. Floating-Point Operands |   | 155<br>156       |

| 30.4. Floating-Point Exceptions                            |   | 156              |

| 30.4.1. Invalid.Operation                                  |   | 157 ·            |

| 30.4.2. Divide.By.Zero                                     | • | 158              |

| 30.4.3. Floating.Overflow<br>30.4.4. Floating.Underflow    |   | 158<br>158       |

| 30.4.5. Floating:Inexact                                   |   | 158 <sup>-</sup> |

| 30.5. Rounding                                             |   | 158 <sup>*</sup> |

| 30.6. Infinity Arithmetic                                  |   | 159              |

| 30.7. Floating-Point Instructions                          |   | 159              |

| 31. OPCODE ALLOCATION 31.1. Unimplemented Opcodes          |   | 177<br>177       |

|                                                            |   |                  |

| 32. NOTES                                                  |   | 178              |

| ·<br>•                                                     | • | •                |

|                                                            |   |                  |

| •                                                          |   | •                |

|                                                            | • |                  |

32.1. Prime Item Specification considerations 32.2. Implementation dependencies

178 179

# List of Figures

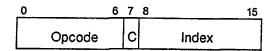

| Figure 4-1: Instruction Format                         | 5    |

|--------------------------------------------------------|------|

| Figure 4-2: Integer Data Types                         | 6    |

| Figure 4-3: Floating Point Data Types                  | 6    |

| Figure 5-1: Operand Specifiers                         | 8    |

| Figure 6-1: Processor Status Word                      | 19   |

| Figure 7-1: Auxiliary Status Register                  | 21   |

| Figure 8-1: Stacked Procedure Contexts                 | 23   |

| Figure 8-2: Procedure Descriptor                       | 24   |

| Figure 8-3: Example of a Call Context                  | 28   |

| Figure 8-4: Normal Operand Processing                  | 29   |

| Figure 8-5: Parameter List Operand Processing          | 30   |

| Figure 8-6: Parameter Access                           | 30   |

| Figure 8-7: SVC and OPEX Vector Registers              | 31   |

| Figure 8-8: Vectored Call Address Calculation          | 32   |

| Figure 8-9: Vector Format                              | 33   |

| Figure 9-1: States of an Exception Handler             | 34   |

| Figure 9-2: Transfer to an Exception Handler           | 36   |

| Figure 12-1: Map Data Structure                        | 43   |

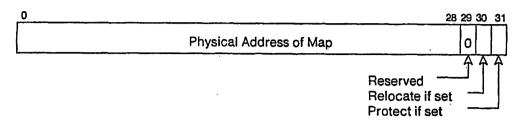

| Figure 12-2: Memory Map Pointer Registers              | 45   |

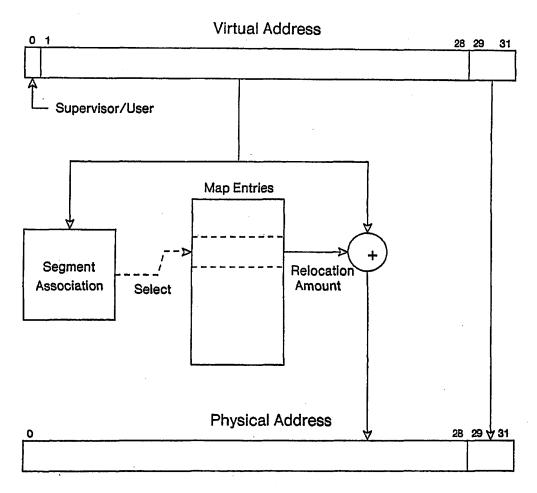

| Figure 12-3: Map Entry Format                          | 45   |

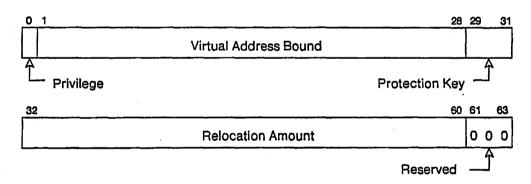

| Figure 12-4: Address Relocation                        | : 46 |

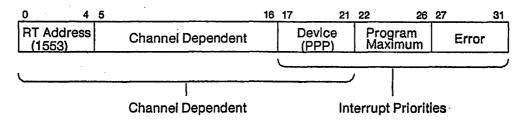

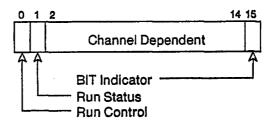

| Figure 13-1: Channel Configuration Register            | -50  |

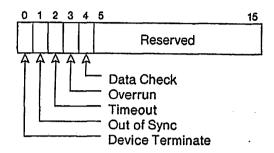

| Figure 13-2: Channel Status Register                   | 51   |

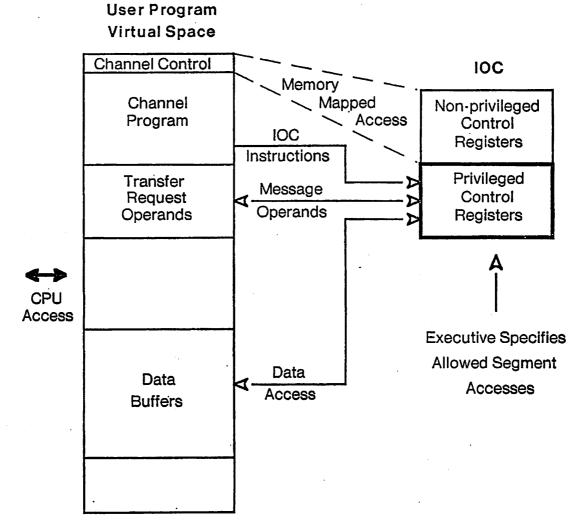

| Figure 13-3: Channel Program Status                    | 52   |

| Figure 13-4: IOC Virtual Addressing                    | 53   |

| Figure 14-1: Timer Control Register                    | 70   |

| Figure 16-1: Conceptual model of instruction execution | 74   |

| Figure 30-1: Floating Point Number Representation      | 156  |

| Figure 30-2: Floating Point Control Bits in ASR        | 157  |

| Figure 30-3: The Compare Operation                     | 171  |

## 1. Scope and Purpose

- 1.1. Scope. This standard defines the Nebula Instruction Set Architecture. The instruction set architecture includes all information required by a programmer in order to write any time independent program that will execute on computers conforming to this standard. This standard does not define any specific implementation details of a computer.

- 1.2. Purpose. The purpose of this document is to define the Nebula Architecture, independent of any specific implementation or vendor, with sufficient precision to permit independent implementations of this architecture that execute identical programs in the identical manner.

# 2. Referenced Documents

2.1. Issue of document. The following document, of the issue in effect on date of invitation for bid or request for proposal, forms a part of the standard to the extent specified herein. In the event of conflict between the documents referenced herein and the contents of this standard, the contents of this standard shall be considered a superseding requirement.

### Standard

### Military

MIL-STD-1553 - Aircraft Internal Time Division Command/Response Multiplex Data Bus

### 3. Definitions

. The following terms are used in this document:

### Cacheing

The term cacheing is used to refer to a variety of implementation techniques for enhancing performance by maintaining the active copy of some quantity in a place other than its assigned storage. The technique invoked may be as simple as the loading and storing of a register (file) or as complex as an associative memory

### Implementation Dependent

The behavior of an action or feature described as implementation dependent is not defined by this document. The actual behavior seen by the programmer is dependent on the hardware he is using. This behavior will differ between machines.

### Interruptible

An instruction designated as interruptible shall be restartable from the point of interruption.

### Reserved

The use of reserved as a modifier indicates that the entity described is set aside for future definition. Unless otherwise specified, responsibility for definition of a reserved entity lies with the Nebula Control Board (NCB). Any assumptions about the behavior of such entities by anyone other than those responsible for the definition of the entity is forbidden.

### Reserved (value)

A reserved value is a bit pattern that, when written into a particular bit field, will cause unpredictable results. The use of such values by the software is forbidden.

Reserved (bit field) A reserved bit field is a sequence of bits that may produce a Specification. Error exception or unpredictable actions if setto a value other than zero. Reserved bits or reserved bit fields yield undefined results if read.

### Undefined

An undefined result may produce arbitrary bit patterns in all fields that it was specified as modifying.

### Unpredictable

An unpredictable action may produce any change in the state of the machine that is consistent with the rights of the program that caused it. For example, an unpredictable operation performed by a user task may destroy any of the locations it can access normally, but shall not destroy any state protected by the protection mechanisms. This restriction may be breached by a supervisor that gives a user access to critical memory or functions. For this reason, access to the CPU registers in the I/O space should be controlled by means of the memory management system. It should be noted that while the programmer cannot rely on any properties of an unpredictable action, it is considered desirable to make such actions as innocuous as is practical.

3.1. Assembler Notation Conventions. The notation used in example instructions in this document is a subset of the Nebula assembly language. A synopsis of the notation used is included below.

### **Types**

Register numbers and parameter numbers are distinguished by prefix type specifiers. A number preceded by a % character is interpreted as a register number; a number preceded by a ? Is interpreted as a parameter number. Examples:

%4 ;register 4

?3 ;parameter 3

### **Instruction Operands**

Instruction operands are specified as a sequence of mode specifiers separated by commas. The syntax used to specify each mode is described below. Words enclosed in {} describe the contents of the field; the {} is not part of the assembler notation.

| Syntax             | Example | Addressing Mode             |

|--------------------|---------|-----------------------------|

| %{number}          | %3      | Register                    |

| # {value}          | # 52    | Short Literal or Literal    |

| @%{number}         | @%4     | Indirect Register           |

| {index}(%{number}) | 16(%2)  | Register Indexed            |

| @({address})       | @(64)   | Absolute Address            |

| ?{number}          | ?4      | Short or Extended Parameter |

| ?({simple mode})   | ?(%4)   | General Parameter           |

| {base}({index})    | @%3(%4) | Unscaled Index              |

| {base}[{index}]    | @%3[%4] | Scaled Index                |

### Size Specifiers

Operands that address memory must also select the size of the data item referenced. Sizes are specified by following the mode specifier by a postfix size specifier. These specifiers are listed below:

↑B Byte

↑H Halfword

↑W Word

↑D Double Word

### 4. Overview

The Nebula architecture is a 32 bit general register architecture. Some of the characteristics of the architecture are:

- Variable length instructions with variable numbers of operands.

- Explicit addressing of all instruction operands.

- Multiple addressing modes for register, literal, memory and parameter access.

- Procedure based control structure with a local register set for each procedure.

- Support for several data types and representation lengths.

- Memory mapped I/O control.

- Vectored Interrupts and Exceptions.

- 4.1. Memory Organization. Main memory is byte addressable. The architecture provides for a virtual address space of 2<sup>32</sup> 8-bit bytes. Bits are numbered from left to right; memory words are addressed by the address of their most significant byte with the following address locations (increasing addresses) containing the less significant bytes. Multi-byte data (halfwords, words, doublewords) may be aligned on arbitrary byte boundaries, although performance improvements may be expected with aligned data. The first 2<sup>20</sup> bytes of the physical address space are called I/O space. These addresses are used to access device and channel control registers.

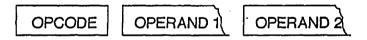

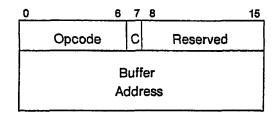

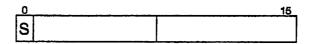

- **4.2.** Instruction Format. Instructions are specified by a one byte opcode followed either by a list of operand specifiers or by a signed displacement. Each of these operand specifiers allows fully general addressing of the operand. The number of operand specifiers used by an instruction is determined solely by the nature of the operation it performs. No arbitrary restrictions are placed on the number of operands an instruction can address.

Figure 4-1: Instruction Format

4.3. Control Structure. The architecture provides a high level procedure based control structure. Procedures may be invoked by various types of calls, interrupts, traps, or as independent tasks. The procedure mechanism automatically provides for the passing of parameters and the maintenance of control linkages. Each procedure is provided with its own register set of up to 15 general registers for local use. The protection provided by the procedure structure allows privileged code to communicate with non-privileged code in a meaningful way.

- **4.4.** Addressing. Addresses are calculated using 32-bit 2's complement arithmetic. Overflow in these calculations is ignored. Instructions can specify addresses using short displacements from registers or the instruction address. For address calculations, these short displacements are sign or zero extended as specified in the appropriate sections of the standard.

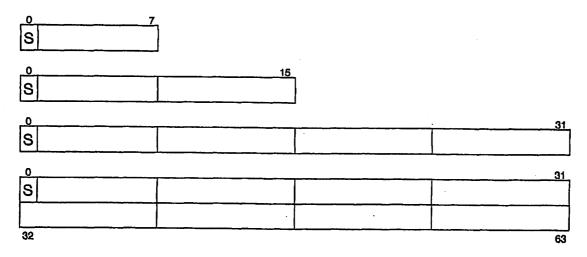

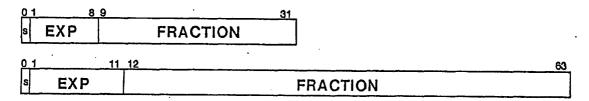

- 4.5. Data Types. The architecture provides support for integer, logical, and floating data types with multiple size representations for each. Integers are fully supported in 8, 16, and 32-bit lengths and some extended precision support is provided for 64-bit lengths. Integers are represented in 2's complement notation.

Figure 4-2: Integer Data Types

Logical quantities are supported in 1, 8, 16, 32, and 64-bit lengths. These data types may be used interchangeably as unsigned integers and bit patterns. The ability to access signed and unsigned bit fields is also provided.

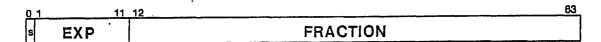

Floating point numbers are provided in single (32-bit) and double (64-bit) length representations.

Figure 4-3: Floating Point Data Types

Conversion between integer and floating point representations is provided. Conversion between different lengths is provided implicitly; no conversion instructions are necessary.

## 5. Operand Addressing Modes

Operands are identified by the instructions through the decoding of multi-byte strings called operand specifiers. Operand specifiers contain the information needed to determine the location and the size of the operands to be accessed.

The location of each operand is fully general and may be:

- a literal constant in the code stream

- a register

- a memory location

The operand specifier selects the size of the operand from the supported primitive data types:

- 8-bit integer/logical

- 16-bit integer/logical

- 32-bit integer/logical

- 64-bit integer/logical

- 32-bit floating point

- 64-bit floating point

The overall structure of the Nebula architecture places a design restriction on the operand specifiers. The location (address) of all operands must be computable in the absence of any context information provided by the opcode. This permits operands to be "pre-evaluated" in the absence of such information as required by the procedure interface. Addressing modes are also required to be free of side effects. This eliminates any order dependencies in operand evaluation.

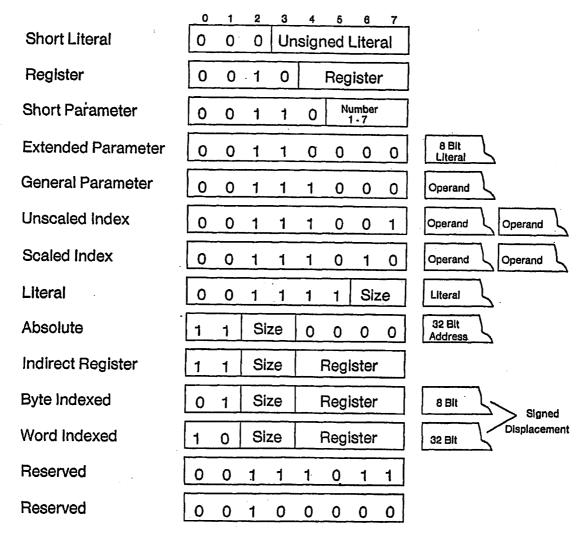

An overview of the addressing modes is shown in figure 5.

- 5.1. Maximum Accessible Register. Several of the addressing modes specify a four bit register field. This field is checked against the *Maxreg* field of the Processor Status Word to insure that the specified register is available in the current context. If the specified register number is greater than Maxreg, an Illegal. Register exception shall be initiated.

- 5.2. Compound Modes. Three addressing modes, General Parameter, Unscaled Index, and Scaled Index, use other operand specifiers as a "subpart" of their complete operand specification. These are referred to as compound modes. The subpart operand specifiers (that form a part of the full compound mode specifier) shall be restricted to non-compound modes. For example, as part of its specification the unscaled index mode calls for two other operands to be specified and used as part of the calculation of the unscaled indexed operand. These two subpart operands cannot be unscaled index or either of the other two compound operands. If a compound type operand is encountered when a subpart operand is being decoded, an Illegal.Mode exception shall be initiated.

Figure 5-1: Operand Specifiers

5.3. Address Operands. Addressing modes that have their operands in memory may be used as address operands. When an instruction calls for an address operand, the operand specifier is evaluated until the address of the operand is obtained. That address is returned to the instruction rather than the value of the operand. If an operand specifier whose operand is NOT in memory (for example, register mode) is specified as an address operand, an Illegal.Address exception shall be initiated. The size field of an address type operand specifier is ignored unless otherwise specified by the individual instruction description.

5.4. Register Mode. In register mode the operand is located in the register (1 to 15) specified by the second half (bits 4:7) of the operand specifier byte. Register operands shall be word (32-bit) size and therefore require no size field specification. The Maxreg restriction applies to register mode.

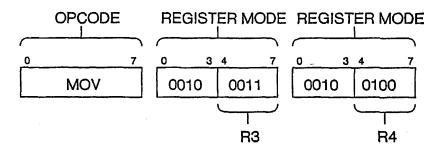

EXAMPLE: MOV %3, %4

In this example, the contents of register 3 are copied into register 4.

5.5. Short Literal Mode. In order to facilitate the use of short literals, a single byte specifier allowing unsigned literals of up to 5 bits is provided. Bits 3:7 of the specifier byte form the short literal. This short literal (0 - 31 decimal) is zero extended internally to the size necessary for further computation. An attempt to write into a short literal mode operand shall generate an Illegal.Write exception.

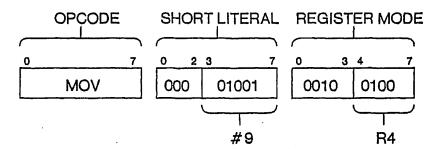

EXAMPLE: MOV #9, %4

The literal 9 (encoded in the lower part of the short literal specifier) is zero extended and placed in register 4.

- 5.6. Literal Mode. When a literal that is negative or too large for short literal mode (larger than 31) must be specified, Literal Mode may be used. Literal mode addressing allows the specification of literals that are one, two, four, or eight bytes long. The literal follows the first specifier byte in the code stream. Bits 6:7 of the first specifier byte contain the encoded size of the literal. The encoding is:

- 00 Byte (8 bits)

- 01 Halfword (2 bytes, 16 bits)

- 10 Word (4 bytes, 32 bits)

- 11 Double word (8 bytes, 64 bits)

Once the literal is fetched, it may be extended internally, based on the requirements of the operation. An attempt to write into a literal mode operand shall generate an Illegal. Write exception:

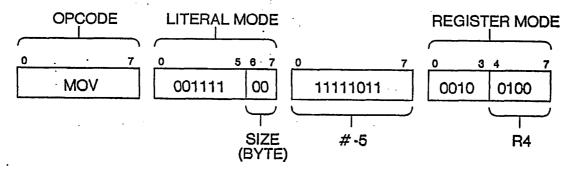

EXAMPLE: MOV #-5, %4

The single byte literal -5 is sign extended and copied into register 4.

5.7. Memory Addressing Modes. The addressing modes described in this section all address memory. They may be used as address operands. Memory operands may be 1, 2, 4, or 8 bytes in length as specified by bits 2:3 of the first specifier byte.

### Size field encoding:

- 00 Byte (8 bits)

- 01 · Halfword (2 bytes, 16 bits)

- 10 Word (4 bytes, 32 bits)

- 11 Doubleword (8 bytes, 64 bits)

5.7.1. Indirect Register Mode. In indirect register mode, the second half of the operand specifier byte (bits 4:7) designates a register that contains the address of the operand. The Maxreg restriction applies to the register designation. Note that specification of 0 in the register field indicates absolute addressing described below.

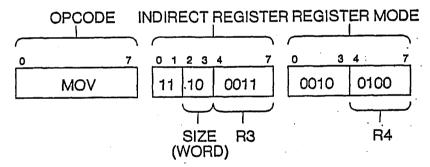

EXAMPLE: MOV @%3†W, %4

The word operand located at the address specified in register 3 is copied into register 4.

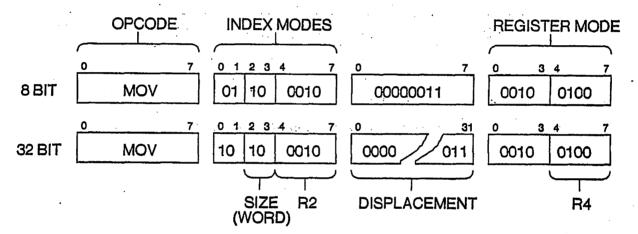

5.7.2. Register Indexed Modes. There are two register indexed modes, Byte Indexed and Word Indexed. Each one specifies a register (bits 4:7) and a size (bits 2:3) in the first operand specifier byte followed by a signed displacement that is 8 or 32 bits long respectively. The signed displacement is added to the contents of the designated register to form the address of the operand. The Maxreg restriction applies to the designated register. The address of the displacement may be designated as the index in both register index modes by specifying a 0 in the register field of the first specifier byte. The specifier is then evaluated as though the index register were pointing to the displacement when calculating the memory address.

**EXAMPLE:** MOV 3(%2)W, %4

The displacement 3 is added to the contents of register 2 to form an address. The contents of the word at this address are copied into register 4. Note that this operation is the same for Byte Indexed and Word Indexed. The only difference is the size of the displacement.

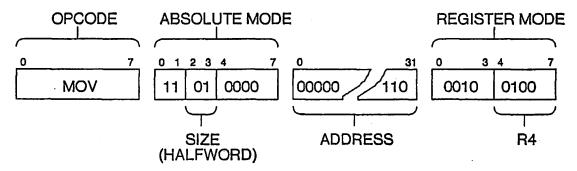

5.7.3. Absolute Mode. In absolute mode, the first specifier byte is followed by the 32-bit address of the operand.

EXAMPLE: MOV @(6)H,%4

The halfword starting at location 6 in memory is copied into register 4.

- 5.8. Parameter Addressing Modes. Parameter addressing modes allow access to parameters defined by the caller of a procedure. The parameter modes specify an unsigned integer parameter number. If this number is greater than the *Number of Parameters* field in the processor status word an Illegal.Parameter exception is raised. Parameter numbers are bound to the actual parameters by the procedure call. Parameter modes may be used as address operands if the parameter referenced is memory type. See section 8.4 for more information on parameters, their generation and use.

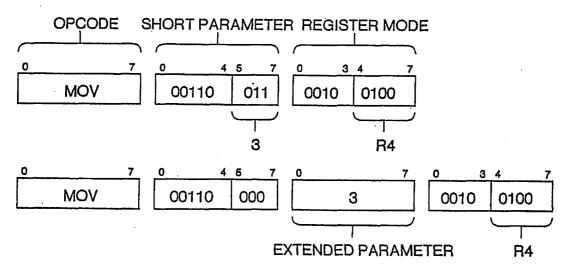

- 5.8.1. Short Parameter Mode. Bits 5:7 of the specifier byte designate a parameter number in the range 1 to 7.

- 5.8.2. Extended Parameter Mode. Specifier 00110000<sub>2</sub> indicates Extended parameter mode. The byte following this initial specifier contains an unsigned parameter number in the range 0 to 255.

EXAMPLE: MOV ?3, %4

The contents of parameter 3 are copied into register 4.

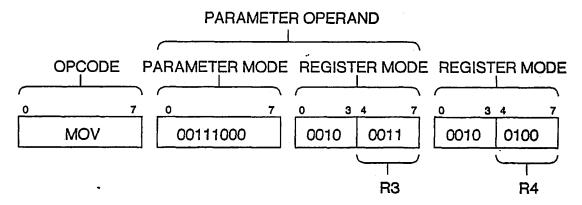

5.8.3. General Parameter Mode. General Parameter Mode is one of the *compound* modes described above. The first byte of the operand specifier is followed by another complete operand specifier. This *second* operand specifier is evaluated as an unsigned integer parameter number.

EXAMPLE: MOV ?(%3), %4

The parameter whose number is in register 3 is accessed and its value is copied into register 4.

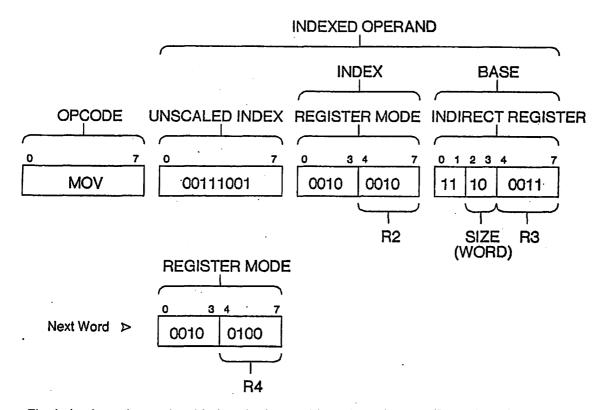

5.9. Unscaled Index Mode. Unscaled Index is another of the *compound* modes. The first specifier byte is followed by *two* complete operand specifiers, the first is the index and the second is the base. The base operand specifier is an *address* type operand, and must evaluate to a memory address as described in section 5.3 above. In order to access the Unscaled Index Operand, the index specifier is evaluated as a signed integer operand and its value is added to the address obtained from the base specifier. This forms the full address of the operand. If the index specifier's size is 64 bits, an Operand. Size exception is raised. The size of the Unscaled Index Operand is determined by the size field in the base (second) specifier. Unscaled index mode may be used as an address operand.

EXAMPLE: MOV @%3(%2)W, %4

The index in register 2 is added to the base address in register 3. The value of the word at this location is copied into register 4.

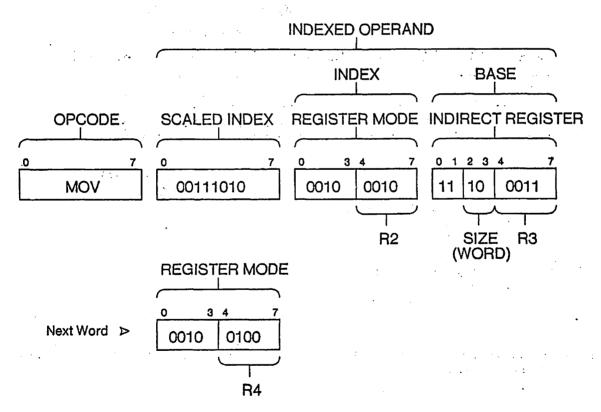

5.10. Scaled Index Mode. Scaled Index is the third *compound* mode. It is very similar to unscaled index described above. The first specifier byte is followed by two complete operand specifiers, the index and the base. The base operand specifier is an *address* type operand, and must evaluate to a memory address as described in section 5.3 above. The address of the Scaled index operand is found by evaluating the index specifier as a signed integer operand, scaling it, and adding it to the address obtained from the base specifier. The scaling is based on the size field in the base specifier. The scale factor is 1, 2, 4, or 8 based on the number of bytes in the operand specified by the base specifier size field. Scaling is simply multiplying the index value by the scale factor (since all of the scale factors are powers of 2 the multiplication can be accomplished by shifting). If the index overflows during scaling, the low order 32 bits are added to the base to form the operand address. If the index specifier's size is 64 bits, an Operand.Size exception is raised. Scaled index mode may be used as an address operand.

EXAMPLE: MOV @%3[%2]W, %4

The index value in register 2 is scaled by 4 (size = word) and added to the base address found in register 3. The value of the word found at the resulting address is copied into register 4.

- 5.11. Reserved Specifiers. Specifiers 00111011<sub>2</sub> and 00100000<sub>2</sub> are reserved for future definition. If they are encountered during operand specifier evaluation, an IIIegal.Mode exception shall be initiated.

- 5.12. Undefined Operand Sizes. The individual instruction descriptions indicate the defined sizes for each operand. If, during execution, an instruction encounters an operand whose size is not defined in the instruction description, an Operand. Size exception shall be initiated.

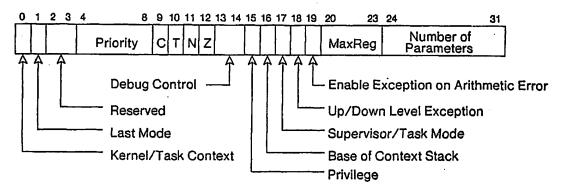

### 6. Processor Status Word

Control information related to the current execution context is maintained in the 32-bit Processor Status Word. Bits 0:12 contain information global to the currently executing task. Bits 13:31 contain information related to the current procedure's context. The procedure call and return facilities alter only bits 13:31, while initiation or completion of interrupts or tasks alters the entire PSW.

Figure 6-1: Processor Status Word

The form of the PSW is shown in figure 6-1. The fields of the PSW are defined below.

- 6.1. Kernel/Task Mode. Bit 0 specifies whether the processor is in kernel or task mode. If bit 0 is clear, the processor is in kernel mode. The Kernel Context Stack shall be used for the context of calls. If bit 0 of the PSW is set, the processor is in task mode. The task context stack shall be used for procedure calls.

- **6.2. Last Mode.** Bit 1 shall be set on interrupt and trap operations to reflect the state of the Kernel/Task mode bit prior to the interrupt or trap. This information is used by the RET instruction to determine which context stack is to be reactivated.

- 6.3. Reserved Bits. Bits 2:3 of the PSW are reserved for implementation dependent functions. A PSW saved as part of an interrupt or trap context change may have an implementation dependent bit pattern in this field. This PSW should be restored with this pattern unaltered to restart the interrupted context. The results of altering this bit pattern in such a case are unpredictable.

- **6.4. Priority.** Bits 4:8 of the PSW shall define the current priority of the processor. Hardware or software interrupt requests at an equal or lower priority shall be masked.

- **6.5. Carry Condition Code.** Bit 9 of the PSW is the carry bit. The C bit shall be set by integer add and subtract instructions to reflect the carry from the most significant bit of the internal result.

- 6.6. Truncate Condition Code. Bit 10 of the PSW is the truncation flag. The T bit shall be set if the integer result of an operation cannot be correctly represented in the specified result operand. The setting of truncate indicates that significant bits (bits not equal to the stored sign bit) were lost. The truncate bit shall also be set on the occurrence of certain floating point errors, when the corresponding floating point exception is disabled. Refer to section 30.4.

- 6.7. Negative Condition Code. Bit 11 of the PSW is the negative condition code. The N bit shall be set as specified in the instruction descriptions. Generally, setting of the N bit implies a negative or less than condition.

- 6.8. Zero Condition Code. Bit 12 of the PSW is the zero condition code. The Z bit shall be set as specified in the instruction descriptions. Generally, setting of the Z bit implies a zero or equal condition.

- 6.9. Debugging Control. Bits 13:14 of the PSW control the instruction and procedure level debugging facilities. Refer to section 10 for a description of their function.

- **6.10.** Privilege. Bit 15 of the PSW specifies whether the current context is privileged. If this bit is set, privileged instructions may be executed. If this bit is clear, an attempt to execute a privileged instruction shall cause a trap.

- 6.11. Base of Context. Bit 16 of the PSW indicates the execution context base. If this bit is set, the currently executing context has no caller. Execution of a RET instruction with the Base bit set shall cause an interrupt return operation as defined in the RET instruction description. Bit 16 shall be set in the PSW of the new context produced by an interrupt, trap, TINIT instruction, or PINIT Instruction.

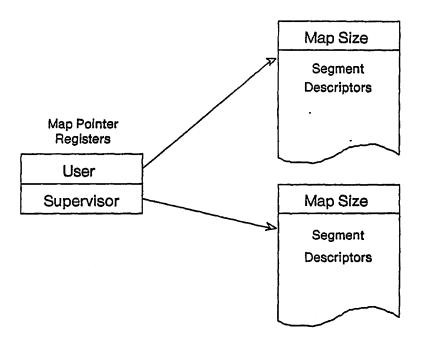

- 6.12. Supervisor Mode. Bit 17 shall indicate whether the current context is in Supervisor mode. If this bit is set accesses through the supervisor map may be made.

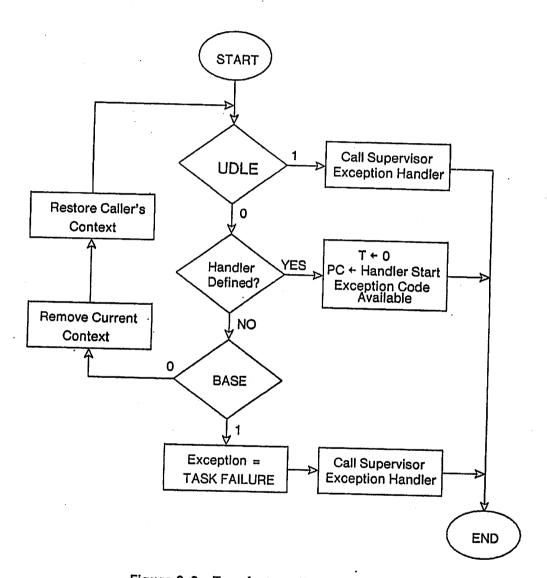

- 6.13. Up/Down Level Exception Propagation (UDLE). Bit 18 shall indicate the direction of exception propagation. If bit 18 is clear, the exception shall be directed to the current exception handler or to the caller. If bit 18 is set, the exception shall be directed to the Supervisor Exception Handler: Refer to section 9.4 for a detailed explanation of exception propagation.

- 6.14. Enable Arithmetic Error. EAE, bit 19 of the PSW, shall control the generation of exceptions related to arithmetic errors. If EAE is set and the T bit (bit 10 of the PSW) is set at the end of an instruction, a Truncation exception shall occur. If EAE is clear, truncation exceptions shall be suppressed. EAE is also used as a mask for floating point errors. Refer to section 30.4.

- 6.15. Maxreg Field. Bits 20:23 of the PSW define the unsigned maximum accessible register number in the current context. An attempt to access a register number greater than that specified in Maxreg shall cause an Illegal.Register exception.

- 6.16. Number of Parameters. Bits 24:31 define the unsigned number of parameters accessible in the current context. An attempt to access a parameter number greater than that specified in bits 24:31 shall cause an Illegal.Parameter exception.

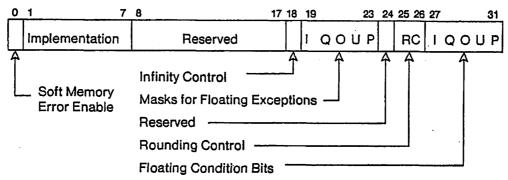

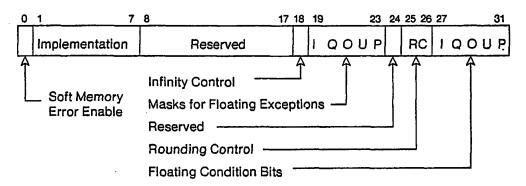

## 7. Auxiliary Status Register

The Auxiliary Status Register is a 32-bit register located in the I/O space. It contains various processor control and status bits that need be accessed only infrequently. It is not saved and restored on context changes. The format of the ASR is shown in figure 7-1. The fields of the ASR are described below.

Figure 7-1: Auxiliary Status Register

- 7.1. Soft Memory Error Enable. Bit 0 shall control the generation of traps on soft memory error conditions. If this bit is clear, no traps shall be generated. Refer to section 11.6 for a description of the memory error handling facility.

- 7.2. Reserved Bits. Bits 8:17 and 24 are reserved for future definition. Bits 1:7 are reserved for implementation dependent functions. The ASR may have an implementation dependent bit pattern in this field.

- 7.3. Floating Point Mode Control. Bits 18:23 and 25:31 are dedicated to control and status information for the various modes supported by the floating point system. Refer to section 30.4 for a detailed discussion of each.

- 7.3.1. Infinity Control. Bit 18 shall control the ordering of the special floating point infinity symbols. If set, negative infinity shall be considered less than positive infinity. If clear, negative and positive infinity shall be considered equal.

- 7.3.2. Exception Event and Mask Bits. For each of five different exception conditions supported by the floating point system there shall be an event and a mask bit in the ASR. The mask bit shall control generation of an exception on occurrence of the corresponding condition. Refer to section 30.4 for a description of floating exception processing. The assigned bits and exceptions for each condition are listed below.

| Condition         | Mask Bit | Event Bit   | Exception          |

|-------------------|----------|-------------|--------------------|

| Invalid Operation | ´ 19     | <b>27</b> · | Invalid.Operation  |

| Divide By 0       | 20       | 28          | Divide.By.Zero     |

| Overflow          | 21       | 29          | Floating.Overflow  |

| Underflow         | 22       | 30          | Floating.Underflow |

| Inexact Result    | 23       | 31          | Floating.Inexact   |

**7.3.3.** Rounding Control. Bits 25:26 select the rounding mode used by floating point operations. Refer to section 30.5 for a complete description.

### 8. Procedure Interface

The fundamental unit of execution in the Nebula architecture is the procedure. A procedure is a code sequence with an associated context. The context of a procedure includes:

PSW The processor status word contains information about the current procedure.

Included is the number of registers accessible, the number of parameters, the method of dealing with exceptions, and certain privilege information. The context

for each procedure includes the PSW that describes its capabilities.

Registers Each procedure is provided with its own set of registers that are separate from

those of any other procedure.

Parameters Procedures may have parameters. If a procedure has parameters, then the list of

parameters for the procedure is included in the procedure's context.

Exception Handler Each procedure may define a sequence of code to be executed when an error or

abnormal condition is detected. This error code is called an exception handler. The location and state of a procedure's exception handler is recorded in its

context.

This collection of information, called the Procedure Context, defines the current state of execution of a procedure.

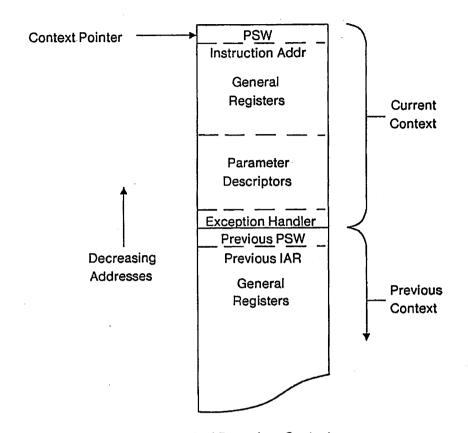

Procedures may call other procedures. This implies that the current procedure context should be preserved and a new procedure context created for the called procedure. Completion of the called procedure should cause its context to be eliminated and the calling procedure's context to be restarted. Thus the call/return behavior of procedures produces a stacking of procedure contexts. In the Nebula architecture, the stacked procedure contexts are maintained on a Context Stack. Figure 8-1 shows the general form of the context stack.

In each task there is a procedure (usually called the "main program") that has the unique property that it has no caller. The context for this procedure was created by the initiation of execution of the task. A return from this "main program" implies termination of the task. The context of the "main program" forms the BASE of the stack of procedure contexts for this task. This unique procedure context is identified by the fact that its PSW has bit 16, the BASE bit, set. The collection of procedure contexts (the currently active routine plus its caller plus the caller's caller... down to the "main program") is called an Execution Context.

- 8.1. The Context Stacks. There are two active context stacks in the Nebula architecture: the Kernel Context Stack and the Task Context Stack. These stacks are accessed by using one of two context pointers. The context stack used by the executing code is determined by the current PSW. Normal call and return operations do not change the context stack in use. Interrupts, traps, and task completions may cause a context stack switch.

- 8.1.1. Context Pointers. There shall be two 32-bit registers, called the Kernel Context Pointer and the Task Context Pointer, that contain the virtual addresses of the currently active procedure contexts on the Kernel and Task context stacks, respectively. The Context Pointer currently in use shall be selected by bit 0 of the current PSW. If this bit is clear, the Kernel Context pointer shall be used, if this bit is set the Task Context pointer shall be used. These registers shall be accessible in the I/O space and by the privileged LTASK and STASK instructions. The operation of these instructions nsure that the address contained in the context pointer is aligned on a 32-bit word boundary.

Figure 8-1: Stacked Procedure Contexts

- 8.1.2. Structure of Context Stacks. The context stack selected by the current context pointer shall be used by the executing code. The context of each executing procedure shall be stored in the following order (increasing addresses):

- 1. The PSW for this procedure.

- 2. The registers for this procedure, starting with the instruction address register, up to the maximum accessible register as defined in this procedure's PSW.

- 3. The parameter descriptors for this procedure (defined in section 8.4.4).

- 4. The state of the exception handler for this procedure (defined in section 9).

The context stack shall expand downward. A call by the currently executing procedure shall cause the context pointer to be decremented by the size of the context of the called procedure. The context of the called procedure shall then be placed in the area defined by the decremented context pointer. Note that contexts are not position independent in the virtual address space.

- 8.1.3. Cacheing of the Context Stack. The context of a procedure contains areas reserved for a variety of frequently accessed quantities such as the instruction address register, the PSW, the general registers and so on. In many implementations it will be desirable to maintain such information in fast registers. This is particularly true for the currently executing procedure's instruction address register and general registers. The Nebula architecture does *not* define the properties of any such cacheing mechanism. The representation of the context stored on the Kernel and Task context stacks is IMPLEMENTATION DEPENDENT. The value of such memory locations is undefined. The effect of storing into such memory locations is unpredictable. The memory management system provides a mechanism for protecting against such invalid software actions.

- 8.1.4. Changing of Context Stack Pointers. The Nebula architecture provides two active context stacks, corresponding to the Kernel Context Pointer and Task Context Pointer. Since each task in the system has associated with it a unique execution context, a mechanism for changing the active Task Context Pointer is provided. The LTASK and STASK instructions provide this facility. Additionally, these instructions shall force consistency between the context in memory and any cached state. Subsequent to the execution of STASK all context information necessary to restart the task context shall be stored in addressable memory in the context stack. For a complete description of their functions, refer to the individual instruction descriptions.

- 8.1.5. Alignment of Context Pointers. The knowledge of which item in the current procedure context is pointed to by the context pointer is implementation dependent. The address in the context pointer shall be greater than or equal to the smallest address occupied by the current context. When a new procedure context is created, the context pointer (prior to being decremented) shall be greater than the address of any byte of the newly created context. These restrictions imply that a context stack may be initialized by setting the context pointer to the greatest word address in the context segment plus 4.

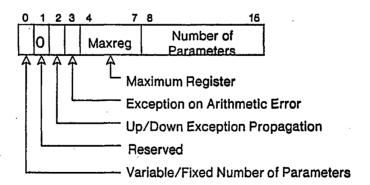

- 8.2. Procedure Descriptor. The characteristics of a procedure are specified by a procedure descriptor located at the entry point(s) of the procedure. This 16-bit descriptor will be aligned on a word boundary. The format of the procedure descriptor is shown in figure 8-2. Upon invocation of the procedure, the information contained in bits 2:15 is recorded in bits 18:31 of the PSW. Execution of the procedure shall begin at the location immediately following the procedure descriptor located at the addressed entry point. The function of each field of the procedure descriptor is described below.

Figure 8-2: Procedure Descriptor

8.2.1. Fixed/Variable Number of Parameters. Bit 0 of the procedure descriptor shall specify whether the number of parameters for this procedure is fixed or variable. If bit 0 is clear, bits 8:15 will contain the number of parameters. If bit 0 is set, bits 8:15 are reserved and the first byte of the parameter list shall be evaluated as the unsigned integer number of parameters. In either event, the number of parameters for the procedure shall be placed in bits 24:31 of the PSW.

Some procedure entries, such as interrupt and trap handlers, have their number of parameters fixed by the hardware. In such procedure descriptors, bit 0 is reserved and bits 8:15 are ignored.

- 8.2.2. Reserved Bit. Bit 1 of the procedure descriptor shall be reserved for future definition.

- 8.2.3. Exception Propagation Control. Bit 2 of the procedure descriptor shall be copied to bit 18 of the PSW. This bit defines the direction of exception propagation. See section 9.4.

- 8.2.4. Arithmetic Error Control. Bit 3 of the procedure descriptor shall be copied to bit 19 of the PSW. This bit defines the action to be taken on arithmetic errors. See section 6.14.

- 8.2.5. Available Registers. Bits 4.7 shall determine the maximum numbered register accessible to this procedure. This value shall be copied to bits 20:23 of the PSW. This number of registers (and an instruction address register) shall be allocated for use by this procedure.

- 8.3. Procedure Invocation. In the Nebula architecture calls, supervisor calls (SVCs), unimplemented opcodes (OPEXs), supervisor handled exceptions, task initiations, interrupts, and traps are all handled as procedure invocations using a common mechanism. They differ primarily in the manner in which they determine the entry address of the procedure to be invoked and the parameters to be passed.

The procedure call mechanism is driven by the procedure descriptor located at the entry address of the procedure. Invocation of a procedure shall cause the following actions to occur:

- The current PSW is saved in the context stack and a new PSW is created.

- The register set of the invoked procedure is allocated.

- The exception handler for the procedure is initialized.

- The parameter descriptors for the procedure are initialized.

The current context pointer shall be updated to reflect the new procedure context added to the context stack. Each of these actions is detailed below.

8.3.1. Determination of a New PSW. The contents of the new PSW are determined by the type of invocation (call, trap, etc.) and by the procedure descriptor. Bits 18:31 of the PSW shall be determined by the procedure descriptor as described in section 8.2. Bit 16 (BASE) shall be set by interrupts, traps, the TINIT and PINIT instructions (task initiation), and by invocation of the supervisor exception handler with a Task.Failure exception. It shall be cleared otherwise. Bit 17 (Supervisor) shall be set equal to the most significant bit of the procedure entry address. Note that the call instructions will produce a trap if a non-supervisor program attempts to set this bit.Bits 2:3 are set/reset in an implementation dependent manner. Bits 0:1 and 4:14 of the PSW shall be set in the following manner:

CALL, CALLU Unchanged

SVC Bits 13:14 are cleared. Bits 0:1 and 4:12 are Unchanged

Supervisor Exception Handler

Bits 13:14 are cleared. Bits 0:1 and 4:12 are Unchanged

Unimplemented Opcode (OPEX)

Bits 13:14 are cleared. Bits 0:1 and 4:12 are Unchanged

Task Initiation

The TINIT and PINIT instructions specify the contents of bits 0:1 and 4:15 of the PSW as one of their operands. Bits 2:3 are implementation dependent.

Traps

Last mode (bit 1) shall be set to the previous value of bit 0. Bit 0 (Kernel/Task) shall be clear. This forces the trap to use the Kernel context stack. Bits 4:8 shall be set to 1F (Hex). Bits 9:14 (the condition codes and debug control) shall be clear. Bits 2:3 are implementation dependent.

Interrupts

The new PSW shall be determined as for traps except the priority (bits 4:8) shall be set to the priority of the interrupting device.

The privilege bit of the new PSW (bit 15) shall be set equal to bit 31 of the vector for trap and interrupt entries. For SVC, Supervisor Exception Handler, unimplemented opcode (OPEX) entries, the privilege bit of the new PSW shall be formed by OR'ing the privilege bit of the old PSW with Bit 31 of the vector. Task initiation specifies this bit explicitly. Call instructions leave the bit unchanged or clear it, depending on the opcode.

- **8.3.2.** Register Set Allocation. The registers of a called procedure are separate from those of the caller. The number of registers available to the invoked procedure shall be determined by the procedure descriptor. Space shall be allocated on the context stack for each register starting with the instruction address register followed by the number of registers specified in the procedure descriptor. The contents of the newly created general registers are undefined with the exception of register 1. If this is not a task initiation, interrupt or trap invocation, and register 1 exists in both the caller and called procedure's registers, then the value of the caller's register 1 shall be copied to the called procedure's register 1. Otherwise, the contents of register 1 are also undefined. With this single exception, there is no inheritance of registers in the Nebula architecture. Note that this inheritance of register 1 applies to the supervisor exception handler. If register 1 is defined for the Supervisor Exception Handler and for the procedure that invoked it, the contents of the invoking procedure's register 1 are copied into register 1 of the Supervisor Exception, no invoking procedure is presumed and register 1 of the Supervisor Exception, no invoking procedure is presumed and register 1 of the Supervisor Exception Handler is undefined.

- 8.3.3. Initialization of Exception Handler. Space in the procedure context shall be provided to contain the state of the exception handler for this procedure. The exception handler shall be set in the Disabled state (see section 9).

- 8.3.4. Initialization of Parameter List. The parameters for a procedure invoked by a CALL, CALLU, SVC, or unimplemented opcode (OPEX) are specified explicitly in a parameter list. The parameters of an interrupt, trap, or supervisor exception handler invocation are implicitly defined by the architecture. Task initiations have no parameters. An area of the procedure context shall be reserved for the parameter descriptors of the invoked procedure. There shall be one such descriptor for each parameter of the procedure. Parameter descriptors are defined functionally in section 8.4.

- 8.4. Parameter Lists. The passing of arguments or parameters to a called procedure is accomplished by specifying a parameter list. In calls, supervisor calls, and unimplemented opcode exceptions (OPEXs) the parameter list is explicitly specified while in interrupts, traps and the supervisor exception handler it is implied by the architecture. The specified parameters are accessed using the parameter addressing modes that determine the number of the parameter to be accessed

(1st, 2nd, 3rd, etc.). The representation of these addressing modes is described in section 5.8. The semantics of parameter access are defined below.

- 8.4.1. Parameter Specification. Explicit specification of parameters is accomplished by a parameter list that immediately follows the call opcode (for OPEX) or the index specifier (for SVC) or the entry address specifier (for CALL and CALLU). The parameter list shall consist of a sequence of operand specifiers or a byte literal followed by a sequence of operand specifiers. These operand specifiers may use any of the addressing modes described in section 5. The number of operand specifiers shall be determined in the following manner:

- The calling instruction (CALL, CALLU, SVC, or OPEX) will specify the address of the procedure to be called. At this address there will be a procedure descriptor, as described in section 8.2.

- 2. If bit 0 of the procedure descriptor is clear, bits 8:15 of the procedure descriptor shall specify the number of parameters. If bit 0 is set, the first byte of the parameter list shall be interpreted as the unsigned integer number of parameters. The remaining operands of the reduced parameter list shall be interpreted as the actual parameter list.

Each operand specifier in the parameter list specifies the location and size of one operand. The location of each operand shall be determined using the state of the CALLER at the time of the call. Any registers specified in the parameter list shall refer to the caller's registers; any addresses in the parameter list shall be computed using the caller's registers as they exist when the call is executed.

- 8.4.2. Parameter Access. The parameters specified in the parameter list are conceptually numbered in increasing order, starting at 1. The parameter addressing modes specify a parameter number. The appearance of a parameter addressing mode as an operand shall be interpreted as an access to the correspondingly numbered parameter of the current context. Parameter 0 shall be interpreted as the number of parameters accessible in the current context; this information is recorded in bits 24:31 of the PSW. Parameter 0 cannot be written; an attempt to do so shall cause a Illegal.Write exception. Bits 24:31 of the PSW specify the maximum parameter number in the current context. An attempt to access a parameter number greater than this shall cause an Illegal.Parameter exception.

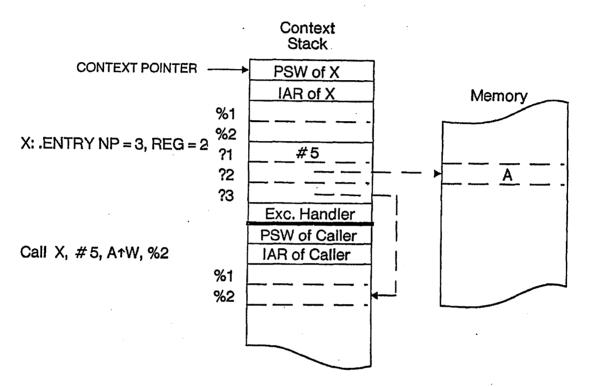

- 8.4.3. Example of Parameter Linkage. The context stack generated by this example (assuming 2 registers for both the caller and callee) is shown in figure 8-3. Assume X is a procedure with a fixed number of parameters = 3 and that both X and its caller have access to a register 2 (%2). The following call:

```

Call X, #5,A+W, %2

```

would set up the following correspondence between parameter numbers (written as ?n) and parameters in the parameter list:

```

?0 = #3 ; Number of parameters

?1 = #5 ; A literal 5

?2 = A+W ; A 32-bit word in memory named A

?3 = %2 ; The caller's register 2

?4.?5... illegal

```

The use of parameter addressing modes in this context would have the following effects:

| MOV | ?1,%2 <=>  | MOV | #5,%2  |

|-----|------------|-----|--------|

| MOV | ?2,%2 <=>  | MOV | A+W,%2 |

| MOV | 73. %2 <=> | MOV | %2*,%2 |

NOTE: The last example moves the contents of the CALLER's register 2 to the called routine's register 2.

Figure 8-3: Example of a Call Context

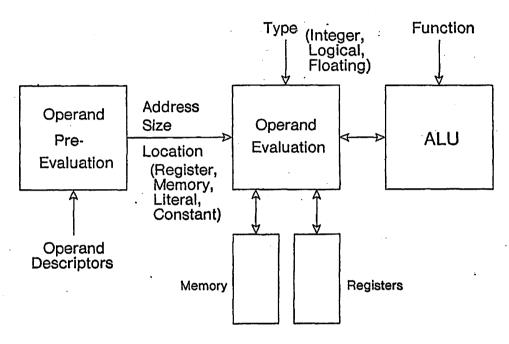

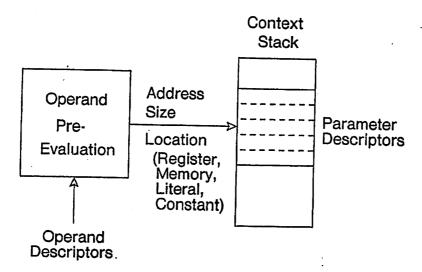

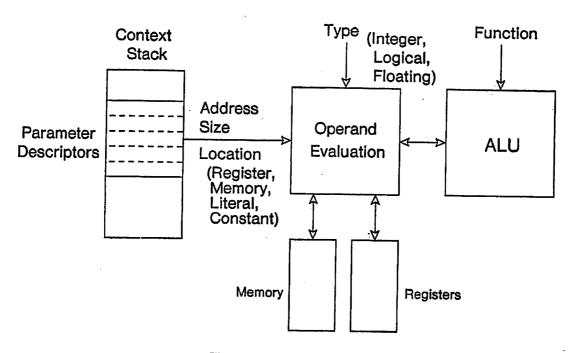

8.4.4. Mechanism of Parameter Addressing. The parameter access mechanism can be viewed as a splitting of the operand access mechanism used by all instructions. Figure 8-4 is a conceptual picture of the Nebula microengine. Operand specifiers are reduced to location and size information by operand pre-evaluation. This primitive information is used for operand access during operand evaluation.

Figure 8-4: Normal Operand Processing

The operands of parameter lists, however, are not fully evaluated in this manner. Instead, the location and size information from pre-evaluation is diverted to the appropriate parameter descriptor in the context stack as shown in figure 8-5. This reduces the parameter list to a linear descriptor array.

Access to parameters is accomplished by parameter addressing modes. These operand specifiers evaluate to an unsigned integer parameter number. This index is used to recover the position and size information corresponding to the specified parameter. The mechanism is diagrammed in figure 2.6

Figure 8-5: Parameter List Operand Processing

Figure 8-6: Parameter Access

The size and format of the parameter descriptors is implementation dependent. The encoding of these descriptors is constrained only by the functional requirements placed on the parameter passing and access facilities. The following is an example of an encoding sufficient to meet these requirements. In this example the parameter descriptors specify one of four possible locations for the parameter:

| Constant | The parameter is a value contained in the parameter descriptor. Such a         |

|----------|--------------------------------------------------------------------------------|

|          | parameter is read-only. An attempt to write a constant parameter will cause an |

|          | Illegal. Write exception                                                       |

| Literal | The parameter is a literal contained in the instruction stream. The address and     |

|---------|-------------------------------------------------------------------------------------|

|         | size of the literal are encoded in this descriptor. This parameter is read-only. An |

|         | attempt to write this parameter will cause an Illegal. Write exception.             |

| Register | The parameter is a register in the context stack. The size of the parameter is 32   |

|----------|-------------------------------------------------------------------------------------|

|          | bits. A pointer to the register in the context stack is encoded in this descriptor. |

| Memory | The parameter is a memory location. | The size and address of this location are |

|--------|-------------------------------------|-------------------------------------------|

|        | encoded in this descriptor.         |                                           |

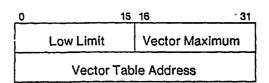

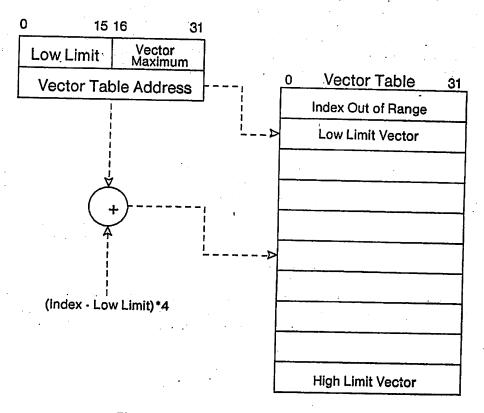

8.5. Vectored Calls: SVC and OPEX. The supervisor call (SVC) and unimplemented opcode (OPcode Exception or OPEX) facilities utilize a vectoring mechanism controlled by the supervisor. Vectoring shall be controlled by a pair of processor registers for SVCs and a pair for OPEXs. The first register specifies the limits for the vectoring index. The second register specifies the word address of the vector table. The two low order bits (bits 30:31) are ignored. The format of these registers is shown in figure 8-7.

Figure 8-7: SVC and OPEX Vector Registers

The vectored instruction shall select the appropriate register pair (SVC or OPEX) and specify an unsigned index. This index shall be compared with the unsigned low limit specified in the first register of the pair. If the index is less than the low limit, or if (index - low limit) is greater than vector maximum (unsigned), the 32-bit word located at the word address before the virtual address in the second register (Vector Table Address - 4) shall be used as the vector. If the index is within the specified range, the quantity Vector Table Address + (index - low limit)\*4 shall be used as the virtual address of the vector. The contents of the 32-bit vector shall be used as the entry address of the procedure. Access to this vector and to the procedure descriptor shall be allowed regardless of the state of the privilege or supervisor bits of the PSW. The vectoring operation is shown in figure 8-8.

Figure 8-8: Vectored Call Address Calculation

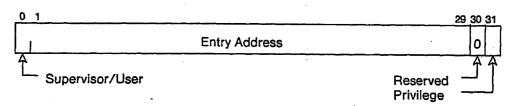

8.6. Vector Format. All vectored operations in the Nebula architecture (interrupts, traps, SVCs, OPEXs and Supervisor Exception Handler entries) use a common vector format. Vectors are 32 bit words with the format shown in figure 8-9. Bits 0:29 of the vector specify bits 0:29 of the entry address. Bits 30:31 of the entry address are assumed to be zero. Bit 0 is copied into bit 17 of the new PSW. Bit 31 of the vector is used in determining the privilege of the called procedure. For interrupts and traps bit 31 of the vector is copied to bit 15 of the new PSW (privilege). For SVCs, OPEXs and supervisor exception handler calls bit 31 of the vector is OR'ed with bit 15 of the caller's PSW to form bit 15 for the new PSW.

Figure 8-9: Vector Format

8.7. Return from Procedures. The return from a procedure is accomplished through the use of a return instruction. Execution of a RET instruction causes a normal return. Execution of an ERET or ERP instruction causes a return with exception information. See the individual instruction descriptions for details.

# 9. Exceptions

Program errors are handled by the exception facility. Exceptions may be handled by the procedure in which they occur, or by the supervisor, or by the caller of the procedure in which they occur.

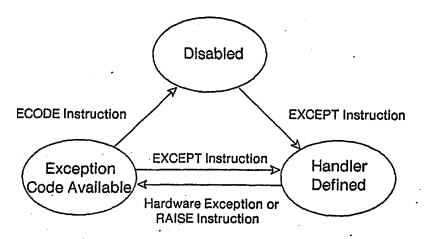

9.1. Procedure Exception Handler. There shall be an entry in the context of each procedure defining the state of the current exception handler associated with that procedure. The exception handler of a procedure shall be in one of three states:

Disabled No exception handler is currently defined for this procedure.

Handler Defined The starting address of the exception handler for this procedure is recorded in the context stack.

### Exception Code Available

No exception handler is currently defined for this procedure. The exception code for the last exception is recorded in the context stack.

The states of the exception handler for a procedure, and the typical transitions between states, are shown in figure 9-1. Encodings of the states in the context area shall be implementation dependent.

Figure 9-1: States of an Exception Handler

- 9.2. Definition of an Exception Handler. Upon invocation, a procedure's exception handler shall be set in the disabled state. The exception handler associated with a procedure can be defined by use of the EXCEPT instruction. When EXCEPT is executed, the exception handler for the current procedure shall be defined to start at the address specified by the EXCEPT instruction.

- 9.3. Raising an Exception. An exception may be raised by the RAISE, ERET, ERP, TRAISE, or PRAISE instructions, or by the detection of an abnormal condition by the hardware. An exception code is associated with each exception raised. The exception code is explicitly specified by the RAISE, ERET, ERP, TRAISE, and PRAISE instructions as an operand. The exception code specified shall be treated as an unsigned integer of 16 bits. Hardware generated exceptions shall have associated with them the following fixed codes:

| Exception Name      | Code (Decimal) | Described in Section |

|---------------------|----------------|----------------------|

| Specification.Error | 1              | 25                   |

| Illegal.Mode        | 2              | 5.2, 5.11            |

| Illegal.Parameter   | 3              | 8.4.2                |

| Illegal.Register    | 4              | 5.1, 6.15            |

| Illegal.Write       | 5              | 5.5, 5.6, 8.4.2      |

| Bit.Field.Size      | 6              | 28                   |

| Illegal.Address     | 7              | 5.3                  |

| Operand.Size        | 8              | 5.9, 5.10, 5.12, 27  |

| Context.Alignment   | 9              | 25 ·                 |

| Context.Base        | 10             | 29                   |

| Segment.Specifier   | 11             | 29                   |

| Supervisor.Check    | 12             | 29                   |

| Task.Load.Error     | 13             | 25                   |

| IOC.Busy            | 14             | 29                   |

| Illegal.Divisor     | 16             | 18.2                 |

| Truncation          | 17             | 18.2                 |

| Range.Error         | 18             | 22                   |

| Invalid.Operation   | 19             | 30.4.1               |

| Divide.By.Zero      | 20             | 30.4.2               |

| Floating.Overflow   | 21             | 30.4.3               |

| Floating.Underflow  | 22             | 30.4.4               |

| Floating.Inexact    | 23             | 30.4.5               |

| Unordered           | 24             | 30.7                 |

| Task.Failure        | 32             | 9.4, 26              |

| Break               | · <b>33</b>    | 29                   |

| Instruction.Break   | 34             | 10                   |

| Call.Break          | 35             | 10.                  |

NOTE: Software should avoid using exception codes 0 to 63. These should be reserved to indicate the conditions listed above and others that may be added in the future.