# **How to Scale Your Model**

A Systems View of LLMs on TPUs

Jacob Austin

Sholto Douglas

Roy Frostig

Anselm Levskaya

Charlie Chen

Sharad Vikram

Federico Lebron

Peter Choy

Vinay Ramasesh

Albert Webson

Reiner Pope

# **Contents**

| Int | trodu      | ction                                   | 4        |

|-----|------------|-----------------------------------------|----------|

| 1   | Intro      | to Rooflines                            | 7        |

|     | 1.1        | Where Does the Time Go?                 | 7        |

|     |            | 1.1.1 Visualizing rooflines             | 9        |

|     |            | 1.1.2 Matrix multiplication             | 9        |

|     |            | 1.1.3 Network communication rooflines   | 10       |

|     | 1.2        | Worked problems                         | 11       |

| 2   | A II A     | About TPUs                              | 12       |

| _   | 2.1        | What is a TPU?                          | 12       |

|     |            |                                         | 16       |

|     | 2.2        | TPU Networking                          | 18       |

|     | 2.3        | Key Takeaways                           |          |

|     | 2.4        | ·                                       | 20       |

|     | 2.5        | Appendix                                | 21       |

|     |            | 2.5.1 Appendix A: Let's talk about GPUs | 21       |

|     |            |                                         | 22       |

|     |            | 2.5.3 Appendix C: TPU internals         | 25       |

| 3   | Shai       | rded Matrices and How to Multiply Them  | 26       |

| •   | 3.1        | • •                                     | 26       |

|     |            | <b>9</b>                                | 26       |

|     |            |                                         | 30       |

|     | 3.2        | Computation With Sharded Arrays         | 31       |

|     | 0.2        |                                         | 32       |

|     |            | i g                                     | 32       |

|     |            | i g                                     | 35       |

|     |            | ·                                       | 36       |

|     | 2.2        | · · · · · · · · · · · · · · · · · · ·   | 37       |

|     | 3.3        |                                         | 37       |

|     |            |                                         |          |

|     |            |                                         | 38       |

|     | 3.4        | ,                                       | 38       |

|     | 3.5        | Worked problems                         | 40       |

| 4   | Tran       | asformers                               | 43       |

|     | 4.1        | Counting Dots                           | 43       |

|     |            | 4.1.1 Forwards and reverse FLOPs        | 43       |

|     | 4.2        |                                         | 44       |

|     | 4.3        |                                         | 46       |

|     | 4.4        |                                         | 48       |

|     |            |                                         | 48       |

|     |            |                                         | 48       |

|     |            | * · · · · · · · · · · · · · · · · · · · | 49       |

|     | 1 =        |                                         | 49<br>49 |

|     | 4.5<br>4.6 | ,                                       | 49<br>50 |

|     |            |                                         |          |

|     | 4./        | Appendix                                | 51       |

|   |      | 4.7.1                                 | Appendix A: How does Flash Attention work?                                            | 51  |  |  |  |  |  |  |  |

|---|------|---------------------------------------|---------------------------------------------------------------------------------------|-----|--|--|--|--|--|--|--|

| 5 | Trai | ning                                  |                                                                                       | 54  |  |  |  |  |  |  |  |

|   | 5.1  | What                                  | Do We Mean By Scaling?                                                                | 54  |  |  |  |  |  |  |  |

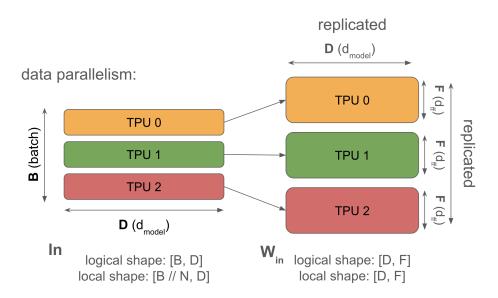

|   |      | 5.1.1                                 | Data Parallelism                                                                      | 55  |  |  |  |  |  |  |  |

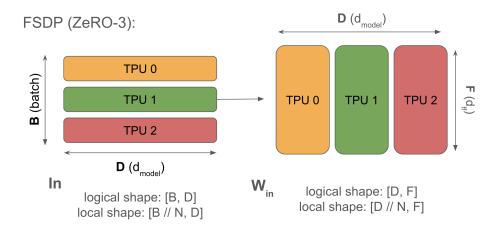

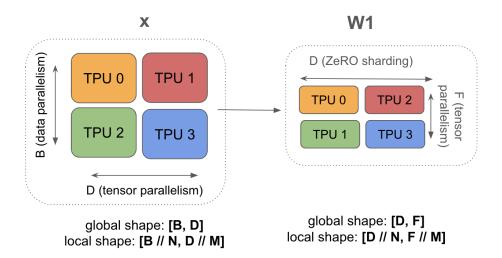

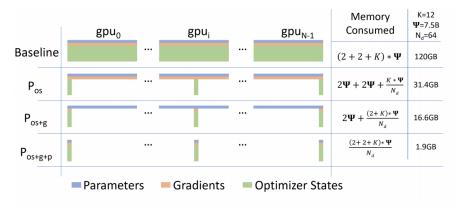

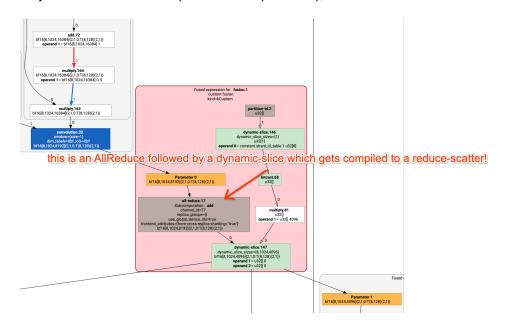

|   |      | 5.1.2                                 | Fully-Sharded Data Parallelism (FSDP)                                                 | 58  |  |  |  |  |  |  |  |

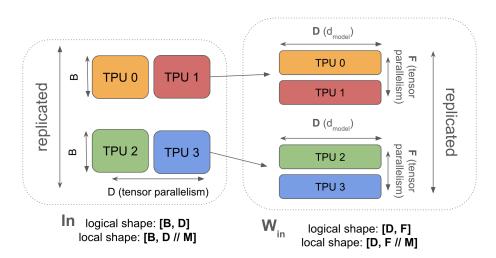

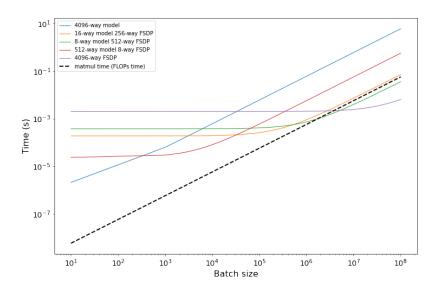

|   |      | 5.1.3                                 | Tensor Parallelism                                                                    | 61  |  |  |  |  |  |  |  |

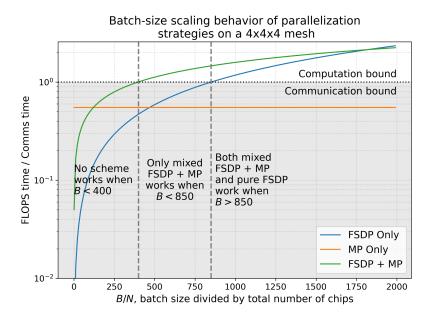

|   |      | 5.1.4                                 | Mixed FSDP and Tensor Parallelism                                                     | 63  |  |  |  |  |  |  |  |

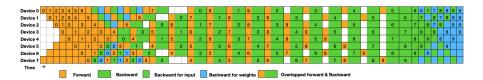

|   |      | 5.1.5                                 | Pipelining                                                                            | 68  |  |  |  |  |  |  |  |

|   |      | 5.1.6                                 | Scaling Between Pods                                                                  | 70  |  |  |  |  |  |  |  |

|   | 5.2  | · · · · · · · · · · · · · · · · · · · |                                                                                       |     |  |  |  |  |  |  |  |

|   | 5.3  |                                       |                                                                                       |     |  |  |  |  |  |  |  |

|   | 5.4  |                                       | ndix                                                                                  | 73  |  |  |  |  |  |  |  |

|   |      | 5.4.1                                 | Appendix A - More stuff about FSDP                                                    | 73  |  |  |  |  |  |  |  |

|   |      | 5.4.2                                 | Appendix B - Deriving the comms necessary for the backward passes                     | 73  |  |  |  |  |  |  |  |

|   |      | 5.4.3                                 | Appendix C - Alternate derivation of the batch size constraint for mixed FSDP + model |     |  |  |  |  |  |  |  |

|   |      | J                                     | parallelism                                                                           | 74  |  |  |  |  |  |  |  |

| 6 | Trai | nina I I                              | AMA 3 on TPUs                                                                         | 75  |  |  |  |  |  |  |  |

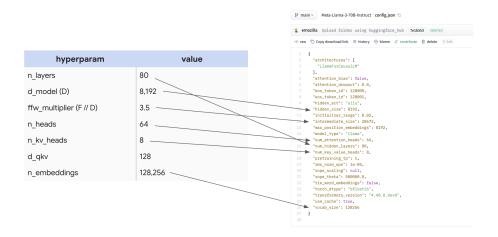

| • | 6.1  | -                                     | does LLAMA 3 look like?                                                               |     |  |  |  |  |  |  |  |

|   | 6.2  |                                       | ing parameters and FLOPs                                                              |     |  |  |  |  |  |  |  |

|   | 6.3  |                                       | o shard LLAMA 3-70B for training                                                      |     |  |  |  |  |  |  |  |

|   | 6.4  |                                       | ed Problems                                                                           |     |  |  |  |  |  |  |  |

|   | 0.4  | WOIKE                                 | su Flobleitis                                                                         | 79  |  |  |  |  |  |  |  |

| 7 |      |                                       | ransformer Inference                                                                  | 80  |  |  |  |  |  |  |  |

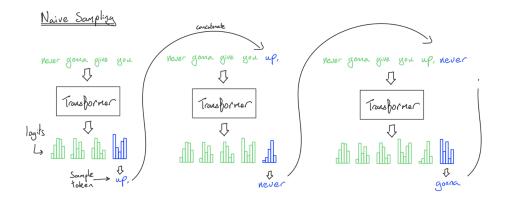

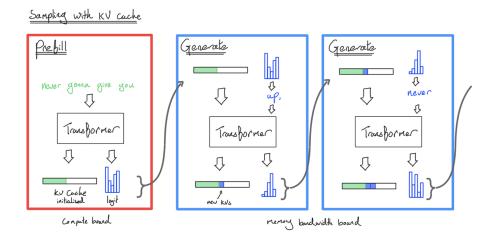

|   | 7.1  |                                       | asics of Transformer Inference                                                        |     |  |  |  |  |  |  |  |

|   |      | 7.1.1                                 | What do we actually want to optimize?                                                 |     |  |  |  |  |  |  |  |

|   |      | 7.1.2                                 | A more granular view of the Transformer                                               |     |  |  |  |  |  |  |  |

|   |      | 7.1.3                                 | Linear operations: what bottlenecks us?                                               |     |  |  |  |  |  |  |  |

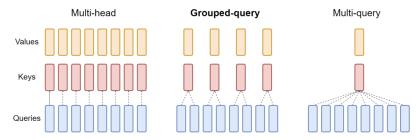

|   |      | 7.1.4                                 | What about attention?                                                                 |     |  |  |  |  |  |  |  |

|   |      | 7.1.5                                 | Theoretical estimates for LLM latency and throughput                                  | 85  |  |  |  |  |  |  |  |

|   |      | 7.1.6                                 | What about memory?                                                                    | 87  |  |  |  |  |  |  |  |

|   |      | 7.1.7                                 | Modeling throughput and latency for LLaMA 2-13B                                       | 88  |  |  |  |  |  |  |  |

|   | 7.2  | Tricks                                | for Improving Generation Throughput and Latency                                       | 89  |  |  |  |  |  |  |  |

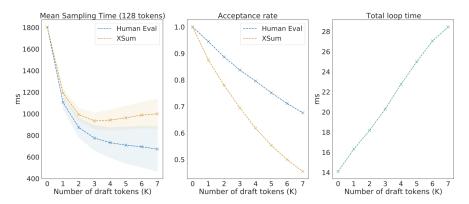

|   |      | 7.2.1                                 | Speculative Sampling                                                                  | 91  |  |  |  |  |  |  |  |

|   | 7.3  | Distrib                               | outing Inference Over Multiple Accelerators                                           | 93  |  |  |  |  |  |  |  |

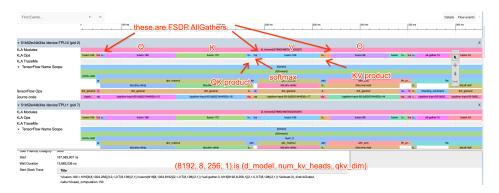

|   |      | 7.3.1                                 | Prefill                                                                               | 93  |  |  |  |  |  |  |  |

|   |      | 7.3.2                                 | Generation                                                                            | 93  |  |  |  |  |  |  |  |

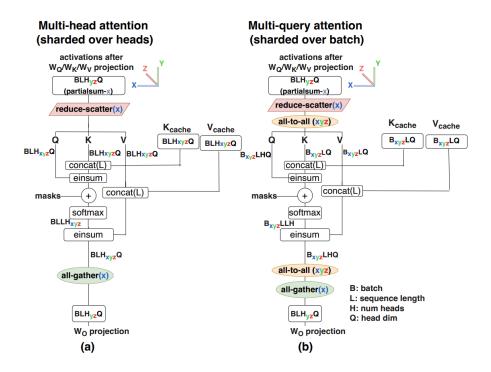

|   |      | 7.3.3                                 | Sharding the KV cache                                                                 | 94  |  |  |  |  |  |  |  |

|   | 7.4  | Desig                                 | ning an Effective Inference Engine                                                    | 96  |  |  |  |  |  |  |  |

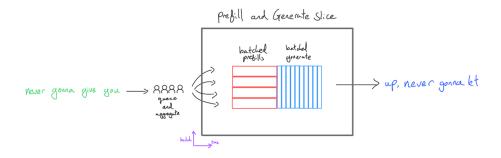

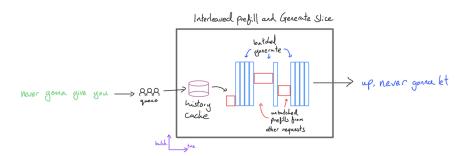

|   |      | 7.4.1                                 | Continuous Batching                                                                   | 98  |  |  |  |  |  |  |  |

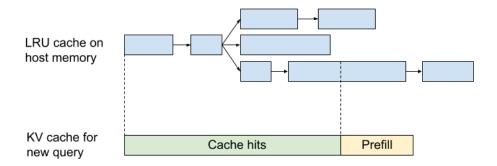

|   |      | 7.4.2                                 | Prefix Caching                                                                        | 99  |  |  |  |  |  |  |  |

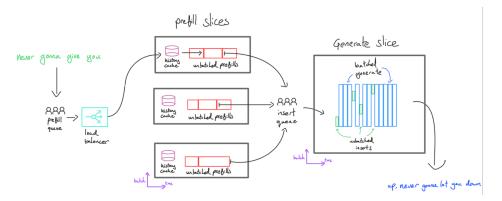

|   |      | 7.4.3                                 | Let's look at an implementation: JetStream                                            | 99  |  |  |  |  |  |  |  |

|   | 7.5  |                                       | ed Problems                                                                           | 100 |  |  |  |  |  |  |  |

|   | 7.6  |                                       | ndix                                                                                  | 102 |  |  |  |  |  |  |  |

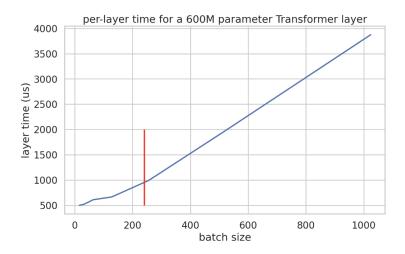

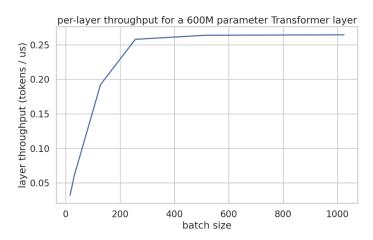

|   |      | 7.6.1                                 | Appendix A: How real is the batch size > 240 rule?                                    | 102 |  |  |  |  |  |  |  |

|   |      | 7.6.2                                 | Appendix B: 2D Weight Stationary sharding                                             |     |  |  |  |  |  |  |  |

|   |      |                                       | Appendix C: Latency bound communications                                              | 104 |  |  |  |  |  |  |  |

| 8  | Serving LLaMA 3-70B on TPUs                                   | 105 |  |  |  |  |  |  |

|----|---------------------------------------------------------------|-----|--|--|--|--|--|--|

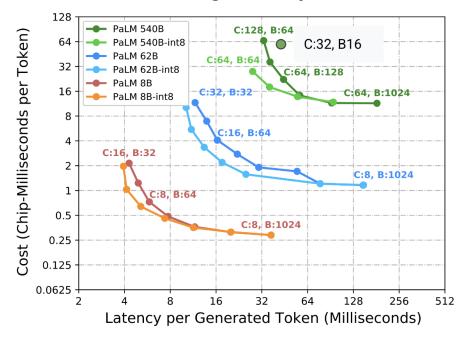

|    | 3.1 What's the LLaMA Serving Story?                           | 105 |  |  |  |  |  |  |

|    | 8.1.1 Thinking about throughput                               | 106 |  |  |  |  |  |  |

|    | 8.1.2 What About Prefill?                                     |     |  |  |  |  |  |  |

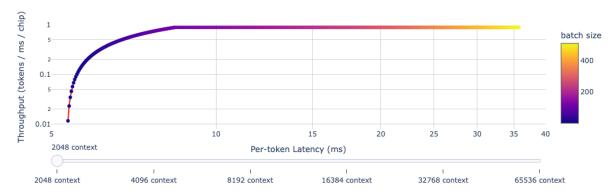

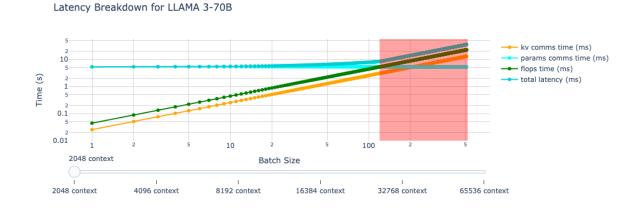

|    | 3.2 Visualizing the Latency Throughput Tradeoff               | 110 |  |  |  |  |  |  |

|    | 3.3 Worked Problems                                           |     |  |  |  |  |  |  |

| 9  | Profiling                                                     | 114 |  |  |  |  |  |  |

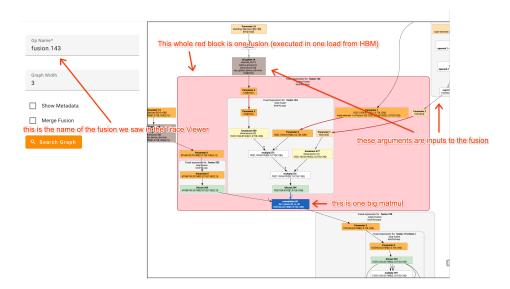

|    | 0.1 A Thousand-Foot View of the TPU Software Stack            | 114 |  |  |  |  |  |  |

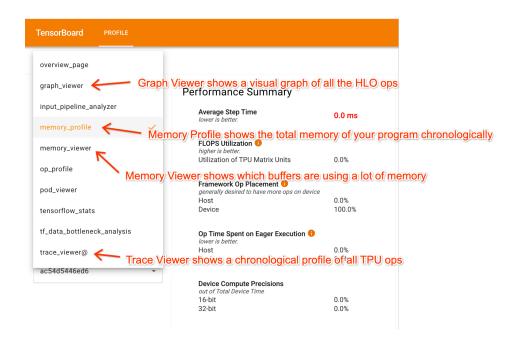

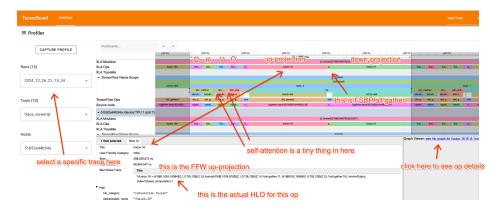

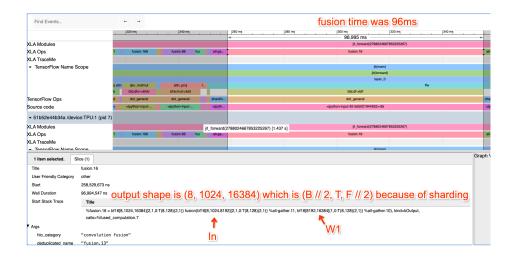

|    | 0.2 The JAX Profiler: A Multi-Purpose TPU Profiler            | 115 |  |  |  |  |  |  |

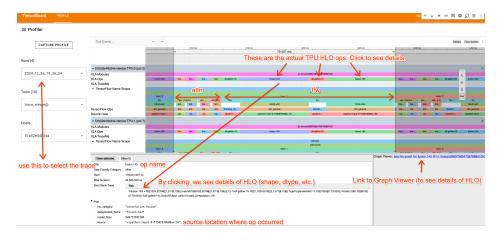

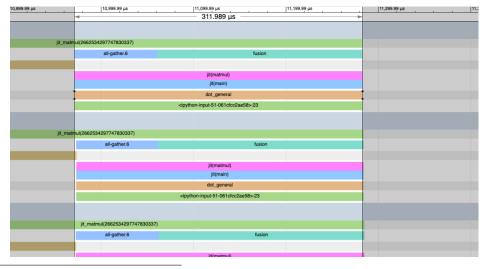

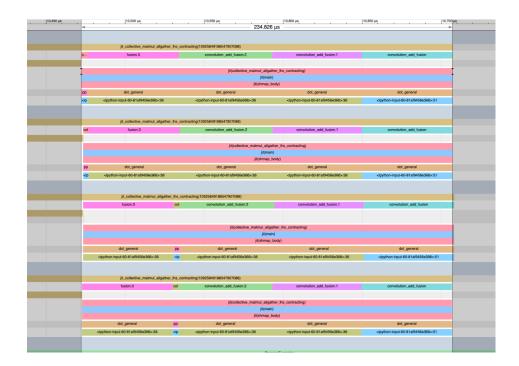

|    | 9.2.1 Trace Viewer                                            | 116 |  |  |  |  |  |  |

|    | 9.2.2 How to Read an XLA Op                                   | 117 |  |  |  |  |  |  |

|    | 9.2.3 Graph Viewer                                            | 119 |  |  |  |  |  |  |

|    | 9.2.4 Looking at a Real(ish) Example Profile                  | 119 |  |  |  |  |  |  |

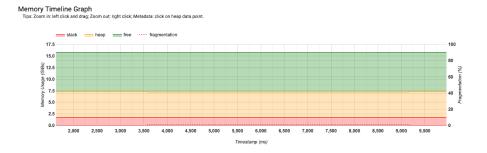

|    | 9.2.5 Memory Profile                                          |     |  |  |  |  |  |  |

|    | 0.3 Worked Problems                                           | 121 |  |  |  |  |  |  |

| 10 | Programming TPUs in JAX                                       |     |  |  |  |  |  |  |

|    | 0.1 How Does Parallelism Work in JAX?                         | 122 |  |  |  |  |  |  |

|    | 10.1.1 jax.jit: the automatic parallelism solution            | 122 |  |  |  |  |  |  |

|    | 10.1.2 shard_map: explicit parallelism control over a program | 124 |  |  |  |  |  |  |

|    | 0.2 Worked Problems                                           | 127 |  |  |  |  |  |  |

| 11 | Conclusions                                                   | 129 |  |  |  |  |  |  |

|    | 1.1 Acknowledgments                                           | 129 |  |  |  |  |  |  |

|    | 1.2 Further Reading                                           | 129 |  |  |  |  |  |  |

|    | 1.3 Feedback                                                  | 130 |  |  |  |  |  |  |

| 12 | Solutions                                                     | 131 |  |  |  |  |  |  |

# Introduction

Much of deep learning still boils down to a kind of black magic, but optimizing the performance of your models doesn't have to — even at huge scale! Relatively simple principles apply everywhere — from dealing with a single accelerator to tens of thousands — and understanding them lets you do many useful things:

- · Ballpark how close parts of your model are to their theoretical optimum.

- Make informed choices about different parallelism schemes at different scales (how you split the computation across multiple devices).

- Estimate the cost and time required to train and run large Transformer models.

- Design algorithms that take advantage of specific hardware affordances.

- Design hardware driven by an explicit understanding of what limits current algorithm performance.

**Expected background:** We're going to assume you have a basic understanding of LLMs and the Transformer architecture but not necessarily how they operate at scale. You should know the basics of LLM training and ideally have some basic familiarity with JAX. Some useful background reading might include this blog post<sup>1</sup> on the Transformer architecture and the original Transformer paper. Also check the list in the conclusion for more useful concurrent and future reading.

**Goals & Feedback**: By the end, you should feel comfortable estimating the best parallelism scheme for a Transformer model on a given hardware platform, and roughly how long training and inference should take. If you don't, email us or leave a comment! We'd love to know how we could make this clearer.

### Why should you care?

Three or four years ago, I don't think most ML researchers would have needed to understand any of the content in this book. But today even "small" models run so close to hardware limits that doing novel research requires you to think about efficiency at scale.<sup>2</sup> A 20% win on benchmarks is irrelevant if it comes at a 20% cost to roofline efficiency. Promising model architectures routinely fail either because they *can't* run efficiently at scale or because no one puts in the work to make them do so.

The goal of "model scaling" is to be able to increase the number of chips used for training or inference while achieving a proportional, linear increase in throughput. This is known as "strong scaling". Although adding additional chips ("parallelism") usually decreases the computation time, it also comes at the cost of added communication between chips. When communication takes longer than computation we become "communication bound" and cannot scale strongly. If we understand our hardware well enough to antici-

<sup>1</sup>https://jalammar.github.io/illustrated-transformer/

<sup>&</sup>lt;sup>2</sup>Historically, ML research has followed something of a tick-tock cycle between systems innovations and software improvements. Alex Krizhevsky had to write unholy CUDA code to make CNNs fast but within a couple years, libraries like Theano and TensorFlow meant you didn't have to. Maybe that will happen here too and everything in this book will be abstracted away in a few years. But scaling laws have pushed our models perpetually to the very frontier of our hardware, and it seems likely that, in the near future, doing cutting edge research will be inextricably tied to an understanding of how to efficiently scale models to large hardware topologies.

<sup>&</sup>lt;sup>3</sup>As your computation time decreases, you also typically face bottlenecks at the level of a single chip. Your shiny new TPU or GPU may be rated to perform 500 trillion operations-per-second, but if you aren't careful it can just as easily do a tenth of that if it's bogged down moving parameters around in memory. The interplay of per-chip computation, memory bandwidth, and total memory is critical to the scaling story.

pate where these bottlenecks will arise, we can design or reconfigure our models to avoid them.<sup>4</sup>

Our goal in this book is to explain how TPU (and GPU) hardware works and how the Transformer architecture has evolved to perform well on current hardware. We hope this will be useful both for researchers designing new architectures and for engineers working to make the current generation of LLMs run fast.

# **High-Level Outline**

The overall structure of this book is as follows::

Section 1 explains roofline analysis and what factors can limit our ability to scale (communication, computation, and memory). Section 2 and Section 3 talk in detail about how TPUs and modern GPUs work, both as individual chips and — of critical importance — as an interconnected system with inter-chip links of limited bandwidth and latency. We'll answer questions like:

- How long should a matrix multiply of a certain size take? At what point is it bound by compute or by memory or communication bandwidth?

- How are TPUs wired together to form training clusters? How much bandwidth does each part of the system have?

- · How long does it take to gather, scatter, or re-distribute arrays across multiple TPUs?

- · How do we efficiently multiply matrices that are distributed differently across devices?

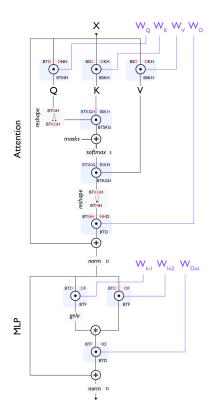

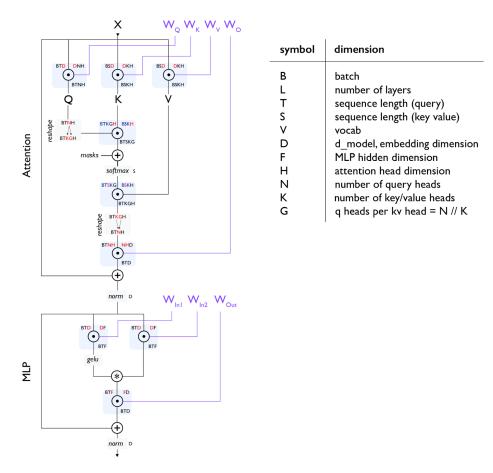

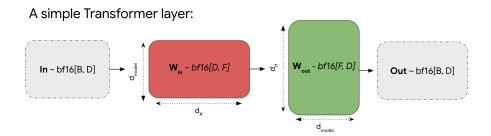

Five years ago ML had a colorful landscape of architectures — ConvNets, LSTMs, MLPs, Transformers — but now we mostly just have the Transformer. We strongly believe it's worth understanding every piece of the Transformer architecture: the exact sizes of every matrix, where normalization occurs, how many parameters and FLOPs<sup>5</sup> are in each part. Section 4 goes through this "Transformer math" carefully, showing how to count the parameters and FLOPs for both training and inference. This tells us how much memory our model will use, how much time we'll spend on compute or comms, and when attention will become important relative to the feed-forward blocks.

<sup>&</sup>lt;sup>4</sup>Hardware designers face the inverse problem: building hardware that provides just enough compute, bandwidth, and memory for our algorithms while minimizing cost. You can imagine how stressful this "co-design" problem is: you have to bet on what algorithms will look like when the first chips actually become available, often 2 to 3 years down the road. The story of the TPU is a resounding success in this game. Matrix multiplication is a unique algorithm in the sense that it uses far more FLOPs per byte of memory than almost any other (N FLOPs per byte), and early TPUs and their systolic array architecture achieved far better perf / \$ than GPUs did at the time they were built. TPUs were designed for ML workloads, and GPUs with their TensorCores are rapidly changing to fill this niche as well. But you can imagine how costly it would have been if neural networks had not taken off, or had changed in some fundamental way that TPUs (which are inherently less flexible than GPUs) could not handle.

<sup>&</sup>lt;sup>5</sup>FLoating point OPs, basically the total number of adds and multiplies required. While many sources take FLOPs to mean "operations per second", we use FLOPs/s to indicate that explicitly.

| symbol | dimension                    |

|--------|------------------------------|

| В      | batch<br>number of layers    |

| T      | sequence length (query)      |

| S      | sequence length (key value)  |

| ٧      | vocab                        |

| D      | d_model, embedding dimension |

| F      | MLP hidden dimension         |

| Н      | attention head dimension     |

| Ν      | number of query heads        |

| K      | number of key/value heads    |

| G      | q heads per kv head = N // K |

Figure 1: A standard Transformer layer with each matrix multiplication (matmul) shown as a dot inside a circle. All parameters (excluding norms) are shown in purple. Section 4 walks through this diagram in more detail.

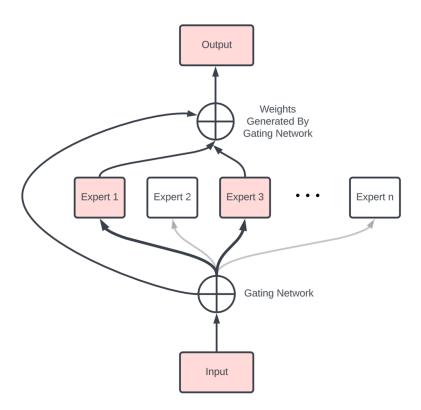

Section 5: Training and Section 7: Inference are the core of this essay, where we discuss the fundamental question: given a model of some size and some number of chips, how do I parallelize my model to stay in the "strong scaling" regime? This is a simple question with a surprisingly complicated answer. At a high level, there are 4 primary parallelism techniques used to split models over multiple chips (data, tensor, pipeline and expert), and a number of other techniques to reduce the memory requirements (rematerialisation, optimizer/model sharding aka ZeRO, host offload, gradient accumulation). We discuss many of these here.

We hope by the end of these sections you should be able to choose among them yourself for new architectures or settings. Section 6 and Section 8 are practical tutorials that apply these concepts to LLaMA-3, a popular open-source model.

Finally, Section 9 and Section 10 look at how to implement some of these ideas in JAX and how to profile and debug your code when things go wrong.

Throughout we try to give you problems to work for yourself. Please feel no pressure to read all the sections or read them in order. And please leave feedback. For the time being, this is a draft and will continue to be revised. Thank you!

We'd like to acknowledge James Bradbury and Reiner Pope who derived many of the ideas in this doc but have since left Google.

### 1 Intro to Rooflines

When we run algorithms on hardware, we're bounded by three things: how fast our computer can do math (OPs/second), the bandwidth available for moving data around (bytes/second), and the total memory available to store data (bytes). These constraints let us upper and lower bound the time of a given computation.

### 1.1 Where Does the Time Go?

Let's start with an extremely simple question: why does an algorithm take 50ms instead of 50s or 5ms? What is actually happening within the model that takes substantial time and how long should we expect it to take?

**Computation:** A deep learning model is effectively a bunch of matrix multiplications, each composed of floating-point multiplication and addition 'operations' (FLOPs). Our accelerator speed determines how long these take to compute:

$$T_{\text{math}} = \frac{\text{Computation FLOPs}}{\text{Accelerator FLOPs/s}}$$

For instance, an NVIDIA H100 can perform about 9.89e14 bfloat $16^1$  FLOPs/s while a TPU v6e can perform 9.1e14 FLOPs/s. That means doing 1e12 FLOPs on an H100 will take (roughly) 1e12 / 9.89e14 = 1.01ms and 1e12 / 9.1e14 = 1.1ms on a TPU v6e.<sup>2</sup>

**Communication within a chip:** Within an accelerator, tensors need to be transferred between on-chip memory (HBM) and the compute cores. You'll see the bandwidth of this link referred to as "HBM bandwidth" On an H100, this is about 3.35TB/s <sup>4</sup> and on TPU v6e this is about 1.6TB/s <sup>5</sup>.

**Communication between chips:** When we distribute a model *across multiple accelerators*, tensors frequently need to be transferred between them. There are often a few options for this on our hardware (ICI, DCN, and PCIe), each with different bandwidths.

Whether the communication is within a chip or between chips, we measure this in bytes/s and estimate the total communication time with:

$$T_{\rm comms} = {{

m Communication Bytes} \over {

m Network/Memory Bandwidth Bytes/s}}$$

Typically (but not always), computation within a single chip can be overlapped with communication within a chip and between chips. This means we can lower-bound training and inference time by using the maximum of computation and communication time. We can also upper-bound with their sum. In practice, we optimize against the maximum as the algebra is simpler and we can usually come close to this bound by overlapping our communication and computation. If we optimize with the maximum in mind then the lower and upper bounds differ by at most a factor of 2 since  $T_{\rm math} + T_{\rm comms} \le 2 * \max(T_{\rm math}, T_{\rm comms})$ . We then increase accuracy beyond this by modeling 'overlap regions' and overheads, which can be informed by profiling your specific model and target system.

$$T_{

m lower} = {

m max}(T_{

m math}, T_{

m comms})$$

$$T_{

m upper} = T_{

m math} + T_{

m comms}$$

<sup>&</sup>lt;sup>1</sup>bf16 is short for bfloat16, a 16-bit floating point format often used in ML.

<sup>&</sup>lt;sup>2</sup>Note that these chips are priced differently, and this comparison does not normalize to cost.

<sup>&</sup>lt;sup>3</sup>NVIDIA also calls this "memory bandwidth."

<sup>4</sup>https://www.nvidia.com/en-us/data-center/h100/

<sup>5</sup>https://cloud.google.com/tpu/docs/v6e

If we assume we can perfectly overlap communication and computation, when  $T_{\rm math} > T_{\rm comms}$ , we see full utilization from our hardware. We call this being "compute-bound". When  $T_{\rm comms} > T_{\rm math}$ , we tend to be "communication-bound" and at least some fraction of our accelerator FLOPs/s is wasted waiting for data to be passed around. One way to tell if an operation will be compute or communication-bound is to look at its "arithmetic intensity" or "operational intensity".

**Definition:** the arithmetic intensity of an algorithm is given by the ratio of the total FLOPs it performs to the number of bytes it needs to communicate — either within a chip or between chips.

$$\mbox{Arithmetic Intensity} = \frac{\mbox{Computation FLOPs}}{\mbox{Communication Bytes}}$$

Arithmetic intensity measures the "FLOPs per byte" of a given operation. To a first order, when our arithmetic intensity is high,  $T_{\rm math}$  is large compared to  $T_{\rm comms}$  and we typically use most of the available FLOPs. When the opposite is true, we spent more time on comms and waste FLOPs. The point where this crossover happens is the "peak arithmetic intensity" of our hardware, the ratio of peak accelerator FLOPs/s to accelerator bandwidth.

$$\begin{split} T_{\text{math}} > T_{\text{comms}} &\Leftrightarrow \frac{\text{Computation FLOPs}}{\text{Accelerator FLOPs/s}} > \frac{\text{Communication Bytes}}{\text{Bandwidth Bytes/s}} \\ &\Leftrightarrow \frac{\text{Computation FLOPs}}{\text{Communication Bytes}} > \frac{\text{Accelerator FLOPs/s}}{\text{Bandwidth Bytes/s}} \\ &\Leftrightarrow \text{Intensity(Computation)} > \text{Intensity(Accelerator)} \end{split}$$

The quantity Intensity (Accelerator) is the arithmetic intensity at which our accelerator achieves its peak FLOPs/s. For the TPU v5e MXU, this is about 240 FLOPs/byte<sup>6</sup>, since the TPU can perform 1.97e14 FLOPs/s and load 8.2e11 bytes/s from HBM. That means if an algorithm has a lower arithmetic intensity than 240<sup>7</sup> FLOPs/byte, it will be bound by byte loading and thus we won't make good use of our hardware. Let's look at one such example:

**Example (dot product):** to compute the dot product of two vectors in bfloat16 precision,  $\mathbf{x} \cdot \mathbf{y}$ : bf16[N], bf16[N]  $\rightarrow$  bf16[1], we need to load x and y from memory, each of which has 2\*N=2N bytes, perform N multiplications and N-1 additions, and write 2 bytes back into HBM.

$$\text{Intensity(dot product)} = \frac{\text{Total FLOPs}}{\text{Total Bytes}} = \frac{N+N-1}{2N+2N+2} = \frac{2N-1}{4N+2} \rightarrow \frac{1}{2}$$

as  $N \to \infty$ . So the dot product has an arithmetic intensity of  $\frac{1}{2}$  or, put another way, the dot product does 0.5 floating point operations per byte loaded. This means our arithmetic intensity is lower than that of our hardware and we will be communication-bound.<sup>8</sup>

<sup>&</sup>lt;sup>6</sup>The MXU is the matrix multiply unit on the TPU. We specify this here because the TPU has other accelerators like the VPU that are responsible for elementwise operations that have a different peak FLOPs/s.

<sup>&</sup>lt;sup>7</sup>This is only true if the algorithm loads its weights from HBM and runs in the MXU. As we'll discuss in the next section, we can sometimes store parameters in VMEM which has a much higher bandwidth. Many algorithms also run in the VPU, which has different performance characteristics.

<sup>&</sup>lt;sup>8</sup>The 240 number above is not the correct comparison here since, as you will see in the next section, a dot-product is performed on the VPU and not the MXU. The TPU v5p VPU can do roughly 7e12 FLOPs / second, so its critical intensity is around 3, which means we are still somewhat comms-bound here. Either way, the fact that our intensity is low and constant means it is difficult on most hardware to be compute-bound.

### 1.1.1 Visualizing rooflines

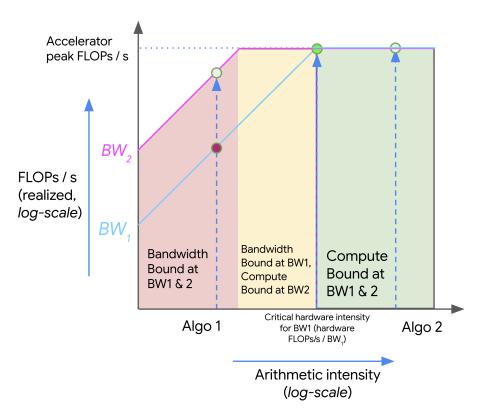

We can visualize the tradeoff between memory and compute using a **roofline plot**, which plots the peak achievable FLOPs/s (throughput) of an algorithm on our hardware (the y-axis) against the arithmetic intensity of that algorithm (the x-axis). Here's an example log-log plot:

Figure 2: An example roofline plot showing two algorithms with different arithmetic intensities (Algo 1 and Algo 2) and their corresponding theoretical peak throughput under different bandwidths (BW1 and BW2). In the red area, an algorithm is bandwidth bound at both bandwidths and is wasting some fraction of the hardware's peak FLOPs/s. The yellow area is bandwidth-bound only at the lower bandwidth (BW1). The green area is compute-bound at all bandwidths. Here, we are using the peak FLOPs/s of the accelerator and increasing bandwidth or improving intensity yield no benefit."

Above, as the intensity increases (moving left to right), we initially see a linear increase in the performance of our algorithm (in FLOPs/s) until we hit the critical arithmetic intensity of the hardware, 240 in the case of the TPU v5e. Any algorithm with a lower intensity will be bandwidth (BW) bound and limited by the peak memory bandwidth (shown in red). Any algorithm to the right will fully utilize our FLOPs (shown in green). Here, Algo 1 is comms-bound and uses only a fraction of the total hardware FLOPs/s. Algo 2 is compute-bound. We can generally improve the performance of an algorithm either by increasing its arithmetic intensity or by increasing the memory bandwidth available (moving from BW1 to BW2).

### 1.1.2 Matrix multiplication

Let's look at our soon-to-be favorite algorithm: matrix multiplication (aka matmul). We write  $X * Y \to Z$  where X has shape bf16[B, D], Y has shape bf16[D, F], and Z has shape bf16[B, F]. To do the matmul

we need to load 2DF + 2BD bytes, perform 2BDF FLOPs, and write 2BF bytes back. 910 Thus:

$$Intensity(matmul) = \frac{2BDF}{2BD + 2DF + 2BF} = \frac{BDF}{BD + DF + BF}$$

We can get a nice simplification if we assume our local "batch size" B is small relative to D and F. Then we get

$$\frac{BDF}{BD + DF + BF} \cong \frac{BDF}{DF} = B \tag{1}$$

Intensity(matmul) > Intensity(TPU)

$$\implies B > \frac{1.97e14}{8.20e11} = 240$$

(2)

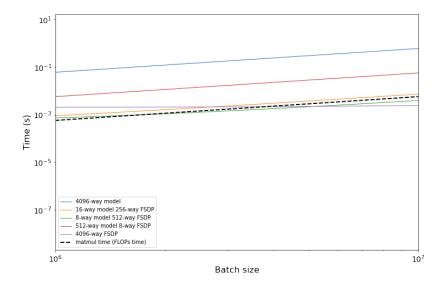

This is a reasonable assumption for Transformer matmuls since for most of our models we have our local batch size in tokens B < 1024 but D and F > 8000. Thus we become compute-bound when our local batch size is greater than 240 tokens, a very simple rule!

**Takeaway:** for a bfloat16 matmul to be compute-bound on most TPUs, we need our local batch size in tokens to be greater than 240.

This comes with a few notable caveats we'll explore in the problems below, particularly with respect to quantization (e.g. if we quantize our activations but still do full-precision FLOPs), but it's a good rule to remember. For GPUs, this number is slightly higher (closer to 300), but the same conclusion generally holds. We'll discuss the lower-level GPU and TPU details in the next section.

### 1.1.3 Network communication rooflines

All the rooflines we've discussed so far have been memory-bandwidth rooflines, all within a single chip. This shouldn't be taken as a rule. In fact, most of the rooflines we'll care about in this book involve communication between chips: usually matrix multiplications that involve matrices sharded across multiple TPUs.

To pick a somewhat contrived example, say we want to multiply two big matrices  $X \sim \text{bfloat16[B, D]}$  and  $Y \sim \text{bfloat16[D, F]}$  which are split evenly across 2 TPUs/GPUs (along the D dimension). To do this multiplication (as we'll see in Section 3), we can multiply half of each matrix on each TPU (A = X[:, :D // 2] @ Y[:D // 2, :] on TPU 0 and B = X[:, D // 2:] @ Y[D // 2:, :] on TPU 1) and then copy the resulting "partial sums" to the other TPU and add them together. Say we can copy 4.5e10 bytes in each direction and perform 1.97e14 FLOPs/s on each chip. What are  $T_{\text{math}}$  and  $T_{\text{comms}}$ ?

$T_{\mathrm{math}}$  is clearly half of what it was before, since each TPU is doing half the work, i.e. <sup>11</sup>

$$T_{\mathsf{math}} = \frac{2BDF}{2 \cdot \mathsf{Accelerator}\,\mathsf{FLOPs/s}} = \frac{BDF}{1.97e14}$$

Now what about  $T_{\rm comms}$ ? This now refers to the communication time between chips! This is just the total bytes sent divided by the network bandwidth, i.e.

$$T_{\text{comms}} = \frac{2BF}{\text{Network Bandwidth}} = \frac{2BF}{4.5e10}$$

$<sup>^9</sup>$ Technically we perform  $BF \times (2D-1)$  FLOPs but this is close enough. This comes from BDF multiplications and  $BF \times (D-1)$  additions. Section 4 has more details.

<sup>&</sup>lt;sup>10</sup>Although the output of a matmul is technically float32 we usually cast down to bfloat16 before copying back to HBM.

<sup>&</sup>lt;sup>11</sup>We're ignoring the FLOPs required to add the two partial sums together (another DF additions), but this is basically negigible.

Therefore we become compute-bound (now with respect to the inter-chip network) when Intensity (matmul (2-chips)) > Intensity (TPU w.r.t. inter-chip network) or equivalently when  $\frac{BDF}{2BF} = \frac{D}{2} > \frac{1.97e14}{4.5e10} = 4377$  or D > 8755. Note that, unlike before, the critical threshhold now depends on D and not B! Try to think why that is. This is just one such example, but we highlight that this kind of roofline is critical to knowing when we can parallelize an operation across multiple TPUs.

# 1.2 Worked problems

# Exercise 1.1 [int8 matmul]

Say we want to do  $X[B,D] \cdot_D Y[D,F] \to Z[B,F]$  in int8 precision (1 byte per parameter) instead of bfloat16.<sup>12</sup>

- 1. How many bytes need to be loaded from memory? How many need to be written back to memory?

- 2. How many total OPs are performed?

- 3. What is the arithmetic intensity?

- 4. What is a roofline estimate for  $T_{\mathsf{math}}$  and  $T_{\mathsf{comms}}$ ? What are reasonable upper and lower bounds for the runtime of the whole operation?

Assume our HBM bandwidth is 8.1e11 bytes/s and our int8 peak OPs/s is 3.94e14.

# Exercise 1.2 [int8 matmul + bf16 matmul]

In practice we often do different weight vs. activation quantization, so we might store our weights in very low precision but keep activations (and compute) in a higher precision. Say we want to quantize our weights in int8 but keep activations (and compute) in bfloat16. At what batch size do we become compute bound? Assume 1.97e14 bfloat16 FLOPs/s.

Hint: this means specifically bfloat16[B, D] \* int8[D, F] -> bfloat16[B, F] where B is the "batch size".

### Exercise 1.3

For the problem above, make a roofline plot of peak FLOPs vs. B for several values of D and F.

### **Exercise 1.4**

What if we wanted to perform int8[B, D]  $*_D$  int8[B, D, F]  $\rightarrow$  int8[B, F] where we imagine having a different matrix for each batch element. What is the arithmetic intensity of this operation?

# **Exercise 1.5** [Memory Rooflines for GPUs]

Using the spec sheet provided by NVIDIA for the H100<sup>13</sup>, calculate the batch size at which a matrix multiplication will become compute-bound. *Note that the Tensor Core FLOPs numbers are twice the true value since they're only achievable with structured sparsity.*

$<sup>^{12}\</sup>text{Here}$  and throughout we'll use the notation  $A\cdot_D B$  to indicate that the multiplication is performing a contraction over the D dimension. This is an abuse of einsum notation.

<sup>13</sup>https://www.nvidia.com/en-us/data-center/h100/

# 2 All About TPUs

This section is all about how TPUs work, how they're networked together to enable multi-chip training and inference, and how this affects the performance of our favorite algorithms. There's even some good stuff for GPU users too!

### 2.1 What is a TPU?

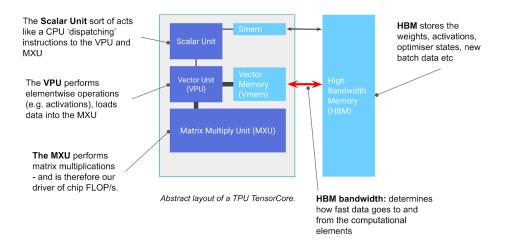

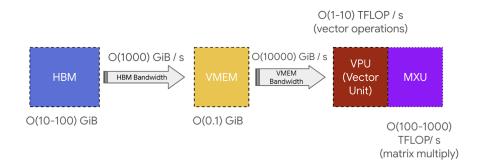

A TPU is basically a compute core that specializes in matrix multiplication (called a TensorCore) attached to a stack of fast memory (called high-bandwidth memory or HBM). Here's a diagram:

Figure 3: the basic components of a TPU chip. The TensorCore is the gray left-hand box, containing the matrix-multiply unit (MXU), vector unit (VPU), and vector memory (VMEM).

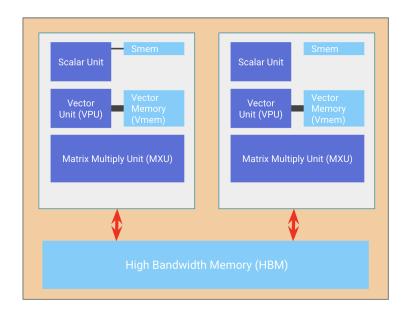

You can think of the TensorCore as basically just being a really good matrix multiplication machine, but it has a few other functions worth noting. The TensorCore has three key units:

- The **MXU** (Matrix Multiply Unit) is the core of the TensorCore. For most TPU generations, it performs one bfloat16[8,128] @ bf16[128,128] -> f32[8,128] matrix multiply<sup>1</sup> every 8 cycles using a systolic array (see Appendix B for details).

- This is about 5e13 bf16 FLOPs/s per MXU at 1.5GHz on TPU v5e. Most TensorCores have 2 or 4 MXUs, so e.g. the total bf16 FLOPs/s for TPU v5e is 2e14.

- TPUs also support lower precision matmuls with higher throughput (e.g. each TPU v5e MXU can do 4e14 int8 OPs/s).

- The VPU (Vector Processing Unit) performs general mathematical operations like ReLU activations or pointwise addition or multiplication between vectors. Reductions (sums) are also performed here. Appendix C provides more details.

- VMEM (Vector Memory) is an on-chip scratchpad located in the TensorCore, close to the compute

units. It is much smaller than HBM (for example, 128 MiB on TPU v5e) but has a much higher bandwidth to the MXU. VMEM operates somewhat like an L1/L2 cache on CPUs but is much larger and

programmer-controlled. Data in HBM needs to be copied into VMEM before the TensorCore can do

any computation with it.

<sup>&</sup>lt;sup>1</sup>TPU v6e (Trillium) has a 256x256 MXU, while all previous generations use 128x128

**TPUs are very, very fast at matrix multiplication.** It's mainly what they do and they do it well. TPU v5p, one of the most powerful TPUs to date, can do 2.5e14 bf16 FLOPs / second / core or 5e14 bf16 FLOPs / sec / chip. A single pod of 8960 chips can do 4 exaflops / second. That's a lot. That's one of the most powerful supercomputers in the world. And Google has a lot of them. <sup>2</sup>

The diagram above also includes a few other components like SMEM and the scalar unit, which are used for control flow handling and are discussed briefly in Appendix C, but aren't crucial to understand. On the other hand, HBM is important and fairly simple:

- **HBM** (High Bandwidth Memory) is a big chunk of fast memory that stores tensors for use by the TensorCore. HBM usually has capacity on the order of tens of gigabytes (for example, TPU v5e has 16GiB of HBM).

- When needed for a computation, tensors are streamed out of HBM through VMEM (see below) into the MXU and the result is written from VMEM back to HBM.

- The bandwidth between HBM and the TensorCore (through VMEM) is known as "HBM bandwidth" (usually around 1-2TB/sec) and limits how fast computation can be done in memory-bound work-loads.

Generally, all TPU operations are pipelined and overlapped. To perform a matmul  $X \cdot A \to Y$ , a TPU would first need to copy chunks of matrices A and X from HBM into VMEM, then load them into the MXU which multiplies chunks of 8x128 (for X) and 128x128 (for A), then copy the result chunk by chunk back to HBM. To do this efficiently, the matmul is pipelined so the copies to/from VMEM are overlapped with the MXU work. This allows the MXU to continue working instead of waiting on memory transfers, keeping matmuls compute-bound, not memory-bound.

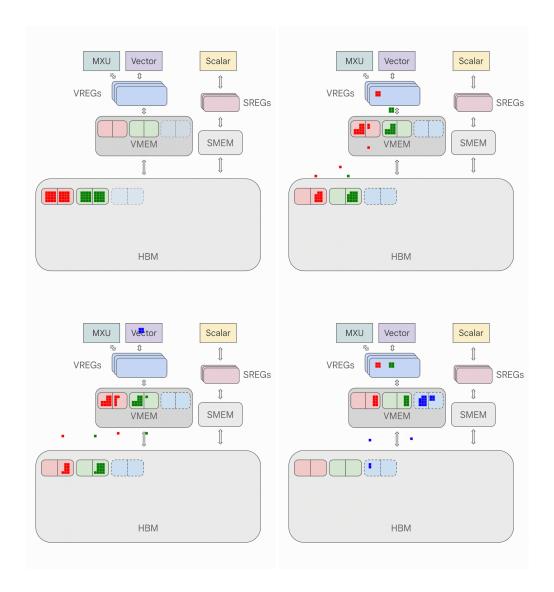

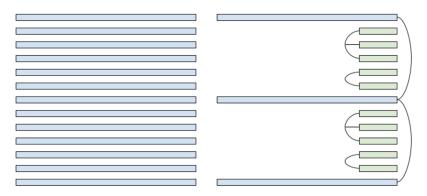

Here's an example of how you might perform an elementwise product from HBM. These are excerpts from an animation found in the online version of the book:

$<sup>^2</sup>$ TPUs, and their systolic arrays in particular, are such powerful hardware accelerators because matrix multiplication is one of the few algorithms that uses  $O(n^3)$  compute for  $O(n^2)$  bytes. That makes it very easy for an ordinary ALU to be bottlenecked by compute and not by memory bandwidth.

A matmul would look nearly identical except it would load into the MXU instead of the VPU/Vector unit, and the loads and stores would occur in a different order, since the same weight chunk is used for multiple chunks of activations. You can see chunks of data streaming into VMEM, then into the VREGs (vector registers), then into the Vector Unit, then back into VMEM and HBM. As we're about to see, if the load from HBM to VMEM is slower than the FLOPs in the Vector Unit (or MXU), we become "bandwidth bound" since we're starving the VPU or MXU of work.

**Takeaway:** TPUs are very simple. They load weights from HBM into VMEM, then from VMEM into a systolic array which can perform around 200 trillion multiply-adds per second. The HBM  $\leftrightarrow$  VMEM and VMEM  $\leftrightarrow$  systolic array bandwidths set fundamental limits on what computations TPUs can do efficiently.

**VMEM** and arithmetic intensity: VMEM is much smaller than HBM but it has a much higher bandwidth to the MXU. As we saw in Section 1, this means if an algorithm can fit all its inputs/outputs in VMEM, it's much less likely to hit communication bottlenecks. This is particularly helpful when a computation has

poor arithmetic intensity: VMEM bandwidth is around 22x higher than HBM bandwidth which means an MXU operation reading from/writing to VMEM requires an arithmetic intensity of only 10-20 to achieve peak FLOPs utilization. That means if we can fit our weights into VMEM instead of HBM, our matrix multiplications can be FLOPs bound at much smaller batch sizes. And it means algorithms that fundamentally have a lower arithmetic intensity can still be efficient. VMEM is just so small this is often a challenge.<sup>3</sup>

A TPU chip typically (but not always) consists of two TPU cores which share memory and can be thought of as one large accelerator with twice the FLOPs (known as a "megacore" configuration). This has been true since TPU v4. Older TPU chips they have separate memory and are regarded as two separate accelerators (TPU v3 and older). Inference-optimized chips like the TPU v5e only have one TPU core per chip.

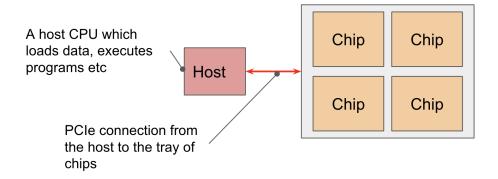

Chips are arranged in sets of 4 on a 'tray' connected to a CPU host via PCle network. This is the format most readers will be familiar with, 4 chips (8 cores, though usually treated as 4 logical megacores) exposed through Colab or a single TPU-VM. For inference chips like the TPU v5e, we have 2 trays per host, instead of 1, but also only 1 core per chip, giving us 8 chips = 8 cores. <sup>4</sup>

<sup>&</sup>lt;sup>3</sup>We sometimes talk about VMEM prefetching, which refers to loading weights ahead of time in VMEM so we can mask the cost of loading for our matmuls. For instance, in a normal Transformer we can sometimes load our big feed-forward weights into VMEM during attention, which can hide the cost of the weight load if we're memory bandwidth bound. This requires our weights to be small enough or sharded enough to fit a single layer into VMEM with space to spare.

<sup>&</sup>lt;sup>4</sup>On Cloud TPU VMs, each tray is exposed as part of a separate VM, so there are once again 4 cores visible.

**PCIe bandwidth is limited:** Like the HBM ↔ VMEM link, the CPU ↔ HBM PCIe connection has a specific bandwidth that limits how quickly you can load from host memory to HBM or vice-versa. PCIe bandwidth for TPU v4 is 16GB / second each way, for example, so close to 100x slower than HBM. We *can* load/offload data into the host (CPU) RAM, but not very quickly.

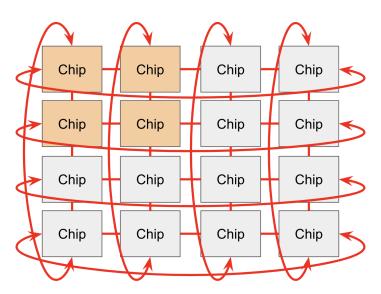

# 2.2 TPU Networking

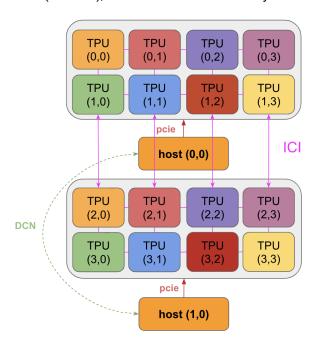

Chips are connected to each other through the ICI network in a Pod. In older generations (TPU v2 and TPU v3), inference chips (e.g. TPU v5e), and Trilium (TPU v6e), ICI ("inter-chip interconnects") connects the 4 nearest neighbors (with edge links to form a 2D torus). TPU v4 and TPU v5p are connected to the nearest 6 neighbors (forming a 3D torus). Note these connections do **not** go through their hosts, they are direct links between chips.

The toroidal structure reduces the maximum distance between any two nodes from N to N/2, making communication much faster. TPUs also have a "twisted torus" configuration that wraps the torus in a Mobiusstrip like topology to further reduce the average distance between nodes.

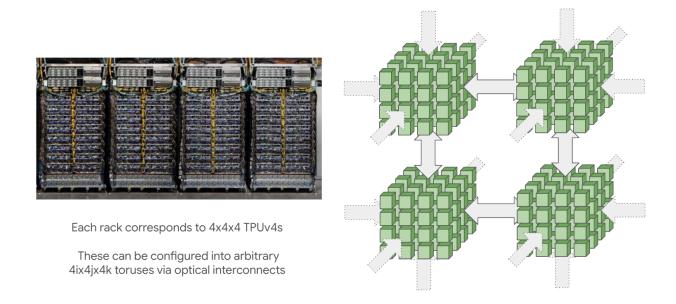

**TPU pods (connected by ICI) can get really big:** the maximum pod size (called a superpod) is 16x16x16 for TPU v4 and 16x20x28 for TPU v5p. These large pods are composed of reconfigurable cubes of 4x4x4 chips

connected by optical wraparound links<sup>5</sup> that we can reconfigure to connect very large topologies.

Smaller topologies (e.g. 2x2x1, 2x2x2) can also be requested, albeit with no wraparounds. This is an important caveat, since it typically doubles the time of most communication. Any multiple of a full cube (e.g. 4x4x4 or 4x4x8) will have wraparounds provided by the optical switches.<sup>6</sup>

Smaller slices can also be requested.

TPU v5e and Trillium pods consist of a single 16x16 2D torus with wraparounds along any axis of size 16 (meaning an 8x16 has a wraparound on the long axis). TPUs v5e and v6e (Trillium) cannot expand beyond a 16x16 torus but pods can still communicate with each other over standard data-center networking (DCN), which connects TPU hosts to each other. Again, smaller topologies can be requested without wraps on dims < 16.

<sup>&</sup>lt;sup>5</sup>The optical switch is simply a reconfigurable connection with the same ICI bandwidth. It just lets us connect cubes while retaining a wraparound link

<sup>&</sup>lt;sup>6</sup>Note that a 2x2x4 won't have any wraparounds since they are provided by the optical switches which are only available on a full cube. A TPU v5e 8x16 *will* have a wraparound on the longer axis, however, since it doesn't use reconfigurable optical networking.

This nearest-neighbor connectivity is a key difference between TPUs and GPUs. GPUs are connected with a hierarchy of switches that approximate a point-to-point connection between every GPU, rather than using local connections like a TPU. Typically, GPUs within a node (8 GPUs for H100 or as many as 500 for B200) are directly connected, while larger topologies require O(log(N)) hops between each GPU. On the one hand, that means GPUs can send arbitrary data within a node in a single low-latency hop. On the other hand, TPUs are dramatically cheaper (since NVLink switches are expensive) and simpler to wire together, and can scale to much larger topologies because the number of links per device and the bandwidth per device is constant.

ICI is very fast relative to DCN, but is still slower than HBM bandwidth. For instance, a TPU v5p<sup>7</sup> has:

- 2.5e12 bytes/s (2.5 TB/s) of HBM bandwidth per chip.

- 9e10 bytes/s (908 GB/s) of ICI bandwidth per axis, with 3 axes per chip.

- 2.5e10 bytes/s (25 GB/s) of DCN (egress) bandwidth per host. Since we typically have 8 TPUs per host, this is really closer to 3.1e9 bytes / s / chip.

This means that when we split models across multiple chips, we need to be careful to avoid bottle-necking the MXU with slower cross-device communication.

**Multi-slice training:** A set of ICI-connected TPUs is called a **slice**. Different slices can be connected between each other using DCN, for instance to link slices on different pods. Since DCN is a much slower connection than ICI, one should try to limit how much our computation has to wait for data from DCN. DCN is host-to-host, so to transfer buffers from TPU to TPU over DCN, we first need to transfer over PCIe to the host, then egress over the network, then ingress over the target host network, then over PCIe into HBM.

# 2.3 Key Takeaways

- TPUs are simple and can in most cases be thought of as a matrix multiply unit connected to memory (super fast), other chips over ICI (rather fast), and the rest of the datacenter over DCN (somewhat fast).

- Communication is limited by our various network bandwidths in order of speed:

- HBM bandwidth: Between a TensorCore and its associated HBM.

<sup>&</sup>lt;sup>7</sup>https://cloud.google.com/tpu/docs/v5p#system\_architecture

<sup>&</sup>lt;sup>8</sup>The page above lists 100 GB/s of bandwidth, which is slightly different from what's listed here. TPU ICI links have slightly different bandwidths depending on the operation being performed. You can generally use the numbers in this doc without worry.

- ICI bandwidth: Between a TPU chip and its nearest 4 or 6 neighbors.

- PCIe bandwidth: Between a CPU host and its associated tray(s) of chips.

- DCN bandwidth: Between multiple CPU hosts, typically hosts not connected by ICI.

- Within a slice, TPUs are only connected to their nearest neighbors via ICI. This means communication over ICI between distant chips in a slice needs to hop over the intervening chips first.

- Weight matrices need to be padded to at least size 128 (256 on TPU v6) in all dimensions to fill up the MXU (in fact, smaller axes are padded to 128).

- Lower precision matrix multiplication tends to be faster. TPUs can do int8 or int4 FLOPs roughly 2x/4x faster than bfloat16 FLOPs for generations that support it. VPU operations are still performed in fp32.

- To avoid bottlenecking the TPU compute unit, we need to make sure the amount of communication across each channel is proportional to its speed.

- · Here are some specific numbers for our chips:

| Model   | Pod size | Host  | НВМ           | HBM BW/chip | FLOPs/s/chip | FLOPs/s/chip |

|---------|----------|-------|---------------|-------------|--------------|--------------|

|         |          | size  | capacity/chip | (bytes/s)   | (bf16)       | (int8)       |

| TPU v3  | 32×32    | 4×2   | 32GB          | 9.0e11      | 1.4e14       | 1.4e14       |

| TPU v4p | 16×16×16 | 2×2×1 | 32GB          | 1.2e12      | 2.75e14      | 2.75e14      |

| TPU v5p | 16×20×28 | 2×2×1 | 96GB          | 2.8e12      | 4.59e14      | 9.18e14      |

| TPU v5e | 16×16    | 4×2   | 16GB          | 8.1e11      | 1.97e14      | 3.94e14      |

| TPU v6e | 16×16    | 4×2   | 32GB          | 1.6e12      | 9.20e14      | 1.84e15      |

Host size refers to the topology of TPUs connected to a single host (e.g. TPU v5e has a single CPU host connected to 8 TPUs in a 4x2 topology). And here are interconnect figures:

| Model   | ICI BW/link (one-way, bytes/s) | ICI BW/link (bidi, bytes/s) |

|---------|--------------------------------|-----------------------------|

| TPU v3  | 1e11                           | 2e11                        |

| TPU v4p | 4.5e10                         | 9e10                        |

| TPU v5p | 9e10                           | 1.8e11                      |

| TPU v5e | 4.5e10                         | 9e10                        |

| TPU v6e | 9e10                           | 1.8e11                      |

We include both one-way (unidirectional) bandwidth and bidi (bidirectional) bandwidth since unidirectional bandwidth is more true to the hardware but bidirectional bandwidth occurs more often in equations involving a full ring. <sup>9</sup>

<sup>&</sup>lt;sup>9</sup>By bidi (bidirectional) bandwidth we mean the total bytes that can be sent along a single link in both directions, or equally, the total number of outgoing bytes from a single TPU along a particular axis, assuming we can use both links efficiently. This is true when we have a functioning ring, AKA when we have a wraparound connection on the particular axis. This occurs on inference chips when we have a full 16 axis, or on training chips (v\*p) when we have an axis which is a multiple of 4. We prefer to use the bidirectional bandwidth because it appears frequently in calculations involving bidirectional comms.

PCIe bandwidth is typically around 1.5e10 bytes / second per chip <sup>10</sup>, while DCN bandwidth is typically around 2.5e10 bytes / second per host. We include both unidirectional and bidirectional bandwidth for completeness. Typically bidirectional bandwidth is the more useful number when we have access to a full wraparound ring, while one-way bandwidth is more true to the hardware.

### 2.4 Worked problems

These numbers are a little dry, but they let you make basic roofline estimates for model performance. Let's work a few problems to explain why this is useful. You'll see more examples in Section 3.

# Exercise 2.1 [bounding LLM latency]

Say you want to sample from a 200B parameter model in bf16 that's split across 32 TPU v4p. How long would it take to load all the parameters from HBM into the systolic array? *Hint: use the numbers above.*

# Exercise 2.2 [TPU details]

Consider a full TPU v5e pod. How many total CPU hosts are there? How many TPU TensorCores? What is the total FLOPs/s for the whole pod? What is the total HBM? Do the same exercise for TPU v5p pod.

# Exercise 2.3 [PCIe operational intensity]

Imagine we're forced to store a big weight matrix A of type bfloat16[D, F], and a batch of activations x of type bfloat16[B, D] in host DRAM and want to do a matrix multiplication on them. This is running on a single host, and we're using a single TPU v6e chip attached to it. You can assume  $B \ll D$ , and F = 4D (we'll see in future chapters why these are reasonable assumptions). What is the smallest batch size B we need to remain FLOPs bound over PCle? Assume PCle bandwidth of 1.5e10 bytes / second.

# Exercise 2.4 [general matmul latency]

Let's say we want to multiply a weight matrix int8[16384, 4096] by an activation matrix of size int8[B, 4096] where B is some unknown batch size. Let's say we're on 1 TPUv5e to start.

- 1. How long will this multiplication take as a function of B? Hint: it may help to calculate how long it will take to load the arrays from HBM and how long the multiplication will actually take. Which is bottlenecking you?

- 2. What if we wanted to run this operation out of VMEM? How long would it take as a function of B?

# Exercise 2.5 [ICI bandwidth]

Let's say we have a TPU v5e 4x4 slice. Let's say we want to send an array of type bfloat16[8, 128, 8192] from TPU{0,0} to TPU{3, 3}. Let's say the per-hop latency for TPU v5e is  $1\mu s$ .

- 1. How soon will the first byte arrive at its destination?

- 2. How long will the total transfer take?

<sup>&</sup>lt;sup>10</sup>Trillium (TPU v6e) has 32GB/s, about 4x higher than v5.

# Exercise 2.6 [pulling it all together (hard)]

Imagine you have a big matrix **A**: int8[128 \* 1024, 128 \* 1024] sharded evenly across a TPU v5e 4x4 slice but offloaded to host DRAM on each chip. Let's say you want to copy the entire array to  $TPU{0, 0}$  and multiply it by a vector bf16[8, 128 \* 1024]. How long will this take? *Hint: use the numbers above*.

# 2.5 Appendix

### 2.5.1 Appendix A: Let's talk about GPUs

Compared to TPUs, GPUs have a simpler communication model and a more complicated programming model.

#### Overview of the compute model:

GPUs are conceptually similar to TPUs: they also function as an accelerator attached to a CPU. Many components are roughly analogous:

| TPU         | GPU                             |

|-------------|---------------------------------|

| Tensor Core | SM ('Streaming Multiprocessor') |

| НВМ         | DRAM                            |

| VPU         | Tensor Cores                    |

| VMEM        | L1 Cache                        |

| ICI         | NVLink/NVSwitch                 |

- Compared to TPUs, GPUs have many more 'streaming multiprocessors' (an H100 has about 140), each

of which can be seen as analogous to a TensorCore (which a TPU only has 1-2 of). Having more SMs

makes computation more flexible (since each can do totally independent work) but also makes the

hardware more complex to reason about.

- Each SM in an H100 has about 1024 CUDA Cores which perform SIMD scalar work (like a TPU VPU)

and a small L1 cache used to speed data access and for register spilling. A section of the memory

used for the L1 cache can also be declared as shared memory allowing access from any thread in the

thread-block, and is used for user-defined caches, parallel reductions and synchronization, etc (similar

to VMEM on a TPU).

- GPUs also have an additional L2 cache that is shared by all SMs. Unlike VMEM, this is hardware managed and optimizing cache hits is often important for performance.

### **Networking:**

Primary difference is that NVIDIA GPUs are typically in 'cliques' of 8-256 GPUs via switches (NVLink → NVSwitch), which allow for point-to-point communication between any GPU within that 'clique', but that means communication between more than 256 is significantly slower - this means training on more than 256 typically requires pipeline parallelism to scale, which is more complex (by contrast, PaLM was trained on two cliques of 3072 TPU chips each).

- For common neural net operations such as AllReduce, all-to-all connections do not hold an advantage (as the same communication patterns must occur regardless), but it does allow for storing MoE models across more GPUs and transmitting the experts around more efficiently.

- Each GPU requires a switch that costs similar to the GPU itself, making on chip interconnect like ICI cheaper.

- NVIDIA deep learning performance<sup>11</sup>

- NVSwitch<sup>12</sup>

- Very different Tensor Parallelism / Pipeline Parallelism transition point!

# 2.5.2 Appendix B: How does a systolic array work?

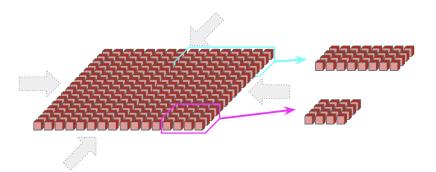

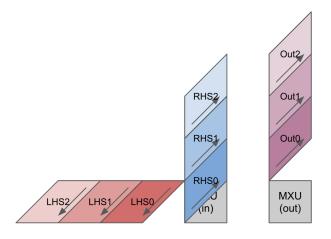

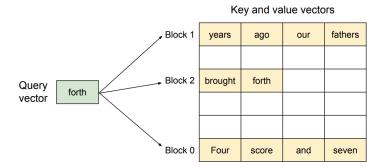

At the core of the TPU MXU is a 128x128 systolic array (256x256 on TPU v6e). When fully saturated the systolic array can perform one bfloat16[8,128] @ bf16[128x128] -> f32[8,128]<sup>13</sup> multiplication per 8 clock cycles.

- At its core, the systolic array is a 2D 128x128 (= 16,384) grid of ALUs each capable of performing a multiply and add operation.

- Weights (**W**, the 128x128 input) are passed down from above (called the RHS) while inputs (**X**, the 8x128 input) are passed in from the left (called the LHS).

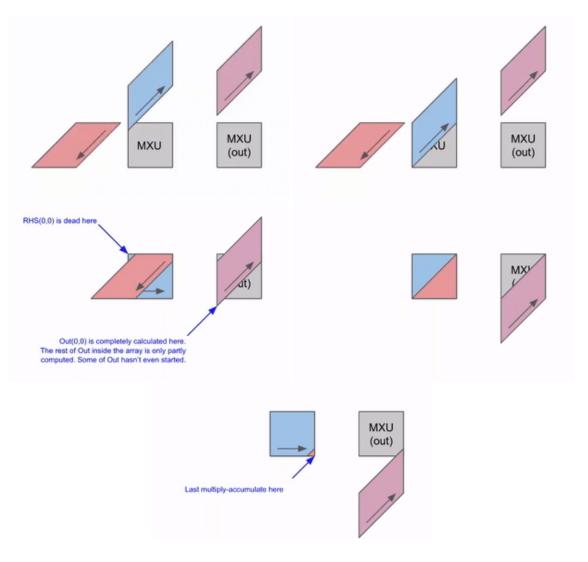

Here is a simplified animation of multiplying a set of weights (blue) with a set of activations (green). You'll notice that the weights (RHS) are partially loaded first, diagonally, and then the activations are fed in, also diagonally. In each frame below, we multiply all the overlapped green and blue units, sum the result with any residual passed in from above, and then pass the result in turn down one unit.

$<sup>^{11}</sup> https://docs.nvidia.com/deeplearning/performance/dl-performance-gpu-background/index.html \#gpu-architectures and the state of t$

<sup>12</sup>https://www.nvidia.com/en-au/data-center/nvlink/

$<sup>^{13}</sup>$ If you are not familiar with this notation, it means: multiplying a 8x128 matrix with bfloat16 elements by a 128x128 matrix with bfloat16 elements and storing the results in a 8x128 matrix with float32 elements.

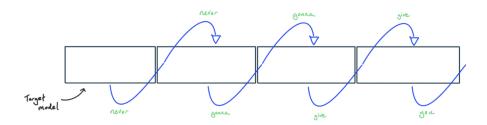

Here's a more general version of this animation showing the output being streamed out of computation:

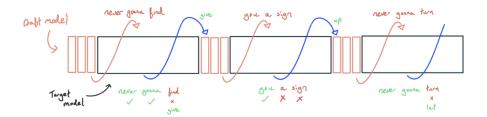

Here's a diagram showing how this can be pipelined across multiple RHS and LHS arrays:

There is an initial pipeline bubble as the weights (RHS) and activations (LHS) are loaded. After that initial bubble, new inputs and weights can be loaded in without an additional bubble.

We can efficiently pipeline this to multiply large matrices without too large a pipeline bubble. With that said, it's important that our matrices have shapes larger than the side dimension of the MXU, which is generally 128x128. Some TPUs (since TPU v3) have multiple MXUs, either 2 for TPU v3 and 4 for TPU v4/5, so we need to ensure tiling dimensions are larger than 128 \* number of MXUs.

Trillium (TPU v6e) has a 256x256 systolic array, which means it can perform 4x more FLOPs / cycle. This also means the dimensions of your tensors needs to be twice as large to utilize the MXU fully.

This blog post<sup>14</sup> has another excellent animation of a systolic array multiplication for a fixed weight matrix.

### 2.5.3 Appendix C: TPU internals

#### **Scalar Core**

The TPU scalar core processes all of the instructions and executes all of the transfers from HBM into vector memory (VMEM). The scalar core is also responsible for fetching instructions for the VPU, MXU and XLU components of the chip. One side-effect of this is that each core of the TPU is only capable of creating one DMA request per cycle.

To put this in context, a single 4 scalar core controls a VPU consisting of 2048 ALUs, 4 MXUs, 2 XLUs, and multiple DMA engines. The highly skewed nature of control per unit compute is a source of hardware efficiency, but also limits the ability to do data dependent vectorization in any interesting way.

#### **VPU**

The TPU vector core consists of a two dimensional vector machine (the **VPU**) that performs vector operations like vadd (vector addition) or vmax (elementwise max) and a set of vector registers called **VREGs** that hold data for the VPU and MXU. The VPU is effectively a 2D vector arithmetic unit of shape (8, 128) where the 128 dimension is referred to as a lane and the dimension of 8 is referred to as a sublane. Each (lane, sublane) pair on v4 contains 2 standard floating-point and integer ALUs. From a software point-of-view, this creates the appearance of a 8x128 vector unit with a total of 2048 floating point adders in v4. TPU v4 has 32 VREGs of size (8, 128) which the VPU loads from and writes to.

The VPU executes most arithmetic instructions in one cycle in each of its ALUs (like vadd or vector add) with a latency of 2 cycles, so e.g. in v5 you can add 4 pairs of f32 values together from VREGs in each cycle. A typical VPU instruction might look like  $\{v2 = vadd.8x128.f32 v0, v1\}$  where v0 and v1 are input VREGs and v2 is an output VREG.

All lanes and sublanes execute the same program every cycle in a pure SIMD manner, but each ALU can perform a different operation. So we can e.g. process 1 vadd and 1 vsub in a single cycle, each of which operates on two full VREGs and writes the output to a third.

<sup>14</sup> https://fleetwood.dev/posts/domain-specific-architectures#google-tpu

# 3 Sharded Matrices and How to Multiply Them

Here we'll explain how the biggest ML models are split (or "sharded") across multiple accelerators. Since LLMs are mostly made up of matrix multiplications, understanding this boils down to understanding how to multiply matrices when they're split across devices. We develop a simple theory of sharded matrix multiplication based on the cost of TPU communication primitives.

# 3.1 Partitioning Notation and Collective Operations

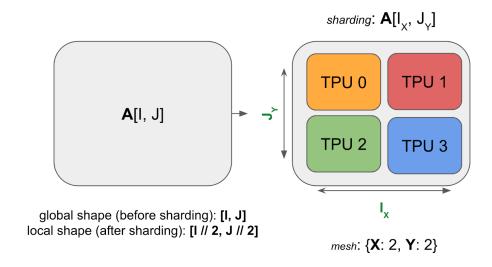

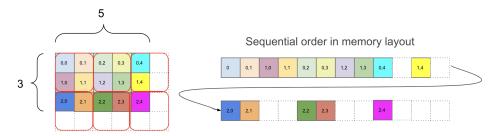

When we train an LLM on ten thousand TPUs, we're still doing abstractly the same computation as when we're training on one. The difference is that **our arrays don't fit in the HBM of a single TPU**, so we have to split them up.<sup>1</sup> We call this "sharding" or "partitioning" our arrays. Here's an example 2D array **A** sharded across 4 TPUs:

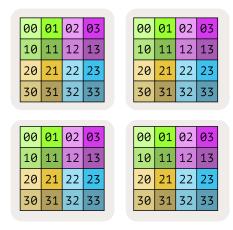

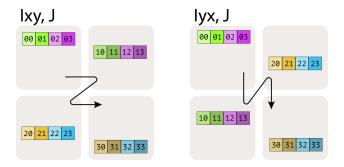

Figure 7: An example array of shape A[I, J] gets sharded across 4 devices. Both dimensions are evenly sharded across 2 devices with a sharding  $A[I_X, J_Y]$ . Each TPU holds 1/4 of the total memory.

Note how the sharded array still has the same *global* or *logical shape* as unsharded array, say (4, 128), but it also has a *device local shape*, like (2, 64), which gives us the actual size in bytes that each TPU is holding (in the figure above, each TPU holds ¼ of the total array). Now we'll generalize this to arbitrary arrays.

### 3.1.1 A unified notation for sharding

We use a variant of *named-axis notation* to describe *how* the tensor is sharded in blocks across the devices: we assume the existence of a 2D or 3D grid of devices called the **device mesh** where each axis has been given **mesh axis names** e.g. **X**, **Y**, and **Z**. We can then specify how the matrix data is laid out across the device mesh by describing how each named dimension of the array is partitioned across the physical mesh axes. We call this assignment a **sharding**.

#### **Example (the diagram above)**: For the above diagram, we have:

<sup>&</sup>lt;sup>1</sup>It's worth noting that we may also choose to parallelize for speed. Even if we could fit on a smaller number of chips, scaling to more simply gives us more FLOPs/s. During inference, for instance, we can sometimes fit on smaller topologies but choose to scale to larger ones in order to reduce latency. Likewise, during training we often scale to more chips to reduce the step time.

- Sharding:  $A[I_X, J_Y]$ , which tells us to shard the first axis, I, along the mesh axis X, and the second axis, J, along the mesh axis Y. This sharding tells us that each shard holds  $1/(|X| \cdot |Y|)$  of the array.

- Mesh: the device mesh above  $Mesh(devices=((0, 1), (2, 3)), axis_names=('X', 'Y'))$ , which tells us we have 4 TPUs in a 2x2 grid, with axis names X and Y.

Taken together, we know that the local shape of the array (the size of the shard that an individual device holds) is (|I|/2, |J|/2), where |I| is the size of A's first dimension and |J| is the size of A's second dimension. **Example (2D sharding across 1 axis)**:  $A[I_{XY}, J]$  shards the first dimension (I) along both the X and Y hardware axes. The number of bytes per device is the same as the previous sharding but the local shape is different. It is now  $(|I|/(|X| \cdot |Y|), |J|)$ .

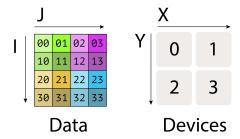

**Visualizing these shardings:** Let's try to visualize these shardings by looking at a 2D array of data split over 4 devices:

We write the *fully-replicated* form of the matrix simply as A[I, J] with no sharding assignment. This means that *each* device contains a full copy of the entire matrix.

When we wish to indicate that one of these dimensions has been partitioned across a mesh axis, then we indicate so using a mesh-axis subscript. For instance  $A[I_X, J]$  would mean that the I logical axis has been partitioned across the **X** mesh dimension, but that the **J** dimension is *not* partitioned, and the blocks remain partially-replicated across the **Y** mesh axis.

$A[I_X,J_Y]$  means that the I logical axis has been partitioned across the **X** mesh axis, and that the **J** dimension has been partitioned across the **Y** mesh axis.

We illustrate the other possibilities in the figure below:

Here  $A[I_{XY}, J]$  means that we treat the **X** and **Y** mesh axes as a larger flattened dimension and partition the I named axis across all the devices. The order of the multiple mesh-axis subscripts matters, as it specifies the traversal order of the partitioning across the grid.

Lastly, note that we cannot have multiple named axes sharded along the same mesh dimension. e.g.  $A[I_X, J_X]$  is a nonsensical, forbidden sharding. Once a mesh dimension has been used to shard one dimension of an array, it is in a sense "spent".

**Pop Quiz:** Let **A** be an array with shape int8[128, 2048], sharding  $A[I_{XY}, J]$ , and mesh Mesh({'X': 2, 'Y': 8, 'Z': 2}) (so 32 devices total). How much memory does **A** use per device? How much total

memory does A use across all devices?

**Answer:** Our array **A** is sharded over X and and Y and replicated over Z, so per device it has shape int8[128 / (2\*8), 2048] = int8[8, 2048], with size 8\*2048 = 16,384 bytes. Because it's replicated over Z, while within a Z-plane it's fully sharded over X and Y, there's one copy of it per Z-plane, and 2 such planes, so the total size (across all devices) is 128\*2048\*2 = 512kiB total.

### 3.1.2 A guick aside: how would we describe this in code?

JAX uses a named sharding syntax that very closely matches the abstract syntax we describe above. We'll talk more about this in Section 10, but here's a quick preview. You can play with this in a Google Colab and profile the result to see how JAX handles different shardings. This snippet does 3 things:

- 1. Creates a **jax.Mesh** that maps our 8 TPUs into a 4x2 grid with names 'X' and 'Y' assigned to the two axes.

- 2. Creates matrices A and B where A is sharded along both its dimensions and B is sharded along the output dimension.

- 3. Compiles and performs a simple matrix multiplication that returns a sharded array.

```

import jax

import jax.numpy as jnp

import jax.sharding as shd

# Create our mesh! We're running on a TPU v2-8 4x2 slice with names 'X' and 'Y'.

assert len(jax.devices()) == 8

mesh = jax.make_mesh(axis_shapes=(4, 2), axis_names=('X', 'Y'))

# A little utility function to help define our sharding. A PartitionSpec is our

# sharding (a mapping from axes to names).

def P(*args):

return shd.NamedSharding(mesh, shd.PartitionSpec(*args))

\mbox{\tt\#} We shard both A and B over the non-contracting dimension and A over the contracting dim.

A = jnp.zeros((8, 2048), dtype=jnp.bfloat16, device=P('X', 'Y'))

B = jnp.zeros((2048, 8192), dtype=jnp.bfloat16, device=P(None, 'Y'))

# We can perform a matmul on these sharded arrays! out_shardings tells us how we want

# the output to be sharded. JAX/XLA handles the rest of the sharding for us.

compiled = jax.jit(lambda A, B: jnp.einsum('BD, DF->BF', A, B), out_shardings=P('X', 'Y')).lower

(A, B).compile()

y = compiled(A, B)

```

The cool thing about JAX is that these arrays behave as if they're unsharded! B.shape will tell us the global or logical shape (2048, 8192). We have to actually look at B.addressable\_shards to see how it's locally sharded. We can perform operations on these arrays and JAX will attempt to figure out how to broadcast or reshape them to perform the operations. For instance, in the above example, the local shape of A is [2, 1024] and for B is [2048, 4096]. JAX/XLA will automatically add communication across these arrays as necessary to perform the final multiplication.

# 3.2 Computation With Sharded Arrays

If you have an array of data that's distributed across many devices and wish to perform mathematical operations on it, what are the overheads associated with sharding both the data and the computation?

Obviously, this depends on the computation involved.

- For elementwise operations, there is **no overhead** for operating on a distributed array.

- When we wish to perform operations across elements resident on many devices, things get complicated. Thankfully, for most machine learning nearly all computation takes place in the form of matrix multiplications, and they are relatively simple to analyze.

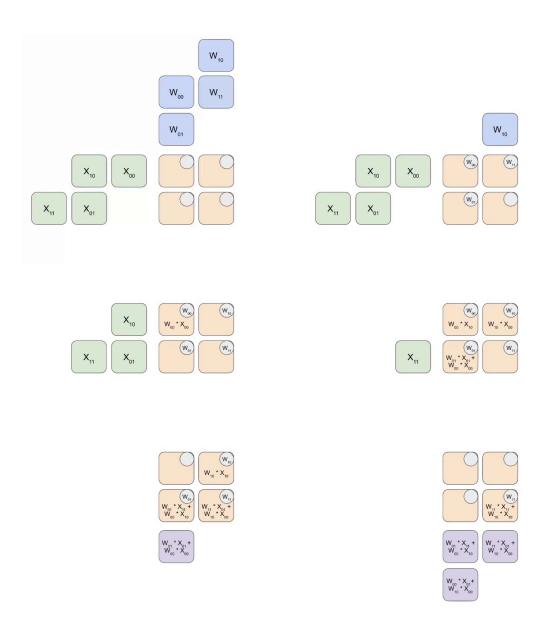

The rest of this section will deal with how to multiply sharded matrices. To a first approximation, this involves moving chunks of a matrix around so you can fully multiply or sum each chunk. **Each sharding will involve different communication**. For example,  $A[I_X, J] \cdot B[J, K_Y] \to C[I_X, K_Y]$  can be multiplied without any communication because the *contracting dimension* (J, the one we're actually summing over) is unsharded. However, if we wanted the output unsharded (i.e.  $A[I_X, J] \cdot B[J, K_Y] \to C[I, K]$ ), we would need to copy A or C to every device. These two choices have different communication costs, so we need to calculate this cost and pick the lowest one.

You can think of this in terms of "block matrix multiplication".

First let's recall the concept of a "block matrix", or a nested matrix of matrices:

$$\begin{pmatrix} a_{00} & a_{01} & a_{02} & a_{03} \\ a_{10} & a_{11} & a_{12} & a_{13} \\ a_{20} & a_{21} & a_{22} & a_{23} \\ a_{30} & a_{31} & a_{32} & a_{33} \end{pmatrix} = \begin{pmatrix} \begin{bmatrix} a_{00} & a_{01} \\ a_{10} & a_{11} \end{bmatrix} \begin{bmatrix} a_{02} & a_{03} \\ a_{12} & a_{13} \end{bmatrix} \\ \begin{bmatrix} a_{20} & a_{21} \\ a_{30} & a_{31} \end{bmatrix} \begin{bmatrix} a_{22} & a_{23} \\ a_{32} & a_{33} \end{bmatrix} = \begin{pmatrix} \mathbf{A}_{00} & \mathbf{A}_{01} \\ \mathbf{A}_{10} & \mathbf{A}_{11} \end{pmatrix}$$

Matrix multiplication has the nice property that when the matrix multiplicands are written in terms of blocks, the product can be written in terms of block matmuls following the standard rule:

$$\begin{pmatrix} A_{00} & A_{01} \\ A_{10} & A_{11} \end{pmatrix} \cdot \begin{pmatrix} B_{00} & B_{01} \\ B_{10} & B_{11} \end{pmatrix} = \begin{pmatrix} A_{00}B_{00} + A_{01}B_{10} & A_{00}B_{01} + A_{01}B_{11} \\ A_{10}B_{00} + A_{11}B_{10} & A_{10}B_{01} + A_{11}B_{11} \end{pmatrix}$$

(3)

What this means is that implementing distributed matrix multiplications reduces down to moving these sharded blocks over the network, performing local matrix multiplications on the blocks, and summing their results. The question then is what communication to add, and how expensive it is.

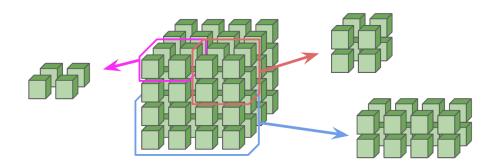

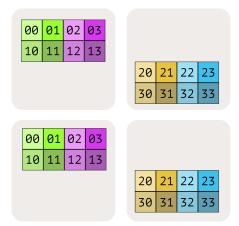

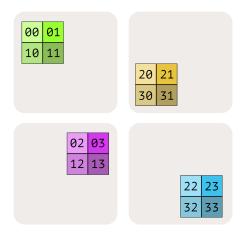

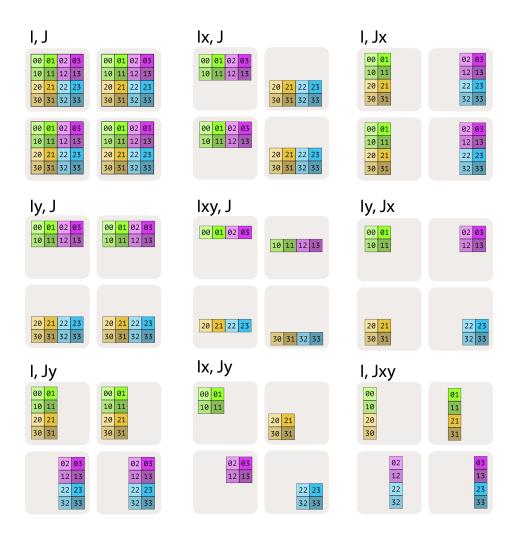

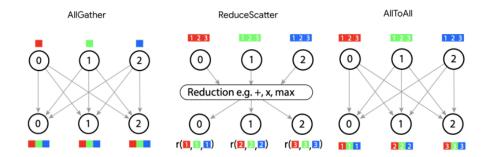

Conveniently, we can boil down all possible shardings into roughly 4 cases we need to consider, each of which has a rule for what communication we need to add:

- Case 1: neither input is sharded along the contracting dimension. We can multiply local shards without any communication.

- Case 2: one input has a sharded contracting dimension. We typically "AllGather" the sharded input along the contracting dimension.

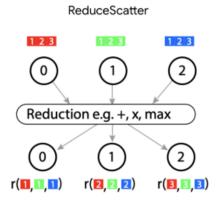

- Case 3: both inputs are sharded along the contracting dimension. We can multiply the local shards, then "AllReduce" the result.

Case 4: both inputs have a non-contracting dimension sharded along the same axis. We cannot proceed without AllGathering one of the two inputs first.

You can think of these as rules that simply need to be followed, but it's also valuable to understand why these rules hold and how expensive they are. We'll go through each one of these in detail now.

### Case 1: neither multiplicand has a sharded contracting dimension

**Lemma:** when multiplying partitioned tensors, the computation is valid and the output follows the sharding of the inputs *unless* the contracting dimension is sharded or both tensors have a non-contracting dimension sharded along the same axis. For example, this works fine

$$A[I_X, J] \cdot B[J, K_Y] \rightarrow C[I_X, K_Y]$$

with no communication whatsoever, and results in a tensor sharded across both the X and Y hardware dimensions. Try to think about why this is. Basically, the computation is *independent* of the sharding, since each batch entry has some local chunk of the axis being contracted that it can multiply and reduce. Any of these cases work fine and follow this rule:

$$\begin{aligned} \mathbf{A}[I,J] \cdot \mathbf{B}[J,K] &\to \mathbf{C}[I,K] \\ \mathbf{A}[I_X,J] \cdot \mathbf{B}[J,K] &\to \mathbf{C}[I_X,K] \\ \mathbf{A}[I,J] \cdot \mathbf{B}[J,K_Y] &\to \mathbf{C}[I,K_Y] \\ \mathbf{A}[I_X,J] \cdot \mathbf{B}[J,K_Y] &\to \mathbf{C}[I_X,K_Y] \end{aligned}$$

Because neither **A** nor **B** has a sharded contracting dimension **J**, we can simply perform the local block matrix multiplies of the inputs and the results will *already* be sharded according to the desired output shardings. When both multiplicands have non-contracting dimensions sharded along the same axis, this is no longer true (see Case 4 for details).

### Case 2: neither multiplicand has a sharded contracting dimension

Let us consider the simple case of the distributed matrix multiply of  $\bf A$  sharded in the contracting  $\bf J$  dimension against a fully replicated  $\bf B$ :

$$A[I, J_X] \cdot B[J, K] \rightarrow C[I, K]$$