-

Beta Was this translation helpful? Give feedback.

Replies: 2 comments 5 replies

-

|

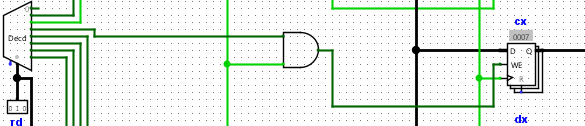

The data registers in your screenshot are sensitive to the falling edge of clock. |

Beta Was this translation helpful? Give feedback.

-

|

Thanks for your Logisim file and the additional screenshots. They make me believe that Logisim-evolution works correctly and that you are not experiencing a bug. To verify, I recommend you to simulate the registers block alone: When you set I think what you are observing is that the above-mentioned control signals get set after the rising edge. At this moment |

Beta Was this translation helpful? Give feedback.

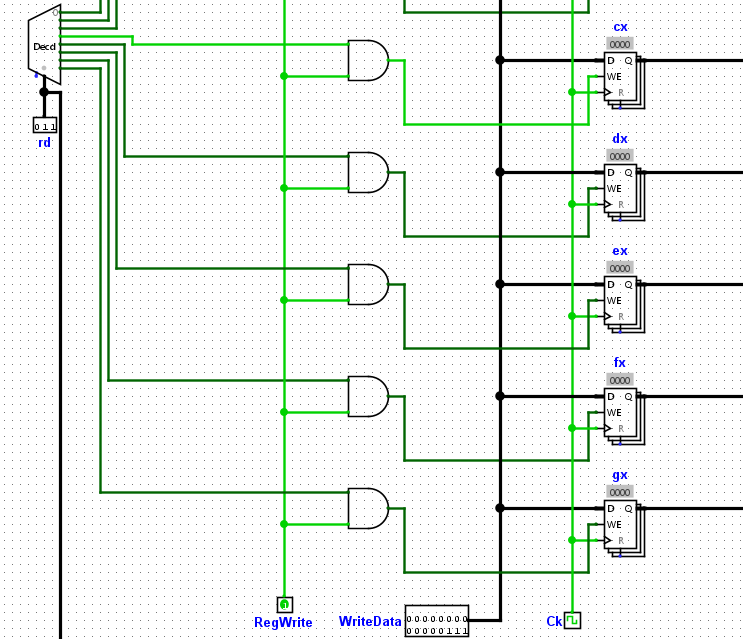

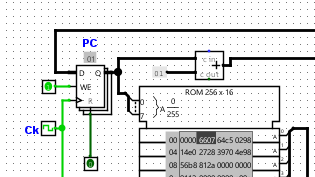

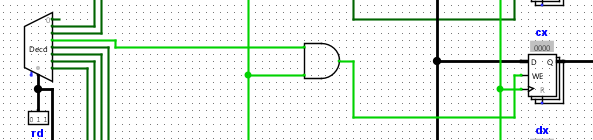

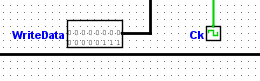

Thanks for your Logisim file and the additional screenshots. They make me believe that Logisim-evolution works correctly and that you are not experiencing a bug. To verify, I recommend you to simulate the registers block alone: When you set

WriteDatato some value, choose withrdthe target register, and activateRegWrite, everything is set up for a write to the register. What is needed now is a transition from0to1(i.e., rising edge) on theCksignal. The value ends up correctly in the register.I think what you are observing is that the above-mentioned control signals get set after the rising edge. At this moment

Ckis still1. However, the register will sample its input only onceCk…