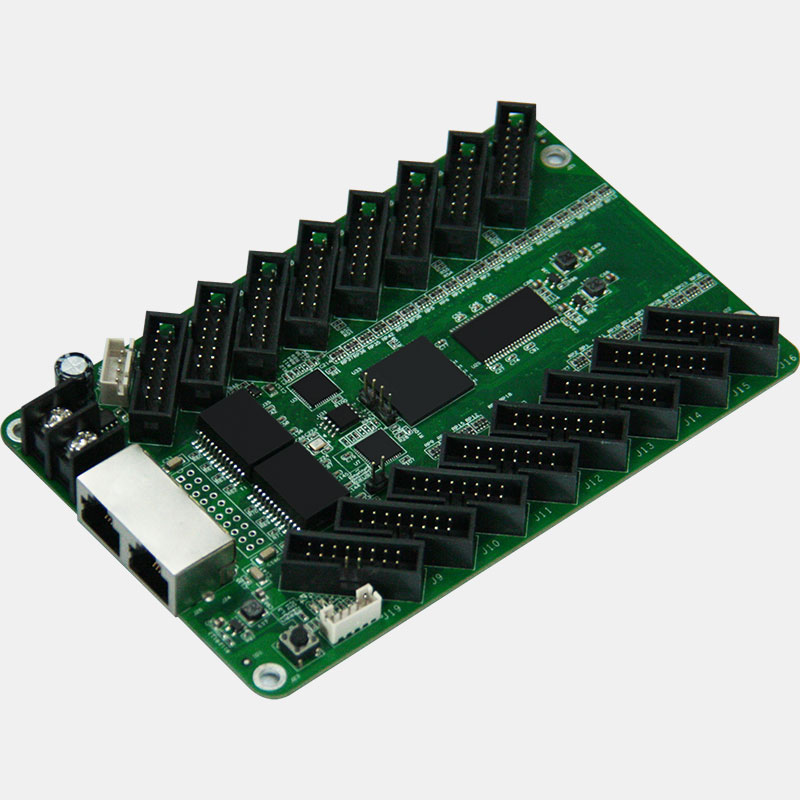

This repository contains a simple program written in different HDLs (Hardware Description Languages) for the Colorlight 5a-75e v8.0 board, using FT232RL as JTAG programmer. The goal is to provide an easy first setup for the Colorlight board.

The program is a simple LED controller, which turns ON the LED everytime the input signal is ON.

You can find more information on how to setup the hardware/toolchain on my blog post.

- FPGA toolchain

- yosys – Yosys Open SYnthesis Suite.

- nextpnr-ecp5 - A portable FPGA place and route tool (for Lattice ECP5 FPGA).

- prjtrellis - Device database and tools for bitstream creation (fully open source flow for ECP5 FPGA).

- openFPGALoader - Universal utility for programming FPGA

- git

- make

In case you want to run the VHDL example, you will also need:

- GHDL - VHDL 2008/93/87 simulator.

In case you want to run the SpinalHDL example, you will also need:

- Scala

- sbt

- Java JDK 8+ (tested on

openjdk 19.0.1 2022-10-18)

> git clone https://github.com/roby2014/ecp5-ft232rl-example

> cd ecp5-ft232rl-example/[verilog/vhdl/spinalhdl]_example

> make

openFPGALoader --cable ft232RL --pins=RXD:RTS:TXD:CTS led_control.bit

Jtag probe limited to 3MHz

Jtag frequency : requested 6000000Hz -> real 3000000Hz

ret 0

Open file: DONE

Parse file: DONE

Enable configuration: DONE

SRAM erase: DONE

Loading: [==================================================] 100.00%

Done

Disable configuration: DONE

After running make, the bitstream should be uploaded to the FPGA and you should be able to control the LED via input button.

When running make, this is what happens "under the hood":

yosyssynthetizes the Verilog/Vhdl files, generating ajsonfile with the RTL information.nextpnr-ecp5transforms synthetized RTL code and pin mapping (lpffile) into a FPGA config file.ecppackgenerates bitstream from the configuration file.openFPGALoaderuploads the bitstream into the FPGA via JTAG.

In case you are running the SpinalHDL example, there is an extra step before all of the above:

- All Scala files from

src/mylib/are compiled into Verilog files (insidegen/folder).

In case you are running the VHDL example, there is an extra step before all of the above:

GHDLanalyzes all.vhdfiles and elaborates the top entity module.