-

Notifications

You must be signed in to change notification settings - Fork 26

Home

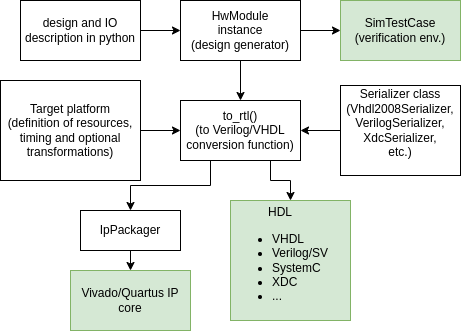

HWT is a library for hardware description as well as for hardware generators. It integrates API for simulator, IP core packages and code transformations. It is meant to shield you from "tricky features" of VHDL/Verilog and tools related to them. It is build for automation and Very-large-scale integration (VLSI) as well as for small projects and rapid developement.

HwModule is a main class from which all hardware components inherit. In HWT every user design is actually a design generator. User specifies IO, configuration and internal code in HwModule by overriding of its methods. HwModule is normal Python class, objects of it are recognizing HW relate object in attribute setter.

Hwt main internal representation is a high level netlist (RtlNetlistCtx) composed of statement (HdlStatement) and operator nodes (HOperatorNode) interconnected with signals (RtlSignal). The design can be hierarchical. And can be converted to most common HDL languages like VHDL, SystemVerilog or SystemC The netlist itself is generated directly by user e.g. hwt.code.If/Switch.

If you know Verilog, you know that the language itself is easy but the hardware description is hard.

In this case the HWT, API is basically just HwModule class with hwConfig(), hwDeclr(),

hwImpl(), _sig(), _reg() method, hwt.code.If/Switch, to_rtl(), some types form hwt.hdl.types.

It is something which you can learn in 30 minutes from examples in hwtLib if you know the Python.

Hwt uses Python exceptions to report design issues early which makes it easy to experiment with.

The Python acts as a preprocessor and generates HDL code objects.

The design description obeys same rules as in VHDL/Verilog except it does not need explicit sensitivity lists

and does not assignment to non constant slices on bit vectors.

So if you know Verilog/VHDL you practically already know HWT and you can use Python as powerful preprocessor. Together with HWT asserts, analysis, introspectivity, simulator API and the most common components in hwtLib your work efficiency can be dramatically improved.

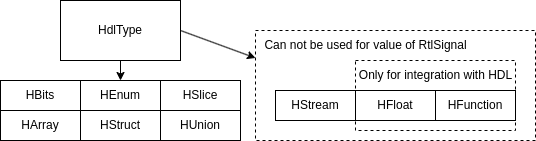

HdlType definitions are stored in hwt.hdl.types. Operators and conversions are defined on HdlType class. These methods are called from RtlSignal/HwIOSignal/HConst instances. HdlType instance is available in _dtype property.

HWT uses C-like strongly typed typesystem where HBits corresponds to integer type, HStruct to struct etc.

In addition it contains HStream which is used mainly to represent data constraint which are used to compute some optimization. It can not be used as a value of signal which has direct HW representation.

HFloat and HFunctions can be used for HDL but it does not define any HW operator. The reason for HFloat not defining any HW operator is that, there are many realizations of the same operator. The process of selection is non trivial and commonly uses hard blocks. From this reasons this is excluded from HWT and it is implemented in hwtHls which has the infrastructure required for complex design decisions.