-

Notifications

You must be signed in to change notification settings - Fork 0

New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

海思HI3531DV200 核心板上主要芯片 #1

Comments

|

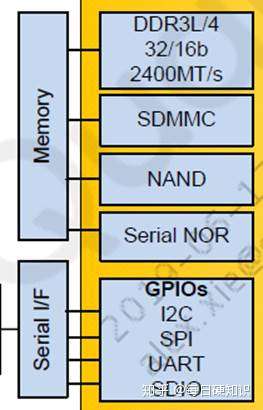

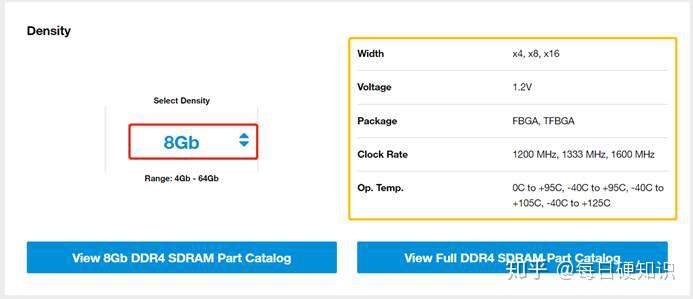

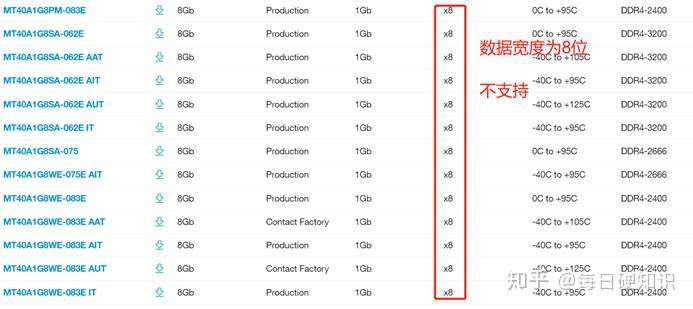

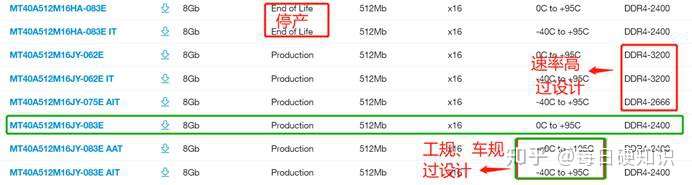

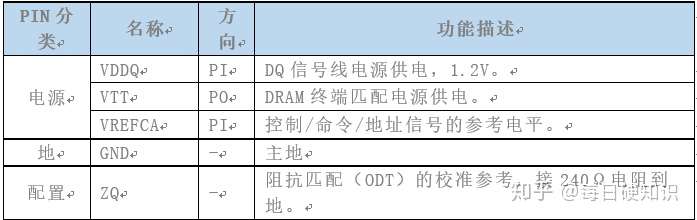

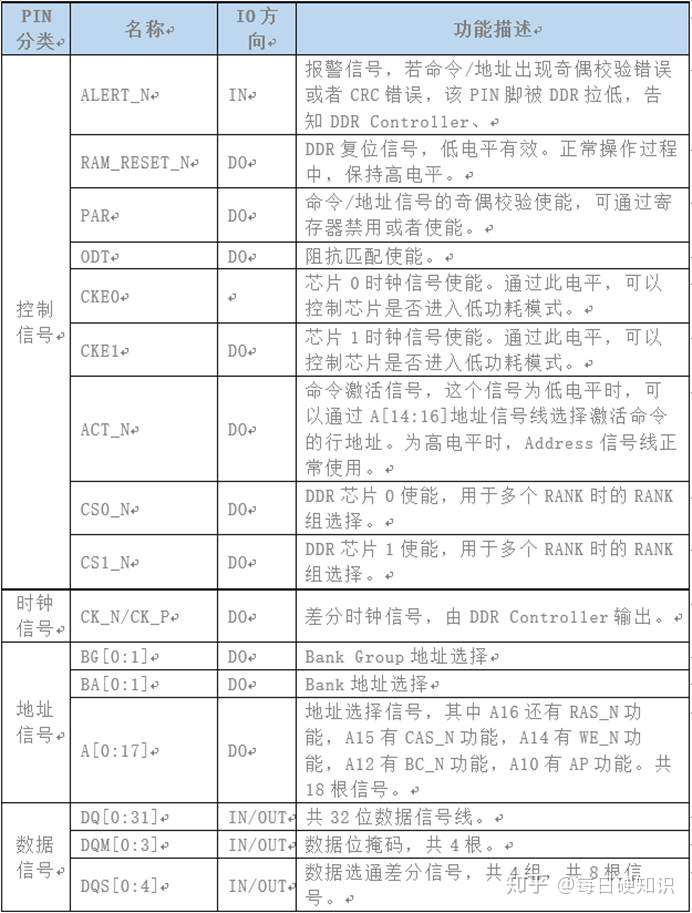

作为硬件工程师,我们通常收到需求是:该产品内存配置为DDR4,容量8Gb(1GB=8Gb)。 而我们通常需要把这个“简陋”的需求,转化为具体的电路,该如何去实现呢? 其实,很简单。DDR4的硬件设计过程可以总结为:为某个平台搭配一颗DDR内存颗粒,并保证平台与DDR内存颗粒均能正常工作。 所以可以分为2部分,如何为平台选型1颗DDR内存颗粒?如何保证DDR相关电路能正常工作? DDR内存颗粒选型目前很多芯片都会把CPU与外围控制电路(例如:FLASH控制电路,DDR控制电路,USB控制电路)集成到1颗芯片中,像高通MDM8909,类似这样的芯片,我们称为“平台芯片”。平台芯片中DDR控制电路,我们称为“DDR Controller”,翻译过来为:DDR控制器。 为DDR控制器搭配它能控制的DDR内存颗粒,你就必须先了解下:DDR控制器需要什么样的内存颗粒? 硬件设计第一步:查阅平台芯片规格书中,关于DDR控制器部分的描述。 It has 16/32 bits DDR3L/4 up to 2400 MT/s, parallel NAND, serial NOR interfaces. 所以我们了解到了: 该平台芯片,支持DDR3L或者DDR4内存颗粒,数据位宽为16位或者32位,最高数据传输速度为2400MT/s,即频率为1200MHz(DDR是双边沿数据传输,1个时钟周期传输2次数据,1s传输了2400M次,即意味着1s时钟变化了1200次,即频率为1200MHz)。 结合产品需求:容量8Gb,那我们基本可以锁定DDR的详细规格了。 在正式选型之前,还要引入1个概念“RANK”。我们知道,DDR即支持多个内存颗粒扩展容量,又支持多个内存颗粒扩展数据位宽。 例如,我们的DDR控制器支持32位数据位宽,那我们可以用8个4位DDR,或者4个8位DDR,或者2个16位DDR,或者1个32位DDR进行数据位扩展。假如我们用8个4位DDR颗粒进行设计,我们的RANK数量就是8,我们戏称为“8-RANK设计”,当然实际生活中,我们肯定不会这么蠢,拿8个4位DDR去扩展32位。 所以,再确定我们的RANK数量后,需求被锁定了。 容量设定为8Gb,类型为DDR4,数据宽度为32位,最高频率为1200MHz。由于目前大部分DDR内存颗粒最高支持16位数据宽度,所以RANK数量为2,即我们说的Dual-RANK设计。 根据这个需求,可以在DDR官网上去寻找合适的“DDR芯片”了。例如在镁光官网产品页,选定DRR4-SDRAM,选定8Gb,DDR4。 网页会为你推荐很多型号。像数据位宽是8位的,可以直接跳过。 数据位宽为16位,频率为1200Mhz(2400MT/s)的,仍然有很多。这时候就是考验硬件工程师职业素养的时候了,我们不仅要考虑硬件性能,还要考虑下物料成本,物料采购周期。考虑成本,就尽量不要有“过设计”的地方,所以速率为3200MT/s的器件排除掉。如果我们是消费类商规产品,所以温度范围选择较窄的商业级器件,其次,为了增进你和采购的感情, 千万不要选择停产的物料。 千万不要选择停产的物料。 千万不要选择停产的物料。 这样下来,我们选型基本就锁定到MT40A512M16JY-083E了,用量为2片。 此时,开始阅览器件规格书,了解电气性能,设计外围电路,让DDR控制器和DDR内存颗粒都欢快的运行起来。 DDR的硬件电路搭建设计逻辑器件电路,就要有逻辑思维,最简单的逻辑思维,就是分组。所以,先了解DDR控制器的硬件接口。控制器硬件PIN脚可以分为电源组,配置组,控制组,时钟组,地址组,数据组。 电源组和配置组接口如下,供电,接电阻就可以完成,1.2V的供电,尽可能要平稳,此处忽略。ZQ电阻是用来校准ODT阻抗的,我们后面会讲到。 控制组接口如下。 分好组后,就要根据DDR的工作原理来进行外围硬件设计了。 控制信号中,需要注意CS0和CS1,2个片选信号的可以用来进行,多RANK内存容量扩展的,说明DDR控制器,最多支持2组RANK。每组RANK分配单独的片选信号。我们此处设计2个16位芯片组成1个RANK,即CS0要同时接在目前选的2个DDR颗粒的CS上,组成菊花链。其余控制信号一般无时序要求,能传递逻辑即可。 地址信号通常要参考时钟信号,来进行寻址,所以地址信号要严格与时钟信号保持长度一致,来保证所有地址位在采样的时候同时到达。因为同一块单板上,每根线上电子的传递速度是一样的,所以信号线长度约长,信号越晚到达,信号线长度越短,信号越早到达,地址采样的时候,是有时间期限的,所以,所有的地址信号必须保证在采样时间范围内,全部到达,因此要求地址线相对时钟线进行长度控制。前面一节我们讲了内存寻址原理,先用BG信号选择BANK GROUP,再用BA信号进行BANK选择,再用A[0:16]进行行列选择,再用A[0:16]进行列选择,完成寻址。可以看到,Address信号在进行行选择和列选择时,BG和BA信号都是保持的,所以BG信号和BA信号的等长要求会相对略宽。 DDR控制器有2根BG信号,2根BA信号,17根Address信号,同一个RANK有2个DDR颗粒,每个DDR颗粒有1根BG信号,2根BA信号,17根Address信号,前面CS0同时连接了2个DDR颗粒的片选,所以寻址时两颗DDR会被同时片选,那么DDR控制器如何区分开寻址其中1颗DDR颗粒呢?硬件又该怎么连接?其实很简单,根据上节讲的内存寻址原理,我们知道每个DDR颗粒有2个BANK GROUP(1根BG信号),4个BANK(2根BA信号),与CS扩展容量的原理一致,我们把BG0接在DDR颗粒1上,BG0拉高拉低,我们可以寻址CHIP1的8个BANK。BG1接在DDR颗粒2上,BG1拉高拉低,我们可以寻址CHIP1的8个BANK。BA、ADDR进行菊花链连接,同时接在2颗DDR芯片上。 接下来,我们看看数据信号的链接,数据信号是内部分组的,由于DDR数据信号传输的时候双边沿数据传输,而且如果所有信号都参考时钟去做等长,会导致等长控制非常困难,增加DDR的设计难度,所以聪明的人类想出了另外一招,额外增加数据选通信号来作为数据信号的采样时钟,每8位信号,参考一组差分。所以我们很轻易可以看出DDR控制器有4组DQS差分信号,32根数据信号。我们的RANK中有2个DDR颗粒,每个颗粒有2组DQS差分信号,16根数据信号。所以 控制器的DQS[0:1]连接DDR CHIP0的DQS[0:1], 控制器的DQ[0:15]连接DDR CHIP0的DQ[0:15]。 控制器的DQS[2:3]连接DDR CHIP1的DQS[0:1], 控制器的DQ[16:31]连接DDR CHIP1的DQ[0:15]。 至此所有信号连接完成。 接下来是阻抗匹配,地址信号都需要外部加49欧姆匹配电阻到电源或者GND,数据信号,则不需要。因为DDR内部集成ODT功能,只需要通过配置,即可完成每组数据线的阻抗匹配。 本节,我们讲解了DDR的硬件设计过程,下一节我们重点讲解DDR的调试关注点以及基于Hyperlynx的信号完整性分析。 |

|

以太网PHY |

|

DDR4实战教学(一):DDR4寻址原理 看上去很牛逼,那DDR4到底是个啥玩意儿?怎么工作的?硬件设计中都涉及哪些参数?在本系列博文中,我们将为大家娓娓道来。 本文简要探讨DDR4到底是什么,以及简述DDR4的工作原理。 DDR4是什么? DDR4全称,DDR4-DRAM,与其他DDR系列DRAM一样,是当前电子系统架构中使用最为广泛的的RAM存储器。 这句话可以分解出3个关键字:存储器、DRAM、DDR4。 先说存储器,说到存储,顾名思义,它是个动词,以生活为例,假如有个酸奶,你不想吃的时候,将酸奶存到某冰箱、某层、某个位置,当你想吃的时候,在某冰箱、某曾、某个位置中取出该酸奶。 这个过程,我们称为存储,结合生活,我们可以看到存储要有3个关键动作:

所以,概括一下,存储器就是“可以寻址”、“能读写数据”、“能保存数据”的一种电子器件。 我们再说说DRAM。DRAM全称Dynamic Random Access Memory,翻译过来为动态随机读取存储器。所谓随机,指的是“想存哪个位置,就存哪个位置”,听起来很自由,很灵活。所谓动态,指的是保存数据过程中,需要不断的补充电量,听起来很耗电,很费劲,为啥我们还要用DRAM结构?因为在电路结构上,DRAM结构比SRAM简单很多。 最后说说DDR。我们聊到DDR,大家都会联想到存储器,但是实际上DDR并不指代存储器,DDR实际是一种技术,全称Double Data Rate,翻译过来为双倍速率,只是这都技术广泛使用在DRAM上,所以人们习惯将DDR代指为存储器,所以宝宝们在后续的硬件设计过程中,在其他总线上看到DDR,请不要惊慌,因为你看到的DDR可能不一定和存储有关。那双倍速率指的是什么?我们可以简要说下,初代存储器在读写数据时,每次都在时钟信号从低变高或从高变低时,采样数据,在1个时钟周期,只能采样1个数。后续聪明的人类在时钟从低到高时,采样一个数据,时钟从高到低时,再采样1个数据,一个时钟周期,可以采样2个数据。所以读写速度比以前快了2倍。这种技术手段,就指的是DDR。如果看不懂“时钟”和“采样”这段话的,那…… 所以,概括下:DDR4-DRAM是第四代支持双数据读取,支持随机位置存取的静态存储器。 DDR4-DRAM的工作原理 一颗DDR4芯片的内部功能框图如下: 其引脚按照功能可以分为7类:前3类为电源、地、配置。 后4类为:控制信号、时钟信号、地址信号、数据信号 电源、地、配置信号的功能很简单,在此不赘述。控制信号主要是用来完成DDR4与DDR4 Controller之间的状态切换。 DDR4中最重要的信号就是地址信号和数据信号。 如上DDR4芯片有20根地址线(17根Address、2根BA、1根BG),16根数据线。在搞清楚这些信号线的作用以及地址信号为何还有复用功能之前,我们先抛出1个问题。假如我们用20根地址线,16根数据线,设计一款DDR,我们能设计出的DDR寻址容量有多大? 按照课本中学到的最简单的单线8421编码寻址的方式,我们知道20根地址线(连读写控制信号都不考虑了)的寻址空间为2^20,16根数据线可以1次传输16位数据,我们能很容易计算出,如果按照单线8421编码寻址方式,DDR芯片的最大存储容量为: Size(max)=(2^20)16=104857616=16777216bit=2097152B=2048KB=2MB。 但是事实上,该DDR最大容量可以做到1GB,比传统的单线编码寻址容量大了整整512倍,它是如何做到的呢?答案很简单,分时复用。 我们把DDR存储空间可以设计成如下样式: 首先将存储空间分成两个大块,分别为BANK GROUP0和BANK GROUP1,再用1根地址线(还剩19根),命名为BG,进行编码。若BG拉高选择BANK GROUP0,拉低选择BANK GROUP1。(当然你也可以划分成4个大块,用2根线进行编码) 再将1个BANK GROUP区域分成4个BANK小区域,分别命名为BANK0、BANK1、BANK2、BANK3。然后我们挑出2根地址线(还剩余17根)命名为BA0和BA1,为4个小BANK进行地址编码。 此时,我们将DDR内存颗粒划分成了2个BANK GROUP,每个BANK GROUP又分成了4个BANK,共8个BANK区域,分配了3根地址线,分别命名为BG0,BA0,BA1。然后我们还剩余17根信号线,每个BANK又该怎么设计呢?这时候,就要用到分时复用的设计理念了。 剩下的17根线,第一次用来表示行地址,第二次用来表示列地址。 原本传输1次地址,就传输1次数据,寻址范围最多16KB(不要读写信号)。 现在修改为传输2次地址,在传输1次数据,寻址范围最多被扩展为2GB。虽然数据传输速度降低了一半,但是存储空间被扩展了很多倍。这就是改善空间。 所以,剩下的17根地址线,留1根用来表示传输地址是否为行地址。 在第1次传输时,行地址选择使能,剩下16根地址线,可以表示行地址范围,可以轻松算出行地址范围为2^16=65536个=64K个。 在第2次传输时,行地址选择禁用,剩下16根地址线,留10根列地址线表示列地址范围,可以轻松表示的列地址范围为2^10=1024个=1K个,剩下6根用来表示读写状态/刷新状态/行使能、等等复用功能。 这样,我们可以把1个BANK划分成67108864个=64M个地址编号。如下所示: 在每个地址空间中,我们16根数据线全部用起来,一次存储16位数据。 所以1个BANK可以分成65536行,每行1024列,每个存储单元16bit。 每行可以存储1024*16bit=2048bit=2Kb。每行的存储的容量,称为Page Size。 单个BANK共65536行,所以每个BANK存储容量为65536*2KB=128MB。 单个BANK GROUP共4个BANK,每个BANK GROUP存储容量为512MB。 单个DDR4芯片有2个BANK GROUP,故单个DDR4芯片的存储容量为1024MB=1GB。 至此,20根地址线和16根数据线全部分配完成,我们用正向设计的思维方式,为大家讲解了DDR4的存储原理以及接口定义和寻址方式。 在下一节,我们将为大家讲解DDR4的详细工作原理和硬件设计步骤,以及调试时需要注意的参数,以及DDR4的SI仿真。 |

主要参数

4*DDR4 8G 2133

8GB EMMC

2GB NANDFLASH

双千兆网口

PCB工艺

线宽 4mil

扇出通孔 via 8/16 即 0.2mm/0.4mm

电源通孔 via 10/20 即0.25mm/0.5mm

核心板上主要芯片

SOC

Hi3531DV200

A53四核 1.15GHZ

封装:珠间距0.8mm!!!

焊盘 直径0.4mm

Hi3531DV200 芯片采用EHS-TFBGA 封装,封装尺寸为31.2mm x 22.4mm,管脚间距

为0.8mm,管脚总数为791 个。

DDR

SAMSUNG

4A8G165WC-BCRC

https://atta.szlcsc.com/upload/public/pdf/source/20210520/C2834754_65F6FB54A91BE8F8AA4F9922A8DA9F4E.pdf

JEDEC standard 1.2V (1.14V~1.26V)

EMMC

SAMSUNG

KLM8G1GETF-B041

https://atta.szlcsc.com/upload/public/pdf/source/20200730/C499918_BA626D9A4952A33A6B491C88DA3C2D72.pdf

NANDFLASH

MXIC(旺宏电子)

MX35LF2G14AC-Z4I

https://atta.szlcsc.com/upload/public/pdf/source/20210810/9C706514DCEB03A38D5FE8709BFD247E.pdf

以太网

RTL8211F

https://datasheet.lcsc.com/lcsc/1912111437_Realtek-Semicon-RTL8211F-CG_C187932.pdf

主板上工作电压

内核电压 0.9V

CPU电压 1.0V

IO电压 1.8V/3.3V

DDR4 1.2V

DDR3 1.3V

The text was updated successfully, but these errors were encountered: