New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

How to update my riscv-gnu-toolchain to enable RVV support #353

Comments

|

You should checkout to branch 'riscv-gcc-rvv-next' |

|

Thank you for your reply! @zhongjuzhe It looks like I don't build up the toolchain correctly, because the core need 32bit files but I have 64bit now. After that what should I do to satisfy the need of the riscv core? |

|

You should specify --arch=rv32gcv |

|

I think you should try to use --with-arch=rv32gcv in configure. |

|

Hi! @pz9115 .

|

|

Edit: just noticed that you seem to have built a Linux toolchain ( Please note that The If you use the standard libs then, in order for the software to link without errors, you'll also need to specify If your makefile/build scripts reference What version of the V extension does your target implement? |

|

Actually, on reflection, it's probably simpler for your purposes, if you're targeting rv32imv, to do... to build the toolchain just for your target architecture/abi. |

|

Thank you for your patient reply! @TommyMurphyTM1234 .I benefited a lot from your answer. I want to know, is the rvv-next branch support Intrinsic coding? When I choose LLVM as the compiler(which is successful) to compile RVV Intrinsic C code, the output would be like: |

rvv-next support all RVV feature including intrinsic and auto-vectorization. Would you mind share your codes? And also you need to check whether you are using the latest branch "riscv-gcc-rvv-next" in riscv-gcc. |

|

Thank you @zhongjuzhe and this command to make: |

|

cd riscv-gcc && git log |

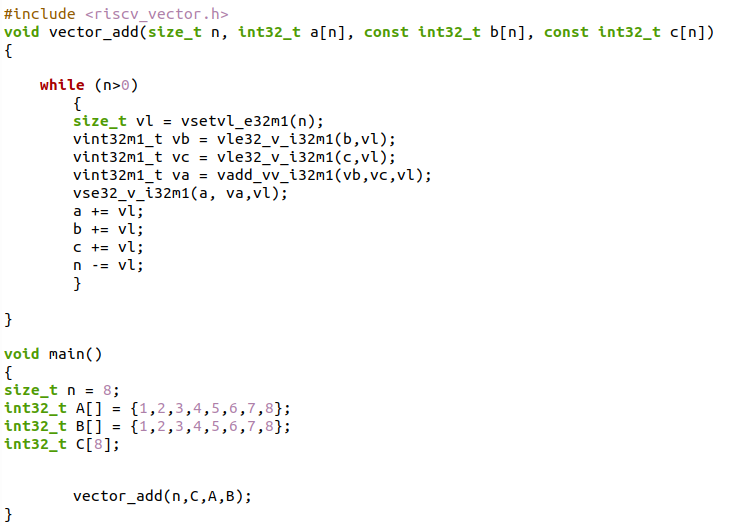

Would you mind giving me the whole program? including the main function and data initilization. |

|

No, plz Don't git log in riscv-gnu-toolchain directory. Plz git log riscv-gcc directly. cd riscv-gcc and then git log. |

|

These codes are obsolete. Plz git pull in riscv-gcc and rebuild the toolchain. The latest commit of risc-gcc-rvv-next should be commit 53fcb21. And try your program again. |

|

That's the problem! @zhongjuzhe I pull the latest commit and compile the code successfully. |

|

@schwa1z Hope you are doing good. Can you please share the steps you follow to compile the Vector C code. As i am also trying to configure the toolchain for RV32IMFCV target. I have gone through the whole conversation and as mention i also try git log and it shows the same message as you post it here but when it try to run git pull it gives me an error so may be i am doing something wrong. Your steps may help me out. Thanks in advance |

|

@HamzaShabbir517 Yes, I'm glad to share my method to configure the toolchain. then, in .../riscv-gnu-toolchain/, switch to 'riscv-gcc-rvv-next'branch, and pull the latest version After that, configure the toolchain:(for you maybe --with-arch=rv32imfcv? I'm not sure), note that you need to configure the environment varible in bashrc. If you don't know how to configure the environment varible, tell me. and make: |

|

@schwa1z Thanks i was able to build it. |

|

@HamzaShabbir517. There are two ways to call riscv vector instructions. I'm a little bit of confused about your last question. When you write specific Intrinsic/inline assembly in C code to call vector instruction, the compiler just compile the specific instruction you write, instead of translating other instructions. |

|

I don't find this instruction in riscv-v-spec-1.0. But it looks strange. I don't know how to prevent the compiler to generate specific instruction. Maybe you could open a new issue. |

|

vl1re32 is whole register load which is a common use instruction. You can find it inchapter 7.9---- Replied Message ***@***.***>Date08/28/2022 15:46 ***@***.***> ***@***.******@***.***>SubjectRe: [riscv-collab/riscv-gcc] How to update my riscv-gnu-toolchain to enable RVV support (Issue #353)

I don't find this instruction in riscv-v-spec-1.0. But it looks strange. I don't know how to prevent the compiler to generate specific instruction. Maybe you could open a new issue.

—Reply to this email directly, view it on GitHub, or unsubscribe.You are receiving this because you were mentioned.Message ID: ***@***.***>

[

{

***@***.***": "http://schema.org",

***@***.***": "EmailMessage",

"potentialAction": {

***@***.***": "ViewAction",

"target": "#353 (comment)",

"url": "#353 (comment)",

"name": "View Issue"

},

"description": "View this Issue on GitHub",

"publisher": {

***@***.***": "Organization",

"name": "GitHub",

"url": "https://github.com"

}

}

]

|

I have tried your code using RVV GCC There is no vl1re32.v instructions when I compile using O3. Here is code-gen in LLVM: |

|

thanks everyone for helping me out. Really appreciate it. |

|

It's wierld. I don't know how you get this.

My compilation works well:

codes:

#include <riscv_vector.h>

void foo (size_t n, uint32_t a[n], const uint32_t b[n], const uint32_t c[n])

{

while (n > 0)

{

size_t vl = vsetvl_e32m1 (n);

vuint32m1_t vb = vle32_v_u32m1 (b, vl);

vuint32m1_t vc = vle32_v_u32m1 (c, vl);

vuint32m1_t va = vadd_vv_u32m1 (vb, vc, vl);

vse32_v_u32m1 (a, va, vl);

a += vl;

b += vl;

c += vl;

n -+ vl;

}

}

assembly:

foo:

beq a0,zero,.L1

.L3:

vsetvli a5,a0,e32,m1,ta,mu

slli a4,a5,2

vle32.v v24,(a2)

vle32.v v25,(a3)

add a2,a2,a4

vadd.vv v24,v24,v25

add a3,a3,a4

vse32.v v24,(a1)

add a1,a1,a4

j .L3

.L1:

ret

***@***.***

From: HamzaShabbir517

Date: 2022-08-28 21:06

To: riscv-collab/riscv-gcc

CC: zhongjuzhe; Mention

Subject: Re: [riscv-collab/riscv-gcc] How to update my riscv-gnu-toolchain to enable RVV support (Issue #353)

@zhongjuzhe Here is the assembly generated by GCC Compiler i also used -03 flag in my compile command

—

Reply to this email directly, view it on GitHub, or unsubscribe.

You are receiving this because you were mentioned.Message ID: ***@***.***>

|

|

@zhongjuzhe Can you try this code as well at your side. } void main() } I am getting this assembly Disassembly of section .text.startup: ee000026 :ee000026: f0040737 lui a4,0xf0040 ee00002a: 711d addi sp,sp,-96 ee00002c: 00070613 mv a2,a4 ee000030: 02000793 li a5,32 ee000034: 868a mv a3,sp ee000036: 00070713 mv a4,a4 ee00003a: 0c37f5d7 vsetvli a1,a5,e8,m8,ta,ma ee00003e: 02070c07 vle8.v v24,(a4) ee000042: 8f8d sub a5,a5,a1 ee000044: 02068c27 vse8.v v24,(a3) ee000048: 972e add a4,a4,a1 ee00004a: 96ae add a3,a3,a1 ee00004c: f7fd bnez a5,ee00003a <main+0x14> ee00004e: 02000793 li a5,32 ee000052: 1018 addi a4,sp,32 ee000054: 0c37f6d7 vsetvli a3,a5,e8,m8,ta,ma ee000058: 02060c07 vle8.v v24,(a2) ee00005c: 8f95 sub a5,a5,a3 ee00005e: 02070c27 vse8.v v24,(a4) ee000062: 9636 add a2,a2,a3 ee000064: 9736 add a4,a4,a3 ee000066: f7fd bnez a5,ee000054 <main+0x2e> ee000068: 0094 addi a3,sp,64 ee00006a: 1008 addi a0,sp,32 ee00006c: 880a mv a6,sp ee00006e: 4721 li a4,8 ee000070: 050777d7 vsetvli a5,a4,e32,m1,ta,mu ee000074: 00279613 slli a2,a5,0x2 ee000078: 02086c07 vle32.v v24,(a6) ee00007c: 02056c87 vle32.v v25,(a0) ee000080: 8f1d sub a4,a4,a5 ee000082: 038c8c57 vadd.vv v24,v24,v25 ee000086: 0206ec27 vse32.v v24,(a3) ee00008a: 9832 add a6,a6,a2 ee00008c: 96b2 add a3,a3,a2 ee00008e: 9532 add a0,a0,a2 ee000090: f365 bnez a4,ee000070 <main+0x4a> ee000092: 6125 addi sp,sp,96 ee000094: 8082 ret |

You really should post the actual code and not a screenshot expecting the other person to manually type the code in. |

You should use -fno-tree-vectorize to disable auto-vectorization |

|

I have tried the flag as you mention but nothing happen got the same assembly as above. These are the CFlags i am using TEST_CFLAGS = -march=rv32imfcv -mabi=ilp32f -O3 -fno-tree-vectorize |

You said : This assembly is correct. What's the problem? |

|

The problem is in the main loop: ee000026: f0040737 lui a4,0xf0040 ee00002a: 7159 addi sp,sp,-112 ee00002c: 00070613 mv a2,a4 ee000030: 02400793 li a5,36 ee000034: 1034 addi a3,sp,40 ee000036: 00070713 mv a4,a4 ee00003a: 0c37f5d7 vsetvli a1,a5,e8,m8,ta,ma ee00003e: 02070c07 vle8.v v24,(a4) ee000042: 8f8d sub a5,a5,a1 ee000044: 02068c27 vse8.v v24,(a3) ee000048: 972e add a4,a4,a1 ee00004a: 96ae add a3,a3,a1 ee00004c: f7fd bnez a5,ee00003a <main+0x14> as here u can see to load scalar data it is also using vector instruction i want to stop that |

|

You can use -Os instead of -O3. It will stop optimizing "memcpy" using vector instructions. |

|

I have build both the toolchains for 64 and 32 by using the following commands for 64 bit for 32 bit But still will try to build a specific toolchain and will try to compile it again |

You don't need this toolchain.

You don't need multilib. I forgot about |

|

ok i will try it and get back to you |

|

@TommyMurphyTM1234 @zhongjuzhe I have rebuild the toolchain by using the following command Now when i compile the code by using following CFLAGS The code got compile by this have some memcy function in which there are lots of instructions ee000000 <vector_add>: Disassembly of section .text.startup: ee000026 :ee000026: 7159 addi sp,sp,-112 ee000028: d4a2 sw s0,104(sp) ee00002a: f0040437 lui s0,0xf0040 ee00002e: 00040593 mv a1,s0 ee000032: 02000613 li a2,32 ee000036: 850a mv a0,sp ee000038: d686 sw ra,108(sp) ee00003a: 026000ef jal ra,ee000060 ee00003e: 00040593 mv a1,s0 ee000042: 02000613 li a2,32 ee000046: 1008 addi a0,sp,32 ee000048: 018000ef jal ra,ee000060 ee00004c: 1014 addi a3,sp,32 ee00004e: 860a mv a2,sp ee000050: 008c addi a1,sp,64 ee000052: 4521 li a0,8 ee000054: fadff0ef jal ra,ee000000 <vector_add> ee000058: 50b6 lw ra,108(sp) ee00005a: 5426 lw s0,104(sp) ee00005c: 6165 addi sp,sp,112 ee00005e: 8082 ret Disassembly of section .text.memcpy: ee000060 : This is the whole code. When i run the same code on godbolt.org so the code compile from there is something like this Now what should i do |

|

This is the make file command i am using to build the code |

|

Your makefile snippet is impossible to read. |

|

@TommyMurphyTM1234 I have updated the code in the previous comment of mine I understand your problem now. You want to use scalar instructions to do the memcpy. However, current rvv-next enable optimizing memcpy using RVV instructions. I will add a compile option to disable this today. After I have done this, I will tell you to pull the latest codes. |

I understand your problem now. You want to use scalar instructions to do the memcpy. However, current rvv-next enable optimizing memcpy using RVV instructions. I will add a compile option to disable this today. After I have done this, I will tell you to pull the latest codes. |

Plz pull the latest codes, the latest code should be: |

|

ok thanks i will rebuild in and let you know |

|

@TommyMurphyTM1234 @zhongjuzhe Thanks its working completely fine now |

I presume you meant @zhongjuzhe ? 🙂 |

Hi @HamzaShabbir517 - should these instructions still work? When I try them I get this: |

|

@TommyMurphyTM1234 Yes but i think you dont need to git pull as when you checkout it checkout the branch with all the updates |

Hello community!

For some reason I want to use GCC as the compiler to support riscv-vector extension compilation. Long ago, I have installed gcc and riscv-gcc. The following is the version information now:

when I type

gcc --versionin terminal:and about riscv-gcc, the information in /riscv-gnu-toolchain/readme.md:

since I'm confused about the relationship between gcc and riscv-gcc, I put all the information here. RVV extension is not supported in this version.

Now I want to update the version of my toolchain to enable RVV extension support. What should I do and what command should I type?

Thank you very much!

The text was updated successfully, but these errors were encountered: