-

Notifications

You must be signed in to change notification settings - Fork 2

Home

Documentation is here.

Metlino is an extension for N.A.T. MicroTCA carrier hub (MCH) optimized for use with Sinara hardware. Together with MCH, it serves as the crate master, controlling uTCA peripherals, such as the Sayma AWG, RFSOC-AMC or Shuttler, in real-time by sending ARTIQ DRTIO commands over the crate backplane (MCH Fabric D). It can also control additional ARTIQ peripherals via the SFP and VHDCI connectors on the front panel.

Metlino can be used either as the ARTIQ master or as an ARTIQ DRTIO slave connected to the master via DRTIO. In master mode, it receives commands from the host PC via ethernet, wherein slave mode, it receives commands from the ARTIQ master via DRTIO link.

Metlino provides 64 LVDS IOs, accessible through 2 VHDCI connectors, as well as 1 FMC LPC. The VHDCIs are compatible with the VHDCI carrier and Eurocard extension modules and can be used to drive such EEM like Sampler, Urukul or DIO BNC.

PDF with schematics for the latest release is available here.

- Kintex UltraScale KU040 FPGA (XCKU040-1FFVA1156C) speed grade -1, motivation for this design choice is here

- 2 GB DDR3L SDRAM (4x 4Gb)

- 2x 32 MB flash memory for FPGA configuration

- JTAG and UART (both to MMC and FPGA) available via onboard microUSB connector (FT4232H Multipurpose UART/MPSSE IC)

- Si5324-based clocking system with hardware support for DDMTD White Rabbit implementation

- Ethernet connectivity to BaseBoard using either FPGA MGT or Marvel 88E1512 RGMII phy

- LPC1776-based management platform for communication with BaseBoard, monitoring and configuration

- Connectors:

- 3 SPF, all routed to FPGA MGT

- 2 VHDCIs providing low-latency digital outputs, and control of EEMs

- 1 FMC LPC with up to 5 DP

- front panel SMA clock output

- front panel SMA reference / clock input

- rear MCX clock input

- MCH Fabric D: 12 TX/RX pairs (MGT 224-225)

- SFP: 3 TX/RX pairs (MGT228/0-2)

- FMC DP: 4/5 TX/RX pairs (MGT 227, MGT 228/3) see note below

- Ethernet: 1 TX/RX pair (MGT 228/3) see note below

FMC DP4 is mutually exclusive with MGT-based Ethernet. If DP4 is to be routed to MGT, RGMII PHY based Ethernet must be used.

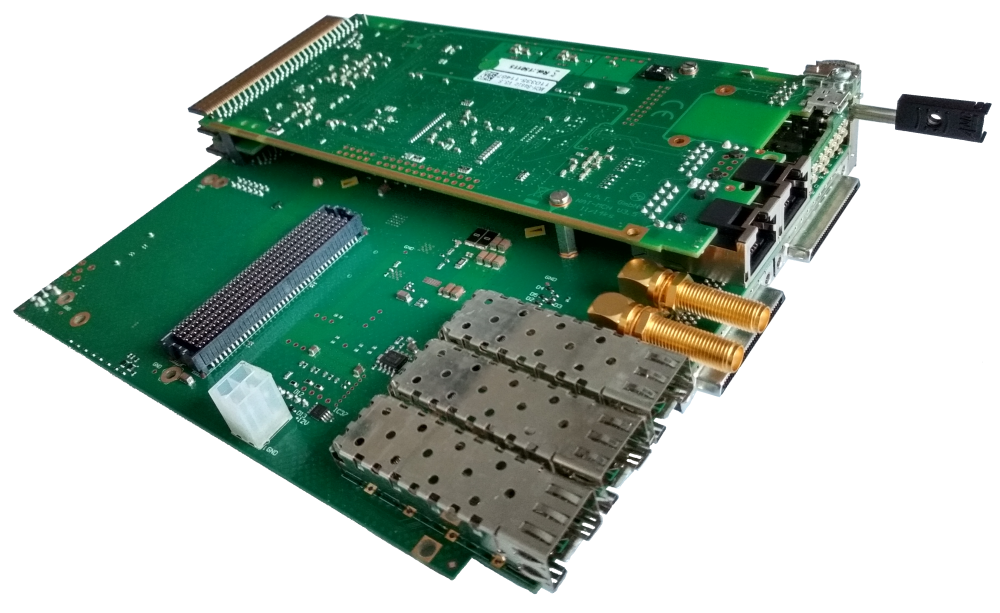

The standard MicroTCA backplane has a many-to-one topology with a MicroTCA Carrier Hub (MCH) that sits at the center. The MCH connects to the backplane via four edge-connect sockets (tongues). Metlino occupies MCH tongues 3 & 4. To assemble Metlino on top of the NAT NAT-MCH-Base12-GbE a simple separating board filling tongue slot 2 is required. All three boards assembled have a single panel (in production) and act as a single device.

To be described