-

Notifications

You must be signed in to change notification settings - Fork 169

New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

Spread-Spectrum Clockings (SSC) settings missing in APL #696

Comments

|

Did you check FIT soft strap in Flex I/O ? |

|

Yes looks like all defaults disabled and LCPLL_CR_RW_CONTROL_1 disabled as well, closing issue |

|

Hi We used a default configuration of LCPLL_RW_CONTROL_1_DEFAULT.SSC_EN as Disable in FIT tool. However, our suspicions that #715 caused because SSC is applied or not disabled at the right time (too late). Andrey |

|

Hi Andrey, Programming of both LJ1PLL and LCPCC SSC in bootloader requires IPC CMD interface for PMC. The IPC CMD library is not available in SBL. |

|

Had to reopen an issue because we've found that the setting from the FIT tool have no any effect. The SSC is enabled from the boot start |

|

Hi As thau-my mentioned earlier, SSC can be controlled via FIT settings. In addition to that, there are some IPC/SideBand Interfaces available to control it during boot. For reference please look at EDK2 support for APL I believe Intel reference BIOS enables SSC and SBL does not. One suggestion I would have is for you to flip the current FIT setting and see if it makes a difference. |

|

Hi Regarding to the changes that I can make in edk2-platform, see the answer on my question from #704. Can you please instruct how to bring 'IPC CMD interface for PMC' into SBL and I will do it? I am relatively familiar with your code already Andrey |

|

Hi I've made a different flip flops to change settings like (made a lot of different permutations): So, SSC actually never disabled !!!!!! Andrey |

|

Hi Can you update if the SBL has a bug with a FIT tool for the specific settings? Andrey |

|

Hi FIT manipulates the soft strap settings in the descriptor region and SBL has no direct interaction with these settings. So I don't think this is an SBL bug. Regarding your other question, I provided the link to a reference on how to control SSC in firmware during boot. Please check PlPeiHighSpeedSerialInterfaceSSCInit and PeiDDRSSCInit functions in this link https://github.com/tianocore/edk2-platforms/blob/devel-IntelAtomProcessorE3900/Platform/BroxtonPlatformPkg/Common/PlatformSettings/PlatformPreMemPei/PlatformInitPreMem.c Thanks. |

|

Hi Would it be possible for you to file an IPS ticket with Intel to get some hardware inputs regarding your requirements/issue. Meanwhile, if you would like to disable SSC through SBL, you have to port the code I referred above to SBL. BoardInit (Phase - PostConfigInit) in https://github.com/slimbootloader/slimbootloader/blob/master/Platform/ApollolakeBoardPkg/Library/Stage1BBoardInitLib/Stage1BBoardInitLib.c may be a good place to implement this. |

|

Hi rprangar Thank you for an update, it looks like I got how to port sideband and IPC, I will update a status after porting and testing Andrey |

|

Hi rprangar I've completed sideband interface porting to SBL can send you code to review and checkout

Andrey |

|

I've completed IPC interface porting also, and only now reading from LCPLL_CTRL_1 receives the correct FIT settings. Have to test it a bit more tomorrow So, I would like to submit 2 changesets for review

|

|

Hi Yes, your contributions are very welcome. Please refer https://slimbootloader.github.io/developer-guides/contributions.html for the github pull request flow. Thanks. |

|

bit lost in creation of pull request (I am a new bee in using git). It returns an error : Creating pull requests for 'slimbootloader:SideBand' failed: Validation Failed I've created a patch with a SideBand interface only and IPC interface |

|

Unfortunately, I can read from FIT setting and see the changes I am making. But setting everything disable in SBL has no effect to SSC (it is always enabled) "..Default values are applied during cold boot and come from the SMIP. If the values need to be updated then the host must initiate an IPC1 command to the PMC withcommand encoding of 0xE8 (EMI/RFI support). Using this command the LJ1PLL registers will be updated after a reset sequence. - That's what it says for LJ , I would assume it's the same situation. It doesn't really say what reset sequence is required" |

|

Any reset has to be conditional - in this case, it would translate to boot-check setting -apply setting-reset-boot-check setting-continue boot. Otherwise the boot will get stuck in a reset cycle. At this point, I would recommend to file an IPS ticket with Intel to get inputs from the HW PAE. There are certain other implications of disabling SSC on which the HW PAE team would be able to provide inputs. |

|

can't really understand why SSC is enabled, reading from FIT setting using IPC interface can verify LJ1PLL and LCPLL SSC is set disabled. However, the board is starting up and continue booting with SSC enabled my patch to the IPC interface is here: |

|

Did you verify that both DDR SSC (LJ1PLL) and HSIO SSC (LCPLL) enable even though set to disable? |

|

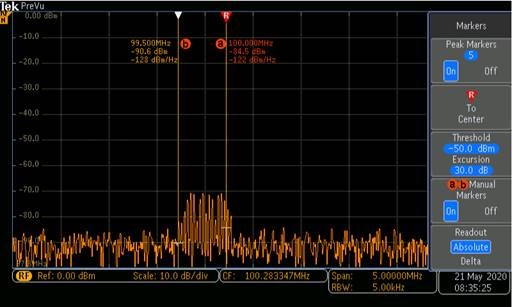

I am verifying it before DDR training (FSP init) https://github.com/andreyv1978/slimbootloader/pull/1/commits/eca86812ad2fd4ca9992d3ad3b84f7a9c31d7527#diff-991058d987bad5212a26703fab2aa2bd After it finishes we are measuring it in SBL shell, can see the attached images previously |

|

I think there may be some confusion. I believe the UEFI reference code that I pointed out earlier, changes the SSC setting through a register. It does not change the soft strap setting in the descriptor set by FIT. I would recommend to continue the follow up through IPS. |

|

I've got an answer from Intel "Disabling SSC in Apollo Lake is not supported / not POR (Plan of Record), not validated and not recommended. It is not possible to disable SSC for PCIe only. There are other IPs that will be impacted if SSC is disabled. If you still want to use this, for own testing, the process for CRB is to leave SSC enabled in FIT and set the override enabled strap, then make according changes in BIOS menu. For own BIOS/Bootloader, the implementation needs to follow the example provided in the comment on Github. Example for UEFI BIOS can be found in the Open Source version of Apollo Lake reference code: The fragment that controls whether SSC is enabled or disabled is based on this parameter: SystemConfiguration.HSSIOSSCEnable and the method called is PeiHighSpeedSerialInterfaceSSCInit. As the file says the SSC enable/disable will affect the following IPs: USB3, PCie, SATA, eDP, DP, eMMC, SD and SDIO SSC Our hardware team is checking if we can add some more details/clarification in our collateral around this topic. Andey |

|

Hi rprangar Maybe you can help me to make it faster:

My problem:

example: right now i am in: Andrey |

|

Hi Andrey The BIOS code is written in a way to allow end users enable/disable SSC. The way end users are allowed to modify this option is by exposing variables (DDRSSCEnable and HSSIOSSCEnable) through the BIOS setup screen. These two options along with many other options are packaged in a structure called SystemConfiguration. This structure is initialized using the UEFI Variable services. This is very much a UEFI BIOS feature. Now, SBL does not support a setup screen where an end user can change certain settings on the fly. The current equivalent approach supported by SBL is the configuration mechanism. This is a static way to configure things (link). So, the approach you are trying to take - to access DDRSSCEnable and HSSIOSSCEnable through PLATFORM_SETUP_VARIABLE_NAME using gEfiPeiReadOnlyVariable2PpiGuid will not work. SBL does not support this. If you want to provide a static option, you need to add this to the SBL configuration structure that can be modified during build time. However, coming to your requirement, if for testing, you want to set SSC enable first, wait for it to get enabled, and then disable it and trigger system restart, you can simply do that. You dont need DDRSSCEnable and HSSIOSSCEnable variables. Copy pasting the code from the EDK2 reference // // // // // I assume this is for testing as this will never boot as the reset is not conditional and it will always reset after enable-wait-disable flow. |

|

I think you can align the SSC handling code in SBL with the APL EDK2 tree. When the Setup variable is required from SystemConfiguration, instead of reading the UEFI variable, you can just use the argument to pass it into function. EX: the following two interfaces can be provided in SBL code. |

|

We have an old BIOS partially made for us by someone else, it looks like uses a full edk2 source code with UEFI BIOS features (i can see all of that when reading debug logs). The first step they are doing is enabling SSC, which are clearly indicated by printing messages after checking HSSIOSSCEnable. The next step is a manual selection of SSC disable and the restart is triggered. At the end the SSC is disabled and the board always boot with SSC disable. I am trying to do the same, but without UEFI BIOS functioanlities. I can trigger SSC enable and wait to the paylod stage (but without having HSSIOSSCEnable, I wouldn't know it applied or not ). The next I can trigger SSC disable and make the cold restart, but I need HSSIOSSCEnable to know that now I am on stage of SSC disable and should not enable it again. Maybe the different approach:

|

|

HSSIOSSCEnable is a setup option. So once it is set in UEFI BIOS, it is static and will not change unless you go to the setup screen to change it again. EX: if you have it enabled in setup, it will always have a value 1. |

|

The following flow is working in our old BIOS (as a pure test :) ):

The FIT setting are not valid because Intel is always have SSC enable by default, but for some reason it should be set enabled as well. I've tried only booting with SSC disable option set in multiple stages Stage 1, or 1B or Stage 2, but it is never set at the end. |

|

Adding the Intel response: CfgData would be alternative to UEFI variables. With CfgData you could have 2 images, with and without SSC configuration for your testing. So, the FIT would not change the behavior of SSC, keeping it enabled at first during boot, then during pre-memory initialization SBL could turn it off. |

|

For the recent code you added into SBL, shouldn't we set ssc_en_over to SSC_ENABLE for both DDR and HSIO SSC ? Without overriding, I guess the actual ssc_en setting will not take effect. WBuf.LJ1PLL_CTRL_1.Fields.ssc_en_ovr = SSC_DISABLE; => SSC_ENABLE ? Your original code: ... // ... // disable SSC |

|

Hi mauricema I've made a few additons to my SBL bios to test a multiple options

So, i've made experiment and set SSC disable according to the flow:

The result even after multiple board resets the SSC still enabled Experiment 2: The result still the same SSC enabled and DOWN_SPREAD_ONLY What am I doing wrong ? Where should I initiate SSC settings ? It looks like nothing applied at all Andrey |

|

Andrey,

|

|

BTW, did you try to use your working BIOS as a base image to stitch SBL IFWI using StitchLoader.py ? |

|

the working scenario is our old BIOS from the external company, I do not have source code, only can use DEBUG BIOS to get a full log Line 81: HSSIO : Setup Variable is not ready for SSC setting! Leave the default system HSSIO SSC settings!! Line 31340 : I've added a marker at the point that the BIOS menu is accessed and F10 is pressed to save settings Line 31372: After a restart the correct value is written to disable SSC After a power cycle the log phoenixputtynewboot is captured: |

hm, not tried to be honest |

|

We want to know if some of the FIT settings have impact on the register settings. Aslo in your working BIOS, what is the setup variable value for DDR and HSIO SSC when you enter the setup screen ? |

|

good question, let me check everything on Monday |

|

Also please try the following instead: Could you try following ? SSC_LCPLL_IPC_BUFFER WBuf; BufferSize = sizeof (UINT32) * 2; //High Speed Serial IO SSC disable |

Looks like my source code is missing a following: Using the IPC IPC_SUBCMD_ID_SSC_APPLY_NOW instead works only 'Stage 1B before FSP Memory Init', trying to set it in any other place stuck the boot I've tested Phoenix bios stitching it with SBL, proven that the SSC still enabled |

|

just making a new experiment from the previously uploaded log: phoenixputty.log line 12657, they set SSC enable first before SiInitPrePolicy() I hope, i am doing similar experiment but setting SSC disable: Stage2BoardInitLib.c line 1046 PreSiliconInit: adding: PeiDDRSsc: And immediately: The boot is stuck on IpcSendCommandEx(IPC_CMD_ID_EMI_RFI_SUPPORT, IPC_SUBCMD_ID_SSC_APPLY_NOW, &WBuf, BufferSize); --> what is wrong ? |

|

SSC_LCPLL_IPC_BUFFER is a structure containing just two DWORD. IPC_SUBCMD_ID_LCPLL_APPLY_NOW is 0x03. IPC_SUBCMD_ID_SSC_APPLY_NOW should not be used for SSC_LCPLL_IPC_BUFFER since the buffer size does not match. |

|

I only have this with 0x03 |

|

Both are correct. These are sub commands. They have different primary command. BufferSize = 8; |

|

WBuf[0] BIT0 is ssc_en_ovr, and BIT1 is ssc_en. You might want to set |

|

Hi mauricema Made a variety of tests today using your recommendation as: also tried to use 0x4 instead of 0x3 all tests are passed to the shell and SSC was enabled Andrey Andrey |

|

If that is the case, I have no further idea on what to try. Since disabling SSC is not POR, not sure if it has been fully validated. Maybe you can follow up through the IPS ticket. |

|

thank you for your help |

|

I am closing this issue. If there is any new information regarding this issue, please feel free to reopen it. Thanks. |

|

Hi rprangar I've been away for some time, but now back online and need to sort out SSC. Andrey |

|

Hi rprangar coreboot have nothing to configure for SSC, therefore parked it |

|

Just a quick update from Intel "....I did some testing Friday on APL CRB with F1 stepping and latest BIOS and couldn't see changes in the behavior using the knobs on my side. |

Hi

I am not be able to find settings for the Spread-Spectrum Clocking (SSC) on its PCIE_CLKOUT outputs

I should set not to use it in the Apollo Lake settings

Can you help me to find it out how to configure in SBL ?

Andrey

The text was updated successfully, but these errors were encountered: