- Abstract

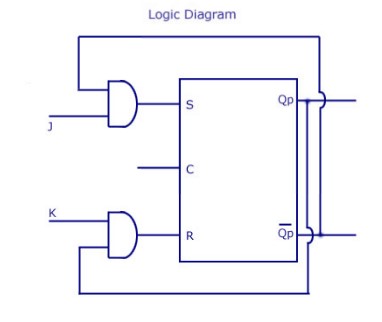

- Reference Circuit Diagram

- Circuit Details

- Truth Table for Digital AND Gate

- Software Used

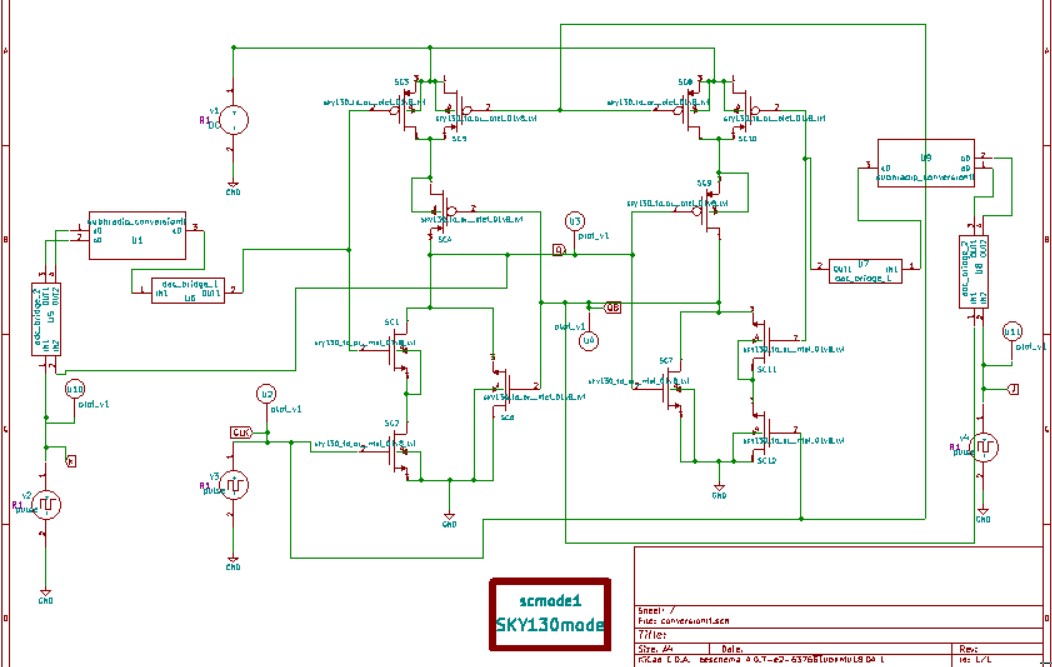

- Circuit Diagram in eSim

- Verilog Code

- Makerchip

- Makerchip Plots

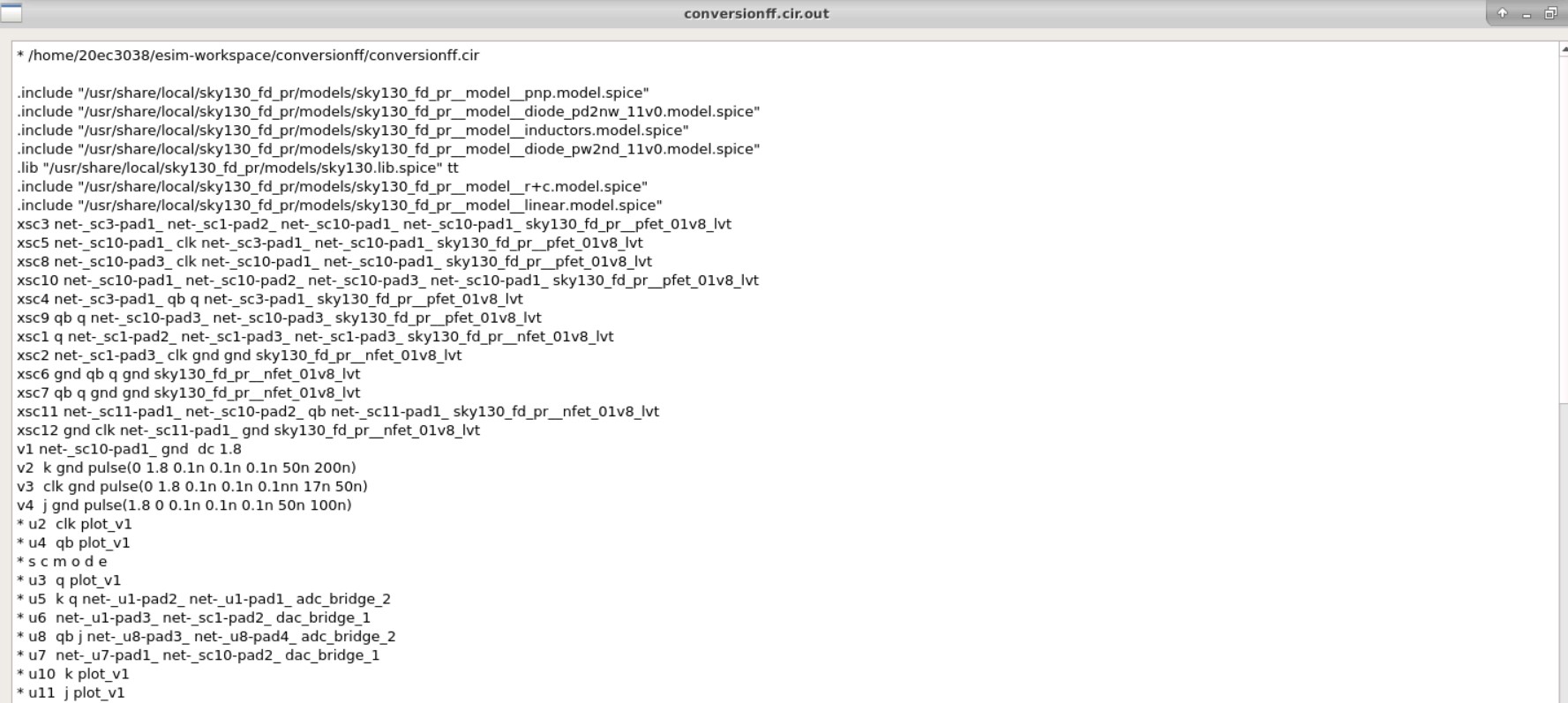

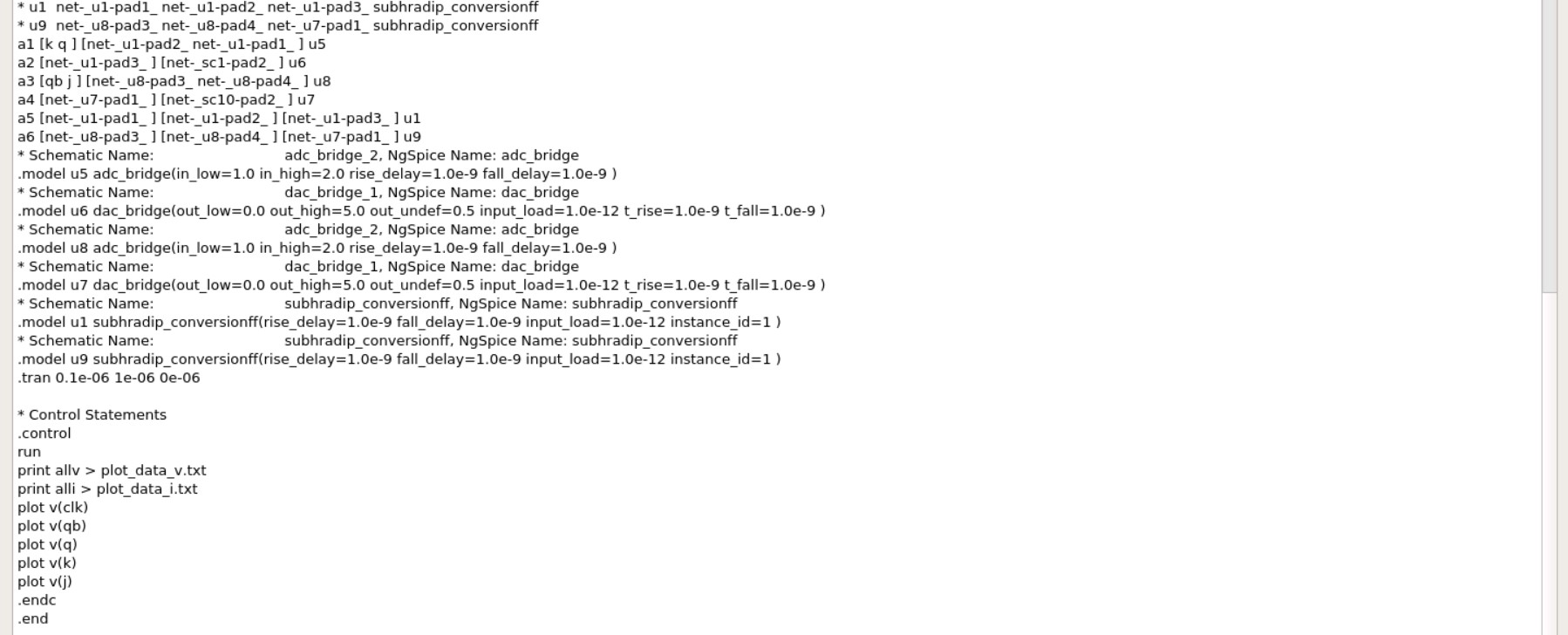

- Netlists

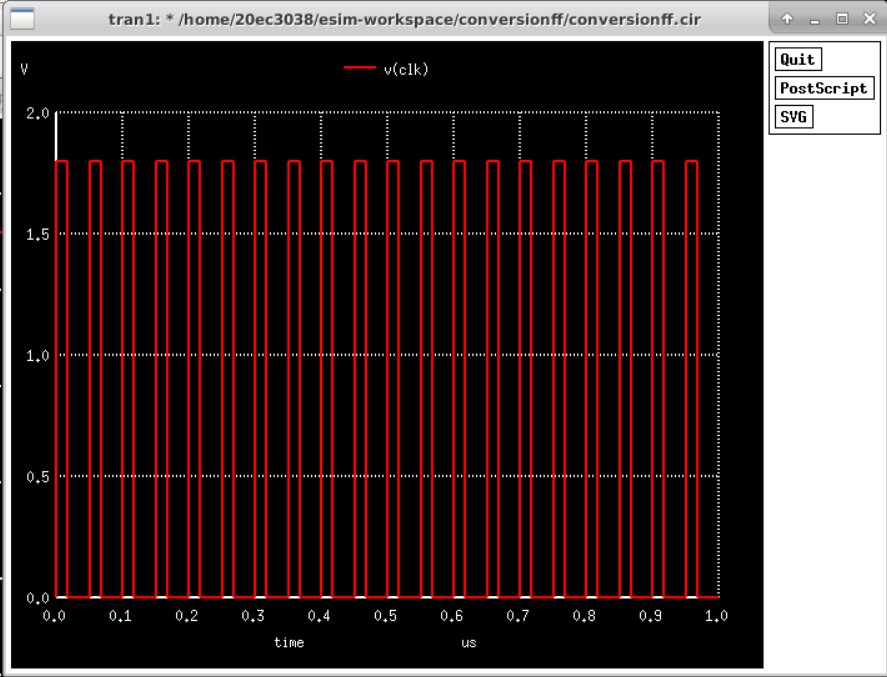

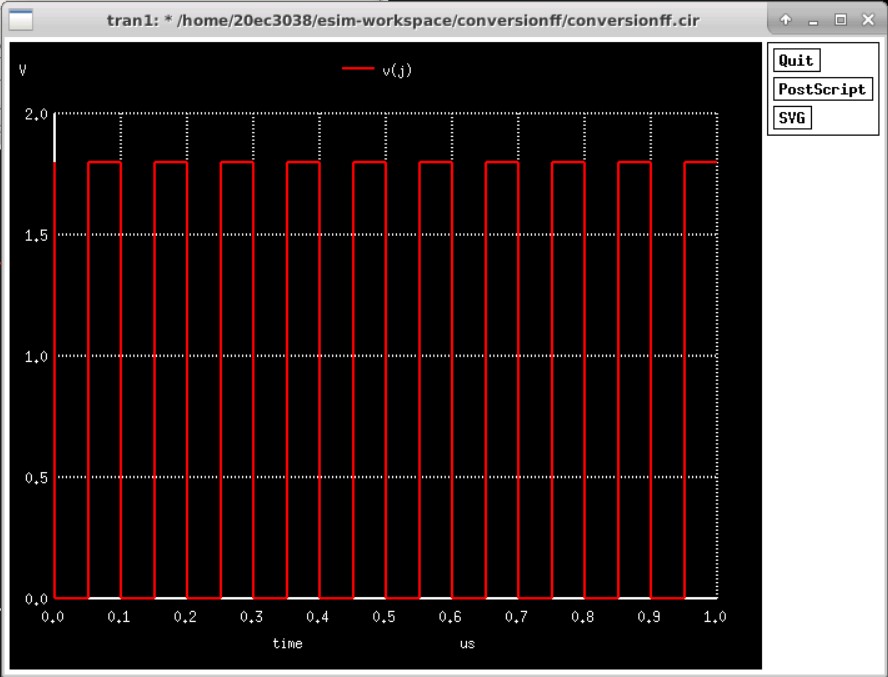

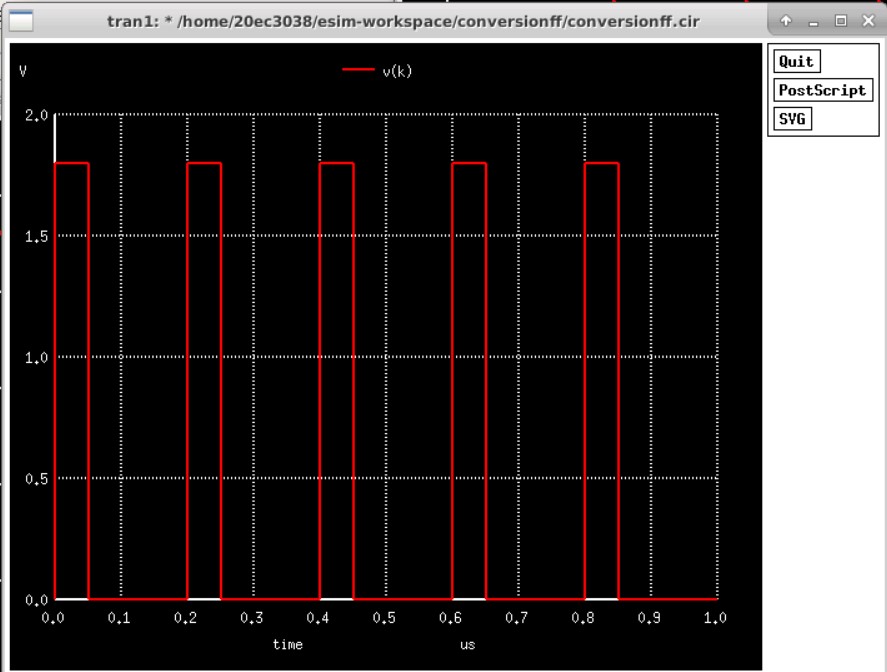

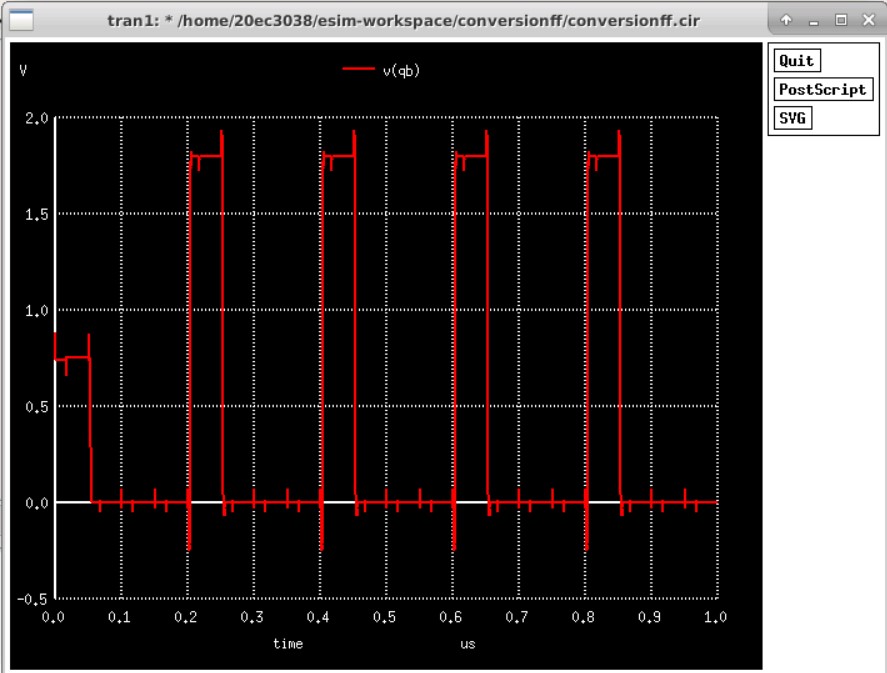

- NgSpice Plots

- Combined Plot

- Acknowlegdements

- References

In this design we are presenting the conversion of SR Flip Flop to JK Flip Flop using SKY130. Flip Flops are widely used in electronic circuit as they have frequency division property. Flip Flops are widely used in counters, registers and in any data transfer block. The design we are going to use for this conversion is the SR Flip Flop will be made of analog block and the gates which provide input to the SR Flip Flop will be made of digital block.

CMOS Implementation of SR Flip Flop & Block Diagram for conversion of SR Flip Flop to JK Flip Flop

As shown in the figure we can see that the the actual input of the SR Flip

Flop are S and R, the external inputs of the SR Flip Flops are

J and K. We will see a total of 8 combinations as input out of

which some values are don’t care in S and R. We are able to

draw this circuit by simplifying the K-Map.

The K-Map is derived from the the truth table of JK Flip Flop

and excitation table of SR Flip Flop.

In the figure as shown above we see the implementation of the SR Flip Flop

using CMOS.This part of our circuit will be the analog circuitry block. The circuit designed is a sky130 circuit as

shown in the CMOS implementation.

The digital block implementation using Verilog Hardware Description Language will be the used to design the AND gate which feeds input to the the S and R input of the CMOS based SR Flip Flop.

| Input A | Input B | Output AND |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

It is an Open Source EDA developed by FOSSEE, IIT Bombay. It is used for electronic circuit simulation. It is made by the combination of two software namely NgSpice and KiCAD.

For more details refer:

https://esim.fossee.in/home

It is an Open Source Software for Spice Simulations. For more details refer:

http://ngspice.sourceforge.net/docs.html

It is an Online Web Browser IDE for Verilog/System-verilog/TL-Verilog Simulation. Refer

https://www.makerchip.com/

It is a tool which converts Verilog code to C++ objects. Refer: https://www.veripool.org/verilator/

The following is the schematic in eSim:

module subhradip_conversionff(c,a,b);

input a,b;

output c;

and (c,a,b);

endmodule

\TLV_version 1d: tl-x.org

\SV

/* verilator lint_off UNUSED*/ /* verilator lint_off DECLFILENAME*/ /* verilator lint_off BLKSEQ*/ /* verilator lint_off WIDTH*/ /* verilator lint_off SELRANGE*/ /* verilator lint_off PINCONNECTEMPTY*/ /* verilator lint_off DEFPARAM*/ /* verilator lint_off IMPLICIT*/ /* verilator lint_off COMBDLY*/ /* verilator lint_off SYNCASYNCNET*/ /* verilator lint_off UNOPTFLAT */ /* verilator lint_off UNSIGNED*/ /* verilator lint_off CASEINCOMPLETE*/ /* verilator lint_off UNDRIVEN*/ /* verilator lint_off VARHIDDEN*/ /* verilator lint_off CASEX*/ /* verilator lint_off CASEOVERLAP*/ /* verilator lint_off PINMISSING*/ /* verilator lint_off BLKANDNBLK*/ /* verilator lint_off MULTIDRIVEN*/ /* verilator lint_off WIDTHCONCAT*/ /* verilator lint_off ASSIGNDLY*/ /* verilator lint_off MODDUP*/ /* verilator lint_off STMTDLY*/ /* verilator lint_off LITENDIAN*/ /* verilator lint_off INITIALDLY*/

//Your Verilog/System Verilog Code Starts Here:

module subhradip_conversionff(c,a,b);

input a,b;

output c;

and (c,a,b);

endmodule

//Top Module Code Starts here:

module top(input logic clk, input logic reset, input logic [31:0] cyc_cnt, output logic passed, output logic failed);

logic a;//input

logic b;//input

logic c;//output

//The $random() can be replaced if user wants to assign values

assign a = $random();

assign b = $random();

subhradip_conversionff subhradip_conversionff(.a(a), .b(b), .c(c));

\TLV

//Add \TLV here if desired

\SV

endmodule

- FOSSEE, IIT Bombay

- Steve Hoover, Founder, Redwood EDA

- Kunal Ghosh, Co-founder, VSD Corp. Pvt. Ltd. - kunalpghosh@gmail.com

- Sumanto Kar, eSim Team, FOSSEE

- http://iitb.ac.in/

- https://www.google.co.in/

- https://fossee.in/

- https://spoken-tutorial.org/

- https://www.vlsisystemdesign.com/

- https://www.c2s.gov.in/

- Website: https://www.circuitstoday.com/flip-flop-conversion

- Prabhu Deva Kumar, Seelam Vasavi Sai and Venkat, Pagadala and Nayini, Lokesh, Implementation and Designing of Low Power SR Flip-Flop Using 45NM CMOS Technology (August 30, 2017). http://dx.doi.org/10.2139/ssrn.3029181

- Github Format: https://github.com/Eyantra698Sumanto/Two-in-One-Low-power-XOR-XNOR-Gate.git