32-bit RISC Processor design using Harvard Architecture in Verilog. Harvard Architecture is a computer architecture with seperate memory and pathways for data and instructions, whereas in von-newmann architecture data and instructions share the same memory and pathways.

Instruction Set

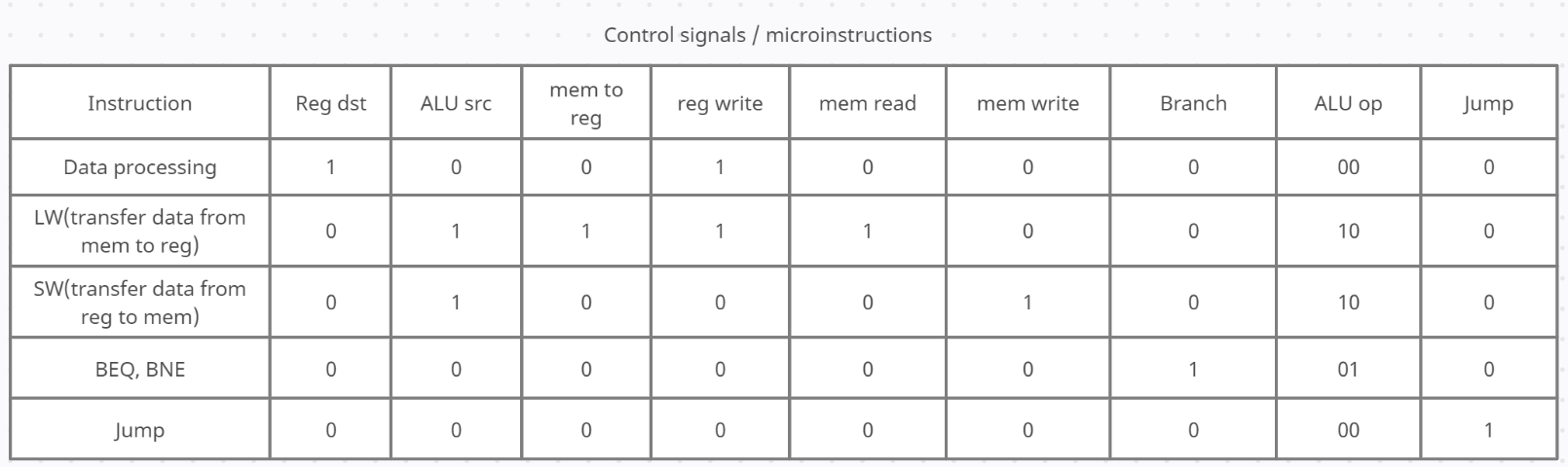

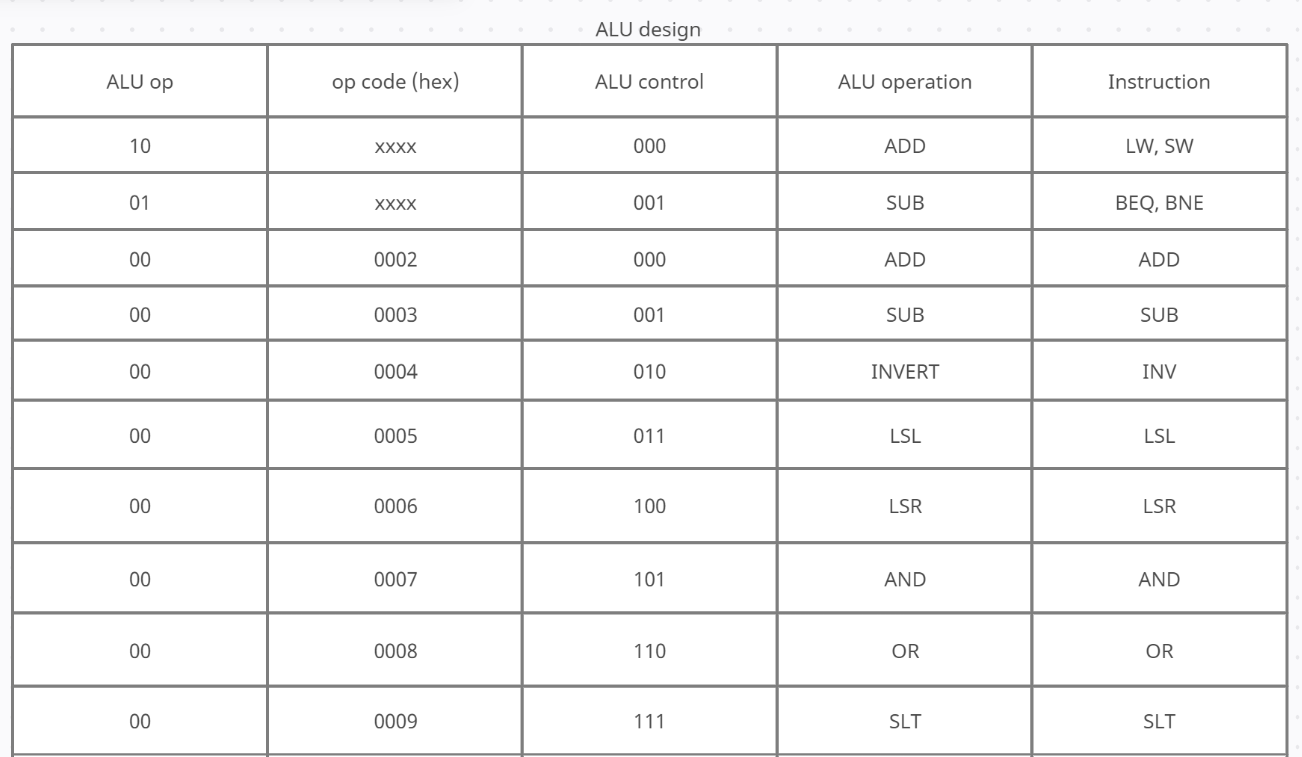

-Memory Access Instructions

- Load word-LW: LD ws, offset(rs1) - ws Mem32[rs1+rs2]

- Store word-SW: ST rs2, offset(rs1) Mem32[rs1+offset]=rs2

-Data Processing Insructions

- Add: ADD ws,rs1,rs2 - ws = rs1+rs2

- Subtract: SUB ws,rs1,rs2 - ws = rss1-rs2

- Invert: INV ws,rs1 - ws = !rs1

- Logical Shift Left: LSL ws,rs1,rs2 - ws = rs1<<rs2

- Logical Shift Right: LSR ws,rs1,rs2 - ws = rs1>>rs2

- Bitwise AND: AND ws,rs1,rs2 - ws = rs1&rs2

- Bitwise OR: OR ws,rs1,rs2 - ws = rs1|rs2

- Set on less than: SLT ws,rs1,rs2 - if rs1<rs2 then ws = 1 else ws = 0

-Control Flow Instructions

- Branch on equal: BEQ rs1,rs2,offset - branch to (pc+2+(offset<<1))when rs1=rs2

- Branch not equal: BNE rs1,rs2,offset - branch to (pc+2+(offset<<1))when rs1!=rs2

- Jump: JMP offset - Jump to {pc[30:26],(offset<<1)}