-

Notifications

You must be signed in to change notification settings - Fork 5

Home

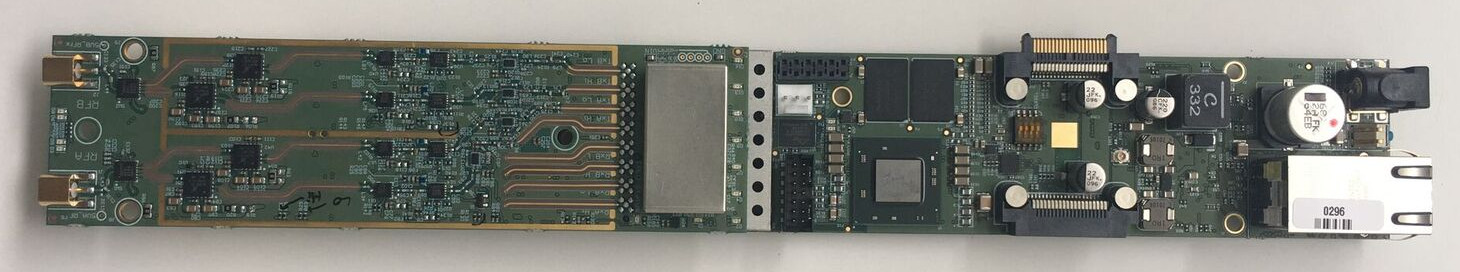

Skylark's Iris module is a network-based SDR device which is supported under the SoapySDR API. The Iris supports dual channel transmit and receive, high rate streaming, and device synchronization with timestamps and burst controls. Streaming rates are limited to to gigabit Ethernet when using the RJ45 connection, but can exceed gigabit rate with additional hardware platforms provided by Skylark.

Soapy Iris table of contents

SoapyIris can be installed from pre-built installers for several chosen platforms, or can be easily installed from source with the appropriate development environment.

TODO: This is a new repo and installers will be available in time. We plan to support installers for Ubuntu via myriadrf's drivers PPA, macosx via a homebrew recipe, and windows via PothosSDR installer.

SoapyIris depends on SoapySDR as a compile time dependency, and SoapyRemote as a runtime dependency for network device communication.

- Install SoapySDR: https://github.com/pothosware/SoapySDR/wiki

- Install SoapyRemote: https://github.com/pothosware/SoapyRemote/wiki

Or install SoapySDR packages on Ubuntu:

sudo add-apt-repository -y ppa:myriadrf/drivers sudo apt-get update sudo apt-get install libsoapysdr-dev soapysdr-module-remote

The CMake build system will locate SoapySDR development files on your system. The plugin module will be built and installed into the SoapySDR modules directories.

git clone https://github.com/skylarkwireless/sklk-soapyiris.git cd sklk-soapyiris mkdir build cd build cmake .. make sudo make install

The remote priority specifies the scheduling priority of the server forwarding threads. SoapyIris uses an elevated priority for the streaming threads to reduce latency and to avoid potential hiccups like overflows and underflows. Users may need to tweak their system configuration to allow elevated thread priority as a non-root user. The driver will print a warning if the thread priority setting is not possible.

To allow elevated priority on linux, edit /etc/security/limits.conf and add the following line for your username:

<username> hard rtprio 99

The SoapyIris repository provides a simple graphical application written in Qt and Python3 that provides a simple spectrum analyzer and signal generator SDR application for and Iris module.

- TODO (screenshot and instructions)

Find Iris modules on a local network with SoapySDRUtil:

#find all iris devices on the network SoapySDRUtil --find="driver=iris" #or a specific device specified by serial number #SoapySDRUtil --find="serial=XXXX" #or a specific device specified by IP address #SoapySDRUtil --find="remote=10.0.0.129" Found device 0 driver = iris label = IRIS-030B - XXXX remote = tcp://10.0.0.129:55132 remote:driver = iris-arm revision = Iris-030b serial = XXXX Found device 1 driver = iris label = IRIS-030B - YYYY remote = tcp://10.0.0.189:55132 remote:driver = iris-arm revision = Iris-030b serial = YYYY

Probe is a useful tool to query available hardware and version numbers from a device on the network:

SoapySDRUtil --probe="driver=iris"

######################################################

## Soapy SDR -- the SDR abstraction library

######################################################

Probe device driver=iris

[INFO] Initializing IRIS-030B - XXXX...

[INFO] LMS7002M rev 0x1, ver 0x7, mask 0x1

[INFO] Opening /etc/iris/calibration.sqlite3

[INFO] Initialization complete

----------------------------------------------------

-- Device identification

----------------------------------------------------

driver=iris

hardware=Iris-030b

driverVer=XXXX

fpgaVer=XXXX

frontend=DEV

lmsMask=0x1

lmsRev=0x1

lmsVer=0x7

revision=Iris-030b

serial=XXXX

----------------------------------------------------

-- Peripheral summary

----------------------------------------------------

Channels: 2 Rx, 2 Tx

Timestamps: YES

Sensors: ZYNQ_TEMP, CLKBUFF_LOCKED

Registers: IRIS30, RFCORE, IOMNGR, GTLINK, ETHFRM, RFEMOD

Other Settings:

* FPGA DIQ mode - in constant test mode, the normal TX path is bypassed,

and a constant level configured by FPGA_TSG_CONST is driven into TX DIQ.

When test mode is off, this value drives the input to the CORDIC when idle.

In loopback test mode, the transmit path is looped back into the receiver path.

[key=FPGA_DIQ_MODE, default=NORMAL, type=string, options=(NORMAL, CONST, LOOPB, PATTERN)]

* LML loopback - loopback transmit data from the BBIC,

which will go into the RX mux and into the receive path to BBIC.

[key=LML_LOOPBACK, default=false, type=bool]

* Generate trigger - Write this setting to generate a trigger.

[key=TRIGGER_GEN, type=string]

* Siggen power - Tell Iris the external signal generator power.

[key=SIGGEN_POWER, default=0.0, type=float]

* Eth0 IPv6 Address - IPv6 configuration for eth0.

[key=ETH0_IPv6_ADDR, type=string]

* RF TX FIFO Depth - The configured transmit fifo depth

[key=RF_TX_FIFO_DEPTH, default=0, type=int]

* UDP service port - UDP port for streaming services

[key=UDP_SERVICE_PORT, default=0, type=int]

----------------------------------------------------

-- RX Channel 0

----------------------------------------------------

Full-duplex: YES

Supports AGC: NO

Stream formats: CF32, CS16, CS12, CS8

Native format: CS12 [full-scale=2047]

Antennas: TRX, RX, LB1, LB2

Full gain range: [-12, 61] dB

LNA gain range: [0, 30] dB

TIA gain range: [0, 12] dB

PGA gain range: [-12, 19] dB

Full freq range: [20, 3810] MHz

RF freq range: [30, 3800] MHz

BB freq range: [-10, 10] MHz

Tune args:

* LO Offset - Tune the LO with an offset and compensate with the baseband CORDIC.

[key=OFFSET, units=Hz, default=0.0, type=float, range=[-1e+07, 1e+07]]

* BB - Specify a specific value for this component or IGNORE to skip tuning it.

[key=BB, units=Hz, default=DEFAULT, type=float, range=[-1e+07, 1e+07], options=(DEFAULT, IGNORE)]

Sample rates: 0.625, 1.25, 2.5, 5, 10 MSps

Filter bandwidths: [1, 60] MHz

Other Settings:

* TSP enable - call the TSP enable routine.

Call with true (enable) to reapply default settings.

[key=TSP_ENABLE, default=true, type=bool]

* BB enable - call the baseband enable routine.

Call with true (enable) to reapply default settings.

[key=BB_ENABLE, default=true, type=bool]

* RF enable - call the RF front-end enable routine.

Call with true (enable) to reapply default settings.

[key=RF_ENABLE, default=true, type=bool]

* LO enable - call the LO synthesizer enable routine.

Call with true before re-tuning the center frequency.

[key=LO_ENABLE, default=true, type=bool]

* siggen level - set the digital signal generator for a constant valued output.

[key=TSP_TSG_CONST, type=int, range=[0, 32768]]

* RBB path - set the RX baseband input path.

Use BYP, LBF, HBF for bypassing or filter path.

Use LB_BYP, LB_LBF, LB_HBF for loopback versions.

[key=RBB_SET_PATH, type=string, options=(BYP, LBF, HBF, LB_BYP, LB_LBF, LB_HBF)]

----------------------------------------------------

-- RX Channel 1

----------------------------------------------------

....

----------------------------------------------------

-- TX Channel 0

----------------------------------------------------

Full-duplex: YES

Supports AGC: NO

Stream formats: CF32, CS16, CS12, CS8

Native format: CS12 [full-scale=2047]

Stream args:

* Tx replay mode - Enable the transmit replay mode (default off).

Replay mode causes the last transmit burst to be replayed repeatedly.

[key=REPLAY, default=false, type=bool]

Antennas: TRX

Full gain range: [0, 52] dB

PAD gain range: [-52, 0] dB

Full freq range: [15, 3815] MHz

RF freq range: [30, 3800] MHz

BB freq range: [-40, 40] MHz

Tune args:

* LO Offset - Tune the LO with an offset and compensate with the baseband CORDIC.

[key=OFFSET, units=Hz, default=0.0, type=float, range=[-4e+07, 4e+07]]

* BB - Specify a specific value for this component or IGNORE to skip tuning it.

[key=BB, units=Hz, default=DEFAULT, type=float, range=[-4e+07, 4e+07], options=(DEFAULT, IGNORE)]

Sample rates: 2.5, 5, 10, 20, 40 MSps

Filter bandwidths: [0.8, 16], [28, 60] MHz

Other Settings:

* TSP enable - call the TSP enable routine.

Call with true (enable) to reapply default settings.

[key=TSP_ENABLE, default=true, type=bool]

* BB enable - call the baseband enable routine.

Call with true (enable) to reapply default settings.

[key=BB_ENABLE, default=true, type=bool]

* RF enable - call the RF front-end enable routine.

Call with true (enable) to reapply default settings.

[key=RF_ENABLE, default=true, type=bool]

* LO enable - call the LO synthesizer enable routine.

Call with true before re-tuning the center frequency.

[key=LO_ENABLE, default=true, type=bool]

* siggen level - set the digital signal generator for a constant valued output.

[key=TSP_TSG_CONST, type=int, range=[0, 32768]]

* TBB loopback - enable TX baseband loopback.

[key=TBB_ENABLE_LOOPBACK, type=string, options=(LB_DISCONNECTED, LB_DAC_CURRENT, LB_LB_LADDER, LB_MAIN_TBB)]

* FPGA Tx siggen level - set the FPGA's TX digital signal generator

for a constant valued output. When FPGA_TX_TEST is 'false',

this value drives the TX FPGA CORDIC when no user stream is applied.

When FPGA_TX_TEST is 'true', this value directly drives the TX DIQ bus.

[key=FPGA_TSG_CONST, type=int, range=[0, 32768]]

* Tx enable override - Force the RF module to be held in transmit mode.

This is useful for generating dummy signals in the PL or LMS7,

while the DAC active signal is being otherwise ignored by logic.

[key=TX_ENB_OVERRIDE, default=false, type=bool]

----------------------------------------------------

-- TX Channel 1

----------------------------------------------------

....

[INFO] Power down and cleanup