New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

Have frequency (and hsync/vsync) information on the inputs in the status message #94

Comments

|

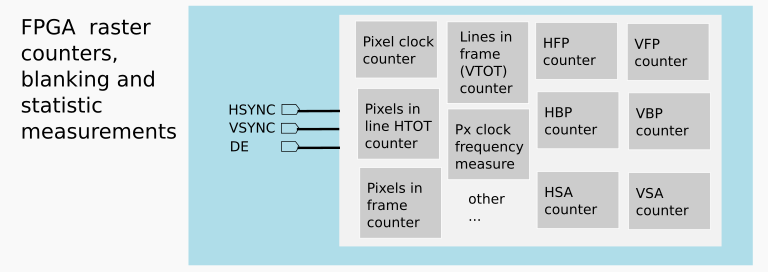

This will probably require modification of both the gateware on the fpga and the firmware running on the lm32 softcore. You'll need to look at code in https://github.com/timvideos/HDMI2USB-misoc-firmware/blob/master/hdl/hdmi_in/analysis.py |

|

@cr1901 - please take a look at this. |

|

Also take a look at https://warmcat.com/hardware%20design/hdmi/fpga/2015/10/21/hdmi-capture-and-analysis-fpga-project-3.html - specially the "Raster measurement and statistics collection" section. This is the data the HDMICap project captures; {

"pll_locked":"1",

"syncs_detected":"1",

"sanity":"1",

"pxclk_MHz":"74.255587",

"ctrl_ch0_pc":"37067.5",

"ctrl_ch1_pc":"9755.0",

"ctrl_ch2_pc":"9755.4",

"dvi":"0",

"hpol":"+",

"vpol":"+",

"hact":"1280",

"vact":"720",

"hrate_kHz":"55.214",

"vrate_Hz":"73.619",

"htot":"1980",

"hbl":"700",

"hsa":"40",

"hfp":"440",

"hbp":"220",

"vtot":"750",

"vbl":"30",

"vsa":"5",

"vfp":"5",

"vbp":"20",

"px_in_frame":"1485000",

"htot_in_frame":"750.000",

"integer_htot_in_frame":"1",

"line_timestamp":"457",

"frame_timestamp":"17577",

"data_px_active":"416045",

"data_px_active_line":"577.840",

"data_vb":"23281",

"ctrl_px_active":"85640",

"ctrl_px_active_line":"118.944",

"ctrl_vb":"33977",

"est_video_clocks":"924617",

"actual_video_clocks":"921600",

"terc4_errs_frame":"766",

"vsync_onset_hpx":"0"

}There might be stuff you can crib from https://git.linaro.org/people/andy.green/hdmicap-vhdl.git/blob/HEAD:/hdmicap_v1_0_S00_AXI.vhd |

* edid-decode changed from b2da151 to 5eeb151

* 5eeb151 - edid-decode: replace AdobeYCC/RGB by opYCC/RGB <Hans Verkuil>

* litedram changed from 7a5ac75 to ea1ac4d

* ea1ac4d - s6ddrphy: Pass missing nranks parameter. <Tim 'mithro' Ansell>

* e5696ad - frontend/ecc: add enable csr <Florent Kermarrec>

* e6ef89a - frontend/axi: optimize burst2beat timings <Florent Kermarrec>

* 6941285 - frontend/ecc: split Write/Read path and add buffer to improve timings <Florent Kermarrec>

* 041817d - frontend/ecc: use csr instead of signal for control <Florent Kermarrec>

* b145b0c - frontend/axi: fix write response implementation <Florent Kermarrec>

* d23dbf6 - phy: add nranks to all phys <Florent Kermarrec>

* 461b076 - frontend/ecc: add ecc adapter <Florent Kermarrec>

* c84b587 - frontend: add initial ecc code (still need to be integrated) <Florent Kermarrec>

* a8d2672 - phy/s7ddrphy_halfrate_bl8: don't generate dqs pre/post-amble, needs simulation <Florent Kermarrec>

* 5719d71 - phy/s7ddrphy_halfrate_bl8: fix cs_n <Florent Kermarrec>

* 36fa324 - core/multiplexer: fix regression (introduced by multirank support) <Florent Kermarrec>

* 42d0e5b - core/multiplexer: add more information on odt fixme <Florent Kermarrec>

* 919b756 - phy/model: pass nranks to Interface <Florent Kermarrec>

* f5c7b61 - multirank: set default nranks to 1 if not specified <Florent Kermarrec>

* f3d403f - s7ddrphy: fix typo (reset_n --> cs_n) <Florent Kermarrec>

* 37f1dec - multirank: one cs_n/cke/odt/clk per rank <Florent Kermarrec>

* 3e17d18 - phy: add halfrate_bl8 variant for s7ddrphy <Florent Kermarrec>

* 412e9a5 - Merge pull request #38 from enjoy-digital/multirank <enjoy-digital>

|\

| * 8ddc6c7 - drive odt of all ranks, fixes and test non regression with 1 rank <Florent Kermarrec>

| * d4f434d - dfii: send command to all ranks <Florent Kermarrec>

| * b1c2739 - initial multirank support (nbankmachines = nranks * (2**bankbits)) <Florent Kermarrec>

* | d9c2430 - Merge pull request #36 from JohnSully/timing_1 <enjoy-digital>

|\ \

| |/

|/|

| * efd7a47 - Fix failing timing <>

* | cc481be - examples: add sdram_rank_nb and user_ports_id_width <Florent Kermarrec>

|/

* 849b1f6 - frontend/axi: generate rlast signal <Florent Kermarrec>

* 1fa73e4 - test: update <Florent Kermarrec>

* 7b61b68 - sdram_init: min value for wr is 5 <Florent Kermarrec>

* 1652ab9 - examples/litedram_gen: fix address width of axi ports (addressing in bytes not words) <Florent Kermarrec>

* 1e64b7f - examples/litedram_gen: expose resp signals to user <Florent Kermarrec>

* 700f76c - frontend/axi: add resp signals <Florent Kermarrec>

* 47fed1b - frontend/axi: add last limitation <Florent Kermarrec>

* de69867 - examples/litedram_gen: expose last signals to user <Florent Kermarrec>

* e8bd782 - examples/litedram_gen: expose burst signals to user <Florent Kermarrec>

* e1598ce - phy/s7ddrphy: fix BL8 assert <Florent Kermarrec>

* ebba39d - README: update <Florent Kermarrec>

* e528e92 - phy/s7ddrphy: add assertion to avoid generating 1:2 controller with DDR3 (needs BL8 support in the PHY) <Florent Kermarrec>

* 6017e7a - phy/s7ddrphy: fix dqs_sys_latency for DDR2 <Florent Kermarrec>

* 7b42739 - phy/s7ddrphy: simplify cmd/dat phases computation and remove restrictions. <Florent Kermarrec>

* 6148618 - phy/s7ddrphy: use dict in get_cl_cw function <Florent Kermarrec>

* 5e4dca9 - add examples with standalone cores for arty and genesys2 <Florent Kermarrec>

* dce4ede - README: update <Florent Kermarrec>

* f6797a1 - test/test_axi: add burst wrap test and fix code <Florent Kermarrec>

* 47988d8 - frontend/axi: remove alignment limitation since we are in fact supporting unaligned transfers as described in the specification. <Florent Kermarrec>

* 6cc42c6 - frontend/axi: add wrap burst support <Florent Kermarrec>

* 9c729ae - core: replace adr with addr on native interface (closer to AXI and allow some simplifications) <Florent Kermarrec>

* 0506708 - core/controller: remove simulation workaround <Florent Kermarrec>

* bc8a9ce - README: update <Florent Kermarrec>

* 6f7ae84 - frontend/axi: increase default depth of buffers to improve performance <Florent Kermarrec>

* ed7eef1 - phy/s7ddrphy: fix preamble/posamble latency when with_odelay (-1 since dqs clk is not shifted) <Florent Kermarrec>

* c37d3af - frontend/bist: only keep random datas (we can generate random addresses with control) <Florent Kermarrec>

* b1e734b - frontend/bist: only use cdc on registers if needed (ie not in sys clock domain) <Florent Kermarrec>

* 92c8513 - frontend/axi: add buffer to accept command before converting burst to beats <Florent Kermarrec>

* c15c474 - test/test_axi: split reads/writes generators <Florent Kermarrec>

* 95cb7cd - test: rename read/write generators to handlers <Florent Kermarrec>

* d5d6737 - frontend/axi: fix read id <Florent Kermarrec>

* 10229d1 - test/test_axi: improve test_axi2native <Florent Kermarrec>

* 295f016 - frontend/axi: add features/limitations <Florent Kermarrec>

* 6a46ea3 - test/test_bist: add generator test, remove async test <Florent Kermarrec>

* 7677a85 - core/bankmachine: expose cmd_buffer_buffered param and small cleanup <Florent Kermarrec>

* liteeth changed from 24b0d2b to 3d86844

* 3d86844 - core/mac/sram: fix code refactoring <Florent Kermarrec>

* 5106bcd - core/mac/sram: simplify last_be code <Florent Kermarrec>

* ce72e34 - core/mac: pass endianness and use if for last_be gen/check <Florent Kermarrec>

* 94af3d6 - README: update and rename example_designs to examples <Florent Kermarrec>

* litepcie changed from a97a691 to 3e8de2d

* 3e8de2d - phy/s7pciephy: remove clock constraints from phy <Florent Kermarrec>

* 6f2d97a - README: update and rename example_designs to example <Florent Kermarrec>

* litesata changed from 002cd25 to fb72044

* fb72044 - README: update and rename example_designs to examples <Florent Kermarrec>

* litescope changed from f26e36e to 686db4f

* 686db4f - Merge pull request #12 from xobs/default-length <enjoy-digital>

|\

| * 4f8b9a3 - analyzer-driver: use default depth from config <Sean Cross>

|/

* 7c1c62e - README: update and rename example_designs to examples <Florent Kermarrec>

* 3567b68 - dump/vcd: fix code generation <Florent Kermarrec>

* 182b683 - core: change cd parameter to clock_domain (keep retro compatibility for now) <Florent Kermarrec>

* liteusb changed from e841c56 to 0a9110f

* 0a9110f - README: update and rename example_designs to examples <Florent Kermarrec>

* litevideo changed from 7b4240f to 13d85a1

* 13d85a1 - README: update <Florent Kermarrec>

* litex changed from 7a14b75c to 537b0e90

* 537b0e90 - Merge pull request #101 from cr1901/icestorm-migen-pull <enjoy-digital>

|\

| * 5c83c881 - Pull in b2740d9 from Migen. nextpnr now default, write out build scripts on dry run. <William D. Jones>

* | 9c6f76f1 - bios/sdram: mode sdhw() <Florent Kermarrec>

* | a44bedd5 - bios/sdram: add missing #ifdef <Florent Kermarrec>

* | 0e68daeb - targets: self.pll_sys --> pll_sys <Florent Kermarrec>

* | 1468b9f3 - bios/sdram: show all read scans when failing. <Florent Kermarrec>

* | 07e4c183 - cpu/lm32: re-enable multiplier/divider in minimal variant (does not seem to work correctly on hardware otherwise) <Florent Kermarrec>

* | df3f003e - soc_sdram: update with litedram <Florent Kermarrec>

|/

* bebc667d - Merge pull request #99 from cr1901/mk-copy-main-ram <enjoy-digital>

|\

| * bd70ba27 - Add COPY_TO_MAIN_RAM generated Makefile variable to distinguish systems with/without main_ram region. <William D. Jones>

* | 69716852 - Merge pull request #100 from cr1901/tinyprog-fix <enjoy-digital>

|\ \

| * | c812321a - lattice/programmer: Use --program-image option with tinyprog if address is given. <William D. Jones>

| |/

* | 12a89447 - soc_sdram: revert vivado l2 cache workaround (still seems to cause issues on some cases...) <Florent Kermarrec>

* | 2b786065 - targets: pass endianness to LiteEThMAC, tftp working with RISC-V, still need to fix txlen <Florent Kermarrec>

* | 26963d62 - libnet/microudp: (WIP) fix endianness issues <Jean-François Nguyen>

* | d9d0320d - Merge pull request #98 from jfng/fix_typo <enjoy-digital>

|\ \

| * | 22c01313 - fix typo and unused include <Jean-François Nguyen>

|/ /

* | fb24ac0e - cpu/minerva: add workaround on import until code is released <Florent Kermarrec>

* | 9cfae4df - setup.py: create litex_sim exec to ease simulation <Florent Kermarrec>

* | 8f377307 - add Minerva support <Jean-François Nguyen>

* | 1944289e - litex_server: update pcie and remove bar_size parameter <Florent Kermarrec>

|/

* c5a2d6f3 - Merge pull request #96 from cr1901/tinyfpga_bx <Tim Ansell>

|\

| * 29492624 - build/platforms: Add TinyFPGA BX board and programmer. <William D. Jones>

* | 3cb754da - Merge pull request #95 from cr1901/lm32-lite <Tim Ansell>

|\ \

| * | ed507d61 - Add lm32 "lite" variant, remove mult/div from "minimal" and update compiler flags accordingly. <William D. Jones>

| |/

* | 28cd2da2 - README: update <Florent Kermarrec>

|/

* 05c7b9da - Merge pull request #94 from cr1901/nextpnr <enjoy-digital>

* 7af89efc - lattice/icestorm: Add nextpnr pnr as alternate pnr tool. <William D. Jones>

* migen changed from 0.6.dev-162-ga6082d5 to 0.6.dev-168-gca0df1c

* ca0df1c - build.platforms: add ice40_up5k_b_evn platform. <whitequark>

* b2740d9 - build.lattice.icestorm: write build script even on dry run. <whitequark>

* 2a7e33e - Emit `default_nettype none. <David Craven>

* cff127d - build/platforms: Add TinyFPGA BX board and programmer. <William D. Jones>

* 97e2651 - kasli: set USERID and USR_ACCESS <Robert Jördens>

* 58894fb - lattice/icestorm: Add nextpnr as alternate pnr tool. (#124) <William D. Jones>

Full submodule status

--

5eeb151a748788666534d6ea3da07f90400d24c2 edid-decode (remotes/origin/HEAD)

a628956da7dc794e6e3c95b31ff9ce3af58bc763 flash_proxies (remotes/origin/HEAD)

ea1ac4d6d72ecb9a65fb884857db8ba6851f3230 litedram (heads/s6-rank-fix)

3d868449e9c38a00524cff8ed2bf5dec2fc0d858 liteeth (remotes/origin/HEAD)

3e8de2d1ef347a1fdfbd01601b1bbdc4558dd90a litepcie (remotes/origin/HEAD)

fb72044dabd121b4643a936b21ca3bf3aed75499 litesata (remotes/origin/HEAD)

686db4f3cd71bade8dd777d112e66797662f5bad litescope (remotes/origin/HEAD)

0a9110f901182a1233cc4e64b6e39175f6784621 liteusb (remotes/origin/HEAD)

13d85a1fe360678bebd57c55f1b35988c655ae95 litevideo (remotes/origin/HEAD)

537b0e9058e6a5b77f434f46f3a56849c82064bd litex (remotes/origin/HEAD)

ca0df1c148950213ff0551a8ec7c188a5910906e migen (0.6.dev-168-gca0df1c)

* litedram changed from 401554f to 08325dd

* 08325dd - Merge pull request #94 from mithro/lpddr-fix <Tim Ansell>

* 746329c - Fix broken lpddr support. <Tim 'mithro' Ansell>

* litex changed from v0.1-1333-ga54b80b9 to v0.1-1335-gbb64f8a7

* bb64f8a7 - Merge pull request #293 from mithro/mor1kx-fix <Tim Ansell>

* 607e1cc4 - Fix file names for the mor1kx processor. <Tim 'mithro' Ansell>

Full submodule status

--

3a6108a75be356a3dc53760d22782f1323248b6b edid-decode (remotes/origin/HEAD)

01d8f819f15baf9a8cc5d96945a51e4d267ff564 flash_proxies (remotes/origin/HEAD)

08325dd04e65859d3410e730dde7ab81d338d6c3 litedram (remotes/origin/HEAD)

4d9e74f10a3fe7bf71ba9bde50f49689c6458dc5 liteeth (remotes/origin/HEAD)

47e76f447f6e3d97aac2638a98f967d44db5c349 litepcie (remotes/origin/HEAD)

db5d2f7881161ce5b9a10a0ab42555f884b9d7c1 litesata (remotes/origin/HEAD)

7a9fa9d3b18362bf707dff25a78661395ef9ee7a litescope (remotes/origin/HEAD)

7457a29b1a47fe15e81fa37f3bbdd510788f1d53 liteusb (remotes/origin/HEAD)

49bafa481075e0bfbaf067b63c351ec29e993894 litevideo (remotes/origin/HEAD)

bb64f8a74daeab1772ea30323f26fe0447d5f2ea litex (v0.1-1335-gbb64f8a7)

742360f2ba4c400c6164908f03c6ca3d965f168b litex-renode (remotes/origin/HEAD)

41922fde2a8c36cd0f99d4b7ebb3ba9c37ce1489 migen (0.6.dev-306-g41922fd)

Change the following

to

The text was updated successfully, but these errors were encountered: