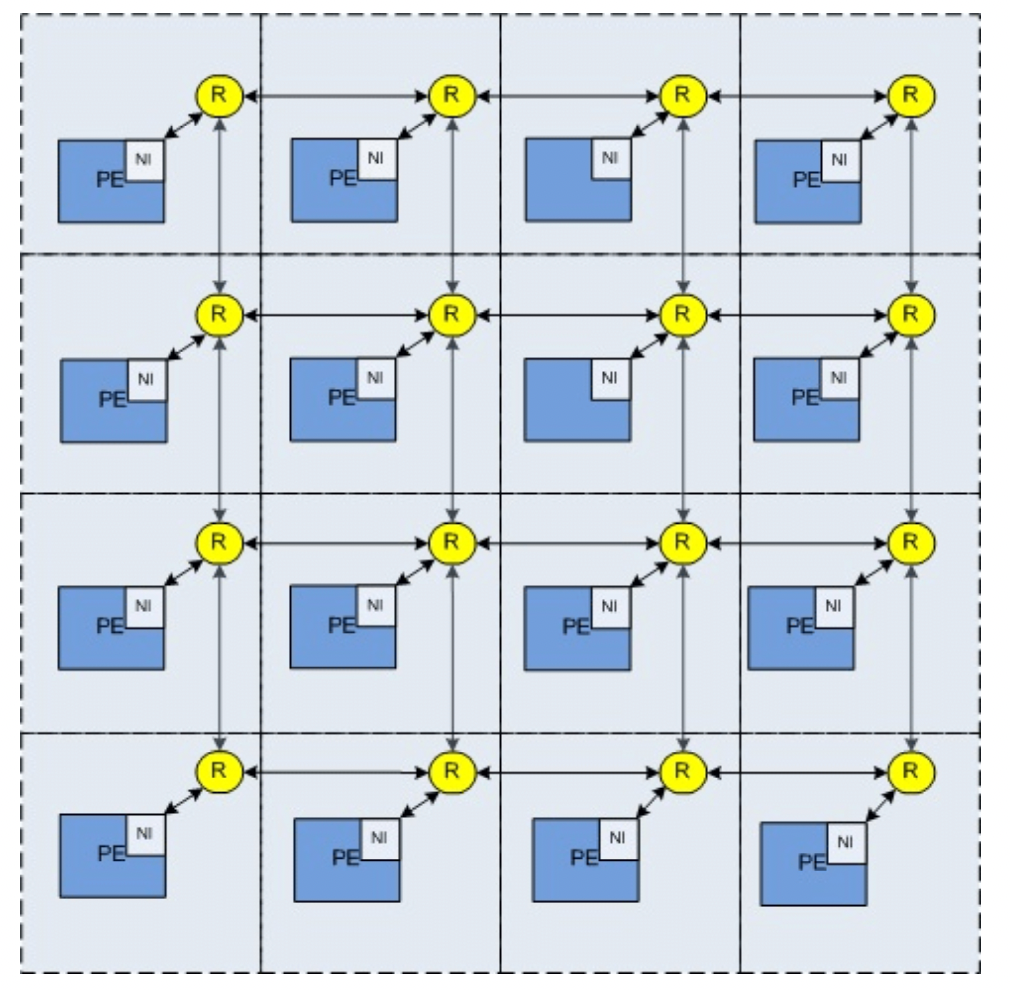

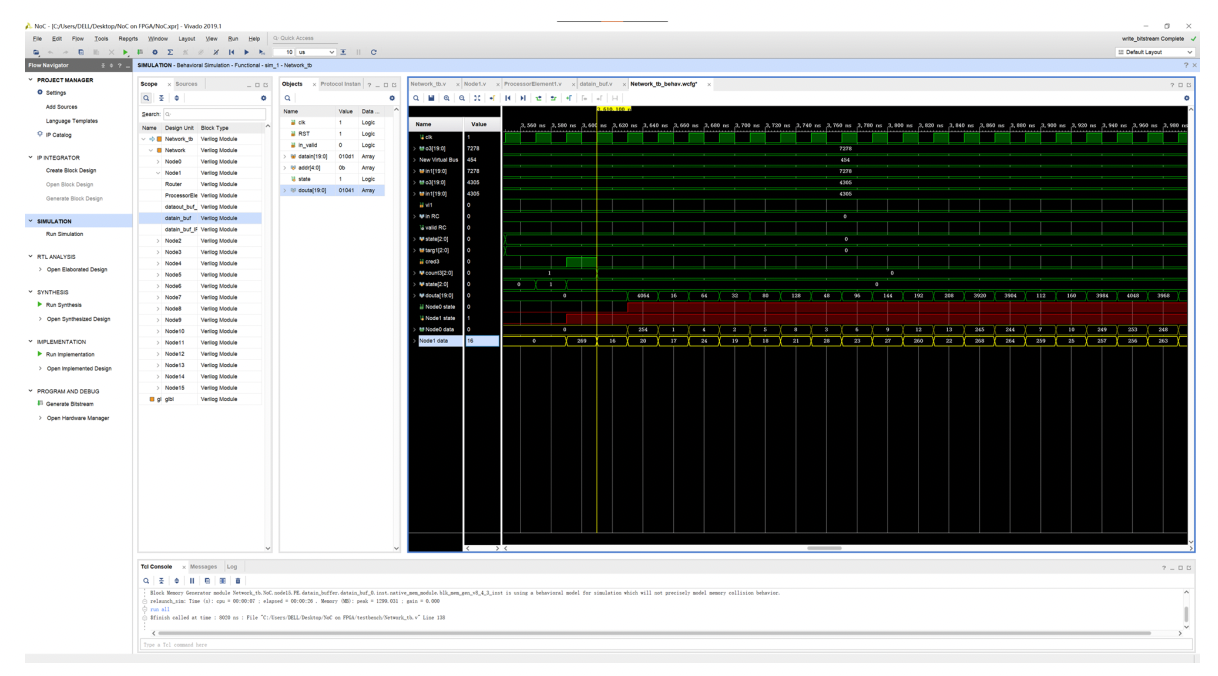

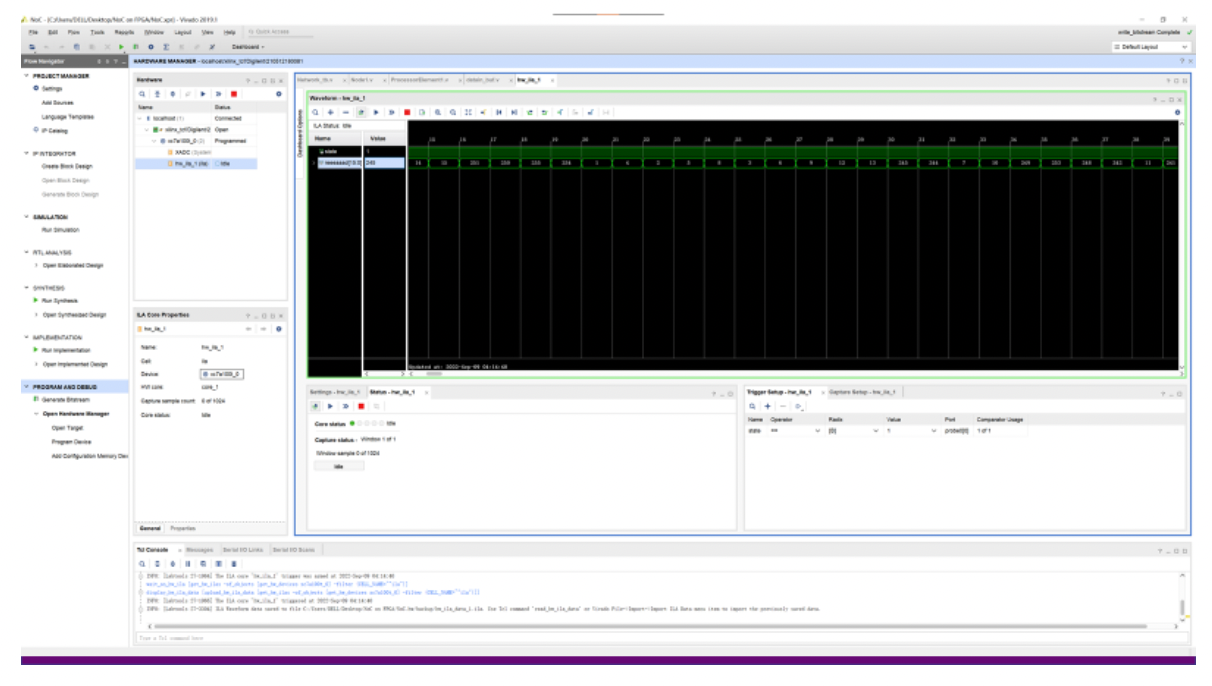

A 2D mesh Network on Chip with 5-stage pipelined router, all implemented in Verilog and run on Artix-7 FPGA with 150MHz frequency.

PE: send data and receive data to and from other PEs. Date stored in BRAM.

Ni: network interface

R: router

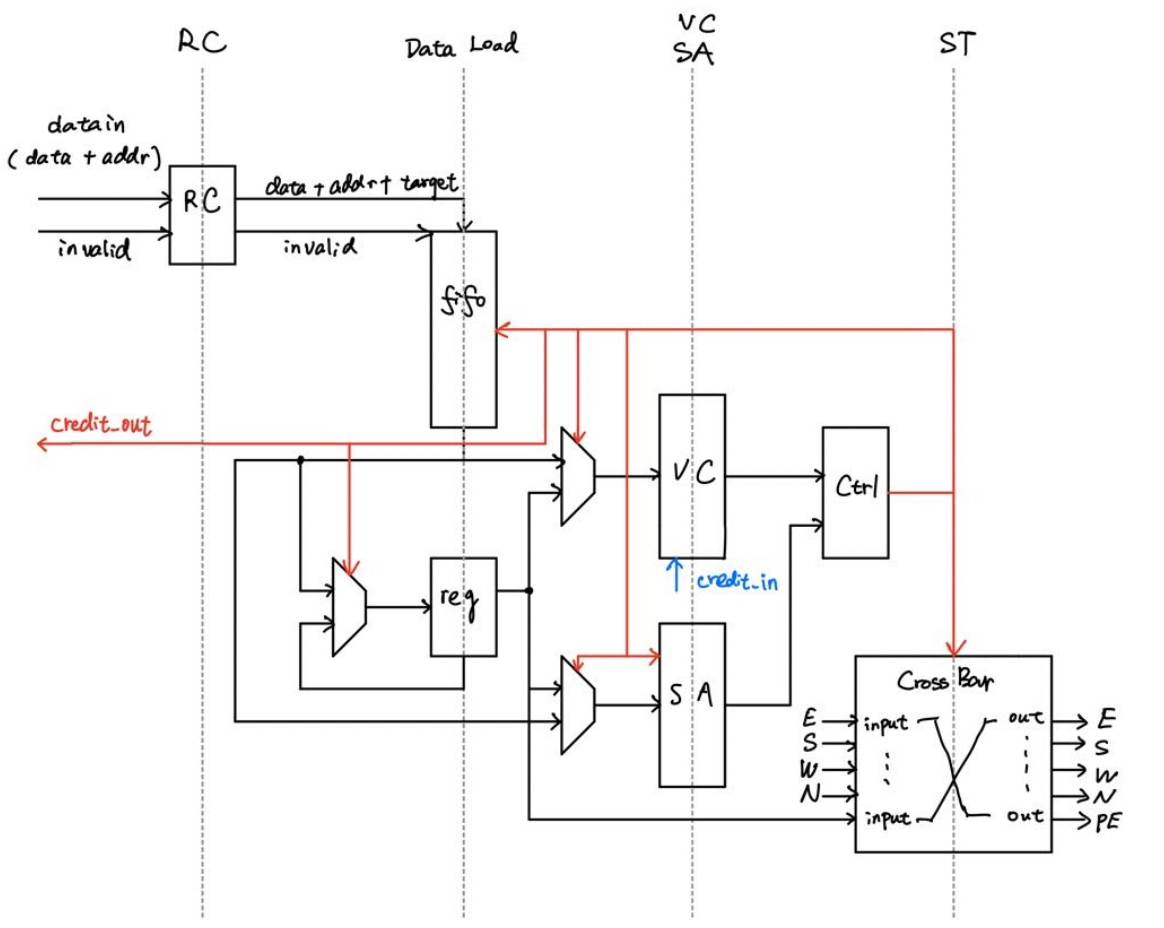

5 pipelined stage:

- route computation

- data transformation and store in fifo

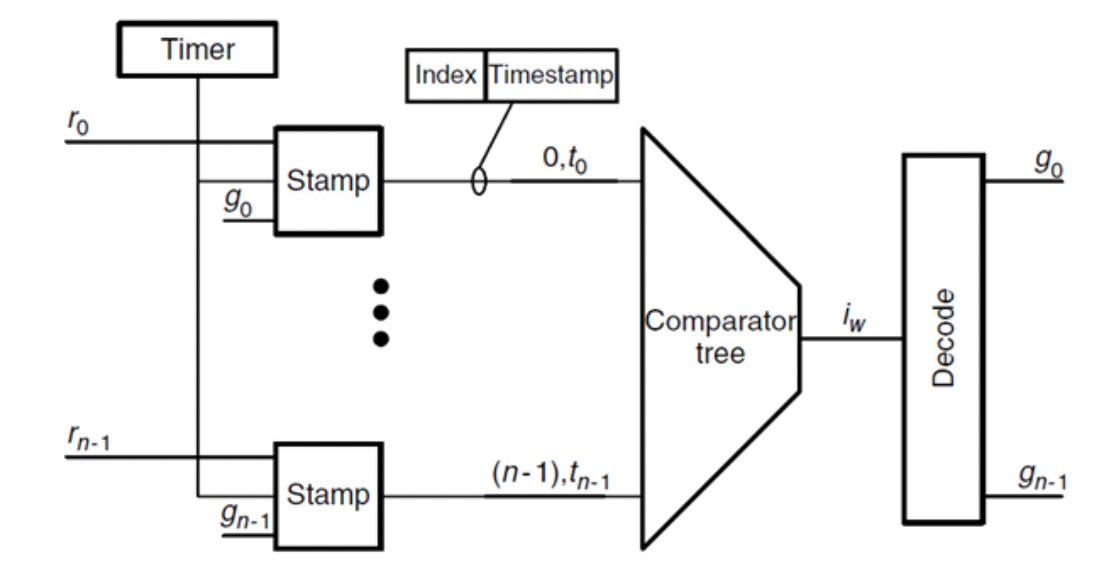

- VC Allocation and Switch Allocation

- Switch Traversal

- Link Traversal

Route computing algorithm: negative-first algorithm (dead-lock free)

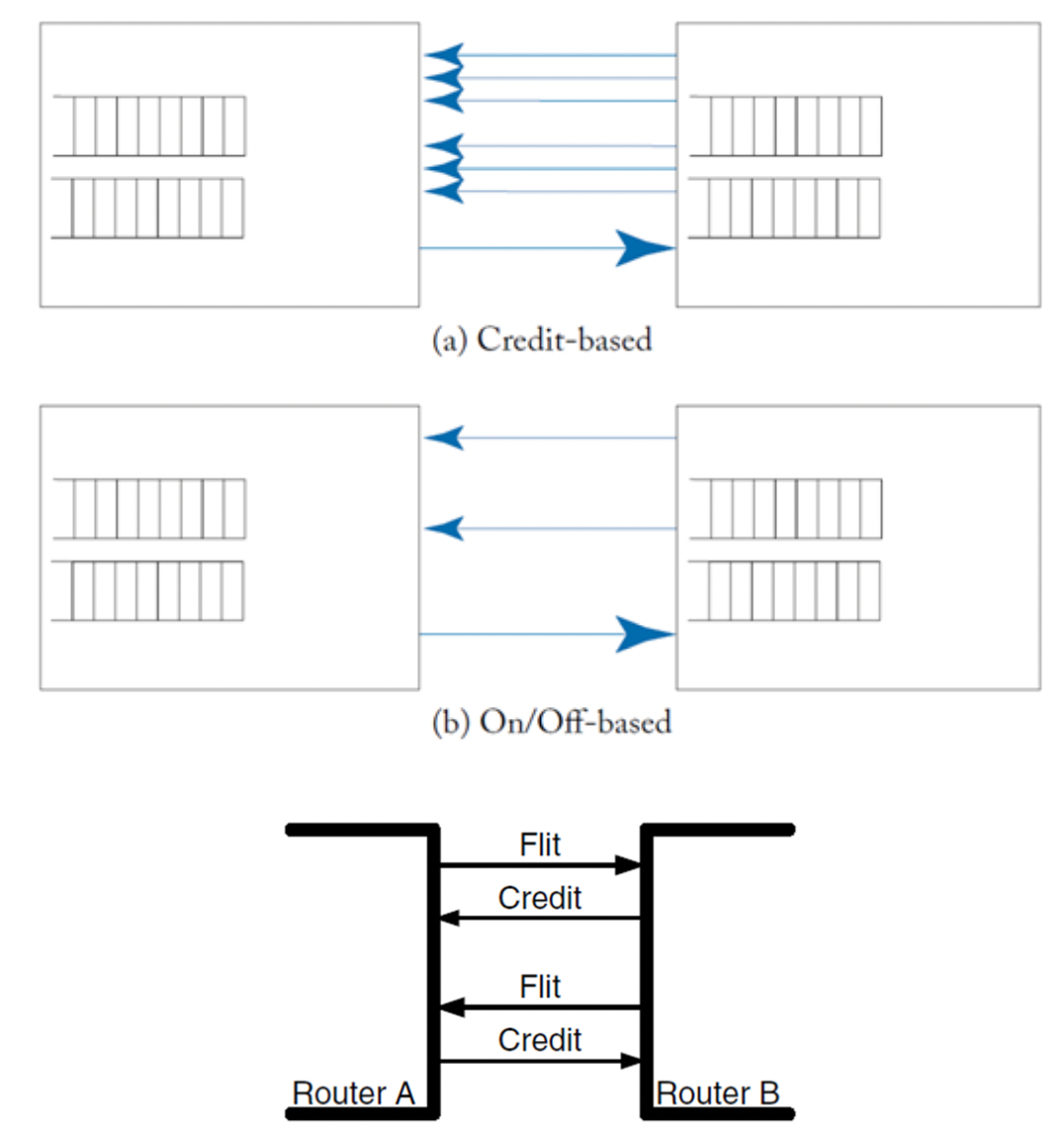

VC: credit-based control

switch channel allocation: Round-Robin and Queuing arbiter

- transport 48*30 flits in 180 cycle, transmission density is 6.7 hops/cycle

- pll frequency: 150MHz

-

High scalability and well seperate modules for testing more policies.

-

Can be applyed to multi-core computing for AI accelarating like matrix convolution, matrix multiplication used in neural networks.