New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

Support for "don't care" bit in comb processes #765

Comments

That's not true. These are the log messages from where it optimizes those X bits:

No. It just happens to produce a circuit with similar behavior. It's not realistic to expect the tool to always find the optimal LUT implementation for a circuit. Btw, I just ran your |

I think this specific case can still be improved. At least I don't see any reason why. This seems like something the SAT based sharing pass could find, no? |

Steps to reproduce the issue

Expected behavior

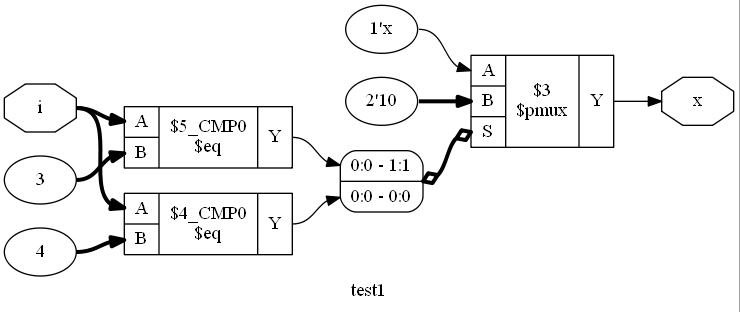

This should generate only 1 LUT4 for o[3] and a pass-through for o[2:0].

Actual behavior

This actually generates 4 LUT4 and completely ignores the "don't care" bit I'm trying to convey and treating them as 0 AFAICT.

The text was updated successfully, but these errors were encountered: