Home

Joe Britton edited this page Oct 30, 2023

·

18 revisions

Design files (schematics, PCB layouts, BOMs) can be found at Kasli-SOC/releases.

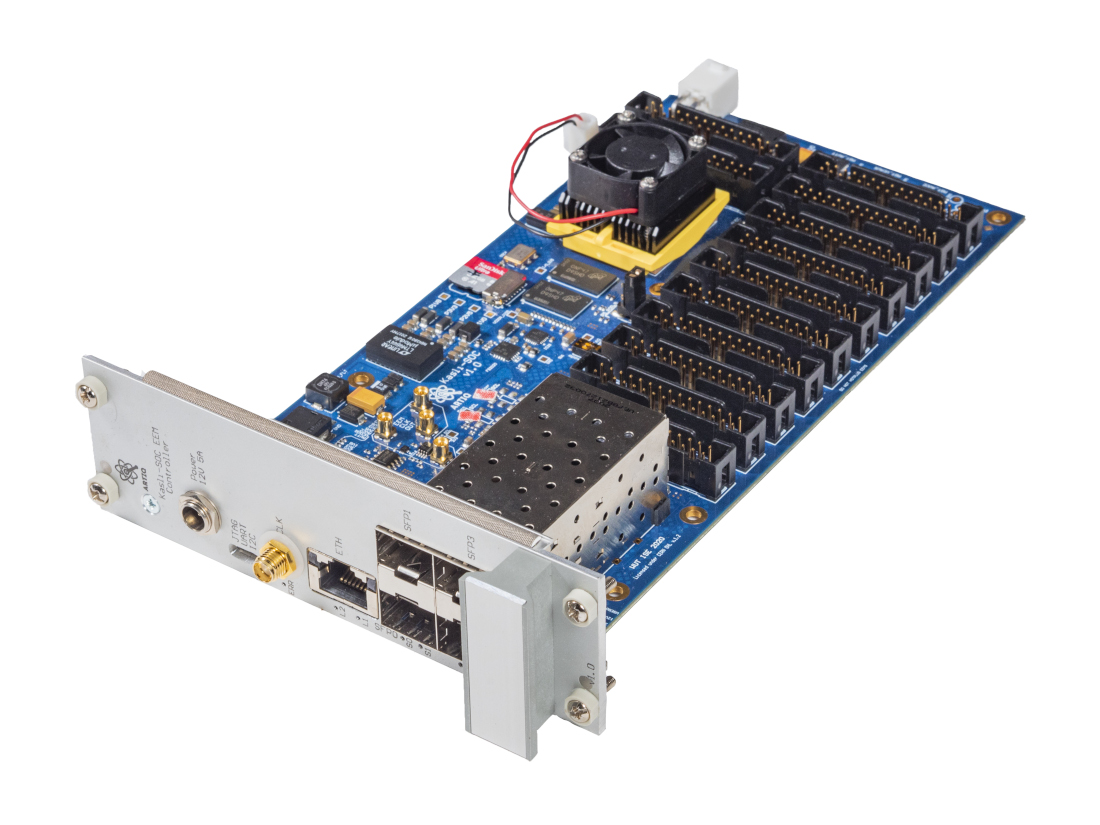

Kasli-SOC is an ARTIQ core device for EEM peripherals. It provides a superset of the features of Kasli v2 with the following notable differences. Board features:

- FPGA is a Xilinx XC7Z030 SoC

- RJ45 10/100/1000T Ethernet -- this is the default network interface for master (Kasli defaults to SFP0)

- USB 2.0 connector (PS UART, PL UART, JTAG)

- FLASH memory is located on a removable micro-SD card

- Two DIP switches toggle between booting from FLASH vs JTAG over USB

- Two jumpers

- PS_POR_B must be set for POR reset via the FTDI USB-JTAG chip

- PS_SRST_B -- unknown function

| Kasli v2 | Kasli-SOC | |

|---|---|---|

| Chipset | XC7A100T | Zynq XC7Z030 |

| 7 Series PL Equivalent | Atrix 7 | Kintex 7 |

| Logic Cells | 101,440 | 125,000 |

| total block ram | 4.86 Mb | 9.3Mb |

| DSP slices | 240 | 400 |

| uP | 0 | 2 (*) |

(*) Kasli-SOC has two hard-core microprocessors: ARM Cortex-A9 MPCore up to 1 GHz with NEON SIMD Engine and single+double FPU.

- ARTIQ support for this board is excellent as of 10/2023. Note that ARTIQ support is not yet merged for this board.

- Note that the ARTIQ support does not support LED LD2 (link)(link).

- Note that ARTIQ does not support Ethernet over SFP.