-

Notifications

You must be signed in to change notification settings - Fork 0

AMBA

jjin-choi edited this page Jul 16, 2020

·

3 revisions

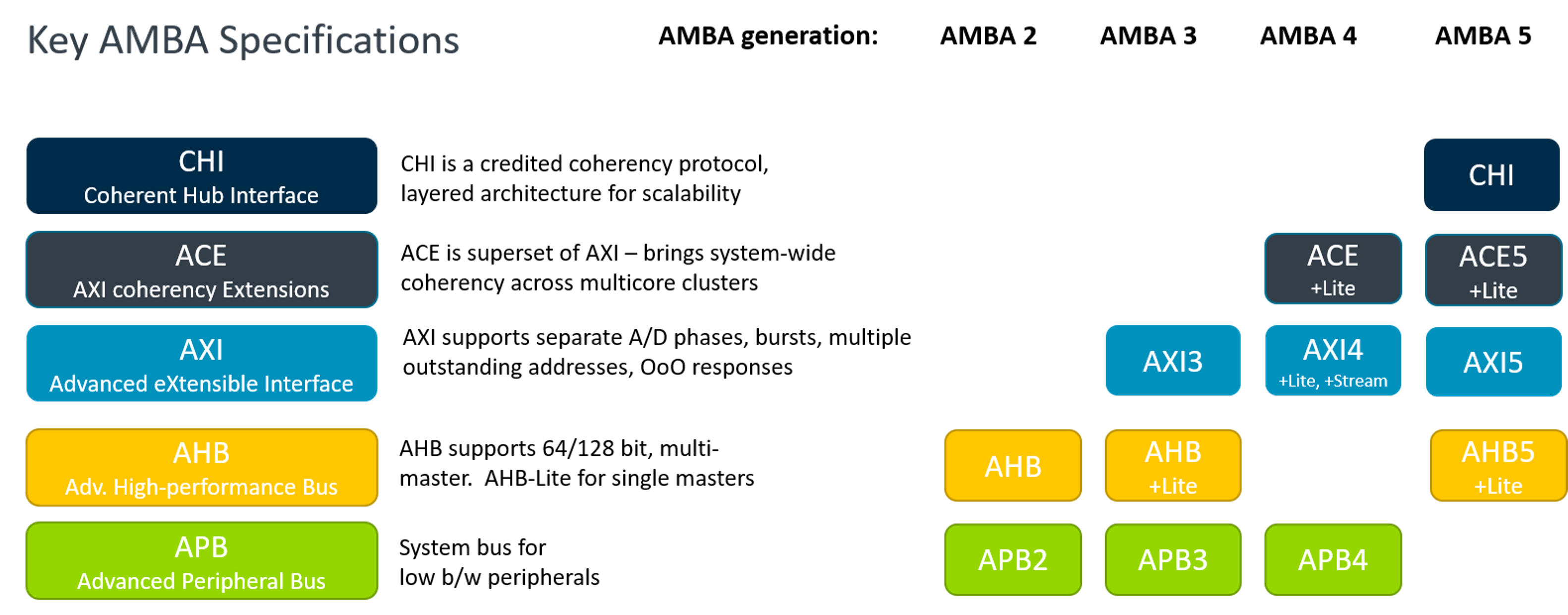

Link: AMBA-Overview-Diagram

- AHB :

- AXI : 다중 채널 버스, 읽기/쓰기에 최적화. AHB와 가장 다른 점은 채널의 도입

-

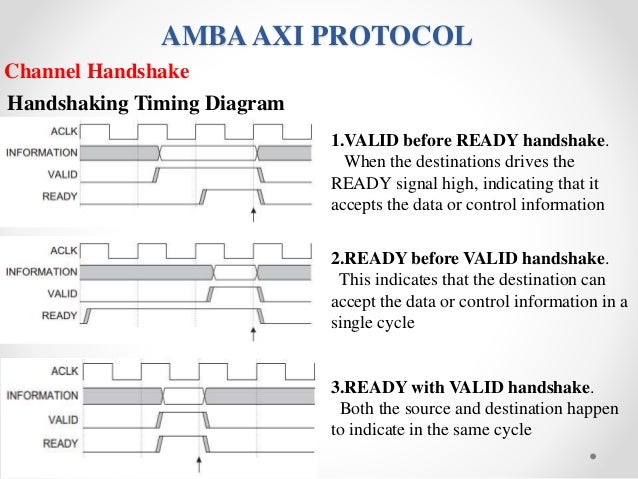

독립적인 5개의 channel 들은 VALID 와 READY 신호의 set 으로 구성된다.

- two way handshake mechanism

- VALID ? 그 channel 에서 유효한 주소, 데이터나 제어 신호가 사용 가능할 때

- READY ? destination 이 정보를 accept 할 수 있을 때 READY 신호를 사용한다.

- LAST ? read data channel 과 write data channel 은 둘다 LAST 신호를 포함하는데, 이는 transaction 의 마지막 data 의 transfer을 가리킨다.

- BRESP ? transaction 이 정상적으로 완료 되었다.

-

READ / WRITE address channels

- READ / WRITE transaction 은 각자 address channel 을 가지고 있고, 그 channel 이 transaction 에 필요한 address, control 정보를 가지고 있음.

-

READ / WRITE data channels

- READ data channel

- read data / read response info from slave to master 를 모두 가지고 있음.

- read transaction 상태에 대한 response

- WRITE data channel

- write data info from master to slave

- read transaction 상태에 대한 response

- READ data channel

-

WRITE response channel

- slave 가 WRTIE reponse 를 보내는데 사용. transaction 이 모두 끝날때만 사용.

Link: AXI-READ-channels

Link: AXI-WRITE-channels

- VALID / READY : address, data, and control 에 대한 정보를 transfer 하는 과정에서의 handshake process

- VALID ? source 가 만드는 신호. address, data, and control 정보가 available 할 때를 가리킨다.

- READY ? destination 이 만드는 신호. information 을 accept 할 수 있다는 것을 의미

- VALID & READY 가 모두 HIGH 일 때 transfer 이 일어난다.

Link: VALID-READY handshake