-

Notifications

You must be signed in to change notification settings - Fork 0

Home

資料來源:RISC-V 手册

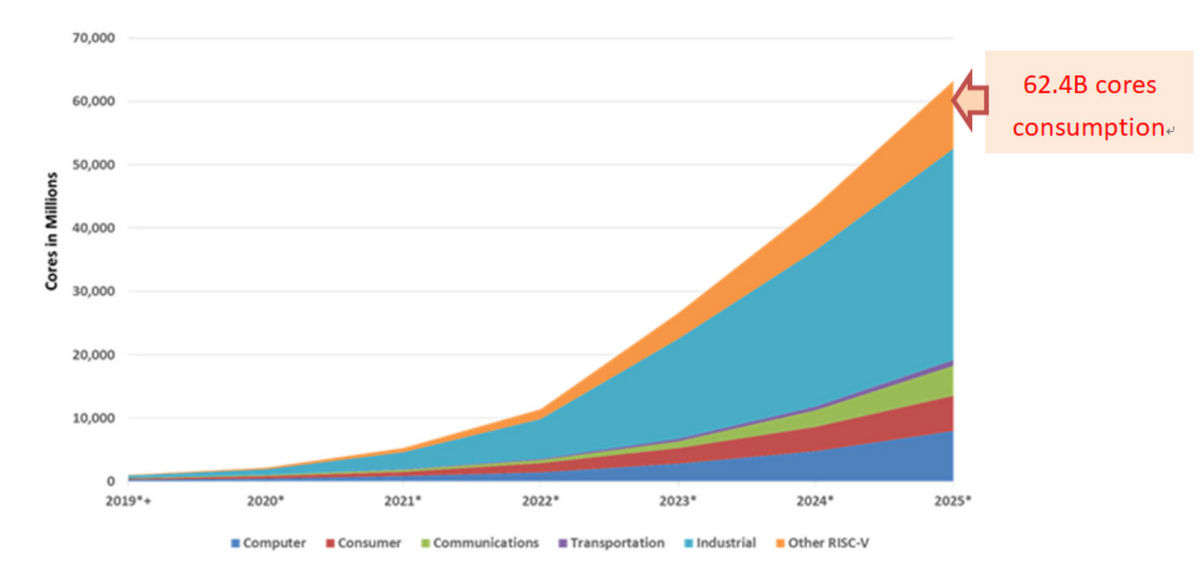

RISC-V 結合了過去數十年的指令集基礎開發出的一種精簡指令集中的開源硬體架構,他的目標是追求簡潔性、低成本以及高性能,希望成為一個通用的指令集架構,比起其他匯編語言,他的ISA基礎模塊化的特徵使得其開放性極高,方便進行編程、編譯與鏈接,不受到未來趨勢發展的影響,達成兼容、穩定的主要性能架構,根據台灣務聯網產業技術協會的資料統計與預測(如圖一),這將帶來更大的優勢, RISC-V的指令數量的使用與成長速度自2019年至2025年快速增長,在現今極為活躍,挑戰主流專有ISA的主導地位,由以下進行分析與介紹。

RV321作為RISC-V的基本整數指令集,相較於以往的指令集,能夠提升計算性能,擁有其獨特的優點,由以下六點介紹:

(一) 指令格式:RV321總共有47道指令,一共可分為六大類指令,分別是:

- I-Type—使用於短立即數和訪存load操作

- R-Type—使用於寄存器與寄存器之間操作

- S-Type—使用於訪存store操作

- B-Type—使用於條件跳轉操作

- U-Type—使用於長立即數跳轉操作

- J-Type—使用於無條件跳轉操作

RV321僅使用了32位指令字中不到八分之一的編碼空間,為ISA擴展出足夠的空間,簡化了數據通路的控制邏輯,同時大幅降低了成本。

(二) 寄存器:RV321僅須由零寄存器作為操作數,便能夠完成其他缺少零寄存器的指令集可以完成的操作,相較於分支預測複雜的PC,其分支指令預測的準確性較不被擔心。

(三) 整數計算: RV321提供了單獨的移位指令,不包含乘法與除法,以低寬數的數據訪問減少大量能量,RISC-V不需要額外添加成除法擴展便能夠完整運行,同時縮小了嵌入式晶片的面積。

(四) Load和Store: RV321能夠容納任何數據類型,在移植舊代碼時邊界對齊的訪問要求較為寬容,簡化了整體設計,達成高開放性的目標。

(五) 條件分支: RV321透過去掉部分擁有延遲分支特性的指令集,避免了條件碼需要設置隱式狀態的額外負擔,達成了簡潔化的目標。

(六) 無條件跳轉: RV321可以利用將零寄存器替換ra作為目標寄存器,達成無條件跳轉的目標,避開了錯綜複雜的程序調用指令,以達成簡潔化的目標。

以上RV321的內容與特徵與ARM-32、MIPS-32、x86-32等指令集相比,主要襯托與強調了RISC-V簡約與排除過去多項瑣碎錯誤的設計,促進未來指示令在編寫與運用的發展。

我認為任何人都可以使用的開源指令集對於未來硬體市場擁有極大的正向發展與潛力,RISC-V受到的侷限比傳統的指令集皆減少許多,在失敗嘗試後造成的外部成本上降低了許多的壓力,雖然RISC-V目前發展的時間較於短暫,整體而言在今日的生態環境下不夠完善,在晶片的選擇上仍面臨著許多挑戰,不過他仍舊為未來開源指令集市場提供了更多的資訊與經驗,鼓勵更多使用者進行成熟指令集的研究設計與開發,擁有更高品質的資訊環境