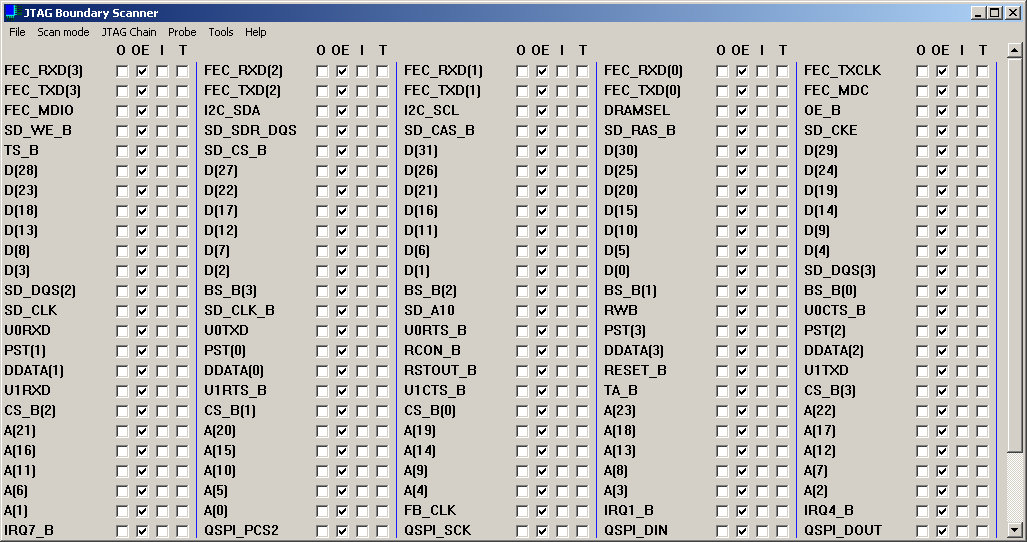

The JTAG Boundary Scanner is a JTAG software tool to debug or test any electronic boards with a JTAG interface.

-

Windows version GUI.

-

Implemented in C.

-

BSDL files support.

-

Target IO pins sampling and control mode ( SAMPLE & EXTEST ).

-

I2C Bus over JTAG emulation.

-

SPI Bus over JTAG emulation.

-

MDIO Bus over JTAG emulation.

-

Parallel port bus over JTAG emulation.

-

JTAG Bus scan and devices auto-detection.

-

BSDL files auto-load.

-

script support.

-

socket interface for remote control.

-

FTDI FT2232H based JTAG probes support (Olimex ARM-USB_OCD-H, Lattice HW-USBN-2B, Xilinx...).

-

JLINK JTAG probes support. Note : JLinkARM.dll need to be copied into the JTAGBoundaryScanner folder for the JLink probes support.

-

Parallel port based JTAG probes support (Altera ByteBlaster, Memec IJC-4, Macgraigor Wiggler).

This project is licensed under the GNU General Public License version 3 - see the LICENSE file for details