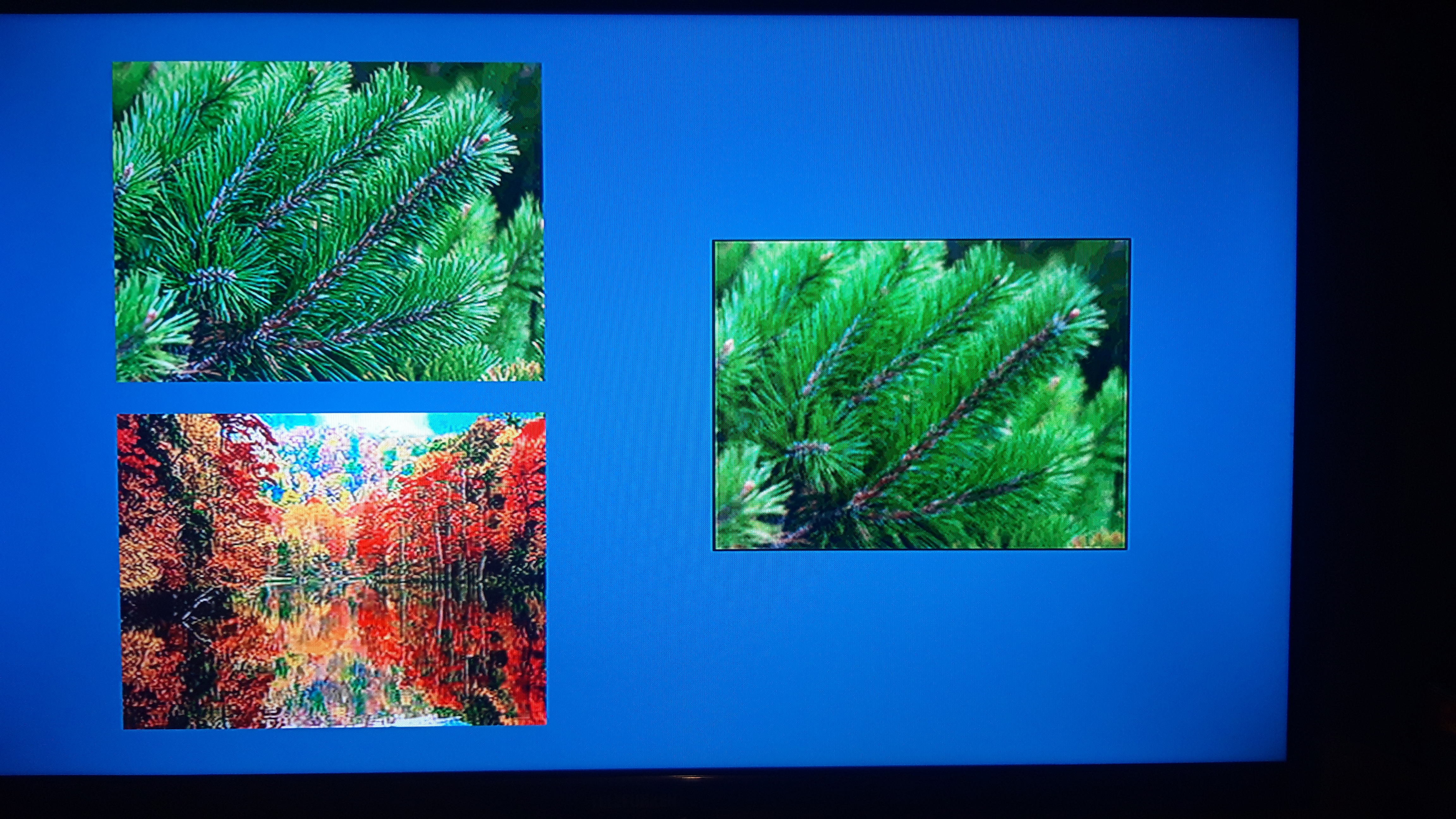

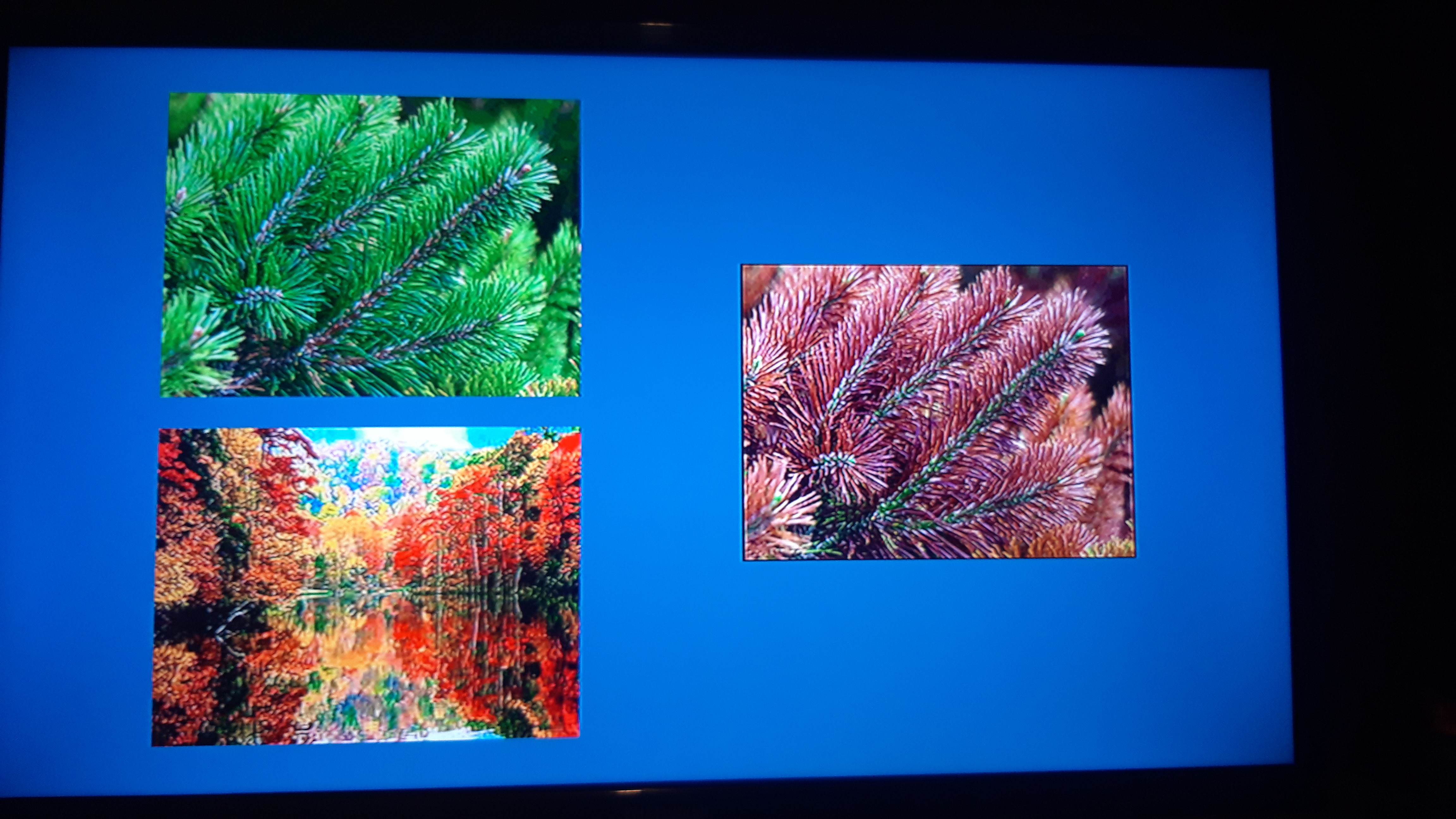

Hardware implemented image processing algorithms like Box blur or Gaussian blur on a Basys3 FPGA. Images are stored in BRAM memory of the FPGA board and displayed on the VGA port. Implementation using VHDL language.

Implemented Processing Algorithms: * Grayscale * Box Blur * Gaussian Blur * Invert Colors * Swap Colors