-

Notifications

You must be signed in to change notification settings - Fork 8.2k

Description

Hello people,

I have an observation regarding UART while using STM32H743ZI nucleo board with Zephyr3.2.0 and Zephyr SDK 0.15.2:

Case 1- When I am configuring 7-bit data length with even/odd parity it is configured as 8-bit. We are getting the correct parity, but 7-bit is not getting configured.

Case 2- While setting up 7-bit with none parity it is considered as 7-bit but not getting the correct response (garbage value).

I think it is related to the function uart_stm32_cfg2ll_databits in the file uart_stm32.c

Note: baudrate=115200 and usart3 peripheral

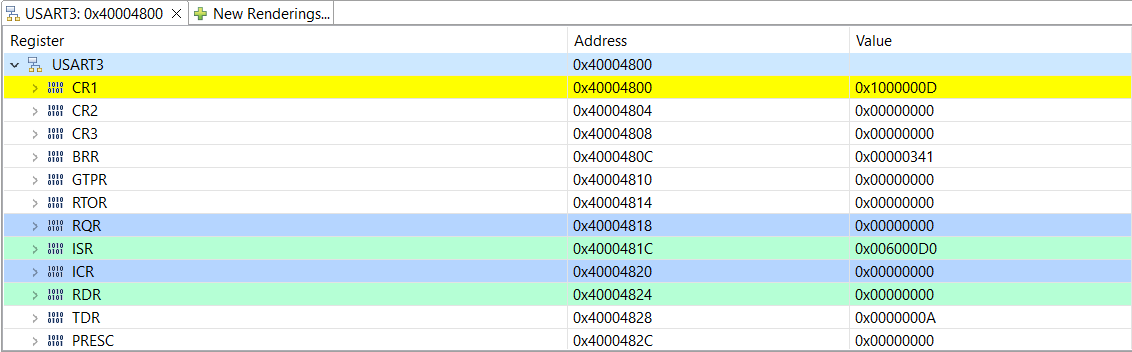

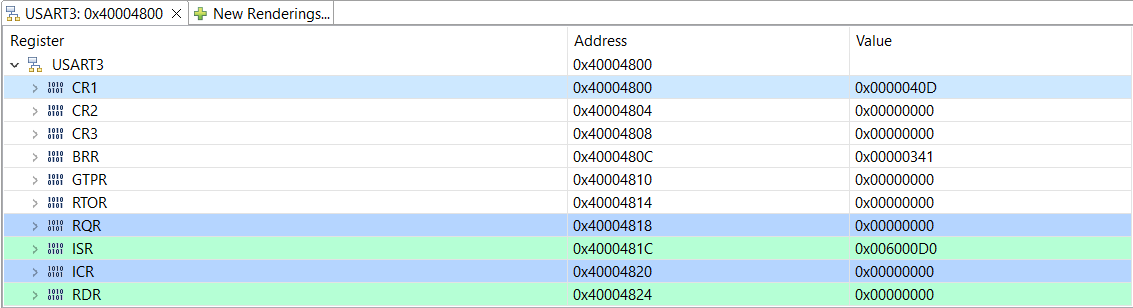

What I can deduct from this situation is, if we send 0x55 the uart data register gets the correct value but in response we get 0 byte in return. The CR1 (control register) have values for word length M1 (bit 28) & M2 (bit 12) :

Case 1- CR1->M[1:0] = '10' 1 start bit, 7 Data bits, n Stop bit

Case 2- CR1->M[1:0] = '00' 1 start bit, 8 Data bits, n Stop bit

Would like to know your thoughts on this.