-

Notifications

You must be signed in to change notification settings - Fork 128

AXI4 Stream and Packet Bus Bridge

nf10_axis_pbs_bridge

v1.00a

Gianni Anitchi (gianni.antichi_at_iet.unipi.it)

Muhammad Shahbaz (muhammad.shahbaz_at_cl.cam.ac.uk)

pcore (HW)

netfpga-10g/lib/hw/contrib/pcores/nf10_axis_pbs_bridge_v1_00_a/

AXI4-Stream

Packet-Stream

S_AXIS: Slave AXI4-Stream bus, Variable width

M_AXIS: Master AXI4-Stream bus, Variable width

S_PBS: Slave Packet-Stream bus, Variable width

M_PBS: Master Packet-Stream bus, Variable width

C_M_AXIS_TDATA_WIDTH: Data width of the master AXI4-Stream bus.

C_M_AXIS_TUSER_WIDTH: User width of the master AXI4-Stream bus.

C_S_AXIS_TDATA_WIDTH: Data width of the slave AXI4-Stream bus.

C_S_AXIS_TUSER_WIDTH: User width of the slave AXI4-Stream bus.

C_M_PBS_DATA_WIDTH: Data width of the master Packet-Stream bus.

C_S_PBS_DATA_WIDTH: Data width of the slave Packet-Stream bus.

No registers are implemented for v1.00a.

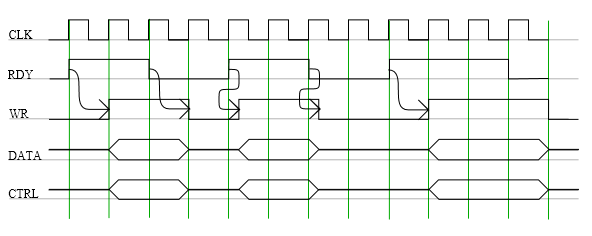

This block functions as a bridge between the AXI stream bus and the native NetFPGA-1G Packet stream bus. It enables existing NetFPGA-1G modules to be integrated in the new 10G platform with minimal changes. Packet stream bus is a fifo-like simple push interface with four signals: WR, RDY, DATA, and CTRL. The WR and RDY signals are each one bit wide while the CTRL is 4/8 bits wide and the DATA is 32/64 bits wide. Say module i wants to push a packet to module i+1. When i+1 is ready to accept some data, it will assert the RDY signal. Module i then puts the packet data on the DATA bus, sets the CTRL bus according to the data it is transmitting (the values of the CTRL bus are discussed later), and raises the WR signal whenever it is ready to send. Module i+1 should be ready to latch the data transmitted the next clock cycle after asserting the RDY signal. If module i+1 cannot accept anymore data, it will deassert the RDY signal at least one clock cycle before the data should stop arriving. The figure below demonstrates a valid transaction.

Note: This core provides bridging support for the streaming interfaces only. For register path please visit AXI4-Lite and Register Bus Bridge.