-

Notifications

You must be signed in to change notification settings - Fork 130

NetFPGA 1G CML Reference Flash

reference_flash_nf1_cml

projects/reference_flash_nf1_cml

-

NetFPGA Specific cores

-

Xilinx IP

The NetFPGA-1G-CML board provides the ability to reconfigure itself in system without power cycling the board. This feature allows new designs to be loaded on the fly. The reconfiguration abilities rely on the on board BPI flash and the Internal Configuration Access Port (ICAP). The BPI flash stores the required bitstream and the ICAP allows the board to reconfigure the FPGA from the BPI flash.

This project provides a basic framework for automatic configuration of the NetFPGA-1G-CML card's FPGA. The NetFPGA-1G-CML's BPI flash is used to store configuration bitstreams. The BPI flash can contain multiple bitstreams to reconfigure itself with. The NetFPGA-1G-CML uses the FPGA ICAP port to perform the reconfiguration.

In order to access the reconfiguration abilities of the NetFPGA-1G-CML, you must have these two capabilities:

- Access to the BPI flash

- Access to the ICAP port

The reference flash project provides these capabilities through a GPIO interface to bit-bang the BPI flash and with the AXI HWICAP peripheral provided by Xilinx.

This project allows the user to program the flash from the host PC, but a simple modification to the embedded firmware would allow any data source to provide a bitstream to use.

The configuration project provides a basic framework which may be useful for incorporation into your NetFPGA-1G-CML development projects. The configuration project currently has several important limitations that you should bear in mind:

- The FPGA always boots from golden image at startup, but the golden image can be overwritten.

- Booting partial bitstreams is not currently supported, although support may be added in a future release;

- Unless the user image contains the appropriate configuration logic (GPIO, axi_hwicap), further reconfiguration is no longer possible after the FPGA is programmed; the card must either be power-cycled or re-configured using a JTAG programming cable.

Follow the instructions below to setup and use the configuration project.

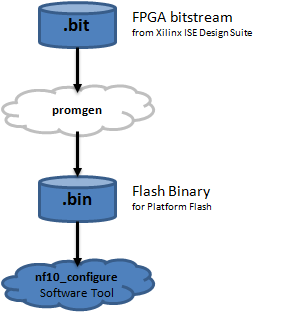

Programming the BPI flash requires a special binary bitstream format to be used. You will need to create a binary image file for each bitstream you wish to store in the BPI flash. FPGA bitstreams are converted into Xilinx compatible binaries by the ISE PromGen tool, as shown in the flow below:

Use the Xilinx promgen tool to convert a bitstream into a flash-compatible binary image.

promgen -c -u 0 <BITFILE> -p bin -w -data_width 8 -s 8192

The output from promgen looks like this:

Release 13.2 - Promgen O.61xd (lin64)

Copyright (c) 1995-2011 Xilinx, Inc. All rights reserved.

0x7d6b40 (8219456) bytes loaded up from 0x0

Using user-specified prom size of 8192K

Writing file "download.bin".

Writing file "download.prm".

Writing file "download.cfi".

This creates a binary named download.bin.

There are a couple of ways to program the BPI flash. One way is through the Xilinx Impact program. Instructions on how to use impact to program the BPI flash can be found in XAPP587. In this series of steps, we'll use the reference_flash_nf1_cml project to download the bitstream to the flash.

-

Program the reference_flash_nf1_cml bitstream to the FPGA by using JTAG.

-

Power cycle the PC to allow the NetFPGA-1G-CML card to renumerate on the PCIe bus. Power cycling the PC causes the PCIe bus to be re-scanned.

-

Enumerate the devices on the PCIe bus:

lspci | grep XilinxYou should see something like:

03:00.0 RAM memory: Xilinx Corporation Device 4243 (rev 02) -

Load the driver (if it is not already loaded). If you're unsure whether the driver is currently loaded, do:

-

Load the NetFPGA Driver (if it's not already loaded). If you're unsure whether the driver is currently loaded, do:

lsmod | grep nf10You should see a line beginning with nf10_eth_driver. If not, follow the instructions on the Driver Quick Start page.

-

Run the nf1_cml_configure command as follows:

./nf1_cml_configure -b <BITSTREAM> -a 0x00000000 -iReplace with the appropriate bitstream to download to the BPI flash. -

The FPGA should now be reconfigured and running the bitstream that was downloaded.

The nf1_cml_configure command takes several arguments. The -b option is used

to specify the bitstream to store. The -b option must be followed by a path

to a bitstream. The -a option is used to specify the address in the BPI flash

used to store the bitstream. Address 0x00000000 is the address of the golden

image that will be loaded into the FPGA at power cycle. Addresses above

0x00c00000 can be used to store alternate bitstreams that can be loaded

dynamically. The -i option instructs the FPGA to reconfigure itself the

bitstream after it has finished programming the BPI flash.