-

Notifications

You must be signed in to change notification settings - Fork 128

Partial Synthesis

Partial synthesis technique can be applied to current tool chain flows of the NetFPGA-10G projects. For the projects, a user can use the partial synthesis to save time for HW implementation.

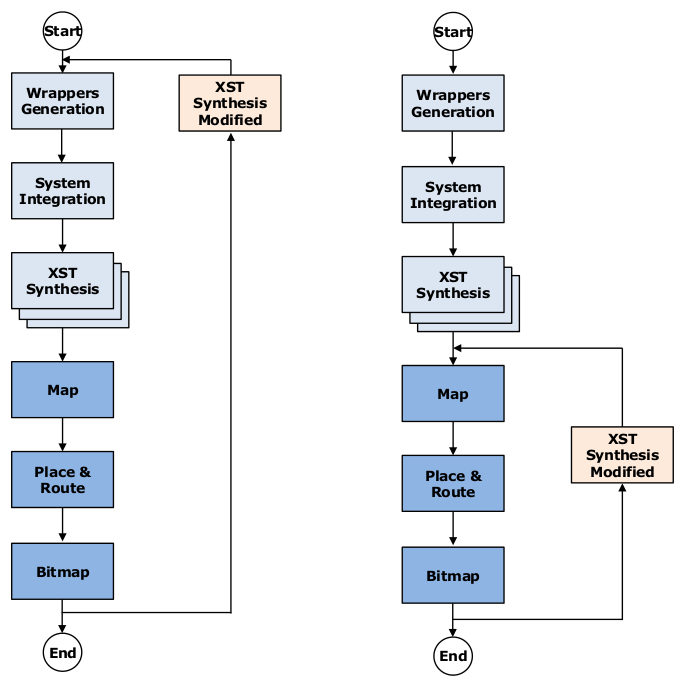

In current design flow, all designed cores are integrated, synthesized, mapped, and routed to achieve hardware implementation. In partial synthesis process, a core that is modified by a developer is only synthesised rather than integrating and synthesising all modules as current tool flows. Then, next flows are mapping and routing as the conventional process.

There are two ways of running partial synthesis. One uses current tool chain, and the other one runs Xilinx PlanAhead for partial synthesis.

Note: Please ensure that you need to do a 'make' first so that the .ngc files are created. Only then you can do partial synthesis.

-

Run makefile at one of the project directories

cd NetFPGA-10G-live/projects/reference_nic make partial MODULE=<module_instantiation_name>

This command synthesis the module that may be modified, and then mapped and routed as current tool chain.

- Run a script file at one of the project directories

cd NetFPGA-10G-live/projects/reference_nic

./planahead_run.sh <module_instantiation_name>

This shell scripts synthesis a modified module and runs PlanAhead tcl scripts for mapping and routing process.